cadence 学习笔记

Cadence自学笔记笔记

Cadence⾃学笔记笔记Cadence SPB15.7 快速⼊门视频教程⽬录Capture CIS 原理图及元件库部分第1-15讲第1讲课程介绍,学习⽅法,了解CADENCE软件Cadence下⼏个程序说明Design Entry CIS 系统级原理图设计Design Entry HDL 芯⽚设计Layout plus orcad ⾃带的pcb板布局布线⼯具,功能不是很强⼤,不推荐使⽤Pcb Editor Pcb librarian Cadence带的PCB布局布线封装设计PCB Router pcb⾃动布线Pcb SI SigXplorer Pcb电路板信号完整性仿真OrCAD Capture CIS 对元件管理更⽅便相对于OrCAD CaptureI 放⼤O 缩⼩页⾯属性设置options Design Templateoptions Schematic Page Propertie s第2讲创建⼯程,创建元件库原理图元件库,某元件分成⼏个部分,各部分间浏览ctrl+N ctrl+B元件创建完后修改footprint封装,options Package Properties第3讲分裂元件的制作⽅法1、homogeneous 和heterogeneous 区别homogeneous,芯⽚包含⼏个完全相同的部分选择该模式,画好第⼀个part后,后⾯的part会⾃动⽣成,因为完全⼀样。

但是引脚编号留空了,要⾃⼰再设置引脚编号。

heterogeneous芯⽚包含⼏个功能部分,可按照功能部分分成⼏个部分。

ctrl+N ctrl+B切换分裂元件的各个部分原理图画完之后,要对各元件⾃动编号,在项⽬管理窗⼝选择项⽬,点击tools annotate,在Action下⾯选择相应的动作。

2、创建homogeneous类型元件3、创建heterogeneous类型元件第4讲正确使⽤heterogeneous类型的元件1、可能出现的错误Cannot perform annotation of heterogeneous part J?A(Value RCA_Octal_stack ) part has not been uniquely group(using a common User Property with differing Values) or the device designation has not been chosen2、出现错误的原因分裂元件分成⼏个part,并且⽤了多⽚这样的分裂元件。

CADENCE学习笔记4

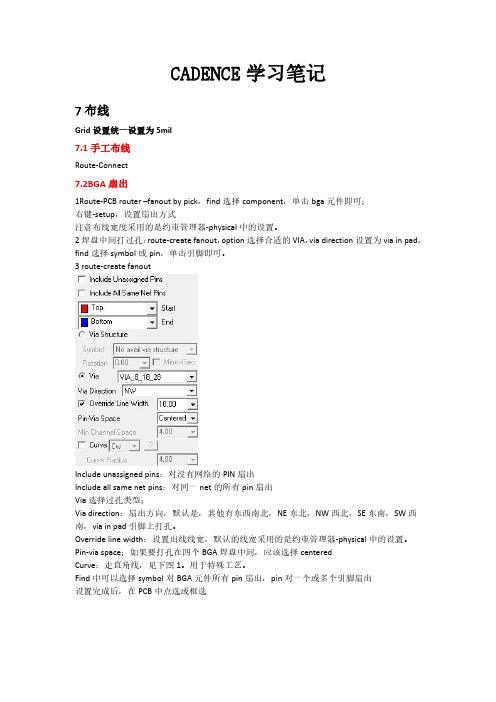

CADENCE学习笔记7布线Grid设置统一设置为5mil7.1手工布线Route-Connect7.2BGA扇出1Route-PCB router–fanout by pick,find选择component,单击bga元件即可;右键-setup,设置扇出方式注意布线宽度采用的是约束管理器-physical中的设置。

2焊盘中间打过孔:route-create fanout,option选择合适的VIA,via direction设置为via in pad,find选择symbol或pin,单击引脚即可。

3route-create fanoutInclude unassigned pins:对没有网络的PIN扇出Include all same net pins:对同一net的所有pin扇出Via选择过孔类型;Via direction:扇出方向,默认是,其他有东西南北,NE东北,NW西北,SE东南,SW西南,via in pad引脚上打孔。

Override line width:设置出线线宽,默认的线宽采用的是约束管理器-physical中的设置。

Pin-via space;如果要打孔在四个BGA焊盘中间,应该选择centeredCurve:走直角线,见下图1。

用于特殊工艺。

Find中可以选择symbol对BGA元件所有pin扇出,pin对一个或多个引脚扇出设置完成后,在PCB中点选或框选有时两个孔叠在一起,无法选中底层或小的过孔,如下图top层的PIN很难选中,首先在idle 模式时选择etch-top,然后使用route-create fanout,就很容易选中top层的PIN了。

7.2利用Constraints Manager实现长度约束规则的设定1在使用constraints Manager设定长度规则前,需给无源器件赋模型及电压值1)给电源地赋电压值操作:点击Logic/Identify DC Nets,在弹出的窗口中选择你要的电源网络名赋电压值即可2)给无源器件分配模型:analyze->model assignment2BUS的创建操作:在Constraints Manager的工作页中选中要创建Bus的Net、Xnet如D0~D7,点击右键,选Create/Bus3Pin pair的创建操作:在工作页中选中要创建Pin pair的一个Net或Xnet,如D0点击右键,选Create/Pin pair,在弹出窗口中First、Second Pins分别选中一个管脚即成一对Pin pair,点击OK即可,若一个Net、Xnet要创建多对Pin pair点击Apply即可继续创建下一Pin pair,而无需退出再进来4Differential Pair的创建操作:在工作页中选中要创建Differential Pair的一对Net或Xnet,如TD+/-,点击右键,选Create/Differential Pair5.不同Bus或Bus中成员的移植操作:拖动左键选中要添加或转移的Net、Xnet,点击右键,选Bus Membership,在弹出的窗口中选你要的Bus名即可7.3设置网络拓扑-T型连接点注意:在约束管理器中经常很多命令不能用,是因为PCB当前处于某个命令状态。

cadence学习笔记1--原理图的创建、查看等系列操作(持续更新)

1、亲手操作教程内容2、OrCAD Capture CIS进行原理图设计3、Cadece PCB Editor 进行PCB布局布线4、光绘文件(Artwork)制作,如何生成Gerber文件OrCAD Capture CIS与OrCAD Capture的区别元件的管理非常方便一、原理图的创建、重命名、删除1、cadence原理图的创建第一种方法:首先先选中原理图文件,然后点击菜单栏上的Design--New Schematic Page输入原理图名称第二种方法:先选中原理图文件,然后右键单击,选择New Page输入原理图名称2、删除原理图文件第一种方法:首先选择你要删除的原理图文件,然后点击菜单栏上的Edit---Delete,点击Delete之后,就会弹出下面的对话框。

点击确定之后,原理图2就删除了。

第二种方法:首先选择你要删除的原理图文件,然后鼠标右键点击Delete,如下图所示弹出如下所示,点击确定,原理图即删除。

3、cadence原理图的重命名第一种方法:选择需要更改原理图文件名的文件,然后点击菜单栏中的Design---Rename在弹出的对话框中,输入名称,点击OK即可。

第二种方法:选择需要更改原理图文件名的文件,然后右键点击Rename弹出对话框,在弹出的对话框中,输入名称,点击OK即可。

二、原理图的放大、缩小方法一: 直接按下快捷---i /o方法二:选择需要放大、缩小的原理图,然后选择菜单栏上的View---Zoom----In 放大Out 缩小方法三:按住键盘上的CTRL键,鼠标上的滑轮,向前滑动,原理图放大;向后滑动,原理图缩小。

如果原理图放的很大,可以移动滚动条进行原理图的上下左右的滚动。

也可以利用快捷键进行滚动条的移动,按住CTRL+PAGEUP,原理图向左移动;按住CTRL+PAGEDOWN,原理图向右移动;按住PAGEUP,原理图向上移动;按住PAGEDOWN,原理图向下移动。

cadence学习笔记

begin layer 正常焊盘regulapadpastemasktop 一样大小加焊层soldermask 阻焊层大0.1Mm通孔焊盘0.7Mm 通孔1mm就好1.先做花焊盘内径外经开口钻孔1mm的话内径比钻孔大6-8mil 1.5mm2.begin layer end 一样3.内层DEFAULT INTERNAL THERMAL 要用Flash焊盘4.sold-- 和pastmask 大点pastmask 和表层一样画好焊盘后,1.place-boud-top add-rectagule courtyad2.silkscreen add-line 和封装一样大3.画角标4. assembly top 直接画5 索引编号标示layout label refdel assembly top 中间qapl963silkscreenshape 矩形etch画圆第一次圆心第二次X半径Y不变错误相容shape merge shapeschret smbortsetup 最后一个设置路径通孔的封装焊盘制作。

通孔比焊盘大10-12mil1.flash 焊盘add-flsh 内圆1.5 外圆1.8 开口0.72做焊盘holetype 圆形plating 孔壁上锡plateddrill diameter 直径drill/slot光会文件时候,形状character 字母with 大小3 geometry-suare 方形圆孔的(第一个脚用的)thermalrelief 一样anti pad 大0.1mm做好后表层拷贝到END layer 表层制作完成4 default internal 花焊盘5pastemask top bottm 和表层一致。

SOLDERMASK 两层和表层大0.1mm之后做外面圆的。

1.添加线创建边框,2.倒角,,manufacture-draft-fillet3.准许布线区域,比边框小点,setup-areas-routekeepin 注意选择shapefill-unfilled不填充4.package-keepin edit-z-kopy 小点5.加固定孔6.setup-cross-section板子层7.铺通,内点层。

Cadence学习笔记1__原理图

cadence学习笔记1__原理图打开Design Entry CIS或OrCAD Capture CIS组件,选择OrCAD Capture CIS(不要选择OrCAD Capture,因为少了一些东西),如果勾选了左下角的“Use as default”复选框,下次就不用选择了,如果要使用其他的部分,就在打开后点击File→Change Product,会弹出一个“Cadence Product Choices”窗口:元器件库File→New→Library新建一个库,如下图,显示了路径和默认库名library1.olb,右击选择Save As可以改变路径和库名,右击新建一个元件,可以选择New Part或者是New Part From Speadsheet,是两种不同的方式,先介绍New Part的操作。

右击选择New Part后,弹出下面的对话框,在Name中填入元件名,还可以指定PCB Footprint,下面Parts per Pkg表示这个元件有几部分,1表示普通的元件,如果元件是两部分组成的分裂元件就写2,这里先操作1,点击ok。

中间的虚线框是这个元件的区域,右边会有一个工具栏,画直线、方框、圆、曲线,也可以输入一些字符,或者点放置一组引脚,放置结束后鼠标右击选择End Mode或按键盘左上角Esc键使命令结束,放置一组引脚的时候,还可以设置引脚的类型,比如输入、输出、双向、电源等等,这个没有区分电源和地,电源和地都是power型的,现在输入下面的几个数字,线型都是默认的Passive,引脚间距Pin Spacing设为1,点击ok,放置好后成为下面的样子,有些部分不需要显示,双击空白处弹出一个属性对话框,虚框里面的数字是PinName,虚框外面的数字是PinNumber,如果可视属性改成False就不显示了。

如果想改变其中一个引脚的引脚名、引脚编号、引脚类型,选中该引脚,右击选择Edit Properties,或者双击该引脚,如下图:画直线的时候,这里默认是按照栅格点为最小单位的,可以改变这种限制,画出任意长度任意角度的线,在工具栏Options Grid Display中,不要勾选Pointer snap to grid就可以了,记得画完想要的任意直线后,再将这里勾选,这是一个好习惯,可以让画出的线更规则整齐。

Cadence学习笔记(十三)

Cadence学习笔记(十三)1. 有些特殊的焊盘上要打很多孔,需要在Multiple Drill里设置。

2. .psm是元件封装的数据文件,不能直接编辑,.dra是绘图文件,我们可以用软件打开它对封装进行编辑。

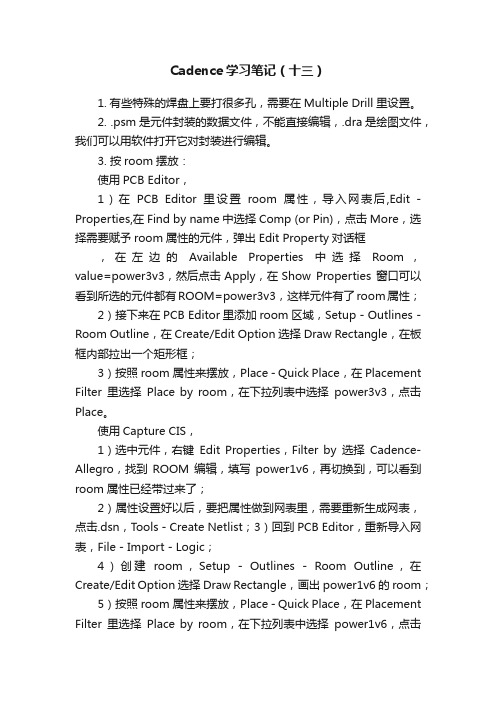

3. 按room摆放:使用PCB Editor,1)在PCB Editor里设置room属性,导入网表后,Edit - Properties,在Find by name中选择Comp (or Pin),点击More,选择需要赋予room属性的元件,弹出Edit Property对话框,在左边的Available Properties中选择Room,value=power3v3,然后点击Apply,在Show Properties 窗口可以看到所选的元件都有ROOM=power3v3,这样元件有了room属性;2)接下来在PCB Editor里添加room区域,Setup - Outlines - Room Outline,在Create/Edit Option 选择Draw Rectangle,在板框内部拉出一个矩形框;3)按照room属性来摆放,Place - Quick Place,在Placement Filter里选择Place by room,在下拉列表中选择power3v3,点击Place。

使用Capture CIS,1)选中元件,右键Edit Properties,Filter by选择Cadence-Allegro,找到ROOM编辑,填写power1v6,再切换到,可以看到room属性已经带过来了;2)属性设置好以后,要把属性做到网表里,需要重新生成网表,点击.dsn,T ools - Create Netlist;3)回到PCB Editor,重新导入网表,File - Import - Logic;4)创建room,Setup - Outlines - Room Outline,在Create/Edit Option选择Draw Rectangle,画出power1v6的room;5)按照room属性来摆放,Place - Quick Place,在Placement Filter里选择Place by room,在下拉列表中选择power1v6,点击Place。

cadence 原理图学习笔记

Design Entry CIS :板基设计的原理图设计Design Entry HDL Rules Checker 芯片设计工具Design Entry HDL 芯片设计工具PCB Editor:PCB布局布线的软件PCB Router:自动布线的工具PCB SI:线路板的完整性分析SigXplorer:线路板的完整性分析平时画原理图工具:OrCAD Capture CIS原理图模板设置:创建原理图元件库新建的原理库存储到指定的位置新建元件库元件新建元件的属性,包括名称,索引号,封装,多元件共体,等信息元件库原理图编辑界面单个引脚放置:弹出引脚属性设置阵列引脚放置:单个引脚双击修改属性多个引脚选中后在spreadsheet一起修改。

放置填充多边形按住shift可以画任意角多边形双击调出多边形属性选择实体就好了放置元件方体画方框结束鼠标重复放置命令,右击End Mode 或者Esc元件属性,设置引脚管脚显示等。

元件封装属性修改,原理图与pcb封装的映射就在这里修改。

多元件共体浏览分裂元件浏览。

不规则元件第3讲:分裂元件制作创建Homogereous双运放元件,每个单元件都一摸一样,引脚编号不同,电源脚编号可以重复。

新建元件画好第一个单元件快捷键Ctrl+n 自动生成另一部分单元件。

需要全部重新定义引脚编号。

引脚名称隐藏快捷键Ctrl+b 可以返回查看A部分元件图形。

创建Heterogeneous元件,每部分图形可以不一致。

快捷键Ctrl+n 会完全留空,全部要重新画。

分裂元件整体浏览第4讲分裂元件的自动编号的问题解决。

分裂元件的组定义,在元件库中操作,使同组元件具备同一属性。

第一步:创建元件第二步:给元件创建一个可以区分“分组”的属性完成了单个元件的新属性的创建依次创建同组的其它元件的新属性。

要求同名同参数第三步:在原理图中双击元件使同组的元件都新属性参数相同即可。

配对时不能冲突,比如双运放就只能有两个运放,同一参数有三个运放相同的话就出错了。

Cadence学习笔记

教程实例:DSP最小系统教程内容:1、利用Capture CIS进行原理图设计2、利用Cadence PCB Editor布局布线3、光绘文件(Artwork)制作,生成Gerber文件1mil=0.0254mm一原理图放大I 缩小O图纸右下角标注:Design Template1、创建新工程文件库文件2、参考datasheet在库文件中添加新元件:Place pin(画管脚编辑属性,power型visible)、Place pin array(管脚阵列)全部元件在Spreadsheet表中编辑(全选右键单击edit properties)可以在新建元件时选New Part Creation Spreadsheet通过表格创建多引脚元件常用选项:Option-part properties / package properties画不规则元件:Preference中取消Pointer snap to Grid,随意划线,画完再改回去3、分裂原件:homogeneous(完全相同)、heterogeneous(多个功能模块不同)以NE5532为例Tools-Annotate:给元件编号原理图中多个heterogeneous分裂原件的分组问题:库文件中选中分裂原件,在part properties中新建new property(name如package不可为group,value为组号123等),分裂原件的多个部分都要执行上一操作;打开原理图,双击分裂原件在property editor中将package属性设置为相同则为同一组分裂原件;要给之编号还需在annotate菜单physical packaging栏中将最后一项改为上文中name名大型元件的分割:参考《cadence电路设计案例精析》P184、在工程中添加元件库(自建库、系统库)电容电阻电感变压在discrete库中不知道元件在哪个库可以搜索放置元件place part5、元件的连接:直接连、用网络别名连接(在同一原理图页面中place net alias,名称相同表示电气上连接在一起)引脚悬空(末端连Place no connect)最好不要在放置元件时就把元件连在一起6、总线:功能类似的信号总线连接:Place-Bus 默认直角拐弯按住shift拉任意转方向画总线命名net alias(规则:XX[起始:结束])拖到总线上连接管脚与总线:place bus entry、按F4连续放置总线入口、信号线(与总线名一致)总线之间的连接:T型交叉有电气连接十字无实际电气连接不同页面之间的连接:place off-page connect 实际上与同一页面连接时net alias相似7、浏览BROWSE-元件parts(容易发现元件编号和大小错误)、网络Nets(双击看某一网络与哪些部分连接)、页面之间进行互联的网络:Browse-off page connectors、电气检查中的错误查看DRC 搜索Find元件parts、网络nets、Netlist修改元件库后更新元件:replace/update cache工程已经不在的元件在cache中删掉cleanup cache8、给元件添加封装信息:双击元件打开Property Editor,在PCB Footprint中标注封装批量修改封装:多选……在元件库中添加封装信息:打开库,选择元件-option-Package Property,回到项目中选中更改封装的元件-replace cache-选择replace schematic part property生成网表:先元件重编号Annotate、再DRC(design rules check)检查、选中dsn文件-Tools-create netlist-PCB Editor生成元件清单BOM,两种:1)Reports-CIS Bill of Materials-standard2)Tools- Bill of Materials9、二PCB高速电路设计流程原则:设计即正确1、工具介绍Allegro PCB Editor用于创建修改设计文件,是主要的设计工具,有两种模式:layout mode和symbol creation mode,进行手工布局布线时,工作在layout mode下,symbol creation mode中可以创建和修改package symbol、mechanical symbol、formal symbol、shape symbol、flash symbol Pad Designer创建及修改焊盘PadstackDBdoctor用于检查设计数据中的错误,Allegro Constraint ManagerAllegro约束管理器,布局布线约束规则的创建、管理、评估、检查Allegro PCB Router自动布线工具,对于有复杂涉及规则的高密度电路板处理能力很强Allegro PCB SI/PI信号/电源完整性仿真工具2、PCB设计流程(理论):1)规划出所设计电子设备的各项系统的规格,包括系统功能、系统的大小、运作情况以及成本2)做出系统的功能方块图,同时将每个方块之间的关系表示出来3)根据系统的功能方块图将系统分割成数个PCB,可以缩小系统的尺寸,同时可以使系统具有升级与交换零件的能力4)决定各PCB使用的技术以及电路数量,决定板子的大小。

CADENCE学习笔记3

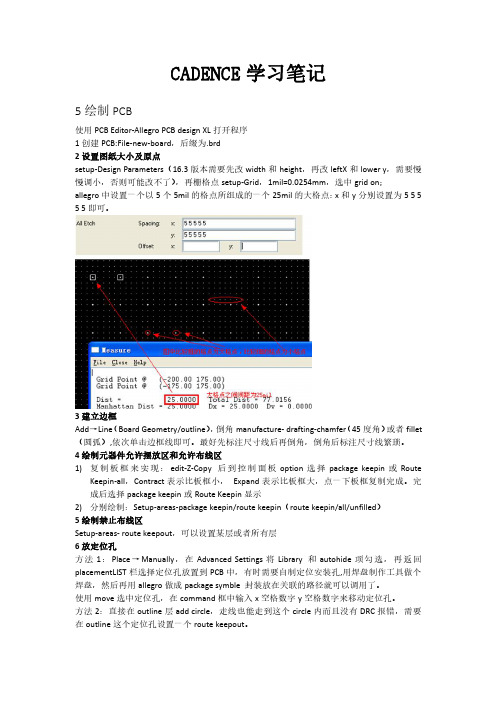

CADENCE学习笔记5绘制PCB使用PCB Editor-Allegro PCB design XL打开程序1创建PCB:File-new-board,后缀为.brd2设置图纸大小及原点setup-Design Parameters(16.3版本需要先改width和height,再改leftX和lower y,需要慢慢调小,否则可能改不了),再栅格点setup-Grid,1mil=0.0254mm,选中grid on;allegro中设置一个以5个5mil的格点所组成的一个25mil的大格点:x和y分别设置为555 55即可。

3建立边框Add→Line(Board Geometry/outline),倒角manufacture-drafting-chamfer(45度角)或者fillet (圆弧),依次单击边框线即可。

最好先标注尺寸线后再倒角,倒角后标注尺寸线繁琐。

4绘制元器件允许摆放区和允许布线区1)复制板框来实现:edit-Z-Copy后到控制面板option选择package keepin或RouteKeepin-all,Contract表示比板框小,Expand表示比板框大,点一下板框复制完成。

完成后选择package keepin或Route Keepin显示2)分别绘制:Setup-areas-package keepin/route keepin(route keepin/all/unfilled)5绘制禁止布线区Setup-areas-route keepout,可以设置某层或者所有层6放定位孔方法1:Place→Manually,在Advanced Settings将Library和autohide项勾选,再返回placementLIST栏选择定位孔放置到PCB中,有时需要自制定位安装孔,用焊盘制作工具做个焊盘,然后再用allegro做成package symble封装放在关联的路径就可以调用了。

Cadence16.5学习笔记之(一)—器件库、原理图

Cadence16.5学习笔记之(一)—器件库、原理图Cadence16.5学习笔记之(一)—器件库、原理图一、简单快捷键R—旋转器件方向(选中时)V—元件的镜像(水平)H—元件的镜像(竖直)F—放置电源G—放置地W—放置连线J—放置节点N—放置网络标号T—放置文本备注(Ctrl + Enter:换行)B—放置总线X—放置电器不连接F4—自动放置线,一直按一直放。

元件的复制:Ctrl + C或按住Ctrl,拖动元件即可。

放置全局网络标号(级联多个原理图):Place—Off-Page Connector放置线、总线时,任意角度走线—按住Shift键,再走线。

二、查找元件、网络连接等对整个工程、或单个的页面进行如下类似操作。

Edit->Browse->Parts:原理图画好了,选中工程,检查、查找定位器件Edit->Browse->Nets:网络连接,对于检查电源连接有帮助Edit->Browse->Off-Page Connector:显示工程中所有,原理图页面之间的网络连接(即归纳显示出所有全局网络标号)Edit->Browse->DRC Markers:DRC检查,显示出DRC电器检查的错误。

(删掉这些错误:Tools->Designe Rules Cheak->Yes->Action->Delete existing DRC marker->Yes)Ctrl + F:搜索定位元件、网络,如在PCB布局、布线时(勾选)。

以下类型选项:Parts:查找元件Nets:查看网络连接Power/GND:查看电源、地的网络连接Flat Nets:查看电源、地的网络连接(功能更强大)三、元件的更新或替换选择工程对话框中的File ->Design Cache->右键->Replace Cach->....->是否保留元件的遗留属性,可以将封装更新过来同样的操作,如果器件库中器件属性有改动,则更新元件(但不能将封装更新过来):File ->Design Cache->右键->Updata Cach四、选中元件1、单个选中、Ctrl + 选中元件、区域选中(整体移动),移动时电气连接是存在的,如果按住Alt再移动,则电气连接断开。

cadence学习笔记

关键字:1.快捷键2.注意基本了解了一下界面最左面的原理图管理器的基本设置;学会两个快捷键:放大I 缩小O;上下滚动pageup、pagedown;鼠标滚动左右滚动ctrl+ pageup、pagedown;ctrl+鼠标滚动刷新F5今天了解了cadence原理图页面的基本设置:页面大小、title是否显示,网格大小显示的基本设置!这都是在options选项中设置!今天学会了自己画简单元件(只需要一部分就能画出的元器件),了解其常见设置;画一个AT90S8535为例!1、练习了显示隐藏引脚(pin)的设置(Options-part propreties选项中设置,ture表示显示,falth表示隐藏);2、练习对引脚的批量属性改变!选中十字光标右键,eide proprepries…出现下图,一一修改;画原件应注意,body部分应该放在虚线框中;注意:liberiy中用到的快捷键:H,V,RAT90S8535:今天了解了分立元件的画法和理念,例如74系列的一类芯片!芯片中分几路功能相同(这种采用homogeneous(同址形式),另外一形式为heterogeneous);在new part 对话框中;设置项parts per Pkg表示元件需要分几部分画!注意:heterogeneous与homogeneous的区别:1.homogeneous是元件的每部分电气属性、结果相同;画一部分,自动生成下一部分!只需自己改下pin的number!heterogeneous不然,表示每一部分的电气属性、结果都不一样,每部分都需自己画!快捷键:ctrl+N 自动切换到下部分!Ctrl+B 自动切换到上面部分!哎!令人蛋腾+乳酸的大学,好不容易休息了一个双休,一切的一切都是拜自考占用学校所赐!何得何能啊?今天初涉原理图设计,也就是添加库文件,放置元器件(快捷键P),元器件连接方式:连接导线(w)、总线连接(b)、网络标号连接(n)等形式,自动命名(tools-annotate)注意:1. 连接导线时改变走线方向时按键shift;2.当某元器件的端口悬空时,需放置place no connect(快捷键X),表示引脚悬空电气检查时不报错!3.尽量不要使两元器件的端口直接连接,这样后期布板,电气检查,容易出错,而是用线直接连上;4.常用的库文件,也就是电阻电容之内的在discrete库中;5.放过的器件都在Design Cache中记录。

Cadence 学习笔记

Cadence 学习笔记◆CELL mode LVS/LPE 的rule文件写法:◇*DESCRIPTION 部分···CHECK-MODE = CELL ;FLAT/CELL/HIER/MULTI/COMPHCELL-FILE = HCELL.TAB ;HCELL filenameHCELL-MAX-SEGMENTS = 1000GEN-TEXT-FILE = HCELL.TEX ;HCELL text filenameGEN-TEXT-FLTNODE = YESGEN-TEXT-WIRE = YESCELL-CHILD-TEXT = YES···◇*INPUT-LAYER部分···IPOL Y = 4 CTEXT = 30 ATTACH = POL Y ;POL Y & Celtxt ···MT1 = 8 CTEXT = 31 ATTACH = MT1 ;MT1 & Pintxt···GEN-TEXT-LAYER = POL Y MT1 MT2 ;Which layer to generate text◆COMP mode LVS/LPE/PRE的rule文件写法:◇*DESCRIPTION 部分···CHECK-MODE = COMP ;FLAT/CELL/HIER/MULTI/COMPHCELL-FILE = HCELL.TAB ;HCELL filenameHCELL-IN-HCELL = YES···◇*INPUT-LAYER部分···CHECK-MODE = COMP ;FLAT/CELL/HIER/MULTI/COMPHCELL-FILE = HCELL.TAB ;HCELL filenameHCELL-IN-HCELL = YES···◇*OPERA TION部分···HEDTEXT = HCELL.TEX ;HCELL text filename◆LOGLVS用法◇顶层文件为Verilog◈CELL mode ◈COMP modeCEL HCELL.TAB FPINVER top.v CEL HCELL.TABCIR sub.spi CIR sub.spiLINK VER top.vCON/NOTOP LINKX CONX◇顶层文件为EDIF◈CELL mode ◈COMP modeCEL HCELL.TAB CEL HCELL.TABCIR sub.spi CIR sub.spiEDI top.edf EDI top.edfCON/NOTOP CON topX X(如果使用EDIF文件格式,则可能需要在primdev.tab文件中指定VDD、GND。

Cadence学习笔记

Cadence学习笔记1__焊盘一、焊盘前期准备在Allegro系统中,建立一个零件(Symbol)之前,必须先建立零件的管脚(Pin)。

元件封装大体上分两种,表贴和直插。

针对不同的封装,需要制作不同的Padstack。

名词解释不同层的名词解释:Begin Layer:最上面的铜Default Internal:中间层End Layer:最下面的铜Solder Mask:阻焊层、绿油层。

是反显,有就是没有。

等于是开了个小孔不涂绿油,是为了把焊盘或是过孔露出来,不涂绿油就是亮晶晶的铜,也就是在板子上看到的焊盘,或者是一个个的孔,其它的部分都上阻焊剂,也就是绿油,其实不光是绿色的,还有红色的、黑色的、蓝色的等等。

Paste Mask:助焊层、钢网层、锡膏防护层、锡膏层,也叫胶贴、钢网、钢板。

是正显,有就是有。

等于是钢网开了个窗,过波峰焊时机器就在此窗口内喷上焊锡了。

这一层是针对表面贴装(SMD)元件的,其实不光是表贴,通孔也要用到,因为通孔的表面上也有个焊盘,该层用来制作钢板﹐而钢板上的孔就对应着电路板上的SMD器件的焊点。

在表面贴装(SMD)器件焊接时﹐先将钢板盖在电路板上(与实际焊盘对应)﹐然后将锡膏涂上﹐用刮片将多余的锡膏刮去﹐移除钢板﹐这样SMD器件的焊盘就加上了锡膏,之后将SMD器件贴附到锡膏上面去(手工或贴片机)﹐最后通过回流焊机完成SMD器件的焊接。

通常钢板上孔径的大小会比电路板上实际的焊盘小一些。

Film Mask:预留层,用于添加用户自定义信息,根据需要使用。

不同焊盘的名词解释:Regular Pad:实际焊盘、规则焊盘,正片中使用,也是通孔焊盘的基本焊盘。

可以是:Null、Circle 圆型、Square 方型、Oblong 拉长圆型、Rectangle 矩型、Octagon 八边型、Shape形状(可以是任意形状)。

Thermal Relief:热焊盘、热风焊盘、花焊盘、防散热焊盘。

cadence学习笔记-画原理图库

cadence学习笔记-画原理图库Candence 学习笔记龚昌盛2014.04.11⼀、使⽤OrCAD Capture CIS来画原理图1.基本操作1).使⽤OrCAD Capture CIS2).原理图的放⼤缩⼩:I、OCtrl + ⿏标,滚轮。

⿏标所在位置,它以⿏标所在的位置为中⼼进⾏放⼤和缩⼩。

3).原理图上下滚动,Page UP、Page Down4).原理图左右滚动,Ctrl + Page UP、Ctrl + Page Down2.简单设置在画原理图之前,进⾏简单设置,Options -> Design Template,⽤于原理图的模版设置。

3.创建⼯程⽂档1.修改背景颜⾊Options ->Preferences ->Colors/Print -> Background2.修改原理图⼤⼩、栅格、单位Options ->Schematic Page Properties⼆、使⽤OrCAD Capture CIS来画规则的元件库→创建库→创建元件→1.基本操作File ->New ->Library2.更换路径选中C:\Library1.olb,File -> Save As或右键Save As ,MyLib.OLB3.创建新元件选中MyLib.OLB,右键,New PartPart Reference Prefix,器件的索引Parts per Pkg:⼀个元器件分成多个⼩部分来画。

4.放引脚5.放引脚排6.批量修改引脚信息选择引脚后,右键,Edit ProportiesNC,可以选择SHOT属性。

7.放⽅形BODY8.调整引脚位置9.修改⽅形BODY⼤⼩10.保存11.熟悉元件属性Options →Part ProportiesOptions →Package ProportiesView → Package⽤于显⽰⼀个元件有多少个⼦部分。

candence学习笔记

candence学习笔记主要学习以下内容:(1)利用OrCAD Capture CIS 进行原理图设计(2)利用Cadence PCB Editor 进行PCB布局布线(3)光绘文件(Artwork)制作,如何生成Gerber文件。

1. 工具介绍PCB Edtor 绘制PCB的工具PCB Librarian 制作PCB原件库的工具PCB Router自动布线的工具PCB SI 和SigXplorar 电路板信号完整性仿真的工具2 . OrCAD Capture CIS启动改工具后,会打开如下界面,通常选择OrCAD Capture CISOrCAD Capture CIS 与OrCAD Capture相比的优势是,在画原理图时对原理图中所有元件的管理会很方便。

3.DSN文件,是建立工程的数据库文件,包含了工程的所有数据。

Design Cache,每在原理图中放置一个元件,就会在该文件下将该元件保存下来,当下次再放置同一个文件时,就可以很方便的从这里来选取相关元件。

Library,包含元理图用到的库4. OrCAD Capture 的菜单是上下文相关的,对不同的窗口操作,菜单是不同的。

5. 原理图文件的创建(1) 选原理图文件夹,Design---->New Schematic Page----->.........(2) 选原理图文件夹,右键单击------>New Page--------->...........6. 原理图文件的删除(1) 选中要删除的原理图文件,Design---->Delete----->.........(2) 选中要删除的原理图文件,按Delete键7. 原理图文件的重命名(1) 选中要得命名的原理图文件,Design---->Rename----->.........(2) 选中要得命名的原理图文件,右键单击------>Rename--------->...........8. 原理图文件的放大和缩小(1) i:放大o:缩小都是以鼠标所在位置为中心(2) 通过菜单操作(3) Ctrl + 鼠标滚轮选中某元件后,就会以该元件为中心来进行放大或者缩小1. 打开Orcad capture CIS 后,在创建原理图前,需要做一些设置:(1)Options------>Design T emplate2.修改原理图的背景色:Options---->Preferences------>Background3.对单个原理图页面设置Options-------Schematic Page Properties4.元件库的建立在OrCAD Capture CIS中,选择File------New-----Library 。

CADENCE学习笔记7

CADENCE学习笔记10PCB常用命令解释注意:无论执行什么操作,有四点需要注意:1当前的模式;在状态栏可看到(次要)2option:重要3find:最重要4右键,经常会有些特殊的功能。

10.1元件选取多次选择或从整体选择中去掉部分idle模式下,右键-application mode-general edit,注意find中的选择对象;方法1:先框选,CTRL+点选或框选,如果新选与原来的选择重叠则减少选择,未重叠则增加选择;方法2:先框选,shift+点选或框选,增加选择;方法3:右键-section set-select by polygon,然后依次单击绘制一个区域选中其中的元件Select by lasso:鼠标任意绘制一个区域,其中元件被选中Select by path:沿路径选择也可以在general edit模式下,使用move等命令,右键-select by polygon,by lasso,by path。

此时option中dim active layer:当前层变暗;dim color assignments:取消高亮颜色。

10.2move1optionsripup etch;移动元件时,相关走线清除slide etch:移动元件时飞线隐藏,已布连线不断开,且自动修线。

stretch etch:选中移动元件时飞线隐藏,已布连线不断开type-incremental:增量方式旋转,可多次选择;absolute;只能一次旋转固定角度;angle设置旋转角度;point表示移动点的选取,user pick表示用户单击PCB的某点作为移动点,sym origin表示封装的原点,body center表示封装中心,sym pin#设置封装某个引脚作为抓取点,如果元件没有引脚1,会导致无法移动,比如mark点,或者以AK定义引脚的二极管,改用user pick 就好了;在placement edit、etch edit模式下,单击元件即可实现move功能。

CADENCE学习笔记2

CADENCE学习笔记2allegro界面介绍2.1option介绍可以完成所有属性的显示隐藏;1pin引脚2package geometry(封装外形):assembly:装配外框,分为top/bottompin number:引脚号place bound:元件重叠限制区域,分为top/bottomsilkscreen:封装丝印,分为top/bottom,常用2package keepin/keepout,route keepin/keepout:布局布线限制局域,常用3board geometry板图形,常用outline:板外框silkscreen:一些板图形,比如公司标志,一些line线等,分为top/bottom dimension:尺寸,制版说明,技术要求等5REF DES元件号assembly:装配元件号silkscreen:丝印元件号,常用6etch:布线,覆铜等,选择ETCH-top层,将top层显示为当前层,同样可以设置其他层为当前层;7device type:器件型号,封装型号8component value:元件值assembly:装配用元件值silkscreen:丝印元件值9via classFilmmasktop光绘掩膜10via keepout–各层layer禁止放置过孔的区域2.2visiblity控制面板可以控制每层的ETCH-布线覆铜(覆铜属于shape),via-过孔,pin-引脚,DRC的显示隐藏;这些属性在option控制面板中也有。

还有很多属性visiblity控制面板无法控制;Conductors:针对所有布线层开关;planes:内电层;etch:布线;PLAN:GRE开关。

View-color view save:将当前显示的图层保存,可以visibility面板的-views下拉框中可找到。

2.3FIND filter介绍Groups:群组;comps:带有元件序号的Allegro元件;function:一组元件中的一个元件;symbols:元件;Nets:一个网络pin;引脚,包括pad,固定孔(plated或no plated)Vias:过孔或贯穿孔clines:布线,具有电气特性的线段;cline segs:cline中没有拐弯的导线,即线段;line:没有电气特性的线段;other segs:lines中没有拐弯的线,即线段;shape:形状;void:任意多边形的挖空部分;figure:图形符号;DRC errors(违反设计规则的位置及相关信息)text:文本,包括元件标号ratsnests:飞线;rat TS:T形飞线;Find by name中devtype:器件类型;symtype:符号类型;property:属性;group:2.4修改工具栏View-customize toolbar-command中选中一些按钮,拖到工具栏(可以不同工具栏)上即可2.5application mode在placement edit模式下,系统会自动将未摆放的元件列在右侧的options下。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

1. Allegro中我设置了highlight的颜色为白色,但选中后颜色是白蓝相间的,很不方便查看。

是什么地方需要设置,哪位大虾告诉哈我?答:setup/user preferences/display/display_nohilitefont 这个选项打勾就行了。

2. 不小心按了Highlight Sov后部分线高亮成白色,怎样取消?答:这个是用来检查跨分割的,取消的办法是:如果是4层板的话,在电源层跟地层都铺上地网络,然后再按Highlight Sov刷新即可。

3. 如何更改Highlight高亮默认颜色?答:可以在Display->Color/Visibility->Display->Temporary Highlight里修改即可,临时修改颜色可以点Display->Assign Color来实现。

4. 如实现Highlight高亮部分网络,而背景变暗,就像Altium Designer那样?答:可以在Display->Color/Visibility->Display->Shadow Mode打开该模式,并且选中Dim active layer 即可。

5. 快速切换层快捷键答:可以按数字区里的“-”或“+”来换层。

6. OrCAD跟Allegro交互时,出现WARNING [CAP0072] Could not find component to highlight 错误等?答:OrCAD输出网表,Allegro导入网表,确保两者对的上号,然后在Orcad选中元件,再右键Editor Select,即可在Allegro中选中该元件;反过来,在Allegro中要先Highlight某元件,在Orcad中变会选中该元件。

1.ORcad :首先打开orcad和allegro分别占1/2的窗口界面。

然后orcad中Tools/creatnetlist/PCB Editor中Create PCB Editor Netlist下的Options中设置导出网表的路径。

然后确定导出网表。

2.Allegro:Files/Import/Logic/ 最底下的Import directory中设置刚才导出网表的路径。

然后导入即可,只要不出现error即可。

3.操作互动:首先在allegro中选中高亮display/Highlight,然后到orcad中选中一个元件或者引脚哪么对应的allegro中旧高亮显示了。

当然了选中Dehighlight就可以不高亮显示了。

7. 关于盲孔及埋孔B/B Via的制作方法?答:可先制作通孔Thru via,然后Setup->B/B via definitions->Define B/B via,如下图,完成后,再在Constraint Manager->Physical->all layers->vias里添加B/B Via即可。

8. 在用Router Editor做BGA自动扇出时,遇到提示无法找到xxx解决方法?答:路径里不能有中文或者空格。

9. 在制作封装时,如何修改封装引脚的PIN Number?答:Edit->Text,然后选中PIN Number修改即可。

10. 对于一些机械安装孔,为什么选了pin后,选中老是删除不了?答:因为这些Mechanical Pin属于某个Symbol的,在Find里选中Symbols,再右键该机械孔,点Unplace Component即可。

11. 在OrCAD里用Off Page Connector为什么没起到电气连接的作用?答:先科普下:1.off_page connector确实是用在不同页间比较合适,同一页中可以选择用连线,总线或者Place net alias来连通管脚,没有见过在同一页中用off_page connector的。

2.off_page connector在电气特性上是没有方向性的,但是在制图时,为了人看方便,所以使用的双向信号和单向信号的符号还是不同的,这是为了让人知道它是输入还是输出。

电气特性的连接是在芯片做原理图封装时,对管脚定义时形成的。

原因分析:Off Page Connector用于平坦式电路图中多页面原理图电气连接(这些原理图必须从属于同一个Parent Sheet Symbol)。

如下图所示才算同一个Parent sheet symbol。

12. 如何将两块电路板合成一块?答:先将电路板A导出成Sub-drawing,然后电路板B再导入该Sub-drawing,同时原理图也合成一个原理图,完后创建网表Netlist,电路板B再导入该Netlist,此时电路板B存在一些未名的器件和已名的器件,因为导入Sub-drawing元件布局跟连线都跟原来的保持一致,但是去掉了电路板A中元件的网表信息的,而导入该Netlist则导入了网表信息,为了利用原来的元件布局,可用Swap->Component命令来交换元件网表信息而保持原来的布局不变。

13. 元件封装中的机械安装孔Mechanical Symbol?答:使用Allegro PCB Design XL的Package symbol模板建立一个元件封装,对于有电气连接性的pin将其按照实际元件的引脚编号。

而对于机械安装孔的pin,将其pin number删除掉,表明它是一个非电气连接性的引脚,大多数指安装孔。

比如DB9、RJ45等接插件都具有两个(或者以上)的机械孔。

14. Mechanical Symbol已经存在库中,但Place->Manually在Mechanical Symbols里见不到?答:在Placement里的Advance Settings选项卡中选中Library即可。

15. ORCAD画原理图时,off page connector 后加上页码的方法?答:用ORCAD画原理图,很多ORCAD的SCH中,大多在offpage connector 加上一个页码。

方法很简单:Tools->annotate->action->add intersheet reference即可。

16. 布线时,添加到约束中的所有的通孔和盲孔都可以显示,但是所有埋孔都不能显示,不知道为什么。

比如,L1—L2,L1--L3,L1--L8(8层板)都可以显示,但是L2——L7,L3--L6都无法显示?答:在pad制作时需要把microvia点上即可。

17. Allegro Region区域规则设置?答:setup - constraints - constraint manager或者快捷菜单中带cm标记的,Cmgr图标启动constraints manager图表窗体,在窗体中选择object-->create-->region,此后就在表中设置一下物理或者间距规则,只不过在设置通孔时可以双击弹出选择过孔窗体,非常方便。

最后设置完了点击OK,此后在allegro pcb的菜单中shape下有利用Rectangular建立一个矩形,然后在option中的active class 选择Constraint Region,subclass选择all.assgin to region选择你刚刚在规则管理中建立的区域规则名称,如果没有说明你没有保存好,重新操作一遍以上的规则建立过程。

18. 与某个Symbol的引脚相连的Clins和Vias删除不了?答:可能该Symbol为fix,Unfix该Symbol即可。

19. Allegro使用Fanout by pick功能时老是扇不出,而且停到一半卡死?答:可能待扇出Symbol所在区域中存在Etch层的Shape,要删掉这些Shape才行。

20. 将某个网络设置成电源网络,并设置其电压、线宽等属性?答:选中该Net,然后Edit->Properties,按下图修改其属性即可。

或者也可以依次点击Tools->Setup Advisor->Next->Next->Identify DC Nets->填入网络的Voltage即可。

21. 为什么器件bound相互重叠了,也不显示DRC错误呢?是不是哪里设置要打开以下?3 u# n/ O$ F1 d3 @# l. |答:有两种,一个是pin到pin的距离约束,主要是防止短路,需要在constrain中设置smd pin 到smd pin的距离,然后在setup——constrain——modes中的spacing modes中勾选smd pin to smd pin。

另外一个是检查两个器件是否重叠,需要用到place bound top/bottom,至于是顶层还是底层,要更具你的器件而定,这个规则只要是两个器件的place bound层相互重叠就会报警,同样需要打开检查开关,在setup——constrain——modes中的design modes(package)中勾选package to package为on(其中on为实时监测,只要触犯规则就报警,batch为只有点击update drc才监测报警,off是不监测,违反规则不报警)。

当然,Color/Visibility中Stack-UP中相应层中的DRC显示也要开启。

22. 拖动时为什么不显示鼠线?移动铺铜或元件时,原来与之相连的过孔和线都消失了,怎么解决?答:Move时要选中Ripup Etch。

选中Ripup Etch时将去掉跟该Symbol引脚相连的Clines,同时显示Rats,选中Stretch Etch时用Clines代替Rats,而什么都不选时则保留Clines同时显示Rats。

所以移动铺铜或元件为保留原来的过孔和线,则不能选中Ripup Etch。

另外:定制Allegro环境Find(选取)Design Object Find Filter选项:Groups(将1个或多个元件设定为同一组群)Comps(带有元件序号的Allegro元件)Symbols(所有电路板中的Allegro元件)Functions(一组元件中的一个元件)Nets(一条导线)Pins(元件的管脚)Vias(过孔或贯穿孔)Clines(具有电气特性的线段:导线到导线;导线到过孔;过孔到过孔)Lines(具有电气特性的线段:如元件外框)Shapes(任意多边形)Voids(任意多边形的挖空部分)Cline Segs(在clines中一条没有拐弯的导线)Other Segs(在line中一条没有拐弯的导线)Figures(图形符号)DRC errors(违反设计规则的位置及相关信息)Text(文字)Ratsnets(飞线)Rat Ts(T型飞线)文件类型:.brd(普通的电路板文件).dra(Symbols或Pad的可编辑保存文件).pad(Padstack文件,在做symbol时可以直接调用).psm(Library文件,保存一般元件).osm(Library文件,保存由图框及图文件说明组成的元件).bsm(Library文件,保存由板外框及螺丝孔组成的元件).fsm(Library文件,保存特殊图形元件,仅用于建立Padstack的Thermal Relief).ssm(Library文件,保存特殊外形元件,仅用于建立特殊外形的Padstack).mdd(Library文件,保存module definition).tap(输出的包含NC drill数据的文件).scr(Script和macro文件).art(输出底片文件).log(输出的一些临时信息文件).color(view层面切换文件).jrl(记录操作Allegro的事件的文件)设定Drawing Size(setup\Drawing size....)设定Drawing Options(setup\Drawing option....)status:on-line DRC(随时执行DRC)Default symbol heightDisplay:Enhanced Display Mode:Display drill holes:显示钻孔的实际大小Filled pads:将via 和pin由中空改为填满Cline endcaps:导线拐弯处的平滑Thermal pads:显示Negative Layer的pin/via的散热十字孔设定Text Size(setup\Text Size....)设定格子(setup \grids...)Grids on:显示格子Non-Etch:非走线层All Etch:走线层Top:顶层Bottom:底层设定Subclasses选项(setup\subclasses...)添加\删除LayerNew Subclass..设定B/Bvia(setup\Vias\Define B/Bvia...)Ripup etch:移动时显示飞线Stretch etch:移动时不显示飞线信号线的基本操作:更改信号线的宽度(Edit\Change\Find\Clines)option\linewidth删除信号线(Edit\Delete)改变信号线的拐角(Edit\Vertex)删除信号线的拐角(Edit\Delete Vertex)23. 如何修改某个Shape或Polygon的网络属性以及边界?答:Shape->Select Shape or void->单击选中该Shape->在右边Option栏Assign net name中将Dummy Net修改成自己想要的网络,当鼠标光标停留在边界时可以拖动光标修改边界。