FPGA配置芯片的网上汇总较杂需自己总结修订稿

一种基于fpga的cx9261芯片配置方法

一种基于fpga的cx9261芯片配置方法下载温馨提示:该文档是我店铺精心编制而成,希望大家下载以后,能够帮助大家解决实际的问题。

文档下载后可定制随意修改,请根据实际需要进行相应的调整和使用,谢谢!并且,本店铺为大家提供各种各样类型的实用资料,如教育随笔、日记赏析、句子摘抄、古诗大全、经典美文、话题作文、工作总结、词语解析、文案摘录、其他资料等等,如想了解不同资料格式和写法,敬请关注!Download tips: This document is carefully compiled by the editor. I hope that after you download them, they can help you solve practical problems. The document can be customized and modified after downloading, please adjust and use it according to actual needs, thank you!In addition, our shop provides you with various types of practical materials, such as educational essays, diary appreciation, sentence excerpts, ancient poems, classic articles, topic composition, work summary, word parsing, copy excerpts, other materials and so on, want to know different data formats and writing methods, please pay attention!FPGA技术在现代电子行业中扮演着越来越重要的角色,而CX9261芯片作为一种基于FPGA的解决方案,其配置方法对于设备性能的优化和功能实现至关重要。

FPGA经验之谈汇总

FPGA经验之谈汇总FPGA设计要点之一:时钟树对于FPGA来说,要尽可能避免异步设计,尽可能采用同步设计。

同步设计的第一个关键,也是关键中的关键,就是时钟树。

一个糟糕的时钟树,对FPGA设计来说,是一场无法弥补的灾难,是一个没有打好地基的大楼,崩溃是必然的。

具体一些的设计细则:1)尽可能采用单一时钟;2)如果有多个时钟域,一定要仔细划分,千万小心;3)跨时钟域的信号一定要做同步处理。

对于控制信号,可以采用双采样;对于数据信号,可以采用异步fifo。

需要注意的是,异步fifo 不是万能的,一个异步fifo也只能解决一定范围内的频差问题。

4)尽可能将FPGA内部的PLL、DLL利用起来,这会给你的设计带来大量的好处。

5)对于特殊的IO接口,需要仔细计算Tsu、Tco、Th,并利用PLL、DLL、DDIO、管脚可设置的delay等多种工具来实现。

简单对管脚进行Tsu、Tco、Th的约束往往是不行的。

FPGA设计要点之二:FSM关于上期的时钟树,可能说的不是很确切。

这里的时钟树实际上泛指时钟方案,主要是时钟域和PLL等的规划,一般情况下不牵扯到走线时延的详细计算(一般都走全局时钟网络和局部时钟网络,时延固定),和ASIC中的时钟树不一样。

对于ASIC,就必须对时钟网络的设计、布线、时延计算进行仔细的分析计算才行。

FSM:有限状态机。

这个可以说时逻辑设计的基础。

几乎稍微大一点的逻辑设计,几乎都能看得到FSM。

FSM分为moore型和merly型,moore型的状态迁移和变量无关,merly型则有关。

实际使用中大部分都采用merly型。

FSM通常有2种写法:单进程、双进程。

初学者往往喜欢单进程写法,格式如下:always @( posedge clk or posedge rst )beginif ( rst == 1'b1 )FSM_status <= ......;elsecase ( FSM_status )......;endcaseend简单的说,单进程FSM就是把所有的同步、异步处理都放入一个always中。

FPGA工程师职场必修能力和面试总结

FPGA工程师职场必修能力和面试总结FPGA这个概念在很多应用领域,出现的频率越来越多,例如:在比特币挖矿中在基于FPGA的矿机,自动驾驶系统中实时视觉处理系统,军事领域的导弹导航系统等。

这段时间,也去面试了十多个FPGA岗位,发现在面试过程中发现有很多很突出的问题,特别是在比较大型的公司都会相当重视。

具体来说会考量面试者很多的几个知识点:同步时钟设计、亚稳态、异步FlFOo可以亳不夸张地说,如果面试者要是能弄明白这几个问题,那么至少能满足迄今绝大多数公司对FPGA岗位的大部分需求。

相比其他电子行业,从事FPGA开发工资高,对技术水平要求也高,一方面除了要求工程师对广泛的基础知识要有一定的了解,其次也需要有实际的经验,如果在投递简历时,能通过拍照片、录视频的方式把你曾经做过的项目经验经历打包整理好,在面试的时候用上,会极大增加你的通过率。

技术面试时,多讲讲你做过的东西,怎么做具体有哪些想法,扩展性思维,尽量多去开拓一些相关性知识,让企业者更多看到你知道得很多,基础很扎实,容易上手易于培养,后续就基本没什么问题了。

以下录自某FPGA专业通信设备商的人员招聘,对于入职FPGA工程师岗位的具体要求。

整个面试过程包含笔试(专业基础题)+面试(主观分析题)共两个部分,下面为大家提供具体题目及参考回答。

FPGA工程师面试必考题目主观题:1.你认为你从事这项工作有什么主要的优点?2.描述一下你之前参与的最有成就的项目,你觉你的成就来源是什么?3.你觉得你自身最大的缺点是什么?该如何克服或改进。

4.你该如何与最新的技术保持同步?专业知识题:1.什么是同步逻辑和异步逻辑?同步时序逻辑电路的特点:各触发器的时钟端全部连接在一起,并接在系统时钟端,只有当时钟脉冲到来时,电路的状态才能改变。

改变后的状态将一直保持到下一个时钟脉冲的到来,此时无论外部输入有无变化,状态表中的每个状态都是稳定的。

异步时序逻辑电路的特点:电路中除可以使用带时钟的触发器外,还可以使用不带时钟的触发器和延迟元件作为存储元件,电路中没有统一的时钟,电路状态的改变由外部输入的变化直接引起.同步逻辑是时钟之间有固定的因果关系。

《详解FPGA:人工智能时代的驱动引擎》札记

《详解FPGA:人工智能时代的驱动引擎》阅读随笔目录一、FPGA简介 (2)1.1 FPGA的定义与特点 (3)1.2 FPGA的发展历程 (4)1.3 FPGA的应用领域 (5)二、FPGA的工作原理 (7)2.1 FPGA的基本架构 (8)2.2 FPGA的工作模式 (10)2.3 FPGA的编程语言 (11)三、FPGA在人工智能领域的应用 (12)3.1 机器学习与深度学习 (14)3.2 自动驾驶与机器人技术 (15)3.3 无人机与智能物流 (17)3.4 医疗诊断与生物信息学 (18)3.5 其他领域的FPGA应用 (20)四、FPGA的设计与优化 (22)4.1 FPGA设计流程 (23)4.2 硬件描述语言 (25)4.3 设计优化策略 (26)4.4 性能评估与测试 (28)五、FPGA的未来发展趋势 (29)5.1 技术创新与突破 (30)5.2 行业合作与生态系统建设 (32)5.3 应对挑战与机遇 (33)六、结论 (35)6.1 FPGA在人工智能时代的重要性 (36)6.2 未来展望与期许 (37)一、FPGA简介FPGA(现场可编程门阵列)是一种集成电路芯片,它允许设计师在硬件层面上实现可编程的解决方案。

与传统的专用硬件电路相比,FPGA具有更高的灵活性和可扩展性,因此在人工智能、数据中心、通信等领域得到了广泛应用。

FPGA的核心特点是可编程性。

它可以根据需要动态地重新配置内部逻辑单元,从而实现各种功能。

这种可编程性使得FPGA在应对不断变化的应用需求时具有很高的效率。

FPGA还具备低功耗、高性能、高可靠性等优点。

FPGA的发展历程可以追溯到20世纪80年代,当时Xilinx公司推出了世界上第一款商用FPGA产品。

随着技术的不断发展,FPGA的性能不断提高,功能也越来越丰富。

FPGA已经发展到了第四代,即UltraScale系列,其最大容量可达140亿个逻辑单元,支持多种编程语言和开发工具,为人工智能时代的应用提供了强大的支持。

加法器除法器FPGA实现总结文档

加法器除法器FPGA实现总结文档FPGA实现加法器和除法器总结文档引言FPGA(Field-Programmable Gate Array)是一种可编程逻辑芯片,可以根据需要进行配置和重新编程,具有灵活性和可重复性。

在数字电路设计中,加法器和除法器是非常常见且基础的功能模块。

本文将总结FPGA实现加法器和除法器的过程和结果,并对实现的优势和不足进行分析。

一、加法器的实现在FPGA中实现加法器有多种方法,最基本也是最常见的是使用全加器构建一个完整的加法器。

全加器是一个三输入一输出的电路,可以实现两个二进制位的加法。

通过级联多个全加器,就可以构造出任意位数的加法器。

1.实现步骤:(1)定义加法器的输入和输出位数:假设我们要实现一个4位加法器,那么就需要4个输入(A[3:0]、B[3:0])和一个4位输出(SUM[3:0])。

(2)使用VHDL或Verilog等硬件描述语言来描述全加器和加法器的逻辑。

(3)使用逻辑综合工具将硬件描述语言代码综合为逻辑电路连接。

(5)验证加法器的功能和正确性。

2.实现优势:FPGA实现加法器的优势主要体现在以下几个方面:(1)灵活性:FPGA可以根据需要重新编程,可以方便地修改加法器的位数和功能。

(2)速度:FPGA中的逻辑电路是并行计算的,可以实现高速的加法运算。

(3)资源利用:FPGA可以利用其内部的查找表(lookup table)实现逻辑运算,节省了硬件资源的使用。

3.实现不足:FPGA实现加法器也存在一些不足之处:(1)成本高:FPGA价格相对较高,成本较高,适合于需要较高性能和灵活性的应用场景。

(2)资源有限:FPGA的资源有限,实现复杂的逻辑电路可能会导致资源不足的问题。

二、除法器的实现除法器是一个更为复杂的数字电路,用于实现两个二进制数的除法运算。

在FPGA中实现除法器需要使用一种称为"非冗余算法"的方法,通过迭代运算来实现除法的功能。

FPGA与CPLD 总结

CPLD(complex programable logic device)复杂可编程逻辑器件FPGA(field programable gate array)现场可编程门阵列FPGA和CPLD的逻辑单元本身的结构与SPLD相似,即与阵列和可配置的输出宏单元组成。

FPGA逻辑单元是小单元,每个单元只有1-2个触发器,其输入变量通常只有几个因而采用查找表结构(PROM形式)这样的工艺结构占用的芯片面积小,速度高(通常只有1-2纳秒),每个芯片上能集成的单元数多,但逻辑单元功能弱。

如果想实现一个较复杂的功能,需要几个这样的单元组合才能完成(总延时是各个单元延时和互连延时的和),互连关系复杂。

CPLD中的逻辑单元是单元,通常其变量数约20-28个。

因为变量多,所以只能采用PAL结构。

由于这样的单元功能强大,一般的逻辑在单元内均可实现,因而其互连关系简单,一般通过集总总线既可实现。

电路的延时通常就是单元本身和集总总线的延时(通常在数纳秒至十几纳秒),但是同样集成规模的芯片中的触发器的数量少得多。

从上面分析可知道:小单元的FPGA较适合数据型系统,这种系统所需要的触发器数多,但是逻辑相对简单;大单元的CPLD较适合逻辑型系统,如控制器等,这种系统逻辑复杂,输入变量多,但触发器需求量相对较少。

反熔丝工艺只能一次性编程,EPROM EEPROM 和FLASH工艺可以反复的编程,但是他们一经编程片内逻辑就被固定。

他们都是只读型(ROM)编程,这类编程不仅可靠性较高还可以加密。

XILINX公司的FPGA芯片采用RAM型编程,相同集成规模的芯片中的触发器数目较多,功耗低,但是掉电后信息不能保存,必须与存储器联用。

每次上电时必须先对芯片配置,然后才能使用,这似乎是RAM型PLD的缺点,但是ROM型PLD中的编程信息在使用时是不能变化的,RAM型PLD却可以在工作时更换内容,实现不同的逻辑。

CPLD和FPGA的结构,性能对照:CPLD FPGA PROM集成规模:小(最大数万门)大(最高达百万门)单元粒度:大(PAL结构)小(PROM结构)互连方式:集总总线分段总线长线专用互连编程工艺:EPROM EEPROM FLASH SRAM编程类型:ROM RAM型须与存储器联用信息:固定可实时重构触发器数:少多单元功能:强弱速度:高低222222222222222222222222222222222222延迟:确定,可以预测不能确定不能预测功耗:高低加密性能:可加密不能加密适用场合:逻辑型系统数据型系统LCA(LOGIC CELL ARRAY)逻辑单元阵列CLB(CONFIGURABLE LOGIC BLOCK)可配置逻辑模块IOB(INPUT OUTOUT BLOCK)输入输出块Spartan-xl系列FPGA的主要特性SPARTAN-XL系列的FPGA具有低压,低功耗的特点。

fpga资源评估与选型

fpga资源评估与选型

FPGA资源评估与选型

FPGA(Field Programmable Gate Array)是一种基于可编程逻辑门阵列的芯片,可以实现现场可编程的数字电路设计,因此成为了众多应用领域中重要的芯片之一。

而在进行FPGA设计时,选型和资源评估是非常重要的步骤。

选型

在进行FPGA选型时,需要考虑如下因素:

1. 功能需求:首先根据设计需要确定所需的FPGA芯片类型,如数字信号处理、网络通讯等。

2. 性能需求:对于要求高并发、高速度的应用,需要选用频率高、I/O 丰富、资源丰富的FPGA芯片。

3. 市场价格:FPGA芯片价格差异较大,需要结合项目特点和预算进行选型。

4. 厂商支持:不同厂商提供的开发工具和技术支持也是选型时需要考

虑的因素。

综合以上因素进行选型可以找到合适的FPGA芯片,并保证后续设计

的正确性和性能。

资源评估

在进行FPGA资源评估时,需要考虑如下因素:

1. 逻辑资源:确定所需的逻辑资源是评估FPGA资源的基本条件。

2. 存储资源:存储资源的大小和速度也是评估FPGA资源的重要因素。

3. I/O资源:在FPGA设计中,外部I/O资源的充足性非常重要。

4. 时序分析:考虑FPGA的时序限制和性能特点对资源的要求会更准确。

综合以上因素进行FPGA资源的评估可以评估出选型后FPGA的性能

特点,为后续的设计和开发提供参考。

在FPGA设计过程中,选型和资源评估是不可或缺的两个环节。

选型

是能否满足功能要求和成本预算,资源评估则保证设计后的可行性和性能特点,只有深入了解这两个环节才能保证FPGA设计的成功和有效。

Xilinx-FPGA配置的一些细节

Xilinx-FPGA配置的一些细节Xilinx FPGA配置的一些细节2010年07月03日星期六 14:260 参考资料(1) Xilinx: Development System Reference Guide. dev.pdf, v10.1在Xilinx的doc目录下有。

(2) Xilinx: Virtex FPGA Series Configuration and Readback. XAPP138 (v2.8) March 11, 2005在Xilinx网站上有,链接/bvdocs/appnotes/xap p138.pdf(3)Xilinx: Using a Microprocessor to Configure Xilinx FPGAs via Slave Serial or SelectMAP Mode.XAPP502 (v1.5) December 3, 2007在Xilinx网站上有,链接/bvdocs/appnotes/xap p502.pdfGTS : 激活用户IO,之前都是高阻。

EOS : 表示配置结束DCI_MATCH : 表示所有的DCI(Digitally Controlled Impedance)控制器已经把内部电阻和外部参考电阻匹配完毕。

DCM_LOCK : 表示所有的DCM已经锁定。

这个选项默认是选中的。

因此,我们可以得出如下结论:(1)FPGA最后的Startup过程有8个周期,其中DONE变高仅仅是第4个周期。

因此,在DONE 变高之后还需要再给3个CCLK。

否则DONE虽然变高了,FPGA程序并没有正确运行。

(2)ISE会在设计中搜索用户是否使用了DCI,如果是,FPGA会使用2个周期的Start Up Phase,等待DCI匹配上。

即FPGA会在那儿等待,直到DCI匹配上。

如果我们在上位机读取了配置文件,获得了文件大小,我们把它写到负责加载V4的SP3里,然后CCLK时钟就不给了。

fpga工程师年终总结

fpga工程师年终总结篇一:FPGA研发牛人心得总结FPGA研发之道FPGA是个什么玩意? FPGA是个什么玩意?首先来说:FPGA是一种器件。

其英文名 feild programable gate arry 。

很长,但不通俗。

通俗来说,是一种功能强大似乎无所不能的器件。

通常用于通信、络、图像处理、工业控制等不同领域的器件。

就像ARM、DSP等嵌入式器件一样,成为无数码农码工们情感倾泻而出的代码真正获得生命的地方。

只不过,一样的编程,却是不一样的思想。

嵌入式软件人员看到的是C。

而FPGA工程师看到是硬件描述语言,verilog或VHDL。

软件看到是函数、对象、重构。

FPGA工程师则是模块、流水、复用。

从现象上看,都是代码到下载程序再到硬件上运行。

不能只看现象而忽略本质。

FPGA 开发本质上是设计一颗IC,“**的身子,丫鬟的命”不是所有verilog/VHDL代码,都能获得青睐去流片成为真正的芯片,而更多的则成为运行在FPGA器件上,成为完成相同功能的替代品。

其实现的功能却一点也不逊色于百万身价流片的近亲。

从而成为独树一帜的行业。

FPGA开发的流程,是通过verilog/VHDL等硬件描述语言通过EDA工具编译、综合、布局布线成为下载文件,最终加载到FPGA器件中去,完成所实现的功能。

那硬件描述语言描述的是什么?这里描述的就是组合逻辑电路和时序逻辑电路。

组合逻辑电路就是大家所熟知的与门、或门、非门。

时序逻辑电路则是触发器。

数字芯片上绝大部分逻辑都是这两种逻辑实现的。

也就是基本上每个电子行业的人所学过的数字电路。

顺便说一下,感谢香农大师,在其硕士毕业论文就奠定了数字电路的的根基。

只不过在FPGA中,与或非的操作变成了查找表的操作。

于是所有的数字电路变成了查找表和寄存器,这就构成了FPGA的基础。

查找表负责逻辑实现,寄存器存储电路状态。

二者配合,双剑合璧,天衣无缝。

这是最初的FPGA的雏形。

现代FPGA内部出了查找表和寄存器之外,还有RAM块,用于存储大量的数据块,这是因为RAM块较寄存器来存储大量数据更能节省芯片实现的面积。

(完整)FPGA笔试题及答案总结,推荐文档

第 1 章 FPGA基础知识1.1 FPGA设计工程师努力的方向SOPC,高速串行I/O,低功耗,可靠性,可测试性和设计验证流程的优化等方面。

随着芯片工艺的提高,芯片容量、集成度都在增加,FPGA 设计也朝着高速、高度集成、低功耗、高可靠性、高可测、可验证性发展。

芯片可测、可验证,正在成为复杂设计所必备的条件,尽量在上板之前查出bug,将发现bug的时间提前,这也是一些公司花大力气设计仿真平台的原因。

另外随着单板功能的提高、成本的压力,低功耗也逐渐进入FPGA设计者的考虑范围,完成相同的功能下,考虑如何能够使芯片的功耗最低。

高速串行IO的应用,也丰富了FPGA 的应用范围,象xilinx的v2pro中的高速链路也逐渐被应用。

总之,学无止境,当掌握一定概念、方法之后,就要开始考虑FPGA其它方面的问题了。

1.2 简述FPGA等可编程逻辑器件设计流程系统设计电路构思,设计说明与设计划分,电路设计与输入(HDL代码、原理图),功能仿真与测试,逻辑综合,门级综合,逻辑验证与测试(综合后仿真),布局布线,时序仿真,板级验证与仿真,加载配置,在线调试。

常用开发工具(Altera FPGA)HDL语言输入:Text Editor(HDL语言输入),还可以使用Ultra Edit 原理图输入:Schematic Editor IP Core输入:MegaWinzad综合工具:Synplify/Synplify Pro,Qaustus II内嵌综合工具仿真工具:ModelSim实现与优化工具:Quartus II集成的实现工具有Assignment Editor(约束编辑器)、LogicLock(逻辑锁定工具)、PowerFit Fitter(布局布线器)、Timing Analyzer(时序分析器,STA分析工具)、Floorplan Editor(布局规划器)、Chip Editor(底层编辑器)、Design Space Explorer(设计空间管理器)、Design Assistant(检查设计可靠性)等。

FPGA芯片软核、硬核、固核知识及工作固核解析

FPGA芯片软核、硬核、固核知识及工作原理解析.一、内嵌专用硬核内嵌专用硬核是相对底层嵌入的软核而言的,指FPGA处理能力强大的硬核(Hard Core),等效于ASIC电路。

为了提高FPGA性能,芯片生产商在芯片内部集成了一些专用的硬核。

例如:为了提高FPGA的乘法速度,主流的FPGA中都集成了专用乘法器;为了适用通信总线与接口标准,很多高端的FPGA内部都集成了串并收发器(SERDES),可以达到数十Gbps的收发速度。

高端产品不仅集成了Power PC系列CPU,还内嵌了DSP Core模块,其相应的系统级设计工具是EDK和Platform Studio,并依此提出了片上系统(System on Chip)的概念。

通过PowerPC、Miroblaze、Picoblaze等平台,能够开发标准的DSP处理器及其相关应用,达到SOC的开发目的。

二、软核与硬核以及固核知识IP(Intelligent Property)核是具有知识产权核的集成电路芯核总称,是经过反复验证过的、具有特定功能的宏模块,与芯片制造工艺无关,可以移植到不同的半导体工艺中。

到了SOC阶段,IP核设计已成为ASIC电路设计公司和FPGA提供商的重要任务,也是其实力体现。

对于FPGA开发软件,其提供的IP核越丰富,用户的设计就越方便,其市场占用率就越高。

目前,IP核已经变成系统设计的基本单元,并作为独立设计成果被交换、转让和销售。

从IP核的提供方式上,通常将其分为软核、硬核和固核这3类。

从完成IP核所花费的成本来讲,硬核代价最大;从使用灵活性来讲,软核的可复用使用性最高。

1、软核软核在EDA设计领域指的是综合之前的寄存器传输级(RTL)模型;具体在FPGA设计中指的是对电路的硬件语言描述,包括逻辑描述、网表和帮助文档等。

软核只经过功能仿真,需要经过综合以及布局布线才能使用。

其优点是灵活性高、可移植性强,允许用户自配置;缺点是对模块的预测性较低,在后续设计中存在发生错误的可能性,有一定的设计风险。

毕业论文-基于FPGA数字信号音频处理总结

基于FPGA数字信号音频处理The Digital Signal Processing of audio based on FPGA摘要:目前,随着电子技术的快速发展人们对MP3多媒体播放器、DVD音频唱盘、Iphone等的音质、体积、功耗和处理速度有了更多更高要求。

因此现在数字音频处理技术已经逐渐取代模拟音频处理技术,并且得到了迅速的普及应用。

音频处理的数字化是利用数字滤波算法对采集的音频信号进行变换处理来实现,对此在本文中介绍了数字滤波器的一些算法。

傅里叶变换(DFT)作为其数字信号处理中的基本运算,发挥着重要作用。

特别是可快速傅里叶变换换(FFT)算法的提出,减少了当N很大的时候DFT的运算量,使得数字信号处理的实现与应用变得更加容易。

由于快速傅里叶变换算法在实际中得到了广泛应用,毕业设计给出了基-2FFT原理、讨论了按时间抽取FFT算法的特点。

本文主要探讨了基于FPGA数字信号音频处理的理论与实现,涉及到了其结构与设计流程、硬件描述语言(VHDL)、Quartus II软件、音频录放、DE2开发板介绍等等。

关键词:音频处理技术、数字滤波、算法、FPGAAbstractAt present,with the rapid development of the electronic technology,people have many higher requirements such as sound quality,volume,power waste and processing speed to the MP3 multimedia,DVD audio disc,Iphone and so on.So nowadays,the analog audio processing technology is replaced gradually by the digital audio processing technology,and digital audio processing technology has a chance to become common and widely used.The audio processing digitization is using the digital filter algorithm to sample.In the part of this passage there are some introduction about the digital filter algorithm. DFT plays an important part in digital signal processing as a basic calculation.Especially,FFT algorithm reduces the calculation quantity when N is a little great ,which makes it much easier for implement and application.As the fast Fourier transform algorithm in practice to a wide range of applications,radix-2 FFT theory has been given out and the characteristic of DIT FFT are discussed in the design of graduation.The passage mainly probes into the theories and realization of the digital signal processing of audio based on FPGA(Field Programmable Gate Array),including its structure and processing of design.It also contains VHDL,Quartus II software ,audio record and broadcast,introduction of DE2 study board and so on.Keywords:audio processing technology、digital filter、algorithm、FPGA前言第一章绪论1.1音频处理技术概述在科技飞速发展的数字化时代,数字音频技术是数字信号处理中应用最为广泛的数字技术之一。

FPGA,学习心得体会

篇一:fpga学习心得大报告《fpga技术基础》学习报告--课程内容学习心得姓名:学号:年级专业:指导教师:瞿麟 201010401128 自动化101薛小军摘要从开始学fpga到现在粗略算来的话,已经有3个多月了,就目前而言,我并不确定自己算不算高手们所说的入门了,fpga学习总结。

但是不管现在的水平如何,现在就总结一下自己学习它的感受或一些认识吧。

关键词fpga de2板 quartusii软件 verilog语言引言fpga是什么?fpga现状?怎样学习fpga?fpga是现场可编程门阵列的简称,fpga的应用领域最初为通信领域,但目前,随着信息产业和微电子技术的发展,可编程逻辑嵌入式系统设计技术已经成为信息产业最热门的技术之一,应用范围遍及航空航天、医疗、通讯、网络通讯、安防、广播、汽车电子、工业、消费类市场、测量测试等多个热门领域。

并随着工艺的进步和技术的发展,向更多、更广泛的应用领域扩展。

越来越多的设计也开始以asic转向fpga, fpga正以各种电子产品的形式进入了我们日常生活的各个角落。

正文(1)掌握fpga的编程语言在学习一门技术之前我们往往从它的编程语言开始,如同学习单片机一样,我们从c语言开始入门,当掌握了c语言之后,开发单片机应用程序也就不是什么难事了。

学习fpga也是如此,fpga的编程语言有两种:vhdl和verilog,这两种语言都适合用于fpga的编程。

(2)fpga实验尤为重要除了学习编程语言以外,更重要的是实践,将自己设计的程序能够在真正的fpga里运行起来,这时我们需要选一块板子进行实验,我们选择使用de2板才进行试验。

初识de2开发板de2的资源de2的资源非常丰富,包括1. 核心的fpga芯片-cyclone ii 2c35 f672c6,从名称可以看出,它包含有35千个le,在altera的芯片系列中,不算最多,但也绝对够用。

altera下载控制芯片- epcs16以及usb-blaste对jtag的支持。

可编程逻辑器件(FPGA)在集成电路中的应用

可编程逻辑器件(FPGA)在集成电路中的应用可编程逻辑器件(FPGA)是一种集成电路(IC)的设计工具,具有可重构和可编程的特性。

它可以在硬件级别上重新配置其内部逻辑功能,使其能够执行特定任务。

FPGA在集成电路设计和应用中扮演着重要的角色,广泛应用于各个领域。

一、FPGA的基本结构与工作原理FPGA由大量的逻辑门、寄存器、RAM和其他数字电路组成。

其核心部分是可编程逻辑单元(PLU),它由可编程逻辑阵列(CLA)组成,每个逻辑单元都包含一个查找表(LUT),用于实现逻辑功能。

通过配置寄存器和LU以及将内部信号路由到特定的输入/输出引脚,可以将FPGA定制为特定的电路。

FPGA利用静态随机存取存储器(SRAM)来保存逻辑配置信息。

在每次启动时,FPGA首先将配置信息从外部存储器加载到内部SRAM中,然后根据配置信息将内部逻辑电路重新组织和重连。

该重组过程称为配置。

一旦FPGA被配置完成,它就开始执行特定的任务。

二、FPGA的应用领域1. 数字信号处理(DSP):FPGA在DSP领域中的应用十分广泛。

它可以执行数字滤波、图像处理、高速数据转换和算法加速等任务。

由于其可以快速重配置的特性,FPGA在需要快速响应和高度并行处理的应用中具有很大的优势。

2. 通信与网络:FPGA在通信与网络领域中有着重要的作用。

它可以实现各种通信协议的编解码、信号调制与解调、协议转换以及高速数据处理等功能。

在网络设备中,FPGA通常被用于数据包处理、流量控制和数据路由等任务。

3. 图像与视频处理:FPGA在图像与视频处理中也发挥着重要的作用。

它可以实现图像和视频的实时处理、编解码、图像增强、视频合成和视频传输等功能。

在高清视频和虚拟现实应用中,FPGA被广泛应用于图像和视频数据的高效处理。

4. 工业控制与自动化:FPGA在工业控制与自动化领域中的应用十分广泛。

它可以实现实时数据采集、传感器信号处理、运动控制和逻辑控制等任务。

FPGA开发全攻略——配置电路

FPGA开发全攻略——配置电路展开全文配置电路FPGA配置方式灵活多样,根据芯片是否能够自己主动加载配置数据分为主模式、从模式以及JTAG模式。

典型的主模式都是加载片外非易失( 断电不丢数据) 性存储器中的配置比特流,配置所需的时钟信号( 称为CCLK) 由FPGA内部产生,且FPGA控制整个配置过程。

从模式需要外部的主智能终端( 如处理器、微控制器或者DSP等) 将数据下载到FPGA中,其最大的优点就是FPGA 的配置数据可以放在系统的任何存储部位,包括:Flash、硬盘、网络,甚至在其余处理器的运行代码中。

JTAG 模式为调试模式,可将PC 中的比特文件流下载到FPGA中,断电即丢失。

此外,目前赛灵思还有基于Internet 的、成熟的可重构逻辑技术System ACE解决方案。

(1) 主模式在主模式下,FPGA上电后,自动将配置数据从相应的外存储器读入到SRAM中,实现内部结构映射;主模式根据比特流的位宽又可以分为:串行模式( 单比特流) 和并行模式( 字节宽度比特流) 两大类。

如:主串行模式、主SPI Flash 串行模式、内部主SPI Flash串行模式、主BPI 并行模式以及主并行模式,如图5-19所示。

(2) 从模式在从模式下,FPGA 作为从属器件,由相应的控制电路或微处理器提供配置所需的时序,实现配置数据的下载。

从模式也根据比特流的位宽不同分为串、并模式两类,具体包括:从串行模式、JTAG模式和从并行模式三大类,其概要说明如图5-20所示。

(3)JTAG模式在JTAG模式中,PC和FPGA通信的时钟为JTAG接口的TCLK,数据直接从TDI进入FPGA,完成相应功能的配置。

图5-19 常用主模式下载方式示意图图5-20 常用的从模式下载方式示意图目前,主流的FPGA芯片都支持各类常用的主、从配置模式以及JTAG,以减少配置电路失配性对整体系统的影响。

在主配置模式中,FPGA自己产生时钟,并从外部存储器中加载配置数据,其位宽可以为单比特或者字节;在从模式中,外部的处理器通过同步串行接口,按照比特或字节宽度将配置数据送入FPGA芯片。

用CPLD和Flash实现FPGA配置

用CPLD和Flash实现FPGA配置CPLD(复杂可编程逻辑器件)和Flash(闪存)是FPGA(现场可编程逻辑门阵列)的两种基本配置方式。

FPGA的配置是指将存储在Flash中的逻辑代码加载到FPGA中的过程。

这篇文档将着重介绍使用CPLD和Flash实现FPGA配置。

FPGA是一种现场可编程逻辑门阵列,它可以灵活地实现各种逻辑电路和数字信号处理。

FPGA芯片本身没有内置的逻辑代码,需要通过配置方式在启动时加载逻辑代码。

一般情况下,常用的FPGA配置方式有三种:JTAG、ICAP和CFI(常规闪存接口)。

JTAG配置方式适用于小容量的FPGA芯片,ICAP适用于大容量的FPGA芯片,CFI则是将配置位流存储在外部Flash中,再通过FPGA芯片上的配置接口进行加载。

在CFI配置方式中,外部Flash存储了FPGA芯片需要的逻辑代码,但是芯片本身无法直接访问Flash。

因此,需要一个额外的器件来控制FPGA芯片加载逻辑代码。

这个额外的器件就是CPLD,它是一种用于实现特定逻辑功能的可编程逻辑器件。

使用CPLD和Flash实现FPGA配置相比较其他配置方式,具有以下优点:1. CPLD控制FPGA芯片的配置方式,可以实现更快的配置速度和更高的配置可靠性。

2. 配置电路简单,特别适用于单片机控制的系统。

3. 执行速度快,且机器启动速度较快。

4. 具有较高的适用性和兼容性,因为复杂逻辑的实现可以通过FPGA来实现。

在使用CPLD和Flash实现FPGA配置时,需要按照以下步骤进行:1. 将实现逻辑电路的设计文件编译成位流文件(.bit)。

2. 将位流文件存储到Flash中。

3. 将芯片时钟和复位信号连接到CPLD器件引脚上,连接Flash引脚到CPLD器件的S端口上,连接FPGA的配置引脚到CPLD器件的D端口上。

4. 将CPLD引脚连接到单片机或处理器的端口上,控制CPLD进行FPGA配置。

需要注意的是,在使用CPLD和Flash实现FPGA配置时,需要正确选择CPLD和Flash芯片的型号和参数,以确保它们可以适配FPGA芯片并满足配置速度和兼容性的要求。

fpga配置芯片

fpga配置芯片FPGA(Field-Programmable Gate Array)是一种灵活可编程的芯片,可以通过配置来实现不同的电路功能。

它拥有矩阵式的可编程逻辑单元(PLU)和可编程的连线资源(Interconnect)。

配置芯片是将特定的逻辑电路输出信号烧录到FPGA内部的存储器中,使其在运行时能够按照所需的功能来工作。

FPGA配置芯片的过程主要包括以下几个步骤:1. 设计和编写硬件描述语言(HDL)代码:首先,需要使用HDL语言(如Verilog、VHDL)来描述所需的逻辑电路功能。

HDL代码可以分为结构化编程和行为编程两种方式,具体编写的内容包括输入输出端口的定义、逻辑门的连接等。

2. 仿真和验证设计:在进行配置芯片之前,需要使用仿真工具对HDL代码进行验证,确保设计的正确性。

通过仿真可以检查逻辑电路是否按照预期工作,并可以进行调试和优化。

3. 合成:合成是将HDL代码转换为实际的逻辑电路的过程。

合成工具将HDL代码进行优化和转换,生成一个包含逻辑门和连线的网络表示。

4. 实现:在实现过程中,将逻辑网进行布局和布线,将逻辑门放置在FPGA芯片的逻辑单元中,并将它们之间的连线连接起来。

布局是指确定逻辑门在FPGA芯片上的位置,布线是指将逻辑门之间的连接线路连接起来,确保信号能够正确传输。

5. 生成比特流文件:配置芯片的最后一步是将实现的电路转化为比特流文件。

这些文件包含了逻辑门和连线的配置信息,以及其他必要的控制信号等。

6. 下载比特流文件:最后,在配置芯片的时候,需要将比特流文件下载到FPGA芯片的内存中。

下载可以通过专用的下载线缆或者其他接口来进行。

FPGA配置芯片的优点是它的可编程性和灵活性。

通过重新配置FPGA芯片,可以实现不同的电路功能,极大地提高了开发和测试的效率。

同时,FPGA配置芯片还可以减少硬件设计的成本和时间,并且能够快速响应市场需求的变化。

总的来说,FPGA配置芯片是将特定的逻辑电路功能烧录到FPGA芯片中的过程,它通过硬件描述语言的编写和优化、仿真和验证设计、合成、实现、生成比特流文件和下载等步骤来完成。

FPGA综述报告

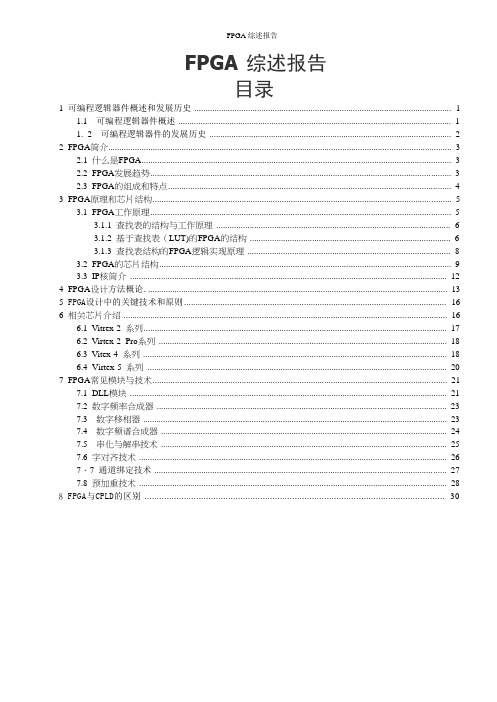

FPGA综述报告FPGA 综述报告目录1可编程逻辑器件概述和发展历史 (1)1.1 可编程逻辑器件概述 (1)1. 2 可编程逻辑器件的发展历史 (2)2 FPGA简介 (3)2.1 什么是FPGA (3)2.2 FPGA发展趋势 (3)2.3 FPGA的组成和特点 (4)3 FPGA原理和芯片结构 (5)3.1 FPGA工作原理 (5)3.1.1 查找表的结构与工作原理 (6)3.1.2 基于查找表(LUT)的FPGA的结构 (6)3.1.3 查找表结构的FPGA逻辑实现原理 (8)3.2 FPGA的芯片结构 (9)3.3 IP核简介 (12)4 FPGA设计方法概论 (13)5 FPGA设计中的关键技术和原则 (16)6 相关芯片介绍 (16)6.1 Vitrex-2 系列 (17)6.2 Virtex-2 Pro系列 (18)6.3 Vitex-4 系列 (18)6.4 Virtex-5 系列 (20)7 FPGA常见模块与技术 (21)7.1 DLL模块 (21)7.2 数字频率合成器 (23)7.3 数字移相器 (23)7.4 数字频谱合成器 (24)7.5 串化与解串技术 (25)7.6 字对齐技术 (26)7.7通道绑定技术 (27)7.8 预加重技术 (28)8 FPGA与CPLD的区别 (30)FPGA综述报告1 可编程逻辑器件概述和发展历史1.1 可编程逻辑器件概述可编程逻辑器件(Programmable Logic Device,PLD)起源于20 世纪70 年代,是在专用集成电路(ASIC)的基础上发展起来的一种新型逻辑器件,是当今数字系统设计的主要硬件平台,其主要特点就是完全由用户通过软件进行配置和编程,从而完成某种特定的功能,且可以反复擦写。

在修改和升级PLD 时,不需额外地改变PCB 电路板,只是在计算机上修改和更新程序,使硬件设计工作成为软件开发工作,缩短了系统设计的周期,提高了实现的灵活性并降低了成本,因此获得了广大硬件工程师的青睐,形成了巨大的PLD 产业规模。

FPGA的配置引脚说明

FPGA是基于SRAM编程的,编程信息在系统掉电时会丢失,每次上电时,都需要从器件外部的FLASH或EEPROM中存储的编程数据重现写入内部的SRAM中。

FPGA在线加载需要有CPU的帮助,并且在加载前CPU已经启动并工作。

FPGA的加载模式主要有以下几种:1). PS 模式(P assive Serial Con figuration Mode)即被动串行加载模式。

PS模式适合于逻辑规模小,对加载速度要求不高的FPGA加载场合。

在此模式下,加载所需的配置时钟信号CCLK由FPGA外部时钟源或外部控制信号提供。

另外,PS加载模式需要外部微控制器的支持。

2).AS 模式(Active Serial Con figuration Mode),即主动串行加载模式。

在AS模式下,FPGA主动从外部存储设备中读取逻辑信息来为自己进行配置,此模式的配置时钟信号CCLK由FPGA内部提供。

3).PP 模式(Passive Parallel Configuration Mode,即被动并行加载模式。

此模式适合于逻辑规模较大,对加载速度要求较高的FPGA加载场合。

PP模式下,外部设备通过8bit并行数据线对FPGA进行逻辑加载,QCLK信号由外部提供。

4).BS 模式(Bou ndary Sca n Con figuratio n Mode),即边界扫描加载模式。

也就是我们通常所说的JTAG加载模式。

所有的FPGA芯片都有三个或四个加载模式配置管脚,通过配置MESL[0..3]来选取不同的加载模式。

首先来介绍下PS加载模式,各个厂商FPGA产品的PS加载端口定义存在一些差异,目前主流的三个FPGA厂商Altera, Xilinx,Lattice的PS加载方式进行一一介绍。

Altera公司的FPGA产品PS加载接口如下图所示。

nSTATUS1).C0NFIG_D0NE :加载完成指示输出信号,I/O接口,高有效,实际使用中通过4.7K电阻上拉到VCC,使其默认状态为高电平,表示芯片已加载完毕,当FPGA正在加载时,会将其驱动为低电平。

FPGA和ASIC比较谈

ASIC与FPGA比较谈专用集成电路(ASIC)采用硬接线的固定模式,而现场可编程门阵列(FPGA)则采用可配置芯片的方法,二者差别迥异。

可编程器件是目前的新生力量,混合技术也将在未来发挥作用。

与其他技术一样,有关ASIC技术过时的报道是不成熟的。

新的ASIC产品的数目可能有大幅度下降,但其销售额仍然相当高,尤其是在亚太区。

此外,采用混合式方法,如结构化ASIC,也为该技术注入了新的活力。

同时,FPGA(和其他可编程逻辑器件)也在发挥作用,赢得了重要的大众市场,并从低端应用不断向上发展。

每种技术都有它的支持者。

一般来说,ASIC用于大型项目,而对于需要快速投放市场且支持远程升级的小型项目,FPGA则更为适合。

ASIC和FPGA供应商对这两种技术孰优孰劣不能达成共识,对适合的应用领域也持不同看法。

上述技术及其衍生技术将可能在今后一段时间内长期存在。

Altera Corp的高密度FPGA高级总监David Greenfield指出,FPGA技术的主要优势仍是产品投放市场的时间较短。

他说:“在目前新增的设计方案中,对FPGA的选择倾向超过ASIC。

ASIC技术有其价值所在,它的性能、密度和单位容量都相当出色,不过随着FPGA的发展和ASIC的开发成本不断上升,将会导致ASIC的市场份额不断缩小。

”在上述趋势之后发挥作用的,正是FPGA在性能、密度和制造成本上的发展。

Greenfield指出,高性能曾经是ASIC超出FPGA的优势,当时FPGA在性能和功能上都较逊色。

随着芯片的制造工艺从180nm发展到130nm甚至90nm,上述情况发生了很大变化,现在FPGA的性能已经能够满足大多数应用的需要(要求最高的应用除外),而密度水平则达到逻辑设计的80%。

他解释说:“某些系统设计师也认识到,ASIC的市场领域在于极高性能/密度的产品,这种市场领域风险非常大。

NRE (非重复性工程设计)和开发成本对这种设备而言是最高的。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

F PG A配置芯片的网上汇总较杂需自己总结公司标准化编码 [QQX96QT-XQQB89Q8-NQQJ6Q8-MQM9N]FPGA配置芯片FPGA器件有三类配置下载方式:主动配置方式(AS)和被动配置方式(PS)和最常用的(JTAG)配置方式。

AS由FPGA器件引导配置操作过程,它控制着外部存储器和初始化过程,EPCS系列.如EPCS1,EPCS4配置器件专供AS模式,目前只支持Cyclone系列。

使用Altera串行配置器件来完成。

Cyclone期间处于主动地位,配置期间处于从属地位。

配置数据通过DATA0引脚送入 FPGA。

配置数据被同步在DCLK输入上,1个时钟周期传送1位数据。

(见附图)PS则由外部计算机或控制器控制配置过程。

通过加强型配置器件(EPC16,EPC8,EPC4)等配置器件来完成,在PS配置期间,配置数据从外部储存部件,通过DATA0引脚送入FPGA。

配置数据在DCLK上升沿锁存,1个时钟周期传送1位数据。

(见附图)JTAG接口是一个业界标准,主要用于芯片测试等功能,使用IEEE Std 联合边界扫描接口引脚,支持JAM STAPL标准,可以使用Altera下载电缆或主控器来完成。

FPGA在正常工作时,它的配置数据存储在SRAM中,加电时须重新下载。

在实验系统中,通常用计算机或控制器进行调试,因此可以使用PS。

在实用系统中,多数情况下必须由FPGA主动引导配置操作过程,这时FPGA将主动从外围专用存储芯片中获得配置数据,而此芯片中fpga配置信息是用普通编程器将设计所得的pof格式的文件烧录进去。

专用配置器件:epc型号的存储器?常用配置器件:epc2,epc1,epc4,epc8,epc1441(现在好象已经被逐步淘汰了)等?对于cyclone cycloneII系列器件,ALTERA还提供了针对AS方式的配置器件,EPCS系列.如EPCS1,EPCS4配置器件也是串行配置的.注意,他们只适用于cyclone系列.除了AS和PS等单BIT配置外,现在的一些器件已经支持PPS,FPS等一些并行配置方式,提升配置了配置速度。

当然所外挂的电路也和PS有一些区别。

还有处理器配置比如JRUNNER 等等,如果需要再baidu 吧,至少不下十种。

比如Altera公司的配置方式主要有Passive Serial(PS),Active Serial(AS),Fast Passive Parallel(FPP),Passive Parallel Synchronous(PPS),Passive ParallelAsynchronous(PPA),Passive Serial Asynchronous(PSA),JTAG等七种配置方式,其中Cyclone支持的配置方式有PS,AS,JTAG三种.对FPGA芯片的配置中,可以采用AS模式的方法,如果采用EPCS的芯片,通过一条下载线进行烧写的话,那么开始的"nCONFIG,nSTATUS"应该上拉,要是考虑多种配置模式,可以采用跳线设计。

让配置方式在跳线中切换,上拉电阻的阻值可以采用10K在PS模式下tip:如果你用电缆线配置板上的FPGA芯片,而这个FPGA芯片已经有配置芯片在板上,那你就必须隔离缆线与配置芯片的信号.(祥见下图).一般平时调试时不会把配置芯片焊上的,这时候用缆线下载程序.只有在调试完成以后,才把程序烧在配置芯片中, 然后将芯片焊上.或者配置芯片就是可以方便取下焊上的那种.这样出了问题还可以方便地调试.在AS模式下tip: 用过一块板子用的AS下载,配置芯片一直是焊在板子上的,原来AS方式在用线缆对配置芯片进行下载的时候,会自动禁止对FPGA的配置,而PS方式需要电路上隔离。

一般是用jtag配置epc2和flex10k,然后 epc2用ps方式配置flex10k.这样用比较好.(这是我在网上看到的,可以这样用吗怀疑中)望达人告知.下载电缆,Altera下的下载电缆分为byteblaster和byteblasterMV,以及ByteBlaster II,现在还推出了基于USB-blaster.由于BB基本已经很少有人使用,而USB-Blaster现在又过于昂贵,这里就说一下BBII 和 BBMV的区别.BBII支持多电压供电,,,;BBII支持三种下载模式:AS,可对Altera的As串行配置芯片(EPCS系列)进行编程?PS,可对FPGA进行配置?JTAG,可对FPGA,CPLD,即Altera配置芯片(EPC系列)编程而BBMV只支持PS和JTAG6,一般在做FPGA实验板,(如cyclone系列)的时候,用AS+JTAG方式,这样可以用JTAG方式调试,而最后程序已经调试无误了后,再用 AS模式把程序烧到配置芯片里去,而且这样有一个明显的优点,就是在AS模式不能下载的时候,可以利用Quartus自带的工具生成JTAG模式下可以利用jic文件来验证配置芯片是否已经损坏,方法祥见附件.的FPGA可以通过单片机,CPLD等加以配置,主要原理是满足datasheet中的时序即可,这里我就不多说了,有兴趣的朋友可以看看下面几篇文章,应该就能够明白是怎么回事了.8.配置时,quartus软件操作部分:(1).assignment-->device-->device&pin options-->选择configuration scheme,configuaration mode,configuration device,注意在不支持远程和本地更新的机器中configuration mode不可选择,而configuration device中会根据不同的配置芯片产生pof文件,如果选择自动,会选择最小密度的器件和适合设计?(2).可以定义双口引脚在配置完毕后的作用,在刚才的device&pin option-->dual-purpose pins-->,可以在配置完毕后继续当I/O口使用(3).在general菜单下也有很多可钩选项,默认情况下一般不做改动,具体用法参见altera configuration handbook,volume2,sectionII.(4)关于不同后缀名的文件的适用范围:sof(SRAM Object File)当直接用PS模式下将配置数据下到FPGA里用到,USBBLASTER,MASTERBLASER,BBII,BBMV适用,quartusII会自动生成,所有其他的配置文件都是由sof生成的. pof(Programmer Object File)也是由quartusII自动生成的,BBII适用,AS模式下将配置数据下到配置芯片中?rbf(Raw Binary File)用于微处理器的二进制文件.在PS,FPP,PPS,PPA配置下有用处?rpd(Raw Programing Data File)包含bitstream的二进制文件,可用AS模式配置,只能由pof文件生成? hex(hexadecimal file)这个就不多说了,单片机里很多?ttf(Tabular Text File)适用于FPP,PPS,PPA,和bit-wide PS配置方式?sbf(Serial Bitstream File)用PS模式配置Flex 10k和Flex6000的?jam(Jam File)专门用于program,verigy,blank-checkFPGA配置方式和配置器件介绍配置,就是对FPGA的内容进行编程的一个过程。

在一般的应用中,都是选择用Altera的配置芯片配合完成配置过程。

在Altera的产品中,可以根据FPGA在整个配置过程的角色,可以分为3类:FPGA主动方式(AS);FPGA被动方式(PS);JTAG方式。

在FPGA主动方式下(以下简称AS),由板上的FPGA主动输出输出控制和同步信号给Altera专用的一种串行配置芯片(如EPCS1等),在配置芯片收到命令后,就把配置芯片数据发到FPGA,完成配置过程。

注意:该方式只能与Altera提供的主动串行配置芯片配合使用(即EPCS系列),该配置方式只有在Stratix II系列和Cyclone系列(包括I,II,III代)中使用。

在FPGA被动方式下,由系统的其他设备发起并控制配置过程。

这些设备包括Altera的配置芯片(EPC系列),或者是微控制器(如单片机),CPLD等。

FPGA完全处于被动地位,只是简单的输出一些状态信号配合配置过程。

在FPGA被动方式中,包括被动串行(PS),快速被动并行(FPP),被动并行同步(PPS),被动并行异步(PPA)等。

我们主要介绍一下最常用的,具有代表性的PS模式。

PS模式是所有Altera FPGA都支持的,一般最常见的是用Altera的配置芯片EPC系列来完成配置过程。

在做PS配置时,FPGA配置数据从存储器(一般是EPC系列)里读出,在时钟的上升沿到来时降数据打入FPGA。

JTAG是IEEE 边界扫描测试的标准接口,主要用于芯片的测试等功能。

Altera FPGA基本上都支持由JTAG命令来配置FPGA的方式,而且JTAG的配置方式比其他任何一种配置方式都高级。

不同的Altera FPGA系列所支持的配置方式:?下面介绍下配置芯片:Altera的配置芯片可以分为以下三种:1.增强型配置器件:EPC16,EPC8,EPC42. AS串行配置器件:EPCS64,EPCS16,EPCS4和EPCS1 3.普通配置器件:EPC2,EPC1和EPC1441如下是各个配置芯片的属性:增强型配置器件:AS串行配置器件:普通配置器件:?增强型配置器件可以支持对大容量FPGA单元的配置,可以由JTAG接口进行在线系统编程(ISP)普通配置器件容量较小,其中只有EPC2具有可重复编程的特点。

AS配置芯片是专为为Stratix II,Cyclone系列(包括I,II,III代)设计的单片、低成本的配置芯片,可以由下载电缆进行可重复编程。

漫谈xilinx FPGA 配置电路这里要谈的时xilinx的spartan-3系列FPGA的配置电路。

当然了,其它系列的FPGA配置电路都是大同小异的,读者可以类推,重点参考官方提供的datasheet,毕竟那才是最权威的资料。

这里特权同学只是结合自己的理解,用通俗的语言作一点描述。

所谓典型,这里要列出一个市面上最常见的spartan-3的xc3s400的配置电路。

所有spartan-3的FPGA配置电路的链接方式都是一样的。

Xc3s400是40万门FPGA,它的ConfigurationBitstream虽然只有,但是它还是需要2Mbit的配置芯片XCF02S,不能想当然的以为我的设计简单,最多用到1Mbit,那么我选XCF01S(1Mbit)就可以了。