allegro等长设置总结.doc

Allegro16.6设置等长规则

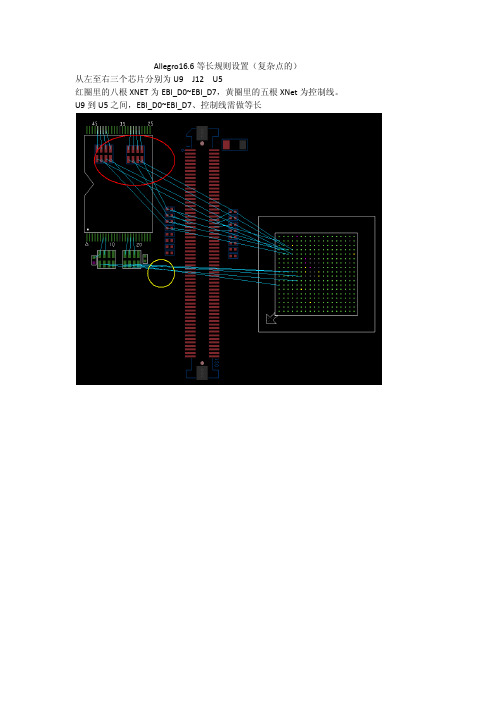

Allegro16.6等长规则设置(复杂点的)从左至右三个芯片分别为U9 J12 U5红圈里的八根XNET为EBI_D0~EBI_D7,黄圈里的五根XNet为控制线。

U9到U5之间,EBI_D0~EBI_D7、控制线需做等长多出来的八根XNET为EBI_D8~EBI_D15J12到U5之间EBI_D0‐ EBI_D15做等长接下来开始步骤:(设模型、X‐NET就不说啦,坛子里有很多说的挺清楚的)将EBI_D0~EBI_D15设为一个Class,EBI_D将EBI_D0~EBI_D15设PINPAIREBI_D0~EBI_D7设置两组PINPAIREBI_D8~EBI_D15设置一组PINPAIR设EBI_D0 拓扑Set‐Constraint红框中填好点ADD再新增另一个规则点ADD点OK后回到以下界面,FILE‐Update Constraint Manager点是出现两组MGrp,每组下面只出现一对,因为仅对EBI_D0设了规则。

EBI_D0和EBI_D1~D7的拓扑一样的,将刚才生成的ElecCset赋予它们赋予它们的同时,两组MGrp里的PPr也在增多但EBI_D8~D15的拓扑和它们不一样,所以得重新建拓扑设规则省略几步,和之前设的时候一样的点是,可以看到EBI_D8被赋予规则EBI_D8,EBI_D9~D15拓扑与EBI_D8一样的,所以把EBI_D8这一规则分别赋予它们。

目前为止,EBI_D0~D15从U5到J12就做了等长,走线时就有控制进度条显示但是从U5到U9这一段还有几根控制线未加进来找到这几根控制线,add to MatchGroupEBINAND这一MatchGroup里就有这些XNET了。

红色框中选择ALL DRIVERS..红色框中改为0mil:100milU9到U5之间,EBI_D0~EBI_D7、控制线就做好等长啦、这种设等长的方式思路挺清晰的,所以就推荐给大家,或者是给还不会设等长的一点参考。

allegro中 Xnet概念和Xnet等长设置

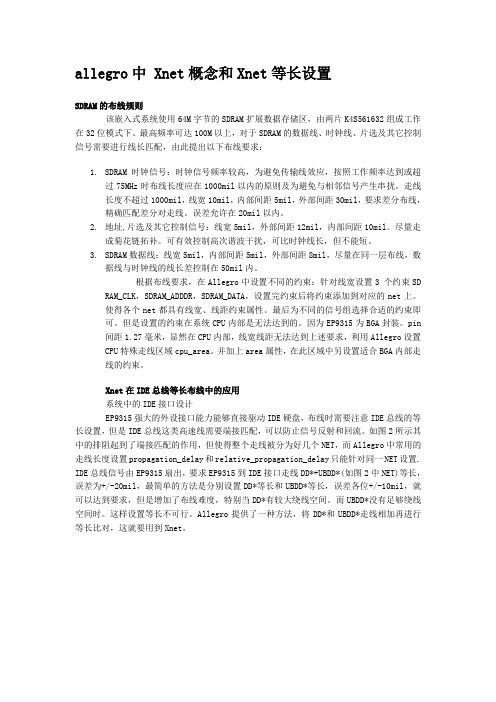

allegro中 Xnet概念和Xnet等长设置SDRAM的布线规则该嵌入式系统使用64M字节的SDRAM扩展数据存储区,由两片K4S561632组成工作在3 2位模式下。

最高频率可达100M以上,对于SDRAM的数据线、时钟线、片选及其它控制信号需要进行线长匹配,由此提出以下布线要求:1.SDRAM时钟信号:时钟信号频率较高,为避免传输线效应,按照工作频率达到或超过75MHz时布线长度应在1000mil以内的原则及为避免与相邻信号产生串扰。

走线长度不超过1000mil,线宽10mil,内部间距5mil,外部间距30mil,要求差分布线,精确匹配差分对走线。

误差允许在20mil以内。

2.地址,片选及其它控制信号:线宽5mil,外部间距12mil,内部间距10mil。

尽量走成菊花链拓补。

可有效控制高次谐波干扰,可比时钟线长,但不能短。

3.SDRAM数据线:线宽5mil,内部间距5mil,外部间距8mil,尽量在同一层布线,数据线与时钟线的线长差控制在50mil内。

根据布线要求,在Allegro中设置不同的约束:针对线宽设置3 个约束SDRAM _CLK,SDRAM_ADDDR,SDRAM_DATA,设置完约束后将约束添加到对应的net上。

使得各个net都具有线宽、线距约束属性。

最后为不同的信号组选择合适的约束即可。

但是设置的约束在系统CPU内部是无法达到的。

因为EP9315为BGA封装。

pin间距1.27毫米,显然在CPU内部,线宽线距无法达到上述要求,利用Allegro设置CPU特殊走线区域cpu_area。

并加上area属性,在此区域中另设置适合BGA内部走线的约束。

Xnet在IDE总线等长布线中的应用系统中的IDE接口设计EP9315强大的外设接口能力能够直接驱动IDE硬盘,布线时需要注意IDE总线的等长设置,但是IDE总线这类高速线需要端接匹配,可以防止信号反射和回流。

如图2所示其中的排阻起到了端接匹配的作用,但使得整个走线被分为好几个NET,而Allegro中常用的走线长度设置propagation_delay和relative_propagation_delay只能针对同一NET设置.I DE总线信号由EP9315扇出,要求EP9315到IDE接口走线DD*+UBDD*(如图2中NET)等长,误差为+/-20mil,最简单的方法是分别设置DD*等长和UBDD*等长,误差各位+/-10mil,就可以达到要求,但是增加了布线难度,特别当DD*有较大绕线空间。

Allegro中等长设置方法

创建模型:

如果排阻PinNumber顺序是这样的,则:

注:Pin Number与Pin Number之间有空格

创建模型:

d)完成模型设置后,查看这个排阻的Net属性,在Net name下面会多 一个Net名字,这表示Xnet已经创建好了。

导入PACAGE长度:

1、File->Import->Pin Delay:

2、Pin Delay File是芯片厂提供的 文件,因没有这一文件,暂时没法演示。

等长规则应用:

i)完成的效果,如下图:

总结

这是通过模型来设置等长规则的一种 方法,如果Xnet已经创建好了,则在 Constraint Manager一样可以设置,会 更方便,之所以提出这种方法,只是多 一种选择,当匹配比较复杂的时候,模 型创建就相对复杂

设置等长规则:

设置等长规则:

设置等长规则:

c)选择菜单Set->Constraints,出现如下窗体:

设置等长规则:

Rule Name:等长规则名字,这里可以随便输入,不过最好方便辨认 From:开始Pin To:结束Pin Scope:规则适应范围

Local:适用本网络 Global:适用所有网络 Bus:适用所在Bus Class: 适用所在Class Delta Type:Delta匹配类型,Delta为与基准线对比值,如果一组线要 求等长,我们可以把Delta设为None,或把Delta值设为0 Delay: 延迟 Length:长度,一般都设长度 Delta: 设定值 Tol Type: 误差类型 Tolerance: 误差范围。

f)在Constraint Manager中就有更新提示:

allegro等长设置总结.doc

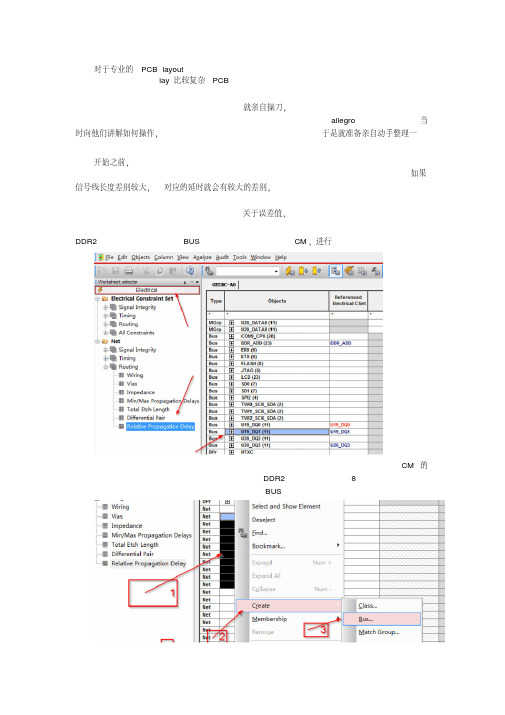

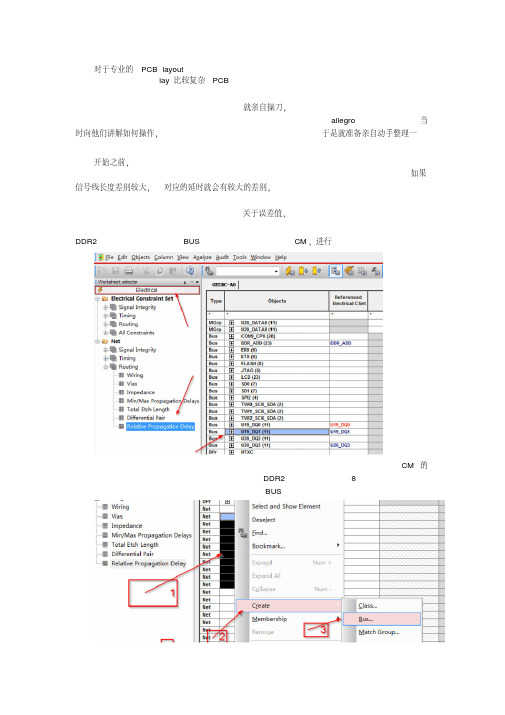

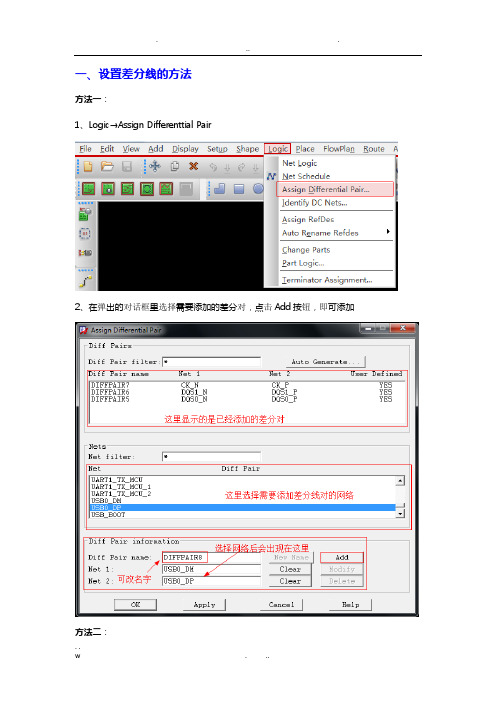

对于专业的PCB layoutlay比较复杂PCB就亲自操刀,allegro当时向他们讲解如何操作,于是就准备亲自动手整理一开始之前,如果信号线长度差别较大,对应的延时就会有较大的差别,关于误差值,DDR2BUS CM,进行CM的DDR28BUS选中信号---右键选择create---BUSBUS OK BUSBUSBUSBUS BUS1.BUS SiXplorer…2.3.1Rel Prop Delayrule name From和ToFrom和To.Delta和Tolerance就是误差长度,如0mil和25mil,50mil,信号线和参考基准信号线25milAdd—Apply—OK.CM File---update CM.constraint manager.1.回到CM rule nameBUS name的MGrp2.MGrp的name,右键analyzelength,升序or降序,1.delay tune2.1.BUS中的信号的模型不一样,如MGrp2.BUS rule name建的rule name MGrp 关于XnetXnetXnet1.Analyze>SI/EMI Sim>Model…DC net,直接YesModel2.model Detype value/refdes3.点选create mode…4.okModenameCircuit typeSingle pins116pin,就连着,接着215相当于另一个电阻…pin number之间用空格隔开,如1和1616和22和15之间…net的property Member of XNet:…XnetPin Pair1.在BUS create---pin pairok net pin pair netppr pin pair2.match group MGrp BUS中所有的ppr,右键create...membership3.MGrp就ok4.set target有时,Pin pin type,pin type,pin pair1,Edit>Properties…2,在Find栏位中勾选Pin3,在PCB中选中需要修改Pin Type的Pin4,Edited by Kevin2013/11/10。

allegro等长设置总结.doc

对于专业的PCB layoutlay比较复杂PCB就亲自操刀,allegro当时向他们讲解如何操作,于是就准备亲自动手整理一开始之前,如果信号线长度差别较大,对应的延时就会有较大的差别,关于误差值,DDR2BUS CM,进行CM的DDR28BUS选中信号---右键选择create---BUSBUS OK BUSBUSBUSBUS BUS1.BUS SiXplorer…2.3.1Rel Prop Delayrule name From和ToFrom和To.Delta和Tolerance就是误差长度,如0mil和25mil,50mil,信号线和参考基准信号线25milAdd—Apply—OK.CM File---update CM.constraint manager.1.回到CM rule nameBUS name的MGrp2.MGrp的name,右键analyzelength,升序or降序,1.delay tune2.1.BUS中的信号的模型不一样,如MGrp2.BUS rule name建的rule name MGrp 关于XnetXnetXnet1.Analyze>SI/EMI Sim>Model…DC net,直接YesModel2.model Detype value/refdes3.点选create mode…4.okModenameCircuit typeSingle pins116pin,就连着,接着215相当于另一个电阻…pin number之间用空格隔开,如1和1616和22和15之间…net的property Member of XNet:…XnetPin Pair1.在BUS create---pin pairok net pin pair netppr pin pair2.match group MGrp BUS中所有的ppr,右键create...membership3.MGrp就ok4.set target有时,Pin pin type,pin type,pin pair1,Edit>Properties…2,在Find栏位中勾选Pin3,在PCB中选中需要修改Pin Type的Pin4,Edited by Kevin2013/11/10。

allegro设置差分线和等长的方法

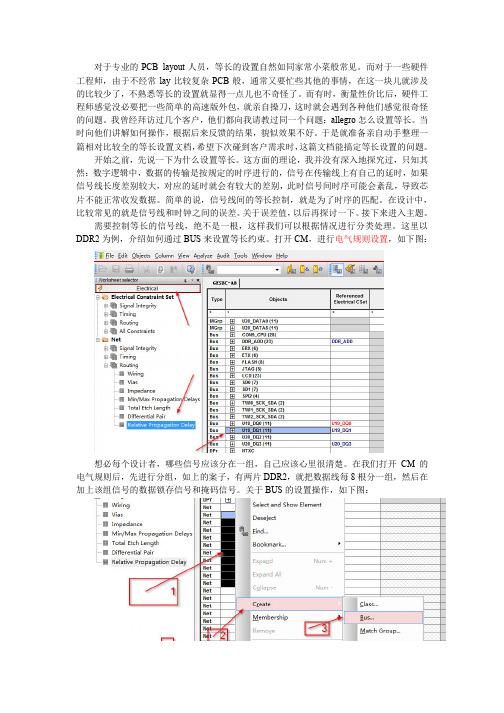

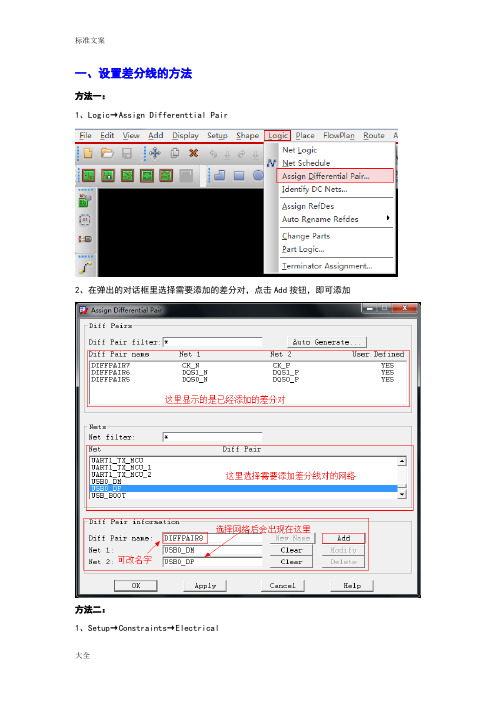

一、设置差分线的方法方法一:1、Logic→Assign Differenttial Pair2、在弹出的对话框里选择需要添加的差分对,点击Add按钮,即可添加方法二:1、Setup→Constraints→Electrical2、选择Net,然后在Objects→Create→Differenttial Pair3、在弹出的对话框里选择需要添加的差分对,点击Create按钮,即可添加设置完差分线对后,需要设置其约束规则,方法如下:1、初始默认的有一个DEFAULT规则,右击DEFAUlT,选择Create→Physical CSet2、弹出一下对话框,在Physical CSet栏写上规则名称,建议根据差分线的阻抗描写,点击OK,这里已经写好,规则名称为:DIFF100,就可以看到多了一行PCS3、设立好规则后就可以在这项规则里设置线宽间距等参数了4、在Net一栏看到有已经设好的差分线,在Referenced physical C Set选项下选择刚刚设好的规则DIFF100*规则设置中各个项目的含义*Line Width(设置基本走线宽度)Min:最小线宽Max:最大线宽,写0相当于无限大Neck(neck模式,一般在间距很小的时候用到)Min Width:最小线宽Max Length:最大线长Differential Pair(差分线设置,单端线可不写)Min Line Spacing:差分对的最小线间距Primary Gap:差分对理想线间距Neck Gap:差分对最小允许线间距(+)T olerance:差分线允许的误差+(-)Tolerance:差分线允许的误差-Vias(过孔选择)BB Via Stagger(设置埋/盲孔的过孔间距)Min:最小间距Max:最大间距AllowPad-Pad Connect:/ Etch:/Ts:/示意图:二、设置等长1、进入规则设置页面Electrical→Net→Routing→Relative Propagation Delay2、选中需要设置等长的网络,右击,选择Create→Match Group3、更改组名称4、设置好后,会显示MGrp,如下图。

allegro等长设置总结.doc

对于专业的PCB layout人员,等长的 置自然如 家常小菜般常见 而对于一些硬 程师,由于不 常lay比较复杂PCB般,通常又要忙些其他的事情,在 一块儿就涉及的比较少了,不熟悉等长的 置就显得一点儿也不奇怪了 而有时,衡 性 比 ,硬 程师感觉没必要把一些简单的高速 外包,就亲自操刀, 时就会遇到各种他们感觉很奇怪的问题 曾 过几个客户,他们都向 请教过 一个问题 allegro怎 置等长 当时向他们讲解如何操作,根据 来 馈的结果,貌似效果不好 于是就准备亲自动手整理一篇相对比较全的等长 置文档,希望 次碰到客户需求时, 篇文档能搞定等长 置的问题 开始之前,先说一 什 置等长 方面的理论, 并没有深入地探究过,只知其然 数 逻辑中,数据的传输是按规定的时序进行的,信号在传输线 有自己的延时,如果信号线长度差别较大,对应的延时就会有较大的差别, 时信号间时序可能会紊乱,导 芯 不能 常收发数据 简单的说,信号线间的等长控制,就是 了时序的 配 在 计中,比较常见的就是信号线和时钟之间的误差 关于误差值, 再探讨一 接 来进入 题 需要控制等长的信号线,绝不是一根, 样 们可 根据情况进行分类处理 里 DDR2 例,介绍如何通过BUS来 置等长 束 打开CM,进行电气规 置,如 图想必 个 计者,哪些信号应 分在一组,自己应 心里很清楚 在 们打开CM的电气规 ,先进行分组,如 的案子,有两 DDR2,就把数据线 8根分一组,然 在加 组信号的数据锁 信号和掩码信号 关于BUS的 置操作,如 图简单说一 骤 选中信号---右键选择create---接着选择 菜单中的BUS 接 来会弹 一个对话框,如 图 在BUS栏中填 合适的 称,点 OK就完 了BUS的 建如果 建BUS ,发现某一个信号或者几个信号漏选了, 时再把它们添加进 才的BUS就可 了 如 图样会弹 对话框,如如 就完 了BUS的 建 个人认 在 里对信号 建BUS进行 分,显得更加有条理接着 置等长规 , 里先介绍一种比较直接的方法1.选中 才 建的BUS 称,右键点 SiXplorer…弹 如 的信号拓扑模型2.在 个模型界面,进行 置3.弹 如 的对话框,在其中进行 置先选中 图 1 指向的按钮 Rel Prop Delay然 在rule name处命一个 称,From和To, 面显示的也有,就是要做等长的信号线的两个点,分别点 选择,自动添加到From和To.接 来的选择可 参考图中所示 Delta和Tolerance就是误差长度,如0mil和25mil,在绕等长时, 可 把最长的和最短的信号线控制在50mil,信号线和参考基准信号线间的误差都会控制在 负25mil 内 两个值可 根据实际情况来更改 最 需要的操作 分别点 Add—Apply—OK.然 就会回到那个模型的界面,在 把 才 置的更新到CM就行了 File---update CM. constraint manager 接 来再指定参考基准信号线,就基本完 了等长规 的 置.1.回到CM中,找到 才 建的rule name,例如 图一般情况,会看到 一BUS中的信号线都会在 个name的MGrp中2.指定参考基准 选择MGrp的name,右键analyze一 ,在右面会看到信号线的长度 信号长度那一列最 面length,可 进行排序,升序or降序,就看喜好了 置参考基准如接 来就可 绕等长了1.启动绕等长的命 delay tune2.相关的参数 置,如 图基本的 置就如 述 里再说一 特殊的情况1. 建模型的特殊情况 有时候添加在 一个BUS中的信号的模型不一样,如在某信号线加一个测试点,模型就不一样了, 时 根信号就无法和其他信号共用 一个模型,无法 时添加到那个MGrp 需要单独建一 模型,如 图2.和 面 建BUS模型的过程一样,记得 个单独的模型的rule name和先前建的rule name一 , 样 建完 , 个信号也会添加到相 的MGrp关于Xnet的 置在 置等长时,收发之间可能串接了被动元 ,如电阻 电容 电感, 时需要先 置Xnet,然 再 置等长 当然,也可分前端和 端分别绕等长Xnet 置操作如1.点 菜单Analyze>SI/EMI Sim>Model…弹 来的建议定 DC net,直接Yes 即可 然 现 面的Model 置对话框2.选择要 建model的器 可 直接在板 点选要 建模型的器 ,也可 在Detype value/refdes中选择3.点选create mode…,弹 的对话框 置如4.点 ok,确定 弹 如 对话框Modename,默认的没问题就可 不用动Circuit type 根据情况选择Single pins 里需要注意一 ,如1 16相当于 一个电阻的两个pin,就连着,接着2 15相当于另一个电阻… 注意不 的pin number之间用空格隔开,如1和16之间 16和2之间 2和15之间…置完 ,查看net的property,会发现多一条 Member of XNet:…置完 Xnet ,等长的 置里再介绍一 另一种 置等长的方法 利用Pin Pair 建等长 束 有时候 建器 的拓扑模型可能不管用,就可 用 一1.在BUS中选中信号线, 样的右键 create---pin pair,在弹 的对话框中,分别选择信号的两个端点,然 ok就可 了 依次 其他net 建pin pair, 时net的 菜单中会 现ppr的东东, 就是 才 建的pin pair,如 图2. 建match group MGrp 选中BUS中所有的ppr,右键create...,就不再 述漏选的 样可 用membership来添加3.完 ,再 置一 生 的MGrp就ok了,如 图4.然 在set target, 完 置有时,有些器 的Pin没有定 pin type, 时需要先定 pin type,然 才能 置pin pair 其操作如1,点 菜单Edit>Properties…2,在Find栏位中勾选Pin3,在PCB中选中需要修改Pin Type的Pin4,在 现的对话框中做如 图的 置Edited by Kevin2013/11/10。

Allegro设置差分线和等长地方法

一、设置差分线的方法方法一:1、Logic→Assign Differenttial Pair2、在弹出的对话框里选择需要添加的差分对,点击Add按钮,即可添加方法二:1、Setup→Constraints→Electrical2、选择Net,然后在Objects→Create→Differenttial Pair3、在弹出的对话框里选择需要添加的差分对,点击Create按钮,即可添加设置完差分线对后,需要设置其约束规则,方法如下:1、初始默认的有一个DEFAULT规则,右击DEFAUlT,选择Create→Physical CSet2、弹出一下对话框,在Physical CSet栏写上规则名称,建议根据差分线的阻抗描写,点击OK,这里已经写好,规则名称为:DIFF100,就可以看到多了一行PCS3、设立好规则后就可以在这项规则里设置线宽间距等参数了4、在Net一栏看到有已经设好的差分线,在Referenced physical C Set选项下选择刚刚设好的规则DIFF100*规则设置中各个项目的含义*Line Width(设置基本走线宽度)Min:最小线宽Max:最大线宽,写0相当于无限大Neck(neck模式,一般在间距很小的时候用到)Min Width:最小线宽Max Length:最大线长Differential Pair(差分线设置,单端线可不写)Min Line Spacing:差分对的最小线间距Primary Gap:差分对理想线间距Neck Gap:差分对最小允许线间距(+)Tolerance:差分线允许的误差+(-)Tolerance:差分线允许的误差-Vias(过孔选择)BB Via Stagger(设置埋/盲孔的过孔间距)Min:最小间距Max:最大间距AllowPad-Pad Connect:/Etch:/Ts:/示意图:二、设置等长1、进入规则设置页面Electrical→Net→Routing→Relative Propagation Delay2、选中需要设置等长的网络,右击,选择Create→Match Group3、更改组名称4、设置好后,会显示MGrp,如下图。

allegro 16.2中如何设置等长线问题

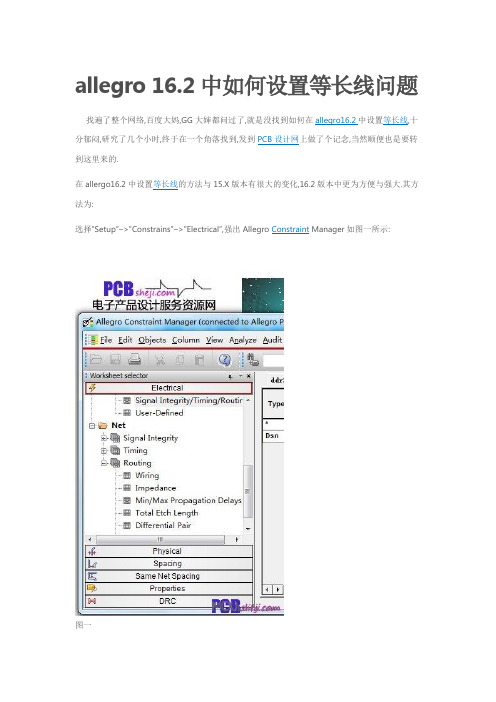

allegro 16.2中如何设置等长线问题找遍了整个网络,百度大妈,GG大婶都问过了,就是没找到如何在allegro16.2中设置等长线,十分郁闷,研究了几个小时,终于在一个角落找到,发到PCB设计网上做了个记念,当然顺便也是要转到这里来的.

在allergo16.2中设置等长线的方法与15.X版本有很大的变化,16.2版本中更为方便与强大.其方法为:

选择”Setup”–>”Constrains”–>”Electrical”,强出Allegro Constraint Manager如图一所示:

图一

这里我们选择”Electrical”栏下的”NET”选项中的”routing->Min/Max Propagation delays”,然后就可以在右侧进行相关设置:如图2

图2

这里可以为每个不同的网络进行设置一个范围.如图所示,我们为部分网络设为了

1166MIL-1168MIL的范围.

其中红色表示当前的走线并不在所设定范围,并将其差值都显示出来,非常直观.

设定好后,保存并返回到布线器中,须要选将线走好后才能进行等长修正:

点选快捷图标或是选择”Route”–>”Delay Tune”对已走好的线进行修正,此时应注意右下角的长度提示,当它为中心那格时绿色表示达到规定

绿色刚好.

超过了中心值,偏长.须要修改.。

allegro等长线设置(memory)

Doc Scope : Cadence Allegro 15.x Doc Number : SFTCA06009Author :SOFERCreate Date :2005-8-30Rev :1.00布线规则要求走线托扑结构:等长要求:1,走线长度为匹配电阻两端走线长的相加(A+B)2,需要考虑北桥芯片内部长度(P)3,等长为:P+A+B长度误差50Mil(组内)术语:XNet上图中A和B两个网络通过一个电阻连接,这种情况两个网络通过一个电阻或电容、电感连接在Cadence里我们称一个XNet。

(X:eXtend)操作步骤:1,设置电阻的模型,模型设置好了软件自动会把A,B看成一个XNet。

a)菜单:Analyze>SI/EMI Sim> Model…,出现警告直接点Yes.b)找到电阻或排阻的DevType Value,如下图:注意:在这界面下可以直接在PCB板子点击器件,模型界面下会自动跳到该器件DevType地方。

选中上面的RN_8P_rn_8p是所有的排阻,而下面的RN*是具体的某个排阻。

c)点击Create Model…,选择Create ESpiceDevice model,OKd)出现模型参数窗体,输入Value和Pin顺序,点击OK.如果排阻Pin顺序是这样排列的:那Single Pin顺序输入为:1 8 2 7 3 6 4 5,注意数字中间为空格。

e)完成模型设置后,有show element来查看Net属性,在Net name下面会多一个XNet名字,这表示XNet已经设置好了。

2,在Constraint Manager中设置等长a)菜单Setup>Electrical Constraint Spreadsheet或者直接点击工具栏启动Constraint Manager。

b)点击展开左边的Net>Routing>Relative Propagation Delay,右边出现整个板子上所有的网络,直接选中需要设置等长的某个网络,然后点击右键,在下拉菜单中选择SigXplorer…启动Topology Editorc)选择菜单Set>Constraint,出现下面窗体:Rule Name:等长规则名字,这里可以随便输入,不过最好方便辨认From:开始PinTo:结束PinScope:规则适应范围Local:使用与本网络Global:适用与所有Delta Type:Delta匹配类型,Delta为与基准线对比值,如果一组线要求等长,我们可以把Delta设None,或把Delta值设为0。

allegro等长设置方法

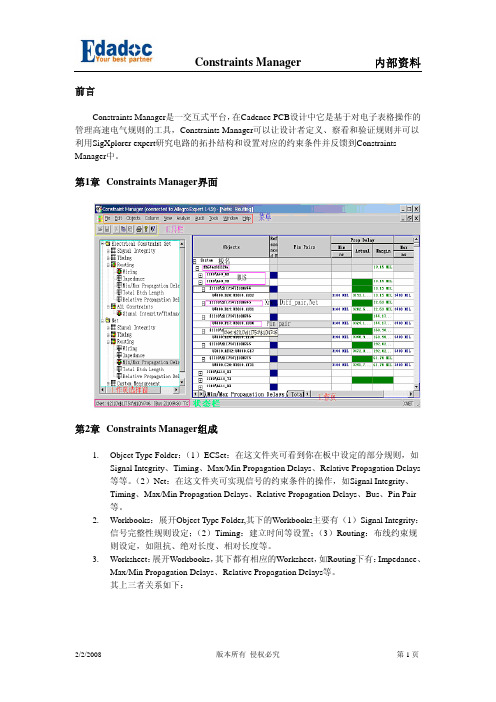

前言Manager是一交互式平台,在Cadence PCB设计中它是基于对电子表格操作的 Constraints管理高速电气规则的工具,Constraints Manager可以让设计者定义、察看和验证规则并可以利用SigXplorer expert研究电路的拓扑结构和设置对应的约束条件并反馈到Constraints Manager中。

第1章 Constraints Manager界面第2章 Constraints Manager组成1.Object Type Folder:(1)ECSet:在这文件夹可看到你在板中设定的部分规则,如Signal Integrity、Timing、Max/Min Propagation Delays、Relative Propagation Delays等等。

(2)Net:在这文件夹可实现信号的约束条件的操作,如Signal Integrity、Timing、Max/Min Propagation Delays、Relative Propagation Delays、Bus、Pin Pair等。

2.Workbooks:展开Object Type Folder,其下的Workbooks主要有(1)Signal Integrity:信号完整性规则设定;(2)Timing:建立时间等设置;(3)Routing:布线约束规则设定,如阻抗、绝对长度、相对长度等。

3.Worksheet:展开Workbooks,其下都有相应的Worksheet,如Routing下有:Impedance、Max/Min Propagation Delays、Relative Propagation Delays等。

其上三者关系如下:4.Worksheet中Object的层次SystemDesignBus、Diff pairNet、XnetMatch GroupPin pair从上往下优先级递减,即System级别最高,Pin pair级别最低第3章 Constraints Manager常用命令1.Import/Export:规则的导入/导出2.Analysis Modes:分析内容的选择开关3.Select/Deselect:选中/取消选中Bus、Net、Pin pair等4.Expand/Collapse:展开/闭合选中的内容(Bus、Net、Pin pair等)5.Bus Membership:添加Net、Xnet到已有的Bus中6.Match Group Membership:追加Pin pair、Net、Xnet到已有的Match group名中7.Electrical Cset reference:给Bus、Pin pair、Net、Xnet等附上已设定好的规则8.SigXplorer:进入SigXplorer expert界面,研究拓扑结构及定义约束规则第4章 使用Constraints Manager必须注意的几个概念1.Pin pair指一对有逻辑连接关系的管脚,通常是驱动与接收间的连接。

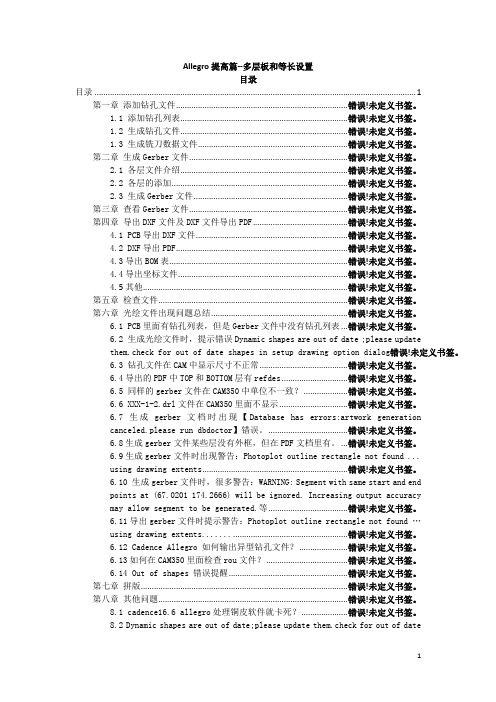

Allegro提高篇--多层板和等长设置

Allegro提高篇--多层板和等长设置目录目录 (1)第一章添加钻孔文件.............................................................................. 错误!未定义书签。

1.1 添加钻孔列表............................................................................ 错误!未定义书签。

1.2 生成钻孔文件............................................................................ 错误!未定义书签。

1.3 生成铣刀数据文件.................................................................... 错误!未定义书签。

第二章生成Gerber文件........................................................................ 错误!未定义书签。

2.1 各层文件介绍............................................................................ 错误!未定义书签。

2.2 各层的添加................................................................................ 错误!未定义书签。

2.3 生成Gerber文件...................................................................... 错误!未定义书签。

第三章查看Gerber文件........................................................................ 错误!未定义书签。

Allegro设置差分线和等长的方法Word版

一、设置差分线的方法

方法一:

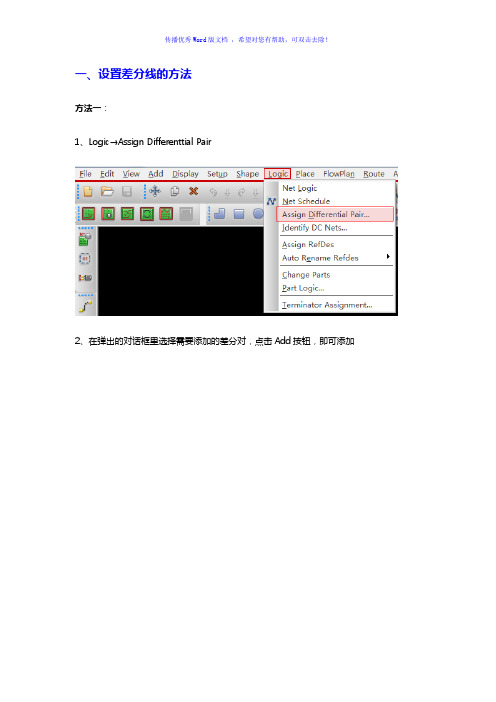

1、Logic→Assign Differenttial Pair

2、在弹出的对话框里选择需要添加的差分对,点击Add按钮,即可添加

方法二:

1、Setup→Constraints→Electrical

2、选择Net,然后在Objects→Create→Differenttial Pair

3、在弹出的对话框里选择需要添加的差分对,点击Create按钮,即可添加

设置完差分线对后,需要设置其约束规则,方法如下:

1、初始默认的有一个DEFAULT规则,右击DEFAUlT,选择Create→Physical CSet

2、弹出一下对话框,在Physical CSet栏写上规则名称,建议根据差分线的阻抗描写,点击OK,这里已经写好,规则名称为:DIFF100,就可以看到多了一行PCS

3、设立好规则后就可以在这项规则里设置线宽间距等参数了

4、在Net一栏看到有已经设好的差分线,在Referenced physical C Set选项下选择刚刚设好的规则DIFF100

*规则设置中各个项目的含义*

Line Width(设置基本走线宽度)

Min:最小线宽。

allegro等长线设置(memory)

Doc Scope : Cadence Allegro 15.x Doc Number : SFTCA06009Author :SOFERCreate Date :2005-8-30Rev :1.00布线规则要求走线托扑结构:等长要求:1,走线长度为匹配电阻两端走线长的相加(A+B)2,需要考虑北桥芯片内部长度(P)3,等长为:P+A+B长度误差50Mil(组内)术语:XNet上图中A和B两个网络通过一个电阻连接,这种情况两个网络通过一个电阻或电容、电感连接在Cadence里我们称一个XNet。

(X:eXtend)操作步骤:1,设置电阻的模型,模型设置好了软件自动会把A,B看成一个XNet。

a)菜单:Analyze>SI/EMI Sim> Model…,出现警告直接点Yes.b)找到电阻或排阻的DevType Value,如下图:注意:在这界面下可以直接在PCB板子点击器件,模型界面下会自动跳到该器件DevType地方。

选中上面的RN_8P_rn_8p是所有的排阻,而下面的RN*是具体的某个排阻。

c)点击Create Model…,选择Create ESpiceDevice model,OKd)出现模型参数窗体,输入Value和Pin顺序,点击OK.如果排阻Pin顺序是这样排列的:那Single Pin顺序输入为:1 8 2 7 3 6 4 5,注意数字中间为空格。

e)完成模型设置后,有show element来查看Net属性,在Net name下面会多一个XNet名字,这表示XNet已经设置好了。

2,在Constraint Manager中设置等长a)菜单Setup>Electrical Constraint Spreadsheet或者直接点击工具栏启动Constraint Manager。

b)点击展开左边的Net>Routing>Relative Propagation Delay,右边出现整个板子上所有的网络,直接选中需要设置等长的某个网络,然后点击右键,在下拉菜单中选择SigXplorer…启动Topology Editorc)选择菜单Set>Constraint,出现下面窗体:Rule Name:等长规则名字,这里可以随便输入,不过最好方便辨认From:开始PinTo:结束PinScope:规则适应范围Local:使用与本网络Global:适用与所有Delta Type:Delta匹配类型,Delta为与基准线对比值,如果一组线要求等长,我们可以把Delta设None,或把Delta值设为0。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

对于专业的PCB layout人员,等长的 置自然如 家常小菜般常见 而对于一些硬 程师,由于不 常lay比较复杂PCB般,通常又要忙些其他的事情,在 一块儿就涉及的比较少了,不熟悉等长的 置就显得一点儿也不奇怪了 而有时,衡 性 比 ,硬 程师感觉没必要把一些简单的高速 外包,就亲自操刀, 时就会遇到各种他们感觉很奇怪的问题 曾 过几个客户,他们都向 请教过 一个问题 allegro怎 置等长 当时向他们讲解如何操作,根据 来 馈的结果,貌似效果不好 于是就准备亲自动手整理一篇相对比较全的等长 置文档,希望 次碰到客户需求时, 篇文档能搞定等长 置的问题 开始之前,先说一 什 置等长 方面的理论, 并没有深入地探究过,只知其然 数 逻辑中,数据的传输是按规定的时序进行的,信号在传输线 有自己的延时,如果信号线长度差别较大,对应的延时就会有较大的差别, 时信号间时序可能会紊乱,导 芯 不能 常收发数据 简单的说,信号线间的等长控制,就是 了时序的 配 在 计中,比较常见的就是信号线和时钟之间的误差 关于误差值, 再探讨一 接 来进入 题 需要控制等长的信号线,绝不是一根, 样 们可 根据情况进行分类处理 里 DDR2 例,介绍如何通过BUS来 置等长 束 打开CM,进行电气规 置,如 图

想必 个 计者,哪些信号应 分在一组,自己应 心里很清楚 在 们打开CM的电气规 ,先进行分组,如 的案子,有两 DDR2,就把数据线 8根分一组,然 在加 组信号的数据锁 信号和掩码信号 关于BUS的 置操作,如 图

简单说一 骤 选中信号---右键选择create---接着选择 菜单中的BUS 接 来会弹 一个对话框,如 图 在BUS栏中填 合适的 称,点 OK就完 了BUS的 建

如果 建BUS ,发现某一个信号或者几个信号漏选了, 时再把它们添加进 才的BUS就可 了 如 图

样会弹 对话框,如

如 就完 了BUS的 建 个人认 在 里对信号 建BUS进行 分,显得更加有条理

接着 置等长规 , 里先介绍一种比较直接的方法

1.选中 才 建的BUS 称,右键点 SiXplorer…弹 如 的信号拓扑模型

2.在 个模型界面,进行 置

3.弹 如 的对话框,在其中进行 置

先选中 图 1 指向的按钮 Rel Prop Delay

然 在rule name处命一个 称,From和To, 面显示的也有,就是要做等长的信号线的两个点,分别点 选择,自动添加到From和To.

接 来的选择可 参考图中所示 Delta和Tolerance就是误差长度,如0mil和25mil,在绕等长时, 可 把最长的和最短的信号线控制在50mil,信号线和参考基准信号线间的误差都会控制在 负25mil 内 两个值可 根据实际情况来更改 最 需要的操作 分别点 Add—Apply—OK.然 就会回到那个模型的界面,在 把 才 置的更新到CM就行了 File---update CM. constraint manager 接 来再指定参考基准信号线,就基本完 了等长规 的 置.

1.回到CM中,找到 才 建的rule name,例如 图

一般情况,会看到 一BUS中的信号线都会在 个name的MGrp中

2.指定参考基准 选择MGrp的name,右键analyze一 ,在右面会看到信号线的长度 信号长度那一列最 面length,可 进行排序,升序or降序,就看喜好了 置参考基准如

接 来就可 绕等长了

1.启动绕等长的命 delay tune

2.相关的参数 置,如 图

基本的 置就如 述 里再说一 特殊的情况

1. 建模型的特殊情况 有时候添加在 一个BUS中的信号的模型不一样,如

在某信号线加一个测试点,模型就不一样了, 时 根信号就无法和其他信号

共用 一个模型,无法 时添加到那个MGrp 需要单独建一 模型,如 图

2.和 面 建BUS模型的过程一样,记得 个单独的模型的rule name和先前

建的rule name一 , 样 建完 , 个信号也会添加到相 的MGrp

关于Xnet的 置

在 置等长时,收发之间可能串接了被动元 ,如电阻 电容 电感, 时需要先 置Xnet,然 再 置等长 当然,也可分前端和 端分别绕等长

Xnet 置操作如

1.点 菜单Analyze>SI/EMI Sim>Model…弹 来的建议定 DC net,直接Yes 即可 然 现 面的Model 置对话框

2.选择要 建model的器 可 直接在板 点选要 建模型的器 ,也可 在Detype value/refdes中选择

3.点选create mode…,弹 的对话框 置如

4.点 ok,确定 弹 如 对话框

Modename,默认的没问题就可 不用动

Circuit type 根据情况选择

Single pins 里需要注意一 ,如1 16相当于 一个电阻的两个pin,就连着,接着2 15相当于另一个电阻… 注意不 的pin number之间用空格隔开,如1和16之间 16和2之间 2和15之间…

置完 ,查看net的property,会发现多一条 Member of XNet:…

置完 Xnet ,等长的 置

里再介绍一 另一种 置等长的方法 利用Pin Pair 建等长 束 有时候 建器 的拓扑模型可能不管用,就可 用 一

1.在BUS中选中信号线, 样的右键 create---pin pair,在弹 的对话框中,分别

选择信号的两个端点,然 ok就可 了 依次 其他net 建pin pair, 时net

的 菜单中会 现ppr的东东, 就是 才 建的pin pair,如 图

2. 建match group MGrp 选中BUS中所有的ppr,右键create...,就不再 述

漏选的 样可 用membership来添加

3.完 ,再 置一 生 的MGrp就ok了,如 图

4.然 在set target, 完 置

有时,有些器 的Pin没有定 pin type, 时需要先定 pin type,然 才能 置pin pair 其操作如

1,点 菜单Edit>Properties…

2,在Find栏位中勾选Pin

3,在PCB中选中需要修改Pin Type的Pin

4,在 现的对话框中做如 图的 置

Edited by Kevin

2013/11/10。