电子时钟设计(DS1302)基于51单片机

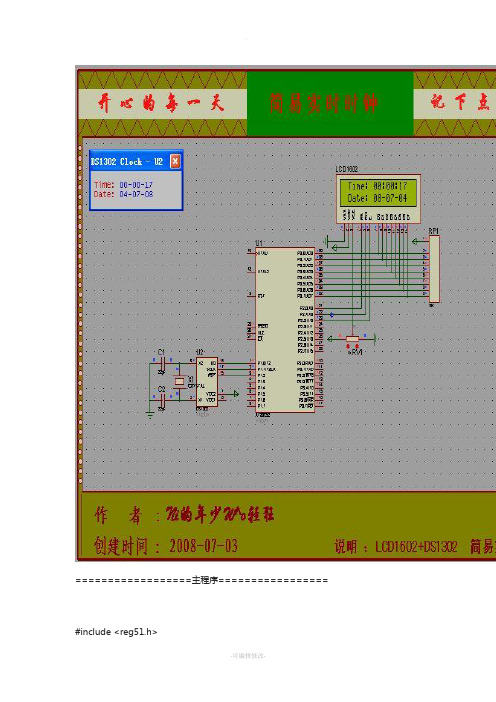

基于51单片机的ds1302与LM016L液晶时钟设计

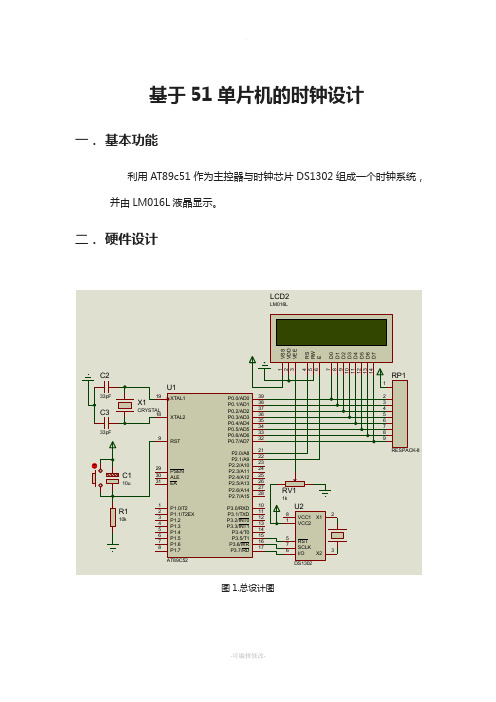

基于51单片机的时钟设计一.基本功能利用AT89c51作为主控器与时钟芯片DS1302组成一个时钟系统,并由LM016L液晶显示。

二.硬件设计图1.总设计图1.单片机最小系统1.1选用AT89C51的引脚功能图2. AT89C51XTAL1:单芯片系统时钟的反向放大器输入端。

XTAL2:系统时钟的反向放大器输出端,一般在设计上只要在XTAL1和XTAL2上接上一只石英震荡晶体系统就可以工作了,此外可以在两引脚与地之间加入20PF的小电容,可以使系统更稳定,避免噪音干扰而死机。

RESET:重置引脚,高电平动作,当要对晶体重置时,只要对此引脚电平提升至高电平并保持两个及其周期以上的时间便能完成系统重置的各项动作,使得内部特殊功能寄存器内容均被设成已知状态。

1.2复位电路如图所示,当按下按键时,就能完成整个系统的复位,使得程序从新运行。

图3.复位电路1.3时钟电路时钟电路用于产生单片机工作所需要的时钟信号,单片机本身就是一个复杂的同步时序电路,为了保证同步工作方式的实现,电路应在唯一的时钟信号控制下严格地按时序进行工作。

在AT89C51芯片内部有一个高增益反相放大器,其输入端为芯片引脚X1,输出端为引脚X2,在芯片的外部跨接晶体振荡器和微调电容,形成反馈电路,就构成了一个稳定的自激振荡器。

此电路采用12MHz的石英晶体。

图4.时钟电路2.时钟芯片部分2.1 DS1302引脚说明图.51)Vcc1:后备电源,VCC2:主电源。

在主电源关闭的情况下,也能保持时钟的连续运行。

DS1302由Vcc1或Vcc2两者中的较大者供电。

当Vcc2大于Vcc1+0.2V时,Vcc2给DS1302供电。

当Vcc2小于Vcc1时,DS1302由Vcc1供电。

2)X1、X2:振荡源,外接32.768kHz晶振。

3)RST:复位/片选线,通过把RST输入驱动置高电平来启动所有的数据传送。

RST输入有两种功能:首先,RST接通控制逻辑,允许地址/命令序列送入移位寄存器;其次,RST 提供终止单字节或多字节数据的传送手段。

51单片机实现基于DS1302_1602_18B20的多功能电子时钟_带测温功能

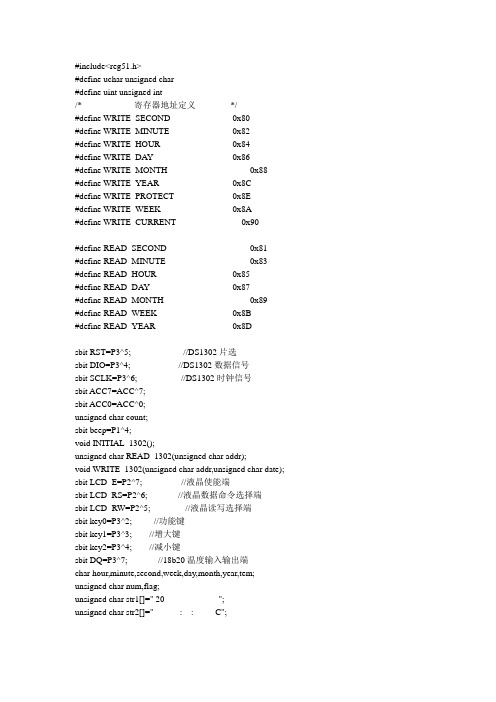

#include<reg51.h>#define uchar unsigned char#define uint unsigned int/*------------------寄存器地址定义------------*/#define WRITE_SECOND 0x80#define WRITE_MINUTE 0x82#define WRITE_HOUR 0x84#define WRITE_DAY 0x86#define WRITE_MONTH 0x88#define WRITE_YEAR 0x8C#define WRITE_PROTECT 0x8E#define WRITE_WEEK 0x8A#define WRITE_CURRENT 0x90#define READ_SECOND 0x81#define READ_MINUTE 0x83#define READ_HOUR 0x85#define READ_DAY 0x87#define READ_MONTH 0x89#define READ_WEEK 0x8B#define READ_YEAR 0x8Dsbit RST=P3^5; //DS1302片选sbit DIO=P3^4; //DS1302数据信号sbit SCLK=P3^6; //DS1302时钟信号sbit ACC7=ACC^7;sbit ACC0=ACC^0;unsigned char count;sbit beep=P1^4;void INITIAL_1302();unsigned char READ_1302(unsigned char addr);void WRITE_1302(unsigned char addr,unsigned char date); sbit LCD_E=P2^7; //液晶使能端sbit LCD_RS=P2^6; //液晶数据命令选择端sbit LCD_RW=P2^5; //液晶读写选择端sbit key0=P3^2; //功能键sbit key1=P3^3; //增大键sbit key2=P3^4; //减小键sbit DQ=P3^7; //18b20温度输入输出端char hour,minute,second,week,day,month,year,tem; unsigned char num,flag;unsigned char str1[]=" 20 - - ";unsigned char str2[]=" : : C";void delay(unsigned char z);void LCD_WRITE_COM(unsigned char com);void LCD_WRITE_DA TA(unsigned char date);void LCD_WRITE_SFM(unsigned char addr,unsigned char date);void LCD_WRITE_NYR(unsigned char addr,unsigned char date);void LCD_WRITE_WEEK(unsigned char week);void LCD_INITIAL();void LCD_WRITE_TEMP(uchar addr,uchar temp);void keyscan();void INITIAL_TEMER0();uchar TMPH ,TMPL;void w1602c(uchar com);void w1602d(uchar data01);void delay2(uint ms);void delay3(uint us);uchar resert(void);uchar read_byte();void write_byte(uchar val);uint get_temp();void display();void delay3(uint us); //18b20uchar resert(void); //18b20uchar read_byte(); //18b20void write_byte(uchar val); //18b20uint get_temp(); //18b20void main(){LCD_INITIAL(); //液晶初始化INITIAL_1302(); //DS1302初始化INITIAL_TEMER0(); //定时器初始化while(1){keyscan(); //按键扫描if(flag==0) //当标志位为0,允许读取DS1302数据,将数据送入液晶显示{second=READ_1302(0x81);LCD_WRITE_SFM(10,second);minute=READ_1302(0x83);LCD_WRITE_SFM(7,minute);hour=READ_1302(0x85);LCD_WRITE_SFM(4,hour);week=READ_1302(0x8b);LCD_WRITE_WEEK(week);day=READ_1302(0x87);LCD_WRITE_NYR(9,day);month=READ_1302(0x89);LCD_WRITE_NYR(6,month);year=READ_1302(0x8d);LCD_WRITE_NYR(3,year);tem=get_temp();LCD_WRITE_TEMP(13,tem);}}}/**********************1602BU份******************************************************/void delay(unsigned char z) //1602de延时函数{unsigned char x,y;for(x=z;x>0;x--)for(y=110;y>0;y--);}void LCD_WRITE_COM(unsigned char com){LCD_RS=0;LCD_RW=0;LCD_E=1;P0=com;delay(5);LCD_E=0;}void LCD_WRITE_DA TA(unsigned char date){LCD_RS=1;LCD_RW=0;LCD_E=1;P0=date;delay(5);LCD_E=0;}void LCD_WRITE_SFM(unsigned char addr,unsigned char date) {unsigned char shi,ge;shi=date/10;ge=date%10;LCD_WRITE_COM(0x80+0x40+addr);LCD_WRITE_DATA(0x30+shi);LCD_WRITE_DATA(0x30+ge);}void LCD_WRITE_NYR(unsigned char addr,unsigned char date) {char shi,ge;shi=date/10;ge=date%10;LCD_WRITE_COM(0x80+addr);LCD_WRITE_DATA(0x30+shi);LCD_WRITE_DATA(0x30+ge);}void LCD_WRITE_WEEK(unsigned char week){LCD_WRITE_COM(0x80+12);switch(week){case 1: LCD_WRITE_DA TA('M');delay(5);LCD_WRITE_DATA('O');delay(5);;LCD_WRITE_DATA('N');break;case 2: LCD_WRITE_DA TA('T');delay(5);LCD_WRITE_DATA('U');delay(5);LCD_WRITE_DATA('E');break;case 3: LCD_WRITE_DA TA('W');delay(5);LCD_WRITE_DATA('E');delay(5);LCD_WRITE_DATA('D');break;case 4: LCD_WRITE_DA TA('T');delay(5);LCD_WRITE_DATA('H');delay(5);LCD_WRITE_DATA('U');break;case 5: LCD_WRITE_DA TA('F');delay(5);LCD_WRITE_DATA('R');delay(5);LCD_WRITE_DATA('I');break;case 6: LCD_WRITE_DA TA('S');delay(5);LCD_WRITE_DATA('A');delay(5);LCD_WRITE_DATA('T');break;case 7: LCD_WRITE_DA TA('S');delay(5);LCD_WRITE_DATA('U');delay(5);LCD_WRITE_DATA('N');break;}}void LCD_WRITE_TEMP(uchar addr,uchar temp){char shi,ge;shi=temp/10;ge=temp%10;LCD_WRITE_COM(0x80+0x40+addr);LCD_WRITE_DATA(0x30+shi);LCD_WRITE_DATA(0x30+ge);}void LCD_INITIAL(){unsigned char i;LCD_WRITE_COM(0x38);LCD_WRITE_COM(0x0c);LCD_WRITE_COM(0x06); //经本人试验证明1602初始化不清屏也可实现LCD_WRITE_COM(0x80);for(i=0;i<16;i++){LCD_WRITE_DATA(str1[i]);delay(5);}LCD_WRITE_COM(0x80+0x40);//液晶第二行显示for(i=0;i<16;i++){LCD_WRITE_DATA(str2[i]);delay(5);}}/***************************1302部分***************************************************/void WRITE_1302(unsigned char addr,unsigned char date) {unsigned char i;RST=0;SCLK=0;RST=1;for(i=8;i>0;i--){SCLK=0;ACC=addr;DIO=ACC0;addr>>=1;SCLK=1;}for(i=8;i>0;i--){SCLK=0;ACC=date;DIO=ACC0;date>>=1;SCLK=1;}RST=0;}unsigned char READ_1302(unsigned char addr){unsigned char i,date1,date2;RST=0;SCLK=0;RST=1;for(i=8;i>0;i--){SCLK=0;ACC=addr;DIO=ACC0;addr>>=1;SCLK=1;}for(i=8;i>0;i--){ACC7=DIO;SCLK=1;ACC>>=1;SCLK=0;}RST=0;date1=ACC;date2=date1/16;date1=date1%16;date1=date1+date2*10;return(date1) ;}void INITIAL_1302(){WRITE_1302(WRITE_SECOND,READ_1302(READ_SECOND)&0x7f); //启动DS1302}/**************************键盘扫描部分***************************************************/void keyscan(){if(key0==0)//确认功能键按下{delay(20);if(key0==0)//去抖{while(!key0);//释放num++;switch(num){case 1: flag=1; //修改时间,禁止从DS1302读数据TR0=0; //定时器关LCD_WRITE_COM(0x0f); //光标开始闪烁LCD_WRITE_COM(0x80+3);//第一次按下,光标定位到年位置break;case 2: LCD_WRITE_COM(0x80+6);//第二次按下,光标定位到月位置break;case 3: LCD_WRITE_COM(0x80+9);//第三次按下,光标定位到日位置break;case 4: LCD_WRITE_COM(0x80+12);//第四次按下,光标定位到星期位置break;case 5: LCD_WRITE_COM(0x80+0x40+4);//第五次按下,光标定位到时位置break;case 6: LCD_WRITE_COM(0x80+0x40+7);//第六次按下,光标定位到分位置break;case 7: LCD_WRITE_COM(0x80+0x40+10);//第七次按下,光标定位到秒位置break;case 8: num=0;//第八次按下,记录清零LCD_WRITE_COM(0x0c);//不显示光标WRITE_1302(WRITE_PROTECT,0x00); //允许写操作WRITE_1302(0x80,(second/10*16)+second%10);//将调节后的秒写入DS1302WRITE_1302(0x82,(minute/10*16)+minute%10);//将调节后的分写入DS1302WRITE_1302(0x84,(hour/10*16)+hour%10);//将调节后的时写入DS1302WRITE_1302(0x8a,(week/10*16)+week%10);//将调节后的星期写入DS1302WRITE_1302(0x86,(day/10*16)+day%10);//将调节后的日写入DS1302WRITE_1302(0x88,(month/10*16)+month%10);//将调节后的月写入DS1302WRITE_1302(0x8c,(year/10*16)+year%10);//将调节后的年写入DS1302WRITE_1302(WRITE_PROTECT,0x80); //开写保护flag=0; //时间修改完毕,允许液晶从DS1302读数据TR0=1;break;}}}if(num!=0){if(key1==0)//确认增大键按下{delay(20);if(key1==0)//增大键确实按下{while(!key1);switch(num){case 1: year++;//调节年if(year==100)year=0;LCD_WRITE_NYR(3,year);//将调节后的年送入液晶显示LCD_WRITE_COM(0x80+3);//光标回到指定处break;case 2: month++;//调节月if(month==13)month=0;LCD_WRITE_NYR(6,month);//将调节后的月送入液晶显示LCD_WRITE_COM(0x80+6);//光标回到指定处break;case 3: day++;//调节日if(day==32)day=0;LCD_WRITE_NYR(9,day);//将调节后的日送入液晶显示LCD_WRITE_COM(0x80+9);//光标回到指定处break;case 4: week++;if(week==8)week=0;LCD_WRITE_WEEK(week);//将调节后的星期送入液晶显示LCD_WRITE_COM(0x80+12);//光标回到指定处break;case 5: hour++;if(hour==24)hour=0;LCD_WRITE_SFM(4,hour);//将调节后的小时送入液晶显示LCD_WRITE_COM(0x80+0x40+4);//光标回到指定处break;case 6: minute++;if(minute==60)minute=0;LCD_WRITE_SFM(7,minute);//将调节后的分送入液晶显示LCD_WRITE_COM(0x80+0x40+7);//光标回到指定处break;case 7: second++;if(second==60)second=0;LCD_WRITE_SFM(10,second);//将调节后的秒送入液晶显示LCD_WRITE_COM(0x80+0x40+10);//光标回到指定处break;default:break;}}}if(key2==0)//确认减小键按下{delay(20);if(key2==0)//减小键确实按下{while(!key2);switch(num){case 1: year--;//调节年if(year==-1)year=99;LCD_WRITE_NYR(3,year);LCD_WRITE_COM(0x80+3);break;case 2: month--;//调节月if(month==-1)month=12;LCD_WRITE_NYR(6,month);LCD_WRITE_COM(0x80+6);break;case 3: day--;//调节日if(day==-1)day=31;LCD_WRITE_NYR(9,day);LCD_WRITE_COM(0x80+9);break;case 4: week--;//调节星期if(week==0)week=7;LCD_WRITE_WEEK(week);LCD_WRITE_COM(0x80+12);break;case 5: hour--;//调节时if(hour==-1)hour=23;LCD_WRITE_SFM(4,hour);LCD_WRITE_COM(0x80+0x40+4);break;case 6: minute--;//调节分if(minute==-1)minute=59;LCD_WRITE_SFM(7,minute);LCD_WRITE_COM(0x80+0x40+7);break;case 7: second--;//调节秒if(second==-1)second=59;LCD_WRITE_SFM(10,second);LCD_WRITE_COM(0x80+0x40+10);break;default:break;}}}}}/*******************************蜂鸣器部分******************************************//*-----------定时器0初始化-------------------------*/void INITIAL_TEMER0(){TMOD=0x01;TH0=(65536-20000)/256;TL0=(65536-20000)%256; //晶振频率12MHZ 定时20ms作右TR0=1;EA=1;ET0=1;}/*-------------------------------------------*/void timer0()interrupt 1{TH0=(65536-20000)/256;TL0=(65536-20000)%256; //重装count++;if(count==50) //1秒到{count=0;beep=0; //蜂鸣器响delay(5);beep=1; //蜂鸣器灭}if(tem>=30){beep=0;}}/*****************************18b20部分*********************************************888*/void delay3(uint us){uint s;for(s=0;s<us;s++);}uchar resert(void){uchar ready;DQ=0;delay3(32) ;DQ=1;delay3(3);ready=DQ;delay3(25);return ready;}uchar read_byte(){uchar i,j;uchar value=0;for(i=0;i<8;i++){DQ=0;DQ=1;for(j=0;j<3;j++);if(DQ){value|=0x01<<i;}delay3(6) ;}return value;}void write_byte(uchar val) {uchar i,temp;for(i=0;i<8;i++){temp=val>>i;temp=temp&0x01;DQ=0;if(temp==1)DQ=1;delay3(5);DQ=1;}DQ=1;}uint get_temp(){float f_temp;uint temp;P2=0x00;resert();delay3(50);write_byte(0xcc);write_byte(0x44);resert();write_byte(0xcc);write_byte(0xbe);TMPL = read_byte();TMPH = read_byte();temp = TMPH;temp <<= 8;TMPL=TMPL&0xf0;temp = temp | TMPL;f_temp=temp*0.0625;temp=f_temp;return temp;}。

51单片机实战指南-使用DS1302设计数字时钟

YEAR

WP

0

0

0 0000

本章内容:

1

DS1302芯片介绍

22 封装的编程思想和结构体类型

3 2

DS1302读写操作的编程实现

4

DS1302读写实战

12.2.1 封装的编程思想

➢ 封装是面向对象编程三大特性(封装、继承、多态)之一 ➢ 核心思想就是尽可能地隐藏内部的细节,只保留一些对外接

口使之与外部发生联系 ➢ 就C语言而言,封装的体现就是函数的编写(小封装)和模

} DS1302_CE = 0;

//传送数据结束

return dat;

}

12.3.2 读写函数的封装-DS1302WriteByte

/* 发送一个字节到DS1302通信总线上 */

void DS1302WriteByte(unsigned char dat)

{

unsigned char i;

for (i=0; i<8; i++)

bit 5

bit 4

bit 3

bit 2

bit 1

bit 0

1

RAM/CK A4

A3

A2

A1

A0

R/W

寄存器名

秒寄存器 分钟寄存器 小时寄存器 日期寄存器 月份寄存器 星期寄存器 年份寄存器 控制寄存器

命令字

写操作 读操作

80H

81H

82H

83H

84H

85H

86H

87H

88H

89H

8AH 8BH

8CH 8DH

12.4 DS1302读写实战-ds1302.c

void mai时间后会刷新显示

基于单片机及时钟芯片DS1302的电子时钟设计

基于单片机及时钟芯片DS1302的电子时钟设计一、概述二、电子时钟的基本原理电子时钟是一种以单片机为核心的智能电子产品,采用数字电路来显示时间。

电子时钟的核心部件是一个定时器,通过周期性的计数来确定时间,然后再将计数器的结果通过数码管等显示装置进行显示。

除此之外,电子时钟还需要一个能够准确计时的时钟芯片,如本文所使用的时钟芯片DS1302。

三、电子时钟的设计方法本文设计的电子时钟采用AT89C52单片机和时钟芯片DS1302,并通过外围的驱动电路和数码管来实现时间的显示。

该电子时钟具有以下特点:1.可进行24小时制和12小时制的切换:电子时钟可以通过按键实现24小时制和12小时制的切换,可按需选择。

2.自动夏令时判断:电子时钟可自动识别夏令时,并根据设定值进行切换,方便易用。

3.温度显示:电子时钟的DS1302时钟芯片自带温度探测器,可实现温度的实时显示。

本文所设计的电子时钟的硬件设计方案如下:1.主控芯片:采用AT89C52单片机2.显示装置:采用数码管进行时分秒的显示,共4位数码管。

3.时钟芯片:采用DS1302时钟芯片,保证时间的准确性。

5.电源:采用开关电源或锂电池供电。

锂电池供电时,电子时钟可实现断电后不重置的功能。

1.初始化:在电子时钟启动时,需要对各个模块进行初始化,如DS1302时钟芯片的读写口、数码管和按键都需要进行初始化。

2.频率切换:按下切换按键后,电子时钟的频率从24小时制切换到12小时制。

3.设定夏令时:按下设定按键后,可以进行夏令时设定。

设定值以秒为单位存储,在夏季过渡期改变时,只需修改设定值即可。

5.时间的显示:通过程序将DS1302时钟芯片中的时间读出并在数码管上显示,实现实时显示的功能。

五、总结本文设计的基于单片机及时钟芯片DS1302的电子时钟,可通过按键实现24小时制和12小时制的切换、自动夏令时判断、温度显示等多种功能,实现了电子时钟的多种要求和需求。

该设计方案具有简单实用、成本低廉、易于维护等优点,可广泛应用于各个领域。

基于MCS-51单片机的实时时钟芯片DS1302设计

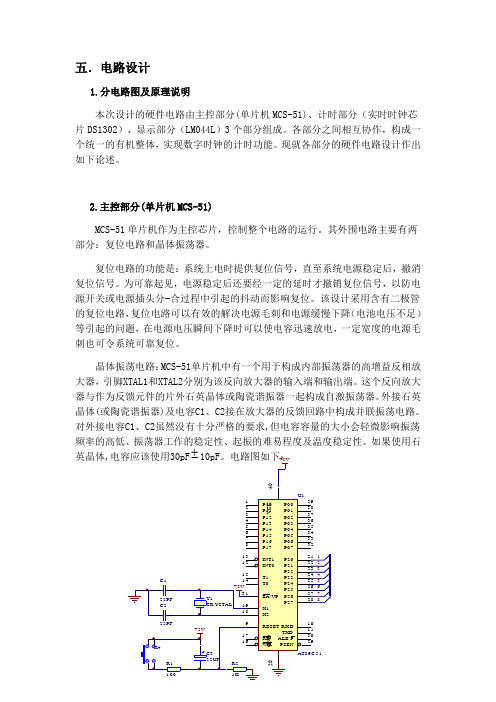

五.电路设计1.分电路图及原理说明本次设计的硬件电路由主控部分(单片机MCS-51)、计时部分(实时时钟芯片DS1302)、显示部分(LM044L )3个部分组成。

各部分之间相互协作,构成一个统一的有机整体,实现数字时钟的计时功能。

现就各部分的硬件电路设计作出如下论述。

2.主控部分(单片机MCS-51)MCS-51单片机作为主控芯片,控制整个电路的运行。

其外围电路主要有两部分:复位电路和晶体振荡器。

复位电路的功能是:系统上电时提供复位信号,直至系统电源稳定后,撤消复位信号。

为可靠起见,电源稳定后还要经一定的延时才撤销复位信号,以防电源开关或电源插头分-合过程中引起的抖动而影响复位。

该设计采用含有二极管的复位电路,复位电路可以有效的解决电源毛刺和电源缓慢下降(电池电压不足)等引起的问题,在电源电压瞬间下降时可以使电容迅速放电,一定宽度的电源毛刺也可令系统可靠复位。

晶体振荡电路:MCS-51单片机中有一个用于构成内部振荡器的高增益反相放大器,引脚XTAL1和XTAL2分别为该反向放大器的输入端和输出端。

这个反向放大器与作为反馈元件的片外石英晶体或陶瓷谐振器一起构成自激振荡器。

外接石英晶体(或陶瓷谐振器)及电容C1、C2接在放大器的反馈回路中构成并联振荡电路。

对外接电容C1、C2虽然没有十分严格的要求,但电容容量的大小会轻微影响振荡频率的高低、振荡器工作的稳定性、起振的难易程度及温度稳定性。

如果使用石英晶体,电容应该使用30pF 10pF 。

电路图如下:EA/VP 31X119X218RESET 9RD 17W R 16INT012INT113T014T115P101P112P123P134P145P156P167P178P0039P0138P0237P0336P0435P0534P0633P0732P2021P2122P2223P2324P2425P2526P2627P2728PSEN29ALE/P 30TXD11RX D10V C C40G N D 20U1AT89C 51Y1CR YSTALC222PFC122PF K4R1100C322UFR21K+5V23456781+5V +5V图5主控部分电路图3. 计时部分(实时时钟芯片DS1302)时钟芯片DS1302与外围电路的连接:与MCS-51单片机的接口是由3条线来完成的,MCS-51单片机的P1.0与时钟芯片的数据传输端I/O 相连,P1.1用来作为DS1302输入时钟SCLK 控制端,P1.2控制DS1302的复位输入端RST 。

基于51单片机的实时时钟芯片DS1302

K_on LED1 LED2 LED3CLK LED4IO RST

BIT P3.0 BIT P3.3 BIT P3.4 BIT P3.5 BIT P3.7 BIT P3.1

;闹铃输出 ;DS1302

SECOND EQU 60H

;60H 秒

;61h 分

;62h 时

;63h 日

;64h 月

;65h DAY

;200Us ; ;display LED

MOV R2,#00H

;

MOV R3,#00H

;

MOV TMOD,#12H MOV TL1,#0e5H MOV TH1,#0BeH MOV TH0,#3FH MOV TL0,#3FH SETB ET0 SETB ET1 setb pt0 SETB TR0 SETB TR1 SETB IT0 SETB EX0 CLR PX0 ;LCALL SET1302 MOV R1,#0C1H acall T_6061 MOV 6AH,A MOV R1,#0C3H ACALL T_6061

;定时到时,显示闪

MOV C,07H MOV acc.7,C ;秒灯闪

段表

mov dptr,#tab2

MOV ANL MOV MOV SWAP ANL

A,61H A,#0FH B,A A,61H A A,#0FH

MOVC A,@A+DPTR

烁 MOV P1,A CLR LED3CLK LCALL DL2M SETB LED3CLK

MOV A,62H ANL A,#0FH MOV B,A MOV A,62H SWAP A ANL A,#07H MOVC A,@A+DPTR MOV P1,A CLR LED1 LCALL DL2M SETB LED1 MOV A,B MOVC A,@A+DPTR

基于ds1302的51单片机简易实时时钟-1602显示-源程序

==================主程序================= #include <reg51.h>。

#include "ds1302.h"#include "LCD1602.h"void change();uchar times[9];uchar date[9];main(){LCD_init();//LCD初始化init_1302(time_1302);gotoxy(1,1);LCD_display("Time:");gotoxy(1,2);LCD_display("Date:");times[8]='\0';//date[8]='\0';while(1){get_1302(time_1302);change();gotoxy(7,1);LCD_display(times);gotoxy(7,2);LCD_display(date);}}/*=========================== 转换子程序===========================*/void change(){// 时间的转换times[0]=time_1302[2]/10+'0';times[1]=time_1302[2]%10+'0';times[2]=':';times[3]=time_1302[1]/10+'0';times[4]=time_1302[1]%10+'0';times[5]=':';times[6]=time_1302[0]/10+'0';times[7]=time_1302[0]%10+'0';// 日期的转换date[0]=time_1302[6]/10+'0';date[1]=time_1302[6]%10+'0';date[2]='-';date[3]=time_1302[4]/10+'0';date[4]=time_1302[4]%10+'0';date[5]='-';date[6]=time_1302[3]/10+'0';date[7]=time_1302[3]%10+'0';}======================================================DS1302驱动程序=============#define uchar unsigned charuchar time_1302[7]={0x00,0x00,0x00,0x03,0x07,0x03,0x08};//设置时间初始值数组// 秒分时号月份星期年sbit T_IO=P1^0; //与硬件相关的连线clk为DS1302的时钟信号线sbit T_CLK=P1^1; //DAT为DS1302的I/O数据线sbit T_RST=P1^2; //RST为DS1302的RST信号线uchar bdata datbyte;sbit datbyte0=datbyte^0;sbit datbyte7=datbyte^7;void get_1302(uchar time[]);void write_ds1302(uchar dat);uchar r_1302(uchar add);void w_1302(uchar add,uchar dat);uchar read_ds1302(void);void init_1302(uchar *time);/*==========================================D S 1 3 0 2 初始化===========================================*/void init_1302(uchar *time){uchar i, add;//uchar time_bcd[7];add=0x80;//0写入,1读出w_1302(0x8e,0x00);for(i=0;i<7;i++){w_1302(add,*time);add+=2;time++;}w_1302(0x8e,0x80);}//===========================// 读取当前时间//===========================void get_1302(uchar time[]){uchar i;uchar add=0x81;w_1302(0x8e,0x00);for(i=0;i<7;i++){time[i]=r_1302(add);add+=2;}w_1302(0x8e,0x80);}/*================================= DS1302写入一个字节(上升沿有效)=================================*/void write_ds1302(uchar dat){uchar i;datbyte=dat;for(i=0;i<8;i++){T_IO=datbyte0;T_CLK=1;T_CLK=0;datbyte=datbyte>>1;}}/*======================================= DS1302读取一个字节(下降沿有效)=======================================*/uchar read_ds1302(void){uchar i;for(i=0;i<8;i++){datbyte=datbyte>>1;datbyte7=T_IO;T_CLK=1;T_CLK=0;}return(datbyte);}/*========================================= 指定位置读取数据=========================================*/uchar r_1302(uchar add){uchar temp,dat1,dat2;T_RST=0;T_CLK=0;T_RST=1;write_ds1302(add);temp=read_ds1302();T_CLK=1;T_RST=0;dat1=temp/16;dat2=temp%16;temp=dat1*10+dat2;return(temp);}/*========================================== 指定位置写入数据==========================================*/void w_1302(uchar add,uchar dat){T_RST=0;T_CLK=0;T_RST=1;write_ds1302(add);write_ds1302(dat/10<<4|dat%10);T_CLK=1;T_RST=0;}=========================================== =============LCD1602驱动程序================#define LCD_DB P0//定义LCD的数据端口sbit LCD_RS=P2^0;sbit LCD_RW=P2^1;sbit LCD_E=P2^2;#define uchar unsigned char#define uint unsigned int//===========延时子函数======================== void delay_lcd(uint x){uint i,j;for(i=x;i>0;i--)for(j=0;j<2;j++);}//==================写指令函数================= void LCD_write_command(uchar command){LCD_DB=command;LCD_RS=0;//指令LCD_RW=0;//写入LCD_E=1;LCD_E=0;delay_lcd(1);//等待执行完毕。

基于DS1302和51单片机的电子时钟设计.

目录第一章系统介绍 (2)1.1电子钟介绍 (2)1.2单片机AT89C51介绍 (2)1.3时钟芯片DS1302简介 (5)1.3.1 主要功能 (5)1.3.2 内部结构及引脚功能 (5)1.3.3 工作原理 (6)1.3.4 控制字节及寄存器 (6)1.3.5 时钟/日历存储区(时分秒) (7)1.3.6 数据的传送 (7)第二章硬件设计 (8)2.1系统结构及总流程图 (8)2.2系统硬件电路设计图 (9)2.2.1整体电路设计 (9)2.2.2 DS1302电路设计 (9)2.2.3 按键电路 (10)2.2.4 显示电路 (10)第三章、程序源代码 (11)3.1程序流程图 (11)3.1源程序 (12)第四章PROTEUS软件仿真 (18)总结 (19)谢辞 (20)参考文献 (21)第一章系统介绍1.1 电子钟介绍电子钟已成为人们日常生活中的必需品,广泛应用于家庭、车站、办公室等场所。

钟表数字化给人们生产生活带来了极大地方便而且大大地扩展了钟表原先的报时功能诸如定时自动报警、按时自动打铃、时间程序自动控制、通断动力设备、甚至各种定时电气的自动启用,因此研究数字钟及扩大其应用有着非常现实的意义。

数字电子钟设计与制作可采用数字电路实现,也可以采用单片机来完成。

若用数字电路完成,所设计的电路相当复杂,大概需要十几片数字集成块,其功能也主要依赖于数字电路的各功能模块的组合来实现,焊接的过程比较复杂,成本也非常高。

若用单片机来设计制作完成,由于其功能的实现主要通过软件编程来完成,那么就降低了硬件电路的复杂性,而且其成本也有所降低。

截止今日,单片机应用技术飞速发展,纵观现在各个领域,从导弹的导航装置,到飞机上各种仪表的控制,从计算机的网络通讯与数据传输,到工业自动化过程的实时控制和数据处理,以及我们生活中广泛使用的各种智能IC卡、电子宠物等,这些都离不开单片机。

单片机即单片微型计算机(Single-Chip Microcomputer ),是集CPU ,RAM ,ROM ,定时,计数和多种接口于一体的微控制器。

基于MCS-51和DS1302时钟电路设计

基于MCS-51和DS1302时钟电路设计摘要随着现代科技的快速发展,时间的不断流逝,从观太阳、摆钟到现在的电子时钟,人类凭借非凡的智慧不断研究又创造出新的纪录。

美国Dallas公司推出了一种具有涓细电流充电能能力的低功耗实时时钟芯片DS1302,可以对年、月、日、星期、时、分、秒进行计时,还具有闰年补偿等多种功能,而且DS1302的使用寿命长,误差小。

本设计采用AT89C51单片机作为控制器,功耗小,电压可选用4.5-5.5V供电。

用8位数码管显示年月日也比较直观。

再运用Proteus仿真平台将硬件电路和软件程序结合起来测试验证,最终完成时钟电路设计。

综上所述本文对时钟电路设计的研究具有读取方便、显示直观、功能多样、电路简单、成本低廉优点,符合电子仪器仪表的发展趋势,具有广阔的市场前景。

关键字:时钟,单片机,DS1302,Proteus目录摘要 (I)目录 (II)1 绪论 (1)1.1课题研究背景 (1)1.2 课题研究的目的与意义 (1)1.3 课题主要研究内容 (1)2 系统设计方案 (2)2.1 单片机芯片选择 (2)2.2 显示模块的选择 (3)2.3 时钟模块的选择 (3)3 硬件电路设计 (3)3.1 电路结构框图 (3)3.2 单片机最小系统设计 (4)3.3 时钟模块电路设计 (5)3.4 显示模块电路设计 (8)4 软件程序设计 (9)5 仿真系统设计 (10)结论 (12)致谢 (13)参考文献 (14)1 绪论1.1课题研究背景万年历在我国已有一千多年的历史,相传为商朝的万年所创,为纪念他的功绩而将该历法命名为“万年历”。

万年历古时通称时宪书或通书,是按照某一特定历法的推算法则编排年、月、日、节气等以供查考的工具书,是人类创造的文化成果之一。

据文学记载,历书大约在距今1100多年前,就已经在中国出现了。

帝制年代,它是皇帝的“垄断品”,所以历书又叫“皇历”。

但真正古老的历书产生于唐顺宗永贞元年(公元805年),之后又包含干支、月令、节气以及各种忌日、星相吉凶、符咒、卜卦等内容。

基于51单片机和时钟芯片DS1302的数字时钟设计 2

基于51单片机和DS1302数字时钟硬件总体设计说明书编制单位:*****作者:*****版本:V1.0发布日期:2011-2-12目录一、引言-----------------------------------------------11.1编写目的-----------------------------------------11.2背景---------------------------------------------11.3参考资料-----------------------------------------1二、总体设计--------------------------------------------32.1设计与运行环境------------------------------------32.2硬件功能描述--------------------------------------3三、数字钟软件和硬件设计-------------------------------33.1 硬件电路设计-------------------------------------33.2软件设计--------------------------------------------63.2.2 源程序--------------------------------------8四、数字钟制作过程中遇到的问题-------------------------19五、总结-----------------------------------------------20附录Ⅰ:DS1302时钟芯片的工作原理和使用方法-----------22 附录Ⅱ:如何利用软件减小的计时误差--------------------25一、引言1.1编写目的为了进一步熟悉51单片机的编程以及学习数字钟的相关设计方法,在老师的指导下我们进行了本次数字钟的设计。

(完整版)基于51系列单片机及DS1302时钟芯片的电子时钟_C语言毕业论文

实时时钟DS1302应用设计高也(陕西理工学院物理与电信工程学院电子信息工程专业,2011级3班,陕西汉中723000)指导教师:王文洋[摘要] 本设计主要为实现一款可正常显示时钟日历、带有定时闹铃的多功能电子时钟。

本文对当前电子钟开发手段进行了比较和分析,最终确定了采用单片机技术实现多功能电子时钟。

本设计应用AT89C52芯片作为核心,LM016L液晶屏显示,使用DS1302实时时钟日历芯片完成时钟日历的基本功能。

这种实现方法的优点是电路简单,性能可靠,实时性好,时间精确,操作简单,编程容易。

[关键词] AT89C52;DS1302;LM016L目录1、基于单片机的电子时钟硬件选择分析..............................................................................1.1主要IC芯片选择.......................................................................................................1.1.1微处理器选择.................................................................................................1.1.2 DS1302简介...................................................................................................2、电子时钟硬件电路设计......................................................................................................2.1.主控部分(单片机MCS-51).......................................................................................2.2时钟电路设计.............................................................................................................2.3整点报时功能.............................................................................................................2.4 LED显示电路.............................................................................................................3、proteus软件仿真及调试 (1)3.1电路板的仿真 (1)3.2软件调试....................................................................................................................4、硬件调试与功能说明 (1)4.1 硬盘调试 (1)4.2 系统性能测试与功能说明 (1)4.3 系统时钟误差分析 (1)5、课设心得 (1)参考文献 (1)附录A 硬件电路原理图 (1)附录B源程序 (1)附录C 元器件清单 (2)1、基于单片机的电子时钟硬件选择分析考虑单片机货源充足、价格低廉,可软硬件结合使用,能够较方便的实现系统的多功能性,故采用单片机作为本设计的硬件基础。

基于51单片机DS1302万年历课程设计报告

课程名称:微机原理课程设计题目:基于DS1302芯片万年历摘要DS1302 是DALLAS 公司推出的涓流充电时钟芯片,内含有一个实时时钟/日历和31 字节静态RAM,通过简单的串行接口与单片机进行通信实时时钟/日历电路.提供秒、分、时、日、日期.、月、年的信息,每月的天数和闰年的天数可自动调整时钟。

本次课程设计的是使用专门的时钟芯片DS1302在数码管上显示的数字电子钟,并能通过按键对其进行调时和校准以及实现年月日。

DS1302是一种高性能、低功耗、带RAM的实时时钟芯片,它能够对时,分,秒进行精确计时,它与单片机的接口使用同步串行通信,仅用3条线与之相连接,就可以实现STC-51单片机对其进行读写操作,把读出的时间数据送到数码管上显示。

程序运行时,数码管将从当前时间开始显示,通过调节K2键和K3键可以分别对小时和分钟进行调整,调整后,时钟以新的时间为起点继续刷新显示,通过调节K1键可以切换年月日和时钟显示。

关键字:STC-51单片机,DS1302,数码管,动态扫描,调时,切换,秒闪;目录一、设计任务与要求 (4)1.1设计任务 (4)1.2设计要求 (4)1.3发挥部分 (4)1.4创新部分 (4)二、方案总体设计 (5)2.1设计目的 (5)2.2硬件功能描述 (5)2.3设计方案选择 (5)2.4总体设计 (6)2.5总体方案及基本工作原理 (6)三、硬件设计 (7)3.1 STC89C51芯片 (7)3.2电源模块及晶振模块 (7)3.3 DS1302 (8)3.4数码管显示模块 (9)3.5蜂鸣器部分 (10)3.6按键部分 (11)四、软件设计 (13)4.1软件流程图 (13)4.2 软件设计 (13)主函数部分: (13)五、系统仿真和调试 (15)5.1 仿真软件简介 (15)5.2硬件调试 (15)5.3软件调试 (15)5.4使用说明 (16)六、设计总结与体会 (18)6.1学习方面 (18)6.2工作方面 (18)七、参考文献 (19)一、设计任务与要求1.1设计任务DS1302万年历;1.2设计要求利用DS1302生成万年历,时钟可调,通过四位数码管显示,并可实现秒闪功能,同时蜂鸣器闹铃;1.3发挥部分设置按键K3用来切换显示时钟和年月日;1.4创新部分只设置了两个按键K1和K2来调节时分,时钟到24归零,分钟到60归零,分钟有长按迅速调节功能。

基于51单片机的多功能电子时钟设计

设计研发2021.07基于51单片机的多功能电子时钟设计杨洁,叶晶晶(黔南民族师范学院物理与电子科学学院,贵州都匀,558000 )摘要:单片机体积小、重量轻、抗干扰能力强、环境要求不高、价格低廉、可靠性高、灵活性好、深受初学者喜欢。

以STC90C58为核心控制芯片,DS1302为时钟芯片,DS18B20釆集温度,完成多功能电子时钟的设计。

该设计能够准确显示年、月、日、星期、时、分、秒及温度,通过按键可以调整年、月、日、星期、时、分、秒、12/24小时转换、整点提示以及闹钟,还可显示阴阳历。

关键词:电子时钟;单片机;阴阳历转换;DS1302 ; DS18B20Design of Multi-function Clock Based on 51 MCUYang Jie, Ye Jingjing(College of physics and electronic science, Qiannan Normal University for N&tionalities, DuyunGuizhou, 558000)Abstract : MCU is small in size, light in weight, strong in anti-interference ability, low in environmentai requirements, low in price, high in reliability, good in flexibility, and is popular among beginners. Stc90c58 as the core control chip, DS1302 as the clock chip, DS18B20 temperature acquisition, complete the design of multi —functional electronic clock. The design can accurately display the year, month, day, week, hour, minute, second and temperatore. Through the button, you can adjust the year, month, day, week, hour, minute, second, 12/24-hour conversion, whole point prompt and alarm clock, and display the lunar calendar.Keywords : Electronic clock ; MCU ; The lunar conversion ; DS 1302 ; DS18B200引言目前单片机的使用已经十分广泛,本次设计的多功能电 子钟能完成年、月、日、星期、时、分、秒的显示与调整,并且还 添加了温度、阴阳历转换显示及闹钟、12/24小时转换、整点提示等功能,有较强的应用性。

电子时钟设计(DS1302)简述基于51单片机

安康学院单片机课程设计报告书课题名称:电子时钟的设计(DS1302)姓名:学号:院系:电子与信息工程系专业:电子信息工程指导教师:时间:2012年6月设计项目成绩评定表设计报告书目录一、设计目的 (1)二、设计思路 (1)三、设计过程 (1)3.1系统设计结构图 (1)3.2 MCU微控制器电路 (2)3.3 LCD液晶显示电路 (4)3.4 实时时钟电路 (5)3.5 复位电路 (5)3.6 晶振电路 (6)四、系统调试与结果 (6)五、主要元器件与设备 (6)六、课程设计体会 (7)七、参考文献 (7)一、设计目的1、掌握电子时钟的基本工作方式。

2、进一步熟悉DS1302芯片的特性。

3、通过使用各基本指令,进一步熟练掌握单片机的编程和程序调试。

二、设计思路利用AT89C52的特点及DS1302的特点,设计一种基于DS1302单片机控制,再利用数码管显示的数字钟。

本系统硬件利用AT89S52作为CPU进行总体控制,通过DS1302时钟芯片获取准确详细的时间(年、月、日、周、日、时、分、秒准确时间),对时钟信号进行控制,同时利用液晶显示芯片LCD1602对时间进行准确显示年、月、日、周、日、时、分、秒。

三、设计过程3.1系统设计结构图图1系统设计结构图图2 系统软件流程图根据系统设计的要求和设计思路,确定该系统的系统设计结构图。

如图1所示。

硬件电路主要由MCU微处理控制器单元、DS1302时钟电路、储存器、复位电路、晶振电路、数码管显示模块构成。

3.2MCU微控制器电路AT89S52作为系统的核心控制元件,只有它能正常工作后才能使其它的元件进入正常工作状态。

因此,下面对AT89S52进行必要的说明,AT89S52的管脚如图3所示。

图3 AT89S52的管脚1)VCC:40脚,供电电压,一般接+5V电压。

2)GND:20脚,接工作地。

3)P0口:1~8脚,P0口是一个8位漏极开路的双向I/O口。

作为输出口,每位能驱动8个TTL逻辑电平。

基于51单片机和DS1302的电子万年历设计论文

1 引言随着科技的不断进步和发展,单片机的使用已经渗透到我们日常生活当中的各个领域,几乎很难找到有哪个领域没有使用单片机的踪迹。

导弹的导航装置,飞机上各种仪表的控制,计算机的网络通讯与数据传输,工业自动化过程的实时控制和数据处理,广泛使用的各种智能IC卡,民用豪华轿车的安全保障系统,录相机、摄像机、全自动洗衣机的控制,以及程控玩具、电子宠物等等,这些都离不开单片机。

更不用说自动控制领域的机器人、智能仪表、医疗器械了。

本文设计的电子万年历属于小型智能家用电子产品。

利用单片机进行控制,实时时钟芯片进行记时,外加掉电存储电路和显示电路,可实现时间的调整和显示。

电子万年历既可广泛应用于家庭,也可应用于银行、邮电、宾馆、饭店、医院、学校、企业、商店等相关行业的大厅,以及单位会议室、门卫等场所。

因而,此设计具有相当重要的现实意义和实用价值。

1.2方案选择由于现在市面上的电子万年历的种类比较多,因此到底选择什么样的方案在设计中是至关重要的。

正确地选择方案就可以使产品更加人性化,并且可以减小开发的难度,缩短开发的周期,降低产品的成本等等,因此就会被人们普遍接受,并且能够更快地将产品推向市场实现其自身的价值。

下面我们就拟订了两种方案,希望能够选择一种性价比高的方案。

1.2.1 方案1——基于AT89S52单片机的电子万年历设计不使用时钟芯片,而直接用AT89S52单片机来实现电子万年历设计。

AT89S52是一种带8K字节闪烁可编程可擦除只读存储器的低电压,高性能CMOS 8位微处理器,俗称单片机。

单片机的可擦除只读存储器可以反复擦写1000余次。

由于将多功能8位CPU和闪烁存储器组合在单个芯片中,ATMEL的AT89S52是一种高效微控制器,为很多嵌入式控制系统提供了一种灵活性高且价廉的方案。

若采用单片机计时,利用它的一个16位定时器/计数器每50ms产生一个中断信号,中断20次后产生一个秒信号,然后根据时间进制关系依次向分、时、日、星期、月、年进位。

基于51单片机的电子时钟设计

基于51单片机的电子时钟设计

电子时钟是一种使用电子元件和计算机技术制造的时计,它可以显示年、月、日、时、分、秒等时间信息,并且具有显示精确、功能齐全、操

作简便等特点。

本文将基于51单片机设计一个电子时钟。

一、硬件设计:

1.时钟模块:我们可以使用DS1302时钟模块作为实时时钟芯片,它

可以提供精确的时间信息,并且可以通过单片机与之进行通信。

2.显示模块:我们可以使用共阳数码管进行时间的显示,将时钟设计

成6位7段显示器。

3.按键模块:我们可以使用按键作为输入方式,通过按键调整时间信息。

二、软件设计:

1.初始化:首先,我们需要初始化时钟模块和显示模块,使它们正常

工作。

同时,设置时钟的初始时间为系统当前时间。

2.获取时间:通过与时钟模块的通信,获取当前的时间信息,包括年、月、日、时、分、秒等。

3.显示时间:将获取到的时间信息通过显示模块显示出来,分别显示

在6个数码管上。

4.时间调整:通过按键模块的输入,判断用户是否需要调整时间。

如

果需要,可以通过按键的不同组合来调整时、分、秒等时间信息。

5.刷新显示:通过不断更新显示模块的输入信号来实现时钟的流动性,保持秒针不断运动的效果。

6.时间保存:为了保证时钟断电后依然能够保持时间,我们需要将时

钟模块获取到的时间信息保存在特定的EEPROM中。

7.闹钟功能:可以通过按键设置闹钟,当到达闹钟时间时,会通过蜂

鸣器发出响声。

以上就是基于51单片机的电子时钟设计方案。

通过对硬件和软件的

综合设计,我们可以实现一个功能齐全的电子时钟。

基于51单片机的实时时钟DS1302

基于51单片机的DS1302实时时钟本讲内容:介绍DS1302实时时钟芯片基本知识,演示DS1302例程。

DS1302实时时钟:DS1302能提供包括秒、分、时、日期、月份和年份信息。

闰年可自行调整,可选择12小时制和24小时制,可以设置AM、PM。

只通过三根线进行数据的控制和传递:/RST、I/O、SCLK。

通过备用电源可以让芯片在小于1mw的功率下运作。

DS1302是总线驱动方式,它不仅要向寄存器写入控制字,还需要读取相应寄存器的数据。

要想与DS1302通信,首先要先了解DS1302的控制字。

DS1302的控制字如图:位7:必须是逻辑1,如果它为0,则不能把数据写入到DS1302中。

位6:如果为0,则表示存取日历时钟数据,为1表示存取RAM 数据。

位5至位1(A4~A0):指示操作单元的地址。

位0:为1表示进行读操作,为0表示要进行写操作,控制字后SCLK下降沿读数据,SCLK上升沿写数据。

数据是低位在前,高位在后。

读数据:读数据时在紧跟8位的控制字指令后的下一个SCLK脉冲的下降沿,读出DS1302的数据,读出的数据是从最低位到最高位。

写数据:写数据时在紧跟8位的控制字指令后的下一个SCLK脉冲的上升沿,数据被写入DS1302,数据输入也是从最低位(0位)开始。

DS1302的数据读写是通过I/O串行进行的。

当进行一次读写操作时最少要读写两个字节。

第一个字节是控制字节,就是一个命令,告诉DS1302是读还是写操作,是对RAM还是对CLOCK寄存器操作,以及操作的地址。

第二个字节就是要读或写的数据了。

单字节写:在进行操作之前先将CE(也可说是RST)置高电平,然后单片机将控制字的位0放到I/O上,当I/O的数据稳定后,将SCLK置高电平,DS1302检测到SCLK的上升沿后就将I/O上的数据读取,然后单片机将SCLK置为低电平,再将控制字的位1放到I/O上,如此反复,将一个字节控制字的8个位传给DS1302。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

安康学院单片机课程设计报告书课题名称:电子时钟的设计(DS1302)姓名:学号:院系:电子与信息工程系专业:电子信息工程指导教师:时间:2012年6月课程设计项目成绩评定表设计项目成绩评定表课程设计报告书目录设计报告书目录一、设计目的 (1)二、设计思路 (1)三、设计过程 (1)3.1系统设计结构图 (1)3.2 MCU微控制器电路 (2)3.3 LCD液晶显示电路 (4)3.4 实时时钟电路 (5)3.5 复位电路 (5)3.6 晶振电路 (6)四、系统调试与结果 (6)五、主要元器件与设备 (6)六、课程设计体会 (7)七、参考文献 (7)一、设计目的1、掌握电子时钟的基本工作方式。

2、进一步熟悉DS1302芯片的特性。

3、通过使用各基本指令,进一步熟练掌握单片机的编程和程序调试。

二、设计思路利用AT89C52的特点及DS1302的特点,设计一种基于DS1302单片机控制,再利用数码管显示的数字钟。

本系统硬件利用AT89S52作为CPU进行总体控制,通过DS1302时钟芯片获取准确详细的时间(年、月、日、周、日、时、分、秒准确时间),对时钟信号进行控制,同时利用液晶显示芯片LCD1602对时间进行准确显示年、月、日、周、日、时、分、秒。

三、设计过程3.1系统设计结构图图1系统设计结构图图2 系统软件流程图根据系统设计的要求和设计思路,确定该系统的系统设计结构图。

如图1所示。

硬件电路主要由MCU微处理控制器单元、DS1302时钟电路、储存器、复位电路、晶振电路、数码管显示模块构成。

3.2MCU微控制器电路AT89S52作为系统的核心控制元件,只有它能正常工作后才能使其它的元件进入正常工作状态。

因此,下面对AT89S52进行必要的说明,AT89S52的管脚如图3所示。

图3 AT89S52的管脚1)VCC:40脚,供电电压,一般接+5V电压。

2)GND:20脚,接工作地。

3)P0口:1~8脚,P0口是一个8位漏极开路的双向I/O口。

作为输出口,每位能驱动8个TTL逻辑电平。

对P0端口写“1”时,引脚用作高阻抗输入。

当访问外部程序和数据存储器时,P0口也被作为低8位地址/数据复用。

在这种模式下,P0具有内部上电阻。

但是P0口在程序校验作为输出指令字节时,需要外部加上拉电阻,一般上拉电阻选4.7K~10K为宜。

本设计中用5.1K的排阻对P0口进行上拉电平。

4)P1口:32~39脚,P1口是一个内部具有上拉电阻的8位双向I/O口,P1口缓冲器能接收输出4个TTL门电流。

P1端口写入“1”后,被内部上拉电阻把端口拉高,此时可以作为作输入口使用。

作为输入使用时,被外部拉低的引脚由于内部电阻的原因,将输出电流。

5)P2口:20~27脚,P2 口是一个具有内部上拉电阻的8 位双向I/O 口,P2 输出缓冲器能驱动4 个TTL 逻辑电平。

对P2 端口写“1”时,内部上拉电阻把端口拉高,此时可以作为输入口使用。

6)P3口:10~17脚,P3 口是一个具有内部上拉电阻的8 位双向I/O 口,P3 输出缓冲器能驱动4 个TTL 逻辑电平。

对P3 端口写“1”时,内部上拉电阻把端口拉高,此时可以作为输入口使用。

7)RESET:9脚,复位输入端。

当振荡器复位器件时,要保持RST脚两个机器周期的高电平时间。

8)ALE/P非:30脚,当访问外部存储器时,地址锁存允许的输出电平用于锁存地址的地位字节。

在FLASH编程期间,此引脚用于输入编程脉冲。

在平时,ALE 端以不变的频率周期输出正脉冲信号,此频率为振荡器频率的1/6。

因此它可用作对外部输出的脉冲或用于系统校验。

9)PSEN:29脚,外部程序存储器的选通信号。

10)RST非/VP:31脚,访问外部程序存储器控制信号。

当EA非为低电平时,读取外部程序存储器;当EA非端为高电平时,则读取内部程序存储器,设计中一般接高电平。

11)XTAL1:19脚,振荡器反相放大器和内部时钟发生电路的输入端。

如采用外部时钟源时,XTAL1为输入端。

12)XTAL2:18脚,振荡器反相放大器的输出端。

如采用外部时钟源时,XTAL2 应悬空不接。

3.3 LCD液晶显示电路液晶显示器以其微功耗、体积小、显示内容丰富、超薄轻巧的诸多优点,在各种小系统中得到了更广泛的应用。

本设计中使用的液晶显示模块是LCD1602。

图4所示为本设计LCD1602的连接图。

图4 LCD1602的连接图本设计使用的实时时钟电路芯片是美国DALLAS公司生产的一种高性能、低功耗、带RAM的实时时钟电路芯片DS1302。

VCC1为后备电源,VCC2为主电源。

在主电源关闭的情况下,也能保持时钟的连续运行。

DS1302由VCC1或VCC2两者中的较大者供电;当VCC2大于VCC1+0.2V时,VCC2给DS1302供电;当VCC2小于VCC1时,DS1302由VCC1供电。

X1和X2是振荡源,外接32.768kHz晶振。

RST非是复位/片选线,通过把RST非输入驱动置高电平来启动所有的数据传送。

图5 时钟电路3.5复位电路在AT89S52单片机中的振荡器运行时,RST非引脚上保持到少2个机器周期的高电平输入信号,复位过程即可完成。

根据此原理,本设计采用上电复位和按键复位嵌套在系统中,增强了系统的实用性。

本设计的具体复位图如下。

图6 复位电路AT89S52在工作时需要外部提供时钟信号,因此,本设计选择在其18脚19脚之间接上12MHz的晶振,为单片机提供1μs的机器振荡周期。

其电路连接图如图所示。

在图中,电容器C3、C4起稳定振荡频率、快速起振的作用,其电容值一般在20~50pF。

图7 晶振电路四、系统调试与结果系统调试过程利用Proteus绘制出相应硬件电路后进行仿真,出现液晶显示无法正常显示的问题。

经过思考和查阅的资料发现AT89C52的P0在进高电平时没有接上拉电阻导致LCD1602无法正常显示时间。

修改电路后(P0口接上拉电阻)烧入程序后,程序正常运行,LCD1602准确的显示。

用Proteus仿真能够正确的现实时间,但烧入学习板出现乱码现实不能正常工作。

经过反复检查及思考发现仿真软件上的硬件电路与学习板上的硬件电路不一致无法对应起来。

最后根据学习板的硬件电路修改相应程序及仿真软件上的硬件电路,最终现实了功能。

系统调试结果图8 调试结果五、主要元器件与设备Protues软件、AT89C512芯片、DS1302芯片及各电路模块六、课程设计体会本设计利用单片机AT89C512控制串行实时时钟芯DS1302构成数字时钟电路,实现计时功能。

该电路使用简单的三线接口,为单片机节省大量的接口资源,时钟芯片带有后备电池。

该时钟功能强大,性能优越,能为很多领域,特别是对时钟工作的准确性和可靠性有较高要求。

通过对电子时钟的设计的设计与制作,让我了解了电子时钟模块的编程思想,也让我明白了电子时钟的基本原理与设计理念,要设计一个电路必须先编好程序,用仿真软件测试成功后再得出结论。

通过这次学习,让我对该软件有了更熟悉的了解,我们应该自己动手,实际操作,才会有更深刻的理解。

经过这次设计我学到很多很多的的东西,不仅巩固了以前所学过的知识,而且通过这次课程设计使我懂得了理论与实际相结合的重要性,同时也提高了自己的实际动手能力和独立思考的能力。

最后感谢老师的授课和教导!七、参考文献[1]张义和.例说51单片机[M].北京:人民邮电出版社,2010年[2] 阎石编著数字电子技术基础 (第五版) 北京高等教育出版社] 2006.1~550[3] 蔡明文冯先成主编单片机课程设计华中科技大学出版社 2007.3[4]陈明萤编著 8051单片机课程设计实训教材清华大学出版社 2004[5] 康华光编著模拟电子技术基础(第五版)高等教育出版社 2006[6 ]黄智伟编著全国大学生电子设计竞赛电路(第一版)航空航天大学出版社 2006.36附录源程序代码:#include<reg52.h>#include <intrins.h>#define uchar unsigned charsbit SCK=P3^6;sbit SDA=P3^4;sbit RST = P3^5;bit ReadRTC_Flag;uchar l_tmpdate[7]={0,0,12,15,5,3,8};uchar l_tmpdisplay[8];uchar bianma[]={0xfe,0xfd,0xfb,0xf7,0xef,0xdf,0xbf,0x7f};code uchar read_rtc_address[7]={0x81,0x83,0x85,0x87,0x89,0x8b,0x8d};code uchar table[]={0x3f,0x06,0x5b,0x4f,0x66,0x6d,0x7d,0x07,0x7f,0x6f,0x40}; void Write_Ds1302_Byte(uchar temp);void Write_Ds1302(uchar address,uchar dat );uchar Read_Ds1302 ( uchar address );void Read_RTC(void);//read RTCvoid Set_RTC(void); //set RTCvoid InitTIMER0(void);//inital timer0void main(void){InitTIMER0(); //初始化定时器0Set_RTC();while(1){if(ReadRTC_Flag){ReadRTC_Flag=0;Read_RTC();l_tmpdisplay[0]=l_tmpdate[2]/16;l_tmpdisplay[1]=l_tmpdate[2]&0x0f;l_tmpdisplay[2]=10; //加入"-"l_tmpdisplay[3]=l_tmpdate[1]/16;l_tmpdisplay[4]=l_tmpdate[1]&0x0f;l_tmpdisplay[5]=10;l_tmpdisplay[6]=l_tmpdate[0]/16;l_tmpdisplay[7]=l_tmpdate[0]&0x0f;}}}void InitTIMER0(void){TMOD|=0x01; //定时器设置16位TH0=(65535-500)/256;TL0=(65535-500)%256; //初始化值ET0=1;TR0=1;EA=1;}void Set_RTC(void) //设定日历{unsigned char i,*p,tmp;for(i=0;i<7;i++){ //BCD处理DS1302存放的数据格式是BCD 型tmp=l_tmpdate[i]/10;l_tmpdate[i]=l_tmpdate[i]%10;l_tmpdate[i]=l_tmpdate[i]+tmp*16;}Write_Ds1302(0x8E,0X00); p=write_rtc_address; //传地址for(i=0;i<7;i++) // 7次写入秒分时日月周年{Write_Ds1302(*p,l_tmpdate[i]); //在0x80--0x8c中写入数据p++;}Write_Ds1302(0x8E,0x80);}void Write_Ds1302( uchar address,uchar dat ){RST=0;_nop_();SCK=0;_nop_();RST=1;_nop_(); //启动Write_Ds1302_Byte(address); //发送地址Write_Ds1302_Byte(dat); //发送数据RST=0; //恢复}void Write_Ds1302_Byte(uchar temp){uchar i;for (i=0;i<8;i++) //循环8次写入一个字节数据{SCK=0;SDA=temp&0x01; //每次传输低字节temp>>=1; //右移一位SCK=1;}}void Read_RTC(void) //读取日历{uchar i,*p;p=read_rtc_address; //地址传递for(i=0;i<7;i++) //分7次读取秒分时日月周年{l_tmpdate[i]=Read_Ds1302(*p);p++;}}uchar Read_Ds1302 (uchar address ){uchar i,temp=0x00;RST=0;_nop_();_nop_();SCK=0;_nop_();_nop_();RST=1;_nop_();_nop_();Write_Ds1302_Byte(address);for (i=0;i<8;i++) //循环8次读取数据{if(SDA)temp|=0x80; //每次传输低字节SCK=0;temp>>=1; //右移一位_nop_();_nop_();_nop_();SCK=1;}RST=0;_nop_(); //以下为DS1302复位的稳定时间_nop_();RST=0;SCK=0;_nop_();_nop_();_nop_();_nop_();SCK=1;_nop_();_nop_();SDA=0;_nop_();_nop_();SDA=1;_nop_();_nop_();return (temp); //返回}void tim(void) interrupt 1 using 1//中断,用于数码管扫描{static uchar i,num;TH0=(65535-500)/256;TL0=(65535-500)%256;P0=table[l_tmpdisplay[i]]; //查表法得到要显示数字的数码段P1=bianma[i];i++;if(i==8){i=0;num++;if(20==num) {ReadRTC_Flag=1; //使用标志位判断num=0;}}}。