2007武汉大学数字逻辑试题答案

数字逻辑部分习题解答..共38页PPT

41、学问是异常珍贵的东西,从任何源泉吸 收都不可耻。——阿卜·日·法拉兹

ቤተ መጻሕፍቲ ባይዱ42、只有在人群中间,才能认识自 己。——德国

数字逻辑部分习题解答..

36、“不可能”这个字(法语是一个字 ),只 在愚人 的字典 中找得 到。--拿 破仑。 37、不要生气要争气,不要看破要突 破,不 要嫉妒 要欣赏 ,不要 托延要 积极, 不要心 动要行 动。 38、勤奋,机会,乐观是成功的三要 素。(注 意:传 统观念 认为勤 奋和机 会是成 功的要 素,但 是经过 统计学 和成功 人士的 分析得 出,乐 观是成 功的第 三要素 。

43、重复别人所说的话,只需要教育; 而要挑战别人所说的话,则需要头脑。—— 玛丽·佩蒂博恩·普尔

44、卓越的人一大优点是:在不利与艰 难的遭遇里百折不饶。——贝多芬

45、自己的饭量自己知道。——苏联

《数字逻辑》期末考试A卷参考答案

《数字逻辑》期末考试 A 卷参考答案、判断题:下面描述正确的打’/,错误的打‘X’(每小题1分,共10 分)1、为了表示104个信息,需7位二进制编码[V ]2、BCD码能表示0至15之间的任意整数[X ]3、余3码是有权码[X ]4、2421码是无权码[X ]5、二值数字逻辑中变量只能取值6、计算机主机与鼠标是并行通信7、计算机主机与键盘是串行通信8、占空比等于脉冲宽度除于周期0和1,且表示数的大小[X ][X ][V ][V ]9、上升时间和下降时间越长,器件速度越慢[V ]10、卡诺图可用来化简任意个变量的逻辑表达式[X ]、写出图中电路的逻辑函数表达式。

(每小题5分,共10分)1、F=A B2、F= AB CD2分,共20分)1、在图示电路中.能实现逻辑功能F = ATH 的电路是 A °TTL 电路(A) F = ABCD(B) F = AH ・ CD -(C) F= A + B + C + D(D) F = A + B • C + D (E) F= A BCD4 . 己知F 二ABC + CD ■可以肯定使F = 0的情况是 _°(A) A=0, BC= 1; (B) B= 1 , C= 1 } (C) AB= 1, CD=Q.(D) BC= 1 , D= 15、逻辑函数A B+BCD+A C+ B C 可化简为A,B,C,D 。

(A) AB + AC + BC (B) AB + C (A4-B)(C) AB + CABA — O ?=11 QA |— I1 F •-&1 Q AB L Il —(B)悬0----空。

—A — &Bo —Co- &BA3 •满足如图所示电路的输岀函数F 的表达式为丄3B 1 o — VOF(D) AB +C (E) 19.图示电路中,当各触发器的状态为C 时.再输入一个CP 脉冲,融发器的 状态为QiQ 严0 0。

数字逻辑 课后习题答案

4. 最简电路是否一定最佳?为什么?

解答

一个最简的方案并不等于一个最佳的方案。最佳方案应满足全面的性能指标 和实际应用要求。所以,在求出一个实现预定功能的最简电路之后,往往要根据 实际情况进行相应调整。

2. 数字逻辑电路具有哪些主要特点?

解答

数字逻辑电路具有如下主要特点:

● 电路的基本工作信号是二值信号。 ● 电路中的半导体器件一般都工作在开、关状态。 ● 电路结构简单、功耗低、便于集成制造和系列化生产。产品价格低

廉、使用方便、通用性好。 ● 由数字逻辑电路构成的数字系统工作速度快、精度高、功能强、可

第二章

1 假定一个电路中,指示灯 F 和开关 A、B、C 的关系为 F=(A+B)C

试画出相应电路图。 解答

电路图如图 1 所示。

图1

2 用逻辑代数的公理、定理和规则证明下列表达式:

(1) AB + AC = AB + AC (2) AB + AB + AB + AB = 1 (3) AABC = ABC + ABC + ABC

= (A + B) ⋅ (A + B) =B

( ) F = BC + D + D ⋅ B + C ⋅ (AC + B)

= BC + D + (B + C)(AC + B) = BC + D + BC(AC + B) = BC + D + AC + B = B + D + AC

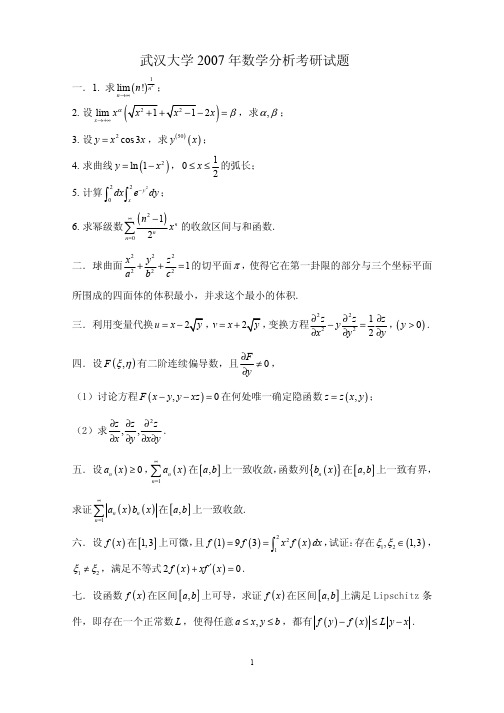

武汉大学2007年数学分析考研试题解答

1

八.计算曲面积分 I = ∫∫ xydydz + yzdzdx + z x 2 + y 2 dxdy ,

∑

其中 ∑ 是由 x 2 + y 2 + z 2 = a 2 , x 2 + y 2 + z 2 = 4a 2 , ( a > 0 ) , z = x 2 + y 2 所围立体 的边界曲面的外侧.

n →∞

n π f ( x ) dx = f ( 0 ) . 2 2 0 1+ n x 2

1

武汉大学 2007 年数学分析考研试题解答

一、简略。 二、解 由对称性,只需考虑第一卦限的情形。

x0 x y0 y z0 z + + = 1, a b c

设切点为 C ( x0 , y0 , z0 ) ,则过点 C 的切平面的方程为:

1 11 1π 1 = 2π [(2a ) 4 − a 4 ]( + − ) 4 22 24 4 = 15π a 4 。 16

九、证明设

un ( x) = an cos nx + bn sin nx

,显然它是连续可微的函数;

1 由条件,可知 | un ( x) |≤| an | + | bn |= (nα | an | + nα | bn |) 1 ≤ 2M α , α n n

≤ 2M

n

α −1

1 ,

当 α > 2 时, ∑ 2 M

n =1 ∞

∞

1 nα −1

收敛,于是 ∑ un′ ( x ) 在

n =1

∞

(−∞, +∞)

上一致收敛,

故有 S ′( x) = ∑ un′ ( x ) ,且在

武汉大学计算机学院2007级系统结构试卷

武汉大学计算机学院2009-2010学年度第一学期2007级《计算机系统结构》期末考试试卷(A)(闭卷)姓名:学号:专业:(注:①考试时间为120分钟;②所有解答必须写在答题纸上。

)一、单项选择题(每小题3分,共30分)1.在系列机中发展一种新型号机器,你认为下列()设想是不行的? 【A】新增加字符数据类型和若干条字符处理指令【B】将中断分级由原来的4级增加到5级【C】在CPU和主存之间增设Cache存贮器【D】将浮点数的下溢处理法由原来的恒置“1”法,改为查表舍入法2.对计算机系统结构来说,不透明的是()。

【A】存储器采用交叉存取还是并行存取【B】CPU内部的数据通路的宽度是8位还是16位【C】采用浮点数据表示还是标志符数据表示【D】指令采用硬联逻辑实现还是微程序实现3.一个平衡的计算机系统,应该是()。

【A】1MIPS的CPU速度【B】1MB的主存容量【C】1Mb/s的I/O吞吐率【D】A、B和C4、()设计是现代计算机系统设计所采用的方法。

【A】由上往下【B】由下往上【C】由中间开始【D】上下同时开始5.当今微型机中实现软件移植最好的方法是()。

【A】系列机【B】兼容机【C】仿真技术【D】统一高级语言6、不能够对向量数据结构提供直接支持的是()数据表示。

【A】向量【B】堆栈【C】描述符【D】A和C7、采用整数边界存储技术,其主要目的是()。

【A】节约主存空间【B】提高数据的访问速度【C】一个主存周期可取多条指令【D】一个主存周期至少可取到一条指令8、在指令的操作码编码方式中,优化实用的编码是()。

【A】Huffman编码【B】等长编码【C】Huffman扩展编码【D】BCD码9、流水计算机中将指令Cache和数据Cache分开,主要是为了()。

【A】提高存储系统的速度【B】增加主存容量【C】解决功能部件冲突【D】解决访存冲突10、当N=16时,能描述4组4元交换的函数是()。

【A】C1+C2 【B】C0+C1 【C】C0+C2 【D】C2+C3二、(10分)在采用通用寄存器指令集结构的计算机上得到了如下所示的数据:优化后的MIPS与优化前的MIPS速率比。

数字逻辑题目及其答案和解析(1)一共60道题

第一部分:1.在二进制系统中,下列哪种运算符表示逻辑与操作?A) amp;B) |C) ^D) ~解析:正确答案是 A。

在二进制系统中,amp; 表示逻辑与操作,它仅在两个位都为1时返回1。

2.在数字逻辑中,Karnaugh 地图通常用于简化哪种类型的逻辑表达式?A) 与门B) 或门C) 异或门D) 与非门解析:正确答案是B。

Karnaugh 地图通常用于简化或门的逻辑表达式,以减少门电路的复杂性。

3.一个全加器有多少个输入?A) 1B) 2C) 3D) 4解析:正确答案是 C。

一个全加器有三个输入:两个加数位和一个进位位。

4.下列哪种逻辑门可以实现 NOT 操作?A) 与门B) 或门C) 异或门D) 与非门解析:正确答案是 D。

与非门可以实现 NOT 操作,当且仅当输入为0时输出为1,输入为1时输出为0。

5.在数字逻辑中,Mux 是指什么?A) 多路复用器B) 解码器C) 编码器D) 多路分配器解析:正确答案是 A。

Mux 是指多路复用器,它可以选择输入中的一个,并将其发送到输出。

6.在二进制加法中,下列哪个条件表示进位?A) 0 + 0B) 0 + 1C) 1 + 0D) 1 + 1解析:正确答案是 D。

在二进制加法中,当两个位都为1时,会产生进位。

7.在数字逻辑中,一个 JK 触发器有多少个输入?A) 1B) 2C) 3D) 4解析:正确答案是 B。

一个 JK 触发器有两个输入:J 和 K。

8.下列哪种逻辑门具有两个输入,且输出为两个输入的逻辑与?A) 与门B) 或门C) 异或门D) 与非门解析:正确答案是 A。

与门具有两个输入,只有当两个输入都为1时,输出才为1。

9.在数字逻辑中,下列哪种元件可用于存储单个位?A) 寄存器B) 计数器C) 锁存器D) 可编程逻辑门阵列解析:正确答案是 C。

锁存器可用于存储单个位,它可以保持输入信号的状态。

10.一个带有三个输入的逻辑门,每个输入可以是0或1,一共有多少种可能的输入组合?A) 3B) 6C) 8D) 12解析:正确答案是 C。

数字逻辑期末考试试卷(含答案)

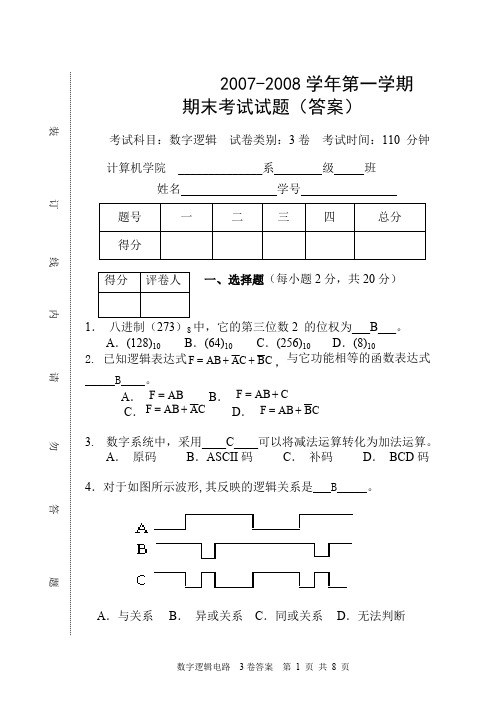

2007-2008学年第一学期期末考试试题(答案)考试科目:数字逻辑 试卷类别:3卷 考试时间:110 分钟计算机学院 ______________系级 班姓名学号毛题号一二三四总分得分 一、选择题(每小题2分,共20分)1. 八进制(273)8中,它的第三位数2 的位权为___B___。

A .(128)10B .(64)10C .(256)10D .(8)102. 已知逻辑表达式B C A AB F ++=,与它功能相等的函数表达式_____B____。

A .AB F = B .C AB F += C .C A AB F +=D . CB AB F +=3. 数字系统中,采用____C____可以将减法运算转化为加法运算。

A . 原码B .ASCII 码C . 补码D . BCD 码4.对于如图所示波形,其反映的逻辑关系是___B_____。

A .与关系B . 异或关系C .同或关系D .无法判断得分评卷人5. 连续异或1985个1的结果是____B_____。

A .0B .1C .不确定D .逻辑概念错误6. 与逻辑函数D C B A F +++= 功能相等的表达式为___C_____。

A . D CB A F +++= B . DC B A F +++=C .D .D C B A F =DC B A F ++=7.下列所给三态门中,能实现C=0时,F=;C=1时,F 为高阻态的AB 逻辑功能的是____A______。

8. 如图所示电路,若输入CP 脉冲的频率为100KHZ ,则输出Q 的频率为_____D_____。

A . 500KHzB .200KHzC . 100KHzD .50KHz9.下列器件中,属于时序部件的是_____A_____。

A . 计数器B . 译码器C . 加法器D .多路选择器10.下图是共阴极七段LED 数码管显示译码器框图,若要显示字符“5”,则译码器输出a ~g 应为____C______。

《数字逻辑》总复习测试题参考答案

目录

• 测试题答案概述 • 选择题答案解析 • 填空题答案解析 • 简答题答案解析 • 计算题答案解析

01

测试题答案概述

测试题答案的解析

测试题1答案解析

这道题考查了基本逻辑门的功能和特点,通 过分析题目中的逻辑表达式,可以确定使用

的逻辑门类型和输入输出关系。

测试题2答案解析

解析:此题考查了触发器的功能,C选项代表了边沿触发器的特性,即在时钟信号的上升沿或下降沿时,触发器 会进行状态更新。

03

填空题答案解析填空题一答案及解析来自答案1010解析

根据二进制数的定义,二进制数由0和1组成,逢2进1。因此,将十进制数10转换为二进制数得到1010。

填空题二答案及解析

答案:8

测试题答案的注意事项

注意单位的统一

在解题过程中,需要注意单位的一致性,避免出现单位混淆或单位 错误的情况。

考虑边界条件

在分析逻辑电路或可编程逻辑器件的应用时,需要考虑各种边界条 件和极端情况,以确保电路的可靠性和稳定性。

重视细节

在解题过程中,需要注意细节问题,如符号的规范使用、电路连接方 式的正确性等,这些细节问题可能会影响最终结果的正确性。

05

计算题答案解析

计算题一答案及解析

答案

11010010

解析

根据二进制加法规则,1010+101=1101,然后后缀一个 0,得到11010010。

计算题二答案及解析

答案:3

解析:根据逻辑或运算规则,当两个输入信 号中至少有一个为高电平时,输出信号为高 电平。因此,A、B、C中至少有一个为高电

02

选择题答案解析

选择题一答案及解析

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

武 汉 大 学 计 算 机 学 院

《数字逻辑》期末考试试题(A 卷)参考答案 2007—2008学年第二学期(闭卷考试)

一、解答(每空1分,共16分)

1. (11011.1)2、(1B.8)16

2. [x ]补=1.0101

3. 奇数

4. 1

5. 0011 0100 0111

6. 高电平, 低电平, 高阻

7. 甲

8. ()(),()()F A B C D F A B C D '=++=++

9. 临界竞争, 非临界竞争 10. 充电时间常数 RC 11. 不是

二、解答(每小题2分,共14分)

1. C

2.A

3.B

4.D

5. C

6.B

7.B

三、解答(每小题5分,共10分)

1.

()F AB AB AB AB CD

AB AB AB ABCD AB AB CD

=+++=+++=++

2. 画出函数F 的卡诺图

解法1 圈为0的项,直接写出或一与式 ()()F B D B D

=++ 解法2 先求F 的最简与一或式。

再对F 求反即得F 的最简或一与式

()()

F BD BD

F F B D B D =+==++

四、解答(每小题10分,共20分)

1. ①写出输出函数表达式

1234F AB F AB F AB F AB ====

② 列其值表

③功能:由其值表可见,每输入一组二进制码时,与这个二进制码值相对应的输出线上将出现一个低电平为0的有效信号。

故其功能是将二进制码按它原来的值译成相应的输出信号,是一个二一四译码器,输出低电平有效。

2. ① 写出激励函数表达式

2211111T c y D y c cp

====

② 作状态转换其值表

状态表

③ (二位二进制数)加1计数器。

时间图如下:

状态图

y 2y 1

五、解答(每小题10分,共20分)

1. 设初态为A

原始状态图

2.①形成原始状态图和原始状态表

②确定激励函数和输出函数

画卡诺图化简

2101010012102102

1010100111J xy y xy y J xy xy J z xy y y xy y y K xy y xy y K xy xy K =+=+=⎧⎧⎧=+⎨⎨⎨=+=+=⎩⎩⎩

③画电路图(略)

六、解答(每小题10分,共20分)

1.① 列真值表求出F 1(大于),F 2 (小于),F 3(等于)的最简与或表达式。

1F A B = 2F AB = 3F AB AB =+

J 2

K 2

……

②画PLA 的阵列图

2.① 先把74193设计成十进制计数器,并用启动脉冲p S 将初态Q D Q C Q B Q A 清零,CLR=Q D Q B ,CPu 接“秒”脉冲CP , CP D 接“1”。

② 把计数器的输出状态Q D Q C Q B Q A 接7448的A 3A 2A 1A 0,并正确处理7448的辅助控制信号,1/1LT BI RBO ==

③ 把7448的七段输出端a~g 接七段显示器的输入a~g 。

D C B A

“秒”脉冲CP

“1”

“秒”时钟逻辑电路图

“1”

A B

A B F 1 F 2 F 3。