DSP处理器常用单元,标志位,段,伪指令,寻址方式

dsp汇编指令系统介绍(精)

汇编指令集本节根据指令的功能来分,提供六张表来说明指令集的概况:累加器、算数和逻辑指令(表2);辅助寄存器和数据页指针指令(表3);TREG、PREG和乘法指令(表4);转移指令(表5);控制指令(表6);I/O和存储器操作(表7)。

在每张表中,指令按字母顺序排列。

执行每条指令所需要的周期数在表中给出,所有指令都假设从内部程序存储器和内部数据存储器中执行,指令的周期数适用于单指令执行,不适用于重复方式。

编程时,用户必须对每条指令的寻址方式了解清楚,因此这里也在表中给出了每条指令的寻址方式。

由于指令的操作码对用户编程没有多大指导意义,在这里就没有列出来。

为了参照起见,我们先定义这六张概述表的符号意义:ACC 累加器。

ARBITXCM 辅助寄存器。

4位数值,用于指定数据存储器数值中的哪一位将被BIT指令所测试。

2位数值,CMPR指令执行CM值所声明的比较:若CM=00,测试当前AR=AR0否;若CM=01,测试当前AR<AR0否;若CM=10,测试当前AR>AR0否;若CM=11,测试当前AR≠AR0否。

ShiftTP 4位右移量。

用于条件执行指令的2位数值,代表如下4种条件:若BIO引脚为低,TP=00;若TC位=1,TP=01;若TC位=0,TP=10;无条件TP=11。

ARX 用于LAR和SAR指令的3位数据值,指定被操作的辅助寄存器。

52表2 累加器、算数和逻辑指令 ABS周期|(ACC)|→ACC 1(ACC)+(数据存储器地址)×12shift→ACC(ACC)+(数据存储器地址)×216→ACC 1(ACC)+k→ACC 1shift(ACC)+lk×2→ACC 2指令功能(ACC)+(数据存储器地址)+(C)→ACC寻址方式直接/间接直接/间接短立即数长立即数指令说明ACC取绝对值移位时低位填0,若SXM=1,高位用符号扩展;若SXM=0,高位填0;结果存在ACC中,该指令使C=0。

DSP常用汇编语言指令简介

1. 累加器等指令举例

Example 1:ADD 1,1;(假设DP = 6),把 第6个数据页的第一个内存单元内容左移一 位加到累加器 Example 2:LACC *,4; (与SXM有关) Example 3:ROL;把累加器内容循环左移 Example 4:SACL *,0,AR7 ;把当前工作寄 存器指示内容左移0位送入累加器的低8位 Example 5:RPT #15 SUBC * ;累加器减去当前寄存 器指的内容,连续减16次,结果存累加器

南航自动化学院DSP技术应用实验 室

LAR AR1,#200H ;设定AR1的值

(2)指明间接寻址选项(*,*+,*-,*0+)) 例如:MAR *,AR0 1, ;然后指向工作寄存器AR1 (3)指明下一个辅助寄存器(可选) 例如: MAR *,AR1 ADD *+,AR4 ;把当前工作寄存器AR1指 向的数据单元内容加至累加器,然后AR1内容加 1,并把工作寄存器定为AR4

2. 工作寄存器等指令举例

Example1:MAR *+,AR1;把当前工作寄 存器的内容加1,然后再改变工作寄存器为 AR1。 Example2:LAR AR4,#8123h;把AR4的 值改变为立即数。 LAR AR0,16;(DP=6)把 地址=310H的内存单元内容装入AR0。 Example3:SAR AR0,*+;(如果当前工 作寄存器=AR1)把AR0的内容拷贝到AR1 南航自动化学院DSP技术应用实验 指向的内存单元。 室

4. 转移指令举例

南航自动化学院DSP技术应用实验 室

EQ NEQ LT LEQ GT GEQ NC C NOV BIO NTC TC UNC

《DSP寻址方式》课件

01

现状

02

广泛应用于信号处理、图像处理、通信等领域。

在大数据和人工智能时代,DSP寻址方式发挥着越来越重要的

03

作用。

DSP寻址方式的未来发展趋势和挑战

发展趋势

1

2

结合人工智能技术,实现更高效的算法加速。

3

支持向量寻址,满足高维数据处理需求。

DSP寻址方式的未来发展趋势和挑战

• 云端和边缘计算的寻址优化。

DSP寻址方式的未来发展趋势和挑战

01

挑战

02 如何应对数据爆炸带来的存储和访问挑战 。

03

如何平衡计算效率和存储空间的需求。

04

如何提高寻址方式的通用性和灵活性,以 适应不断变化的应用场景。

THANKS

感谢观看

算法优化

通过算法优化减少计算量,降低功耗和成本 。

05

总结与展望

DSP寻址方式的发展历程和现状

初始阶段

简单的线性寻址,主要用于基础的数 学运算。

扩展阶段

引入了变址寻址和间接寻址,增强了 数据处理能力。

DSP寻址方式的发展历程和现状

• 现代阶段:支持多种寻址方式,满足复杂算法需 求。

DSP寻址方式的发展历程和现状

详细描述

寄存器寻址方式是指操作数的有效地址通过寄存器给出,即有效地址存储在寄存器中,通过寄存器访问操作数。 这种方式可以用于访问寄存器中的数据,也可以用于实现寄存器间接寻址等操作。

其他寻址方式

总结词

其他特殊的寻址方式

详细描述

除了以上三种寻址方式外,还有一些特殊的寻址方式,如相对寻址方式、位寻址方式等 。这些寻址方式各有特点,可以根据具体的需求选择使用。

PID控制器

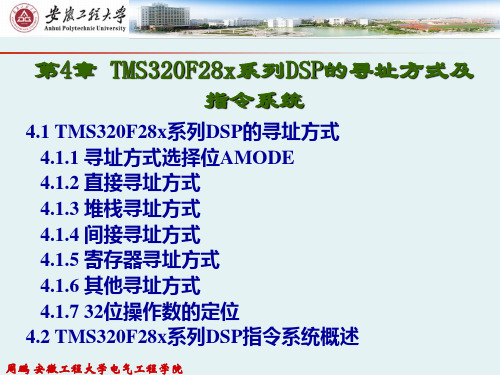

第4章 TMS320F28x系列DSP的寻址方式及指令系统

周鹏 安徽工程大学电气工程学院

TMS320C28x指令集采用7种存储器寻址方式: ▲ 直接寻址方式 ▲ 堆栈寻址方式 ▲ 间接寻址方式 ▲ 寄存器寻址方式 ▲ 数据/程序/IO空间立即寻址方式 ▲ 程序空间间接寻址 ▲ 字节寻址方式 TMS320F2812支持除IO空间立即寻址方式外的其 他寻址方式。

第4章 TMS320F28x系列DSP的寻址方式及 指令系统

4.1 TMS320F28x系列DSP的寻址方式 4.1.1 寻址方式选择位AMODE 4.1.2 直接寻址方式 4.1.3 堆栈寻址方式 4.1.4 间接寻址方式 4.1.5 寄存器寻址方式 4.1.6 其他寻址方式 4.1.7 32位操作数的定位 4.2 TMS320F28x系列DSP指令系统概述

பைடு நூலகம்

周鹏安徽工程大学电气工程学院41tms320f28x系列dsp的寻址方式411寻址方式选择位amode412直接寻址方式413堆栈寻址方式414间接寻址方式415寄存器寻址方式416其他寻址方式41732位操作数的定位42tms320f28x系列dsp指令系统概述周鹏安徽工程大学电气工程学院寻址方式是指cpu根据指令中给出的地址信息来寻找指令中操作数物理地址的方式即获得操作数的方式

在 F2812间接寻址方式中,使用哪个辅助寄存器指针在指令中并不 被明确指出。而在 C2xLP的间接寻址方式中,3位长度的辅助寄存器指 针被用来选择当前使用哪个辅助寄存器以及下次操作将使用哪个辅助寄 存器。

汇编器/编译器对AMODE位的追踪

编译器总是假定AMODE=0,所以它只使用对AMODE=0 有效的寻址模式。而汇编器可以通过设置命令行选项实现默认 AMODE=0或者AMODE=1。 √ – v28 ;假定AMODE=0(C28x寻址方式) – v28 – m20 ;假定AMODE=1(与C2xLP全兼容的寻址方式) √ 在文件中使用内嵌伪指令

DSP各种知识点总结

1 DSP芯片的特点:(1).哈佛结构(程序空间和数据空间分开)(2).多总线结构.(3)流水线结构(取指、译码、译码、寻址、读数、执行)(4)多处理单元. (5)特殊的DSP指令(6).指令周期短. (7)运算精度高.(8)硬件配置强.(9)DSP最重要的特点:特殊的内部结构、强大的信息处理能力及较高的运行速度。

2 三类TMS320:(1)TMS320C2000适用于控制领域(2)TMS320C5000应用于通信领域(3)TMS320C6000应用于图像处理3 DSP总线结构:C54x片内有8条16位主总线:4条程序/数据总线和4条对应的地址总线。

1条程序总线(PB):传送自程序储存器的指令代码和立即操作数。

3条数据总线(CB、DB、EB):CB和EB传送从数据存储器读出的操作数;EB传送写到存储器中的数据。

4条地址总线(PAB、CAB、DAB、EAB)传送相应指令所需要的代码4存储器的分类:64k字的程序存储空间、64K字的数据存储空间和64K字的I/O空间(执行4次存储器操作、1次取指、2次读操作数和一次写操作数。

5存储器空间分配片内存储器的形式有DARAM、SARAM、ROM 。

RAM安排到数据存储空间、ROM构成程序存储空间。

(1)程序空间:MP/MC=1 40000H~FFFFH 片外MP/MC=0 4000H~EDDDH 片外FF00H~FFFFH 片内OVL Y=1 0000H~007FH 保留0080H~007FH 片内OVL Y=0 0000H~3FFFH片外(2)数据空间:DROM=1 F000H~F3FFH 只读空间FF00H~FFFH保留DROM=0 F000H~FEFFH 片外6数据寻址方式(1)立即寻址(2)绝对寻址<两位>(3)累加器寻址(4)直接寻址@<包换数据存储器地址的低7位>优点:每条指令只需一个字(5)间接寻址*按照存放某个辅助寄存器中的16位地址寻址的AR0~AR7(7)储存器映像寄存器寻址(8)堆栈寻址7寻址缩写语Smem:16位单寻址操作数Xmem Ymem 16位双dmad pmad PA16位立即数(0-65535)scr源累加器dst目的累加器lk 16位长立即数8状态寄存器ST0 15~13ARP辅助寄存器指针12TC测试标志位11C进位位10累积起A 的一出标志位OV A 9OVB 8~0DP数据存储器页指针9状态寄存器ST1 CPL:直接寻址编辑方式INTM =0开放全部可屏蔽中断=1关闭C16 双16位算数运算方式10定点DSP 浮点DSP:定点DSP能直接进行浮点运算,一次完成是用硬件完成的,而浮点需要程序辅助。

DSP原理及应用课程重点知识讲解

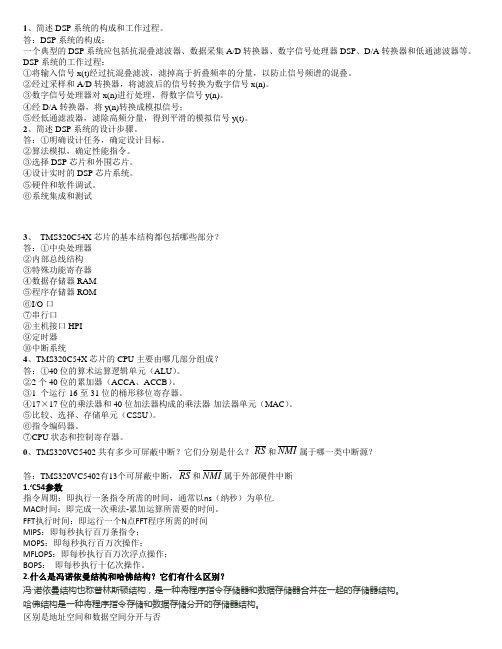

1、简述DSP系统的构成和工作过程。

答:DSP系统的构成:一个典型的DSP系统应包括抗混叠滤波器、数据采集A/D转换器、数字信号处理器DSP、D/A转换器和低通滤波器等。

DSP系统的工作过程:①将输入信号x(t)经过抗混叠滤波,滤掉高于折叠频率的分量,以防止信号频谱的混叠。

②经过采样和A/D转换器,将滤波后的信号转换为数字信号x(n)。

③数字信号处理器对x(n)进行处理,得数字信号y(n)。

④经D/A转换器,将y(n)转换成模拟信号;⑤经低通滤波器,滤除高频分量,得到平滑的模拟信号y(t)。

2、简述DSP系统的设计步骤。

答:①明确设计任务,确定设计目标。

②算法模拟,确定性能指令。

③选择DSP芯片和外围芯片。

④设计实时的DSP芯片系统。

⑤硬件和软件调试。

⑥系统集成和测试3、TMS320C54X芯片的基本结构都包括哪些部分?答:①中央处理器②内部总线结构③特殊功能寄存器④数据存储器RAM⑤程序存储器ROM⑥I/O口⑦串行口⑧主机接口HPI⑨定时器⑩中断系统4、TMS320C54X芯片的CPU主要由哪几部分组成?答:①40位的算术运算逻辑单元(ALU)。

②2个40位的累加器(ACCA、ACCB)。

③1 个运行-16至31位的桶形移位寄存器。

④17×17位的乘法器和40位加法器构成的乘法器-加法器单元(MAC)。

⑤比较、选择、存储单元(CSSU)。

⑥指令编码器。

⑦CPU状态和控制寄存器。

0、TMS320VC5402共有多少可屏蔽中断?它们分别是什么?RS和NMI属于哪一类中断源?答:TMS320VC5402有13个可屏蔽中断,RS和NMI属于外部硬件中断1.‘C54参数指令周期:即执行一条指令所需的时间,通常以ns(纳秒)为单位.MAC时间:即完成一次乘法-累加运算所需要的时间。

FFT执行时间:即运行一个N点FFT程序所需的时间MIPS:即每秒执行百万条指令;MOPS:即每秒执行百万次操作;MFLOPS:即每秒执行百万次浮点操作;BOPS:即每秒执行十亿次操作。

DSP汇编伪指令集讲解

4 .copy, .include .copy, .include告诉编译器从其他文件中读入源语句。 区别在于:.copy读入的源语句将在列表文件中列出, 而.include伪指令读入的不在列表文件中列出。 当汇编器遇到.copy和 .include伪指令时,将停止汇 编当前的源文件语句,而去编译.copy和 .include文件中 的语句,然后继续汇编.copy和 .include后开始的源文件 语句。 5 .data , .text .data是数据段定义伪指令。它告诉汇编器把源代码汇 编到.data段中,且.data成为当前段。该段通常用来存放 数据表或初始化前的变量。 .text:定义.text段中的代码部分,该部分为可执行代 码。.text段是默认段,若汇编开始不指定其他段,就自动 汇编到该段。

4. 当编写具体的应用程序的时候, 用.copy或.include伪指令将I/O寄存器头文 件合中断矢量头文件复制到应用程序中, 形成一个汇编源程序(如delay.asm),再 由汇编器进行汇编后生成一个目标文件 (如delay.obj),最后连接器把该目标文 件和命令文件相连接,生成可执行文件 (如delay.out).

本例中用.usect伪指令定义两个未初始化的命名 段var1和var2。符号ptr和array分别指向var1段和 var2段的第一个字。 dflag指向var1段中50个字块 中的第一个字。

SPC 0000 0000 0000 0001 0001 0065 0002 0000 0003 目标代码 源程序 .text 2003 LACC ptr .usect array .usect 0037 ADD dflag .usect 0065 ADD vec .usect 0000 ADD .global ;汇编到.text段 03h “var1”,1 ;在var1段保留一个字 “var1”,100 ;在var1段保留100个字 037h “var1”,50 dflag ;还在.text段 “var2”,100 ; 在var2段保留100个字 vec ;还在.text段 array ;将array定义为外部符号名

DSP技术与应用习题库及答案(1)

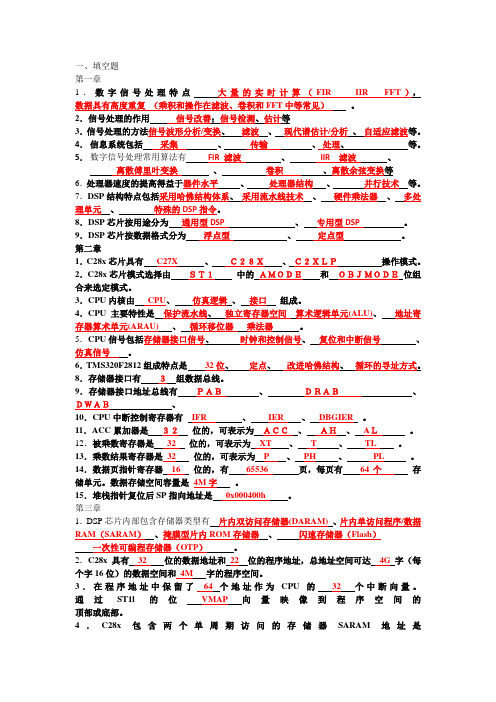

一、填空题第一章1.数字信号处理特点大量的实时计算(FIR IIR FFT),数据具有高度重复(乘积和操作在滤波、卷积和FFT中等常见)。

2.信号处理的作用信号改善;信号检测、估计等3.信号处理的方法信号波形分析/变换、滤波、现代谱估计/分析、自适应滤波等。

4.信息系统包括采集、传输、处理、等。

5.数字信号处理常用算法有FIR 滤波、IIR 滤波、离散傅里叶变换、卷积、离散余弦变换等6.处理器速度的提高得益于器件水平、处理器结构、并行技术等。

7.DSP结构特点包括采用哈佛结构体系、采用流水线技术、硬件乘法器、多处理单元、特殊的DSP指令。

8.DSP芯片按用途分为通用型DSP 、专用型DSP 。

9.DSP芯片按数据格式分为浮点型、定点型。

第二章1.C28x芯片具有C27X、C28X、C2XLP操作模式。

2.C28x芯片模式选择由ST1中的AMODE和OBJMODE位组合来选定模式。

3.CPU内核由CPU、仿真逻辑、接口组成。

4.CPU主要特性是保护流水线、独立寄存器空间算术逻辑单元(ALU)、地址寄存器算术单元(ARAU)、循环移位器乘法器。

5.CPU信号包括存储器接口信号、时钟和控制信号、复位和中断信号、仿真信号。

6.TMS320F2812组成特点是32位、定点、改进哈佛结构、循环的寻址方式。

8.存储器接口有3组数据总线。

9.存储器接口地址总线有PAB、DRAB、DWAB、10.CPU中断控制寄存器有IFR 、IER 、DBGIER。

11.ACC累加器是32位的,可表示为ACC、AH、AL。

12.被乘数寄存器是32 位的,可表示为XT、T、TL 。

13.乘数结果寄存器是32位的,可表示为P 、PH、PL。

14.数据页指针寄存器16 位的,有65536 页,每页有64个存储单元。

数据存储空间容量是4M字。

15.堆栈指针复位后SP指向地址是0x000400h 。

第三章1.DSP芯片内部包含存储器类型有片内双访问存储器(DARAM)、片内单访问程序/数据RAM(SARAM)、掩膜型片内ROM存储器、闪速存储器(Flash)一次性可编程存储器(OTP)。

第三章DSP汇编指令

if 0≤ index+step < BK: index = index + step

else if index + step ≥ BK: index = index + step - BK

else if index + step< 0 index = index + step + BK

只有8条指令能使用存储器映射寄存器寻址:

LDM MMR, dst MVDM dmad, MMR MVMD MMR, dmad MVMM MMRx, MMRy POPM MMR PSHM MMR STLM src, MMR STM #lk, MMR

7. 堆栈寻址

系统堆栈用来在中断和子程序期间自动存放程序计数器。 它也能用来存放额外的数据项或传递数据值。处理器使用一 个16-bit的存储器映射寄存器—堆栈指针来对堆栈寻址,它 总是指向存放在堆栈中的最后一个元素。

2、调用与中断指令

3、返回指令

4、重复指令和堆栈操作指令

四、装入和存储指令

装入和存储指令包括:

一般的装入和存储指令 条件存储指令 并行装入和存储指令 并行装入和乘法指令 并行存储和加件乘指令 混合装入和存储指令

1、一般的装入指令

2、存贮指令

3 并行装入和存储指令 4、条件存储指令

共有四条使用堆栈寻址方பைடு நூலகம்访问堆栈的指令:

PSHD 把一个数据存储器的值压入堆栈。 PSHM 把 一 个 存 储 器 映 射 寄 存 器 的 值 压 入 堆 栈 。 POPD 把一个数据存储器的值弹出堆栈。 POPM 把一个存储器映射寄存器的值弹出堆栈。

§3-2 特殊寻址方式说明

DSP寻址方式

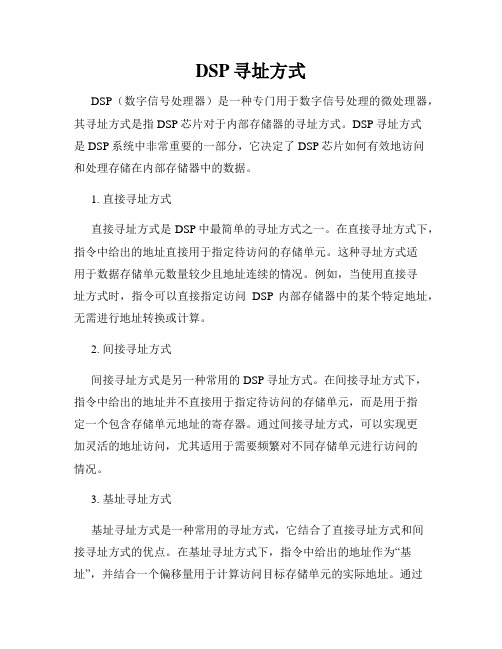

DSP寻址方式DSP(数字信号处理器)是一种专门用于数字信号处理的微处理器,其寻址方式是指DSP芯片对于内部存储器的寻址方式。

DSP寻址方式是DSP系统中非常重要的一部分,它决定了DSP芯片如何有效地访问和处理存储在内部存储器中的数据。

1. 直接寻址方式直接寻址方式是DSP中最简单的寻址方式之一。

在直接寻址方式下,指令中给出的地址直接用于指定待访问的存储单元。

这种寻址方式适用于数据存储单元数量较少且地址连续的情况。

例如,当使用直接寻址方式时,指令可以直接指定访问DSP内部存储器中的某个特定地址,无需进行地址转换或计算。

2. 间接寻址方式间接寻址方式是另一种常用的DSP寻址方式。

在间接寻址方式下,指令中给出的地址并不直接用于指定待访问的存储单元,而是用于指定一个包含存储单元地址的寄存器。

通过间接寻址方式,可以实现更加灵活的地址访问,尤其适用于需要频繁对不同存储单元进行访问的情况。

3. 基址寻址方式基址寻址方式是一种常用的寻址方式,它结合了直接寻址方式和间接寻址方式的优点。

在基址寻址方式下,指令中给出的地址作为“基址”,并结合一个偏移量用于计算访问目标存储单元的实际地址。

通过基址寻址方式,可以实现对存储单元的相对寻址,而无需显式地指定存储单元的具体地址。

4. 变址寻址方式变址寻址方式是一种基于寄存器的寻址方式,它通过使用一个特殊的寄存器,称为“变址寄存器”来实现寻址。

变址寻址方式可以对存储单元的地址进行动态调整,从而实现对存储单元的高效访问。

通过改变变址寄存器中的值,可以改变访问目标存储单元的地址,从而灵活地处理不同的数据访问需求。

5. 直接/间接寻址方式直接/间接寻址方式是一种结合了直接寻址方式和间接寻地址方式的寻址方式。

在直接/间接寻址方式下,指令中既给出了一个直接的地址用于直接寻址,又给出了一个指示寄存器的地址用于间接寻址。

通过使用直接/间接寻址方式,可以在同时满足直接访问和间接访问需求的情况下,提高DSP系统的灵活性和效率。

DSP汇编指令总结

DSP汇编指令引言DSP是指数字信号处理器,是一种专门用于数字信号处理的微处理器。

DSP汇编指令是在DSP芯片上执行操作的命令。

这篇文档将常见的DSP汇编指令及其使用方法。

通用指令MOVMOV是Move的缩写,指将数据从一个寄存器移动到另一个寄存器或内存地址中。

它有很多不同的格式,例如:MOV R1, #0 ; 将0存储在R1寄存器中MOV R2, R1 ; 将R1寄存器中的值复制到R2寄存器中MOV @R3, R2 ; 将R2寄存器中的值存储在R3指向的内存地址中ADD和SUBADD和SUB分别表示加法和减法运算。

它们也有不同的格式,例如:ADD R1, R2 ; 将R2寄存器中的值加到R1寄存器中ADD R1, #2 ; 将2加到R1寄存器中SUB R1, R2 ; 将R2寄存器中的值从R1寄存器中减去AND和ORAND和OR分别表示按位与和按位或运算。

它们也有不同的格式,例如:AND R1, R2 ; 将R1寄存器和R2寄存器中的值按位与后存储在R1寄存器中OR R1, R2 ; 将R1寄存器和R2寄存器中的值按位或后存储在R1寄存器中CMPCMP是Compare的缩写,用于比较两个值。

它会将两个操作数相减,并设置相关的标志位。

它的格式如下:CMP R1, R2 ; 比较R1和R2寄存器中的值跳转指令JMPJMP是Jump的缩写,用于无条件跳转到目标地址。

它的格式如下:JMP label ; 跳转到标签为label的位置JNZ和JZJNZ和JZ分别表示如果结果不为零则跳转和如果结果为零则跳转。

它们的格式如下:JNZ label ; 如果前一条CMP指令比较结果不为零,则跳转到标签为label的位置JZ label ; 如果前一条CMP指令比较结果为零,则跳转到标签为label的位置JGE和JLEJGE和JLE分别表示如果大于或等于则跳转和如果小于或等于则跳转。

它们的格式如下:JGE label ; 如果前一条CMP指令比较结果大于或等于,则跳转到标签为label的位置JLE label ; 如果前一条CMP指令比较结果小于或等于,则跳转到标签为label的位置循环指令DJNZDJNZ是Decrement and Jump if Not Zero的缩写,表示如果操作数不为零则减1并跳转到目标地址。

第六章 DSP寻址方式和汇编指令

第六章 DSP的寻址方式和汇编指令当硬件执行指令时,寻找指令所指定的参与运算飞操作数的方式——寻址方式。

根据程序的要求采用不同的寻址方式,可以有效地缩短程序的运行时间和提高代码执行效率。

汇编指令是可执行指令,每一条指令对应一条机器码,用来控制处理器仲的执行部分进行各种操作。

在本章节当中将主要以基于C28x的DSP芯片为例,为读者讲解DSP的寻址方式和汇编指令系统,其中大部分内容也可适用于其他Ti公司的DSP产品。

6.1汇编语言指令集概述在学习C28x系列DSP的寻址方式和汇编指令指令之前,先来对一些基础的知识进行讲解一下先,在汇编程序当中开发人员会常常使用到许多的特殊符号和标志,它们都具有特殊的含义,在学习汇编之前读者们必须先理解这些符号和标志含义,在这里会对其中最常用最重要的操作数符号和寄存器经行详细说明。

在进行汇编讲解之前先来了解一下开发的核心——CPU。

在TMS320C2000系列中,CPU 内核为:C20x/C24x/C240x:C2xLP:C27x/C28x:C27x、C28x这些CPU的硬件结构有一定差别,指令集也不相同,但是,在C28x芯片中可以通过选择兼容特性模式,使C28xCPU与C27xCPU及C2xLPCPU具有最佳兼容性。

可通过状寄存器STl的位OBJMODE和位AMODE的组合,选定模式。

C28x芯片具有3种操作模式:1.C28x模式:在该模式中,用户可以使用C28x的所有有效特性、寻址方式和指令系统,因此,一般应使C28x芯片工作于该种模式。

2.C27x目标——兼容模式:在复位时,C28x的CPU处于C27x目标-兼容模式。

在该模式下,目标码与C27xCPU完全兼容,且它的循环—计数也与C27xCPU兼容。

3.C2xLP源——兼容模式:该模式允许用户运行C2xLP的源代码,这些源代码是用C28x代码生成工具编译生成的。

在下面的讲解当中会牵涉到模式的转换,希望读者要搞清楚每一个模式的对应关系。

DSP术语

分配:链接器计算输出段的最终存储器地址的过程。 分配节点:将节间消息分配至的处理器节点。 ALU:请参见算术逻辑单元。 ALU 函数:对于并行处理器,是指对到算术逻辑单元 (ALU) 的输入进行的操作, 其中包括三个输入的任何算术或 Boolean 组合,以及混合算术和 Boolean 函 数。(TMS320C8x)

汇编器:从包含汇编语言说明和指令的源文件创建机器语言程序的软件程序。汇 编器将绝对操作代码替换为符号 操作代码,并将绝对或浮动地址替换为符号地 址。

汇编语言:低级的符号编程语言,类似于机器代码语言并由字母组组成 — 每个 字母组代表一个指令;使计算机用 户可以使用助记符(而不是数字指令)来编 写程序。

汇编语言指令:使用计算机操作来表示助记符的语言。

汇编模式:无论当前运行哪种类型的代码,在 DISASSEMBLY 窗口中显示汇编语 言代码但不会显示 FILE 窗口 的调试模式。

汇编程序优化器:可优化线性汇编代码(尚未分配寄存器或预定的汇编代码)的 软件程序。当其中一个输入文件具 有 .sa 扩展名时,汇编程序优化器将会通过 shell 程序 cl6x 自动调用该文件。(TMS320C6x)

异步发送 (TX) 引脚:在该引脚上,来自异步串行端口的数据串行传输;从异步 串行端口移位寄存器 (AXSR) 按一 次一位的速度接收字符。(TMS320C2xx)

属性:指定适用于后续图形信息的部分特性或特点的参数。

音频输出电缆:将软件开发板 (SDB) 连接到音频输入和输出外设的电缆。包含 立体声线路输出、线路输入和辅助 输入的标准 RCA 插孔。(TMS320C8x)

DSP复习题汇总答案版

一、填空题1、DSP的寻址方式有七种,分别的什么?立即寻址、绝对寻址、累加器寻址、直接寻址、间接寻址、存储器映象寄存器寻址、堆栈寻址。

2、程序计数器的值可以通过复位操作、顺序执行指令、分支转移,(累加器转移),块重复,(子程序调用),以累加器调用子程序、中断程序等操作来改变。

3、COFF目标文件都包括以下三种形式的段,分别是:(.text 段),(.data 段),(.bss)段。

4、TI公司的定点DSP产品主要有(TMS320C2000)系列、(TMS320C5000)系列和(TMS320C6000)系列5、DSP芯片的开发工具可以分为(代码生成工具)和(代码调试工具)两类。

6、C54xDSP的指令系统有助记符指令和(代数指令)指令两种形式。

7、DROM为(1),片内RPM配置程序和数据存储空间。

ST1的CPL为(1)表示选用对战指针SP的直接寻址方式;ST1的C16等于(0)表示ALU工作在双精度算术运算式。

(填写0或1)8、DSP具有两个(40)位的累加器A和B。

累加器A的(32~39)位是保护位。

9、TMS320C54xDSP的内容总存储空间为(192K)字,分成3个可选择的存储空间。

10、TMS320C54x有4组地址总线分别是PAB、(CAB)(DAB)和(EAB)总线。

11、链接器对段的处理主要通过(MEMORY)和(SECTIONS)两个命令来完成。

12、DSP有3个16位寄存器作为状态和控制寄存器,分别是(ST0)、(ST1)和(PMST)13、TMS320C54x的三类串行口分别是标准同步串行口、(缓冲串行口)、(时分多路串行口)14、DSP的内部存储器类型可分为RAM和ROM,其中RAM又可以分为两种类型:(单寻址RAM(SARAM))和(双寻址ROM(DARAM))。

15、在数字信号处理器寻址指令系统中,Dmad为16位立即数,表示(数据存储器地址),Pmad表示(程序存储器地址)16、用于DSP与其他总线或CPU进行通信的接口称为(主机接口)17、DSP芯片采用了6级流水线的工作方式,即一条指令分为哪6个阶段?预取指、取指、译码、寻址、读数和执行6个阶段。

TI公司三大系列DSP芯片指令系统比较

TI公司三大系列DSP芯片指令系统比较摘要:DSP技术已成为目前电子工业领域发展最迅速的技术,在各行各业的应用越来越广泛。

DSP微处理器是以数字信号来处理大量信息的器件,已成为电子工业领域增长最迅速的产品之一。

TI公司作为最早从事DSP微处理器研究的厂商之一,已经形成了三大系列的DSP芯片,在电子行业各个领域占有很大的市场份额。

本文通过对TI公司三大系列DSP芯片的简要介绍,对这三大系列芯片的指令系统进行了比较。

关键词:TI DSP芯片指令系统比较一、前言在经历整整二十年的市场拓展之后,DSP所树立的高速处理器地位不仅不可动摇,而且业已成为数字信息时代的核心引擎。

与此同时,DSP的市场正在蓬勃发展。

从TI推出业界第一颗商用DSP开始,陆续有公司设计出适合于DSP处理技术的处理器,于是DSP开始成为一种高性能处理器的名称。

TI在1982年发表一款DSP处理器名为TMS32010,其出色的性能和特性倍受业界的关注,当努力使DSP处理器每MIPS成本也降到了适合于商用的低于$10美元范围时,DSP不仅在在军事,而且在工业和商业应用中不断获得成功。

1991年TI推出的DSP批量单价首次低于$5美元而可与16 位的微处理器相媲美,但所能提供的性能却是其5至10倍。

多家公司跻身于DSP领域与TI进行市场竞争。

TI首家提供可定制DSP,称作cDSP。

cDSP 基于内核DSP的设计可使DSP具有更高的系统集成度,大加速了产品的上市时间。

同时TI瞄准DSP 电子市场上成长速度最快的领域,适时地提供各种面向未来发展的解决方案。

到九十年代中期,这种可编程的DSP器件已广泛应用于数据通信、海量存储、语音处理、汽车电子、消费类音频和视频产品等等,其中最为辉煌的成就是在数字蜂窝电话中的成功,逐渐形成了现今TI三大系列主流DSP芯片。

TI通过不断革新,推陈出新,DSP业务也一跃成为TI的最大的业务,并始终处于全球DSP市场的领导地位。

《DSP寻址方式》课件

3 DSP寻址方式的应用实例

4 DSP的未来发展方向

DSP在数字滤波等方面具有广泛应用,通过选 择合适的寻址方式和算法,可以有效提高数 字信号处理的性能和效率。

未来随着DSP技术的不断发展,DSP的功耗和 成本将进一步降低,DSP的应用范围也将不断 拓展和完善。

DSP的特点和优势

DSP具有高效的并行运算能 力、灵活的寻址和数据储存 结构、低功耗和低成本等优 点,可以大幅提高数字信号 处理的效率和精度。

DSP寻址方式的分类

1

直接寻址方式

2

直接寻址方式通过指定数据的物理地址

来访问数据,在存储器寻址和高速信号

处理方面具有优势。

3

寄存器寻址方式

4

寄存器寻址方式是指通过指定寄存器名 称来访问寄存器中的数据,具有简单、

在程序编译阶段的优化

4

在程序编译阶段应该通过优化算法和代码 生成技术来提高程序的效率和质量。

5

寻址方式的优化目标

对DSP寻址方式的优化目标通常包括提高 运行速度、降低功耗、优化程序结构和提 高数据处理精度。

在程序设计阶段的优化

在程序设计阶段应该尽可能选择简单直观 的寻址方式,避免采用复杂和低效的寻址 方式。

在程序执行阶段的优化

在程序执行阶段应该通过指令级并行、数 据级并行和多路径执行等技术来提高程序 的运行速度和性能。

DSP寻址方式的应用实例

数字滤波

DSP在数字滤波中应用广泛,可 通过选择不同的寻址方式和算 法来增强数字信号处理的效率 和精度。

不同寻址方式在数字 滤波中的应用

DSP三大系列芯片的寻址方式简述

简述TMS320C2000、TMS320C5000、TMS320C6000DSP芯片的寻址方式姓名:刘帅民学号:201120195005 专业:通信与信息系统摘要:本文中主要针对TI公司生产的TMS320C2000系列、TMS320C5000系列和TMS320C6000系列DSP的寻址方式进行简要概述。

Abstract:The article focused on the briefly discusses of TI’s TMS320C2000 Series,TMS320C5000 Series and TMS320C6000 Series DSP’s addressing.TI公司三大系列DSP的寻址方式有许多种,由于它们各自的功能不同造成三者的寻址方式也不同,下面对三者的寻址方式做一个简要的叙述。

一、TMS320C2000的寻址方式TMS320C2000系列DSP有七种寻址方式,接下来进行简单介绍。

1、直接寻址在直接寻址中,数据地址由基地址和偏移地址共同决定。

基地址存放在数据页指针寄存器DP (16位)中,偏移地址由直接寻址指令提供。

当ST1寄存器的AMODE 位为0的时候,偏移地址是6位,对应DP指示的一个数据页内,包含64个数据单元;当ST1寄存器的AMODE位为1的时候,偏移地址是7位,对应DP指示的一个数据页内,包含128个数据单元。

在两种情况下,数据地址高10位全为0,也就是说,直接寻址只能寻址4M数据空间。

2、堆栈寻址堆栈寻址一般是专用SP(堆栈指针寄存器)来对堆栈寻址的方法。

TMS320C2000系列DSP芯片用一个16位的SP来对堆栈寻址,且SP总是指向堆栈中最后存入的数据单元(即顶部)。

堆栈寻址主要负责对系统堆栈的压入和弹出。

用SP进行寻址时,数据地址的低16位与SP相关,而高16位默认为0X0000。

3、间接寻址在间接寻址方式中,数据空间任意单元都可以通过一个辅助寄存器(XAR 0~XAR 7)中的内容所代表的32位地址进行访问。

《DSP处理器及应用》复习题

《DSP处理器及应用》总复习题一、单项选择题1、对于TMS320C54x系列DSP芯片,下列说确的是()。

A、专用型DSPB、32位DSPC、定点型DSPD、浮点型DSP2、下面对一些常用的伪指令说确的是:()。

A、.def所定义的符号,是在当前模块中使用,而在别的模块中定义的符号;B、.ref所定义的符号,是当前模块中定义,并可在别的模块中使用的符号;C、.sect命令定义的段是未初始化的段;D、.usect命令定义的段是未初始化的段。

3、在采用双操作数的间接寻址方式时,要使用到一些辅助寄存器,在此种寻址方式下,下面的哪些辅助寄存器如果使用到了是非法的()。

A、AR2B、AR4C、AR5D、AR64.C54x DSP的流水线是由()级(也即是由多少个操作阶段)组成。

A、4B、6C、8D、105、C54x进行32位长数据读操作时使用的数据总线是()。

A、CB和EBB、EB和DBC、CB和DBD、CB、DB和EB6、以下哪种方法不能清除中断标志寄存器中的中断标志位()。

A、硬件复位B、软件复位C、软件置位IFR寄存器中的标志位D、软件清零IFR寄存器中的标志位7、执行指令PSHM AR5之前SP = 03FEH,则指令执行后SP =()。

A、03FDHB、03FFHC、03FCHD、0400H8、当硬件复位后,CPU将从下面的那个地址执行程序()。

A、0FF80HB、0000HC、0080HD、0FF00H9、C54x DSP采用改进型的哈佛结构,围绕几条几位总线建立()。

A、8,16B、16,8C、8,8D、16,1610、C54x DSP的32个中断源分为14级,其中()级别最高。

A、INTRB、NMIC、RSD、INT011、能将各指令的各个步骤重叠起来执行的是()。

A、DAGB、硬件乘法器C、DMAD、流水技术12、DSP硬件设计又称为目标板设计,是基于()全面考虑的基础上完成的。

A、算法需求分析B、成本和体积C、功耗核算D、算法需求分析和成本、体积、功耗核算13、()就是将输入的信号序列按规定的算法处理之后得到所希望的输出序列的过程。

3.0 DSP寻址方式

地址=ARx * ARx+0% ARx=circ(ARx+AR 0)

双操作数寻址

在指令中,由于只有2位可以用于选择辅助寄存

器,所以根据Xar或Yar的值可以选择4个寄存器。

Xar和Yar域选择的辅助寄存器

Xar、Yar

0 0 1 1 0 1 0 1

辅助寄存器

AR2 AR3 AR4 AR5

6 存储器映像寄存器寻址

LDM MVDM MVMD MVMM POPM PSHM STLM STM MMR,dst dmad,MMR MMR,dmad MMRx,MMRy MMR MMR src,MMR #lk,MMR ;将MMR加载到累加器 ;数据存储器向MMR传送数据 ;MMR向指定地址传送数据 ;MMRx向MMRy传送数据 ;将数据从栈顶弹至MMR ;将MMR数据压入堆栈 ;累加器低位存入MMR ;长立即数lk存入MMR

MMR寻址特点:

① 寻址速度快,对MMR执行写操作开销小;

② 可直接利用MMR的名称快速访问数据存储空间

的0页资源;

③ 只能寻址数据空间的0页单元。 用途:主要用于不改变 DP 、 SP 的情况下,修改 MMR中的内容。

用途:用于对速度要求较低的场合。

绝对寻址

绝对寻址是利用16位地址来寻址操作数的存储 单元。由于绝对地址代码的位数为16位,所以绝对 地址寻址的指令至少应为2个字长

绝对寻址四种类型 :

① ② ③ ④ 数据存储器地址(dmad)寻址; 程序存储器地址(pmad)寻址; 端口(PA)寻址; *(1k)寻址。

直接寻址

例 1 :数据存储器存储数据如图所示,采用数据页指针 DP直接寻址,完成x,y单元的两个数据求和。

RSBX LD LD LD

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

M单元

数据读数据总线BB/CB/DB

数据读地址总线BAB/CAB/DAB

程序读数据总线PB

程序读地址总线PAB

数据写数据总线EB/FB

数据写地址总线EAB/FAB

存储器接口单元

管理所有来自CPU、数据空间(RAM)、

I/O空间的数据和指令

负责CPU和数据空间、CPU和I/O空间的数据传输

标志位:

运算相关

常用的位

作用

状态寄存器

备注

CARRY

M40=0时,31位检测进位/借位,进位为1;反之为0

M40=1时,39位检测进位/借位,借位为1;反之为0

ST0_55

ADD/SUB Smen<<#16,[ACx,]ACy有进/借位时置1,反之不清零

ACOVx

M40=0时,31位ACx溢出,溢出ACOVx为1

循环寻址

BK03、BK47、BKC

循环缓冲区大小

字个数/位数

不能跨主页存放

间接寻址

特有

BSAxx、BSAC

循环缓冲区首地址

1.设置ARnLC和CDPLC

2.设置BKxx,缓冲区长度

3.设置XARx,主数据页数

4.设置BSAxx,缓冲区首地址5.设置ARx,偏移

I/O:16位I/O地址,port(*ARn)

双AR间接寻址

RAM

*ARm,*ARn

可以用于并行指令

CDP间接寻址

RAM/MMR/IO/寄存器位

*CDP

系数间接寻址

RAM中的系数+双AR

*CDP、*ARm、*ARn

CDP->Cmem,ARm->Xmem,ARn->Ymem

Cmem必须放在与Xmem和Ymem不同的存储器块里

单元:

单元简称

总线

单元全称

单元作用

包含内容

I单元

程序读数据总线PB

指令缓冲单元

缓存指令、译码结果传给其他单元

指令缓冲队列(64字节)

指令解码器

P单元

数据读数据总线CB/DB

程序读地址总线PAB

程序流单元

产生所有程序空间地址

控制指令流顺序

程序地址产生器(PAGEN)

程序控制逻辑

P单元寄存器

A单元

数据读数据总线CB/DB

语法元素

含义

说明

Baddr

累加器ACn,

辅助寄存器ARn,

暂存器Tn的位域

Cmem

来自内部数据空间的16位数据

CDP间接寻址能访问

Lmem

来自数据空间、MMR的32位数据

SHIFTW

-32~31的移位值

带符号立即数

Smem

来自数据空间、

I/O空间、

MMR的16位数据

可以使用立即数、

直接和间接寻址方式

控制相关

常用的位

作用

状态寄存器

备注

C54CM

C54CM=0时,C55x不支持C54x代码;反之则支持

ST1_55

MPNMC

MPNMC=0时,微计算机模式,可以在程序空间寻址

MPNMC=1时,微处理器模式,不可以在程序空间寻址

ST3_55

5509A无此引脚

ARnLC

ARnLC=0时,ARn线性寻址;反之循环寻址

SMUL=0时,关闭乘法饱和模式;反之打开

ST3_55

受SATD限制,不受M40位的影响

RDM

RDM=0时,取整时向上取整,反之四舍五入

ST2_55

RDM=0时,取整时+8000h,然后删掉低16位

RDM=1时,低16位小于8000h删掉;大于8000h进位;等于时如果高16位是奇数,+8000h删低位;反之直接删低15位。

间接寻址

AR间接寻址

RAM/MMR/IO/寄存器位

*ARn

ARMS=0,DSP模式:

CPU提供DSP增强应用的高效执行功能

ARMS=1,控制模式:CPU能够优化代码的长度

RAM/MMR:提供低16位,高7位由ARnH提供

寄存器位:当AR中只有1位时,默认为寄存器位寻址

只能访问AC0–AC3、AR0–AR7、T0–T3

SXMD

SXMD=0时,关闭D单元符号拓展模式;反之打开

ST1_55

关系到拓展时是否关心符号位

SATD

SATD=0时,关闭D单元饱和模式;反之打开

ST1_55

关系到D单元计算溢出时计算结果是否饱和

SATA

SATA=0时,关闭A单元饱和模式;反之打开

ST3_55

关系到D单元计算溢出时计算结果是否饱和

SMUL

ST2_55

CDPLC

CDPLC=0时,CDP线性寻址;反之循环寻址

ST2_55

CPL

CPL=0时,选择DP直接寻址模式

CPL=1时,选择SP直接寻址模式

ST1_55

ARMS

ARMS=0,DSP模式:CPU提供DSP增强应用的高效执行功能

ARMS=1,控制模式:CPU能够优化代码的长度

ST2_55

对AR间接寻址有影响

Xmen和Ymen

同时来自数据空间的2个16位数据

AR双间接寻址

TAx

暂存寄存器Tx

辅助寄存器ARn

寻址方法

寻址方式

寻址对象

格式

说明

绝对寻址

k16绝对寻址

RAM/MMR

*abs(#k16)

k32绝对寻址

RAM/MMR

*(#k23)

I/O绝对寻址

I/O

port(#k16)

直接寻址

DP直接寻址

RAM/MMR

bss

给未初始化的变量保留存储空间

否

.bss symbol,size[,[blocking flag][,alignment flag]]

sect

自定义段

是

sect "section name"[,value]

usect

自定义段

否

symbol .usect "section name",size[,[blocking flag][,alignment flag]]

BRAF

CPL

XF

HM

INTM

M40

SATD

SXMD

7

6

5

4

3

2

1

0

C16

FRCT

C54CM

ASM

15

14

13

12

11

10

9

8

ST2_55

ARMS

保留

DBGM

EALLOW

RDM

保留

CDPLC

7

6

5

4

3

2

1

0

AR7LC~AR0LC

15

14

13

12

11

10

9

8

ST3_55

CAFRZ

CAEN

CACLR

HINT

保留

7

6

5

4

3

2

1

0

CBERR

MPNMC

SATA

保留

CLKOFF

SMUL

SST

左对齐是用看的,右对齐的是不用看的

段&伪指令:

段名称

作用

初始化/

是否打断当前段

格式

text

包含可执行代码

是

.text[value] value:段指针(SPC)开始值,只可指定一次

data

包含初始化数据

是

.data[value]

TCx

标志位

条件加减指令(ADDSUBCC)、存储/寄存器比较指令(CMP)

条件移位指令(SFTCC)、位域比较指令(BAND)

存储器位操作指令(BTST)

15

14

13

12

11

10

9

8~0

ST0_55

ACOV2

ACOV3

TC1

TC2

CARRY

ACOV0

ACOV1

DP

15

14

13

12

11

10

9

8

ST1_55

@Daddr

CPL=0,先给出XDP,然后用.dp设定DP值,

最后用@给出偏移值/mmap(@MMR)

SP直接寻址

堆栈

*SP(offset)

CPL=1

寄存器位直接寻址

寄存器一个/两个相邻的位

@bitoffset

BSET @0,AC3

PDP直接寻址

I/O

Port(@Poffset)

先给出PDP的值,然后用port(@Poffset)给出偏移

数据读地址总线BAB/CAB/DAB

数据写地址总线EAB/FAB

数据写数据总线EB,FB

地址数据流单元

DAGEN:产生所有读写数据空间的地址

ALU:简单计算

数据地址产生器单(DAGEN)

A单元寄存器

A单元ALU

D单元

数据读数据总线BB/CB/DB

数据写数据总线EB/FB

数据计算单元

计算

移位器、D单元Aபைடு நூலகம்U

M40=1时,39位ACx溢出,溢出ACOVx为1

ST0_55

ACOVx由复位、指令清零时才会清零

M40

M40=0时,D单元计算模式为32位

M40=1时,D单元计算模式为40位

ST1_55

能影响符号位、进/借位、溢出饱和、和0比较、循环移位