富士通单片机MB90F927数据手册

f2mc-8fx 家族mb95200h210h 系列如何进行cr 调节

序程节调 数的外以 ,

动启将器配适 确正的 确正的

。后电上 标目在生发程过节调 。变改了生发率 频钟时 果如率频钟时 节调要需且,态状的钟时 解了需器配适 ,前始开试调 。止终试调 ,开断会将信通的器配适 与 标目, ± 围范下以出超率频钟时 若 。率频 的 于基是置设的率 特波。信通 线单持支以号信率特波的 生产于用被器荡振 ,下式模试调 。率频 制控以器存寄制控 节调过通能功节调 的器配适 。理原节调 绍介章本

CRTH [4:0] [4:0] CRTH [4:0] CRTL [4:0]

// set CRTH & CRTL 6

CR MHz (

和

的中区

了改修户用若。区

。 至变改能 , 置设码代户用下如像若 。区留预是 和 的区存闪 。复恢够能值些这后位复,值 至存并出取区存闪自据数的 ,时位复

NVR

I/O

置配的器存寄

2.3-1: NVR

器荡振 主 章 第 作操节调

CR

CR 2

V1.0

图

I/O

CRTH

CRTL

改修可户用但

。信通线单保确可度精该。 ± 至节调 把是法做种这,下况情常通。 示指 对将其, 到收接 标目自器配适 若,间期节调 。 作用 回返器配适 向会后节调做稍 标目 ,令命节调的确正到收接若;值的 和 加增性硬会 标目,后之误 错收接令命次每。令命节调待等始开并, 置 和 使 标目 。节调 始开 标目,后误错桢次多生发令命节调的到收接。令命节调到收地确正 接能不 标目则。率频 的误错到得 标目后电上,坏破被 的中 标目若 。 败失节调 限界出超间时试重或 标目向续持 会器配适 ,时节调 行进

SmartPRO编程器编程Spansion的MCU产品应用手册说明书

广州致远电子股份有限公司文件信息类别内容关键词SmartPRO 通用编程器 Spansion FUJITSU MCU摘要本文介绍如何使用SmartPRO 系列通用编程器来编程Spansion 的MCU 芯片。

SmartPRO 编程器编程Spansion 的MCU修订历史版本日期原因V1.00 2008/09/01 创建文档。

V1.01 2009/10/10 将文档中图片修改为SmartPRO 2008版软件截图V1.02 2014/07/23 更改半导体公司名称、修改错别字目录1.Spansion的MCU芯片支持情况 (1)2.Spansion的MCU芯片特点 (2)2.1 加密特点 (2)2.2 NVR区 (2)3.应用软件界面简介 (3)4.烧录器件的步骤 (4)4.1 选择器件 (4)4.2 将数据装入缓冲区 (5)4.3 设置芯片配置信息及加密选项 (6)4.4 编程芯片 (6)4.5 组合定制 (7)4.6 量产 (7)5.脱机模式 (9)5.1 脱机操作说明 (9)5.1.1 键盘使用规则 (9)5.1.2 菜单介绍 (9)5.1.3 创建脱机工程 (9)1.制作脱机工程 (9)2.填写工程信息 (10)3.选择存储介质 (10)5.2 脱机操作步骤 (10)6.免责声明 (13)1. Spansion的MCU芯片支持情况目前,在SmartPRO 5000U-Plus和SmartPRO T9000-PLUS 编程器上均支持52种Spansion(原FUJITSU)的MCU芯片(包含封装),包括F2MC-8FX系列, F2MC-8L系列,F2MC-16LX系列和F2MC-16FX系列。

详细情况见表 1.1。

表 1.1 FUJITSU 芯片支持情况Series Part Number Adapter Part Number AdapterF2MC-8FX MB95F108AMWPFM@QFP64ZY514E MB95F203K@SOP20 ZY308A MB95F108AHWPFM@ QFP64ZY514E MB95F203H@SDIP24 ZY403A MB95F108PFV@ QFP64 ZY565B MB95F203K@SDIP24 ZY403A MB95F118ASPMT@QFP48 ZY509A MB95F204H@SOP20 ZY308A MB95F118NSPMC@LQFP52ZY552D MB95F204K@SOP20 ZY308A MB95F128MBPMC@LQFP100ZY515A MB95F204H@SDIP24 ZY403A MB95F128NBPMC@LQFP100ZY515A MB95F204K@SDIP24 ZY403A MB95F136MBSPF@SOP28 ZY309A MB95F212KMB95F156MPMT@QFP48 ZY509A MB95F212K@SOP8 ZY301A MB95F166DPMC1@QFP64 ZY565A MB95F213KMB95F168JPMC1@QFP64 ZY565A MB95F213K@SOP8 ZY301A MB95F202H@SOP20 ZY308A MB95F214KMB95F202K@SOP20 ZY308A MB95F214K@SOP8 ZY301A MB95F202H@SDIP24 ZY403A MB95F223KMB95F202K@SDIP24 ZY403A MB95F223K@SOP16 ZY301A MB95F203H@SOP20 ZY308A MB95F264K@SOP20 ZY308AF2MC-8LMB89F202P-SH@SDIP32ZY403A MB89F538L-101PFM@LQFP64ZY514DMB89F202RA@SDIP32ZY403A MB89F538L-201PFM@LQFP64ZY514DF2MC-16LXMB90F057@ LQFP100 ZY515C MB90F562BPFM@ LQFP64 ZY514CMB90F342CAPF@ QFP100 ZY510E MB90F562PFM@LQFP64 ZY514CMB90F352SPFM@QFP64 ZY514B MB90F823APF@QFP80 ZY583A MB90F462APFM@ LQFP64 ZY514C MB90F882PMC@ LQFP100 ZY515CMB90F488BPFV@ LQFP100 ZY515B MB90F927PF@ QFP100 ZY510DMB90F543GPF@ QFP100 ZY510DF2MC-16FX MB96F346RWBPQC@QFP100ZY510E MB96F347RSBPQC@QFP100 ZY510E MB96F347RSBPMC@LQFP100ZY515D MB96F348HSBPQC@QFP100 ZY510E注:对于FUJITSU芯片我们正在持续添加中,请到/sitecn/program下载最新软件“SmartPRO 系列通用编程器软件(SmartPRO 2008)”。

Fujitsu ESPRIMO E920 E90+ 产品数据表说明书

Data SheetFujitsu ESPRIMO E920 E90+Combines High Efficiency with ManageabilityFUJITSU ESPRIMO E920 PCs give you the absolute highest PC manageability, performance and expandability. With the 92% efficient power supply, you’ll also save on energy costs. The use of identical components within the family ensures perfect infrastructure compatibility. At retirement, Fujitsu’s distinctive EraseDisk function wipes your data securely.Small form factor PCFlexible desktop solution whatever the space requiredLess than 13 liters volume, can be positioned vertically and horizontallyGreen technologyFujitsu’s contribution to environmental protection and sustainabilityHalogen-free printed circuit of mainboard and power supply, sophisticated product concept for the entire lifecycleEnergy efficiency coupled with high performanceLow power consumption combined with high performance4th generation Intel® Core™ processor family and a power supply with 90% energy efficiency System managementSimple system administration for complex IT infrastructuresIntel® vPro™ technology (depending on processor) and DeskView manageability suite QuietPleasant working environment due to an extremely quiet systemInnovative hardware design, optimized cooling concept ensures silent operationsComponentsProcessor Intel® Core™ i7-4790 processor (4 Cores / 8 Threads, 3.60 GHz, up to 4.0 GHz, 8 MB, Intel® HD Graphics 4600) *Intel® Core™ i5-4690 processor (4 Cores / 4 Threads, 3.50 GHz, up to 3.9 GHz, 6 MB, Intel® HD Graphics 4600) *Intel® Core™ i5-4590 processor (4 Cores / 4 Threads, 3.30 GHz, up to 3.7 GHz, 6 MB, Intel® HD Graphics 4600) *Intel® Core™ i3-4170 processor (2 Cores / 4 Threads, 3.70 GHz, 3 MB, Intel® HD Graphics 4400)Intel® Pentium® processor G3460 (2 Cores / 2 Threads, 3.50 GHz, 3 MB, Intel® HD Graphics)Intel® Pentium® processor G3260 (2 Cores / 2 Threads, 3.30 GHz, 3 MB, Intel® HD Graphics)Intel® Celeron® processor G1840 (2 Cores / 2 Threads, 2.80 GHz, 2 MB, Intel® HD Graphics)Intel® vPro™ Logo with Intel® Core i5 and Core i7 processors*with Intel® Turbo Boost Technology (clock speed and performance will vary depending on workload and othervariables)Intel® Smart Response Technology supported by Intel® Core™ i3, i5 and i7 processorsOperating systemsOperating system Windows 8.1 ProWindows 8.1Windows 7 Professional 64-bitWindows 7 Professional 32-bitOperating system compatible Windows 10 Pro (license + recovery media only)openSUSE LinuxMemory modules 2 GB (1 module(s) 2 GB) DDR3, unbuffered, non-ECC, 1,600 MHz, PC3-12800, DIMM4 GB (1 module(s) 4 GB) DDR3, unbuffered, non-ECC, 1,600 MHz, PC3-12800, DIMM8 GB (1 module(s) 8 GB) DDR3, unbuffered, non-ECC, 1,600 MHz, PC3-12800, DIMMHard disk drives (internal)SSD SATA III Premium, 512 GB, 2.5-inchSSD SATA III Premium, 256 GB, 2.5-inchSSD SATA III Premium, 128 GB, 2.5-inchSSD SATA III, 256 GB, 2.5-inchSSD SATA III, 128 GB, 2.5-inchSSD SATA III, 256 GB, 2.5-inch, SEDSSD SATA III, 128 GB, 2.5-inch, SEDSSHD SATA III, 7,200 rpm, 1,000 GB, 3.5-inchSSHD SATA III, 5,400 rpm, 500 GB, 2.5-inchHDD SATA III, 7,200 rpm, 500 GB, 3.5-inch, business criticalHDD SATA III, 7,200 rpm, 2,000 GB, 3.5-inchHDD SATA III, 7,200 rpm, 1,000 GB, 3.5-inchHDD SATA III, 7,200 rpm, 500 GB, 3.5-inchHDD SATA II, 5,400 rpm, 320 GB, 2.5-inchHard disk notes Up to 20 GB of HDD space is reserved for system recoverySSHD (Solid State Hard Disk, Hybrid drive)SSD (Solid State Disk)SED (Self-Encrypting Drive)Graphics NVIDIA® NVS™315 LP, 1 GBNVIDIA® GeForce® GTX 745 2 GB LP, 2 GBNVIDIA® GeForce® GT630 DisplayPort 2GB LP “0-Watt”, 2 GBNVIDIA® GeForce® 605 DisplayPort 1GB LP, 1 GBLFH59/ 2x DVI-I adapter cableLFH59/ 2x DP adapter cableDVI-I to VGA AdapterDP to DVI-D (single link) Adapter CableDP Extension CardDrives (optional)BD Triple Writer SATA slim (tray)DVD-ROMDVD Super MultiMultiCard Reader 24in1 USB 2.0 3.5”Interface add on cards/components(optional)WLAN 802.11 a/g/n (2x2), (dedicated regions only, not for Indonesia)Parallel InterfaceGigabit Ethernet PCIe x1, DSeSATA InterfaceDual serial card PCIe x1Base unitBase unit ESPRIMO E920 E90+MainboardMainboard type D3222FormfactorμATXChipset Intel® Q87Processor socket LGA 1150Processor quantity maximum1Supported capacity RAM (max.)32 GBMemory slots 4 DIMM (DDR3)Memory frequency1,600 MHzMemory notes Dual channel supportFor dual channel performance, a minimum of 2 memory modules have to be ordered. Capacity per channel has to bethe same.LAN10/100/1,000 MBit/s Intel® I217LMBIOS version AMI Aptio 4.6BIOS features BIOS Flash EPROM update by softwareRecovery BIOSUnified Extensible Firmware Interface (UEFI)Audio type On boardAudio codec Realtek ALC671Audio features Internal speaker supports audio playback, High Definition audio, 5.1 surround soundI/O controller on boardSerial ATA total6thereof SATA III6thereof eSATA2Controller functions Serial ATA II (3 Gbit)Serial ATA III (6 Gbit)NCQAHCIRAID 0/1/5/10InterfacesAudio: line-in1Audio: line-in / microphone1Audio: line-out1Front audio: microphone1Front audio: headphone1USB 2.0 total10InterfacesUSB 3.1 Gen1 (USB 3.0) total4USB front4x 2.0 or 2x 2.0/ 2x 3.0 (optional)USB rear4x 2.0 / 2x 3.0USB internal2VGA1DisplayPort 1 (second DisplayPort optional)DVI 1 (DVI-D)Serial (RS-232) 1 (9pin, 16 byte FIFO, 16550 compatible)Mouse / Keyboard (PS/2)2Ethernet (RJ-45)1Parallel 1 (optional) (25pin with EPP and ECP)eSATA 1 (optional)Interface Module notes Anytime USB charge functionalityInput device / componentsOptical USB wheel mouseInput devices (optional)Optical USB/PS2 tilt wheel mouseKBPC PX ECOMouse M440 ECODrive baysDrive bays total33.5-inch internal bays13.5-inch external bays15.25-inch external bays1Drive bay notes3,5” bay can be used for 2,5” drives; optional external bay as internal 3,5”;SlotsPCI-Express 3.0 x16 1 x (200 mm / 7.87 inch) Low profilePCI-Express 2.0 x4 (mech. x16) 1 x (200 mm / 7.87 inch) Low profilePCI-Express x1 2 x (174 mm / 6.85 inch) Low profileGraphics on boardGraphics brand name Intel® HD Graphics, HD Graphics 4400, HD Graphics 4600 (depending on processor) Shared video memory up to 1,782 MBTFT resolution (VGA)1,024 x 768 pixel1,280 x 1,024 pixel1,360 x 768 pixel1,440 x 900 pixel1,600 x 900 pixel1,600 x 1,200 pixel1,680 x 1,050 pixel1,920 x 1,080 pixelTFT resolution (DVI)1,280 x 1,024 pixel1,360 x 768 pixel1,440 x 900 pixel1,600 x 900 pixel1,680 x 1,050 pixel1,920 x 1,080 pixel1,920 x 1,200 pixelGraphics on boardTFT resolution (DisplayPort)1,280 x 1,024 pixel1,360 x 768 pixel1,440 x 900 pixel1,600 x 900 pixel1,680 x 1,050 pixel1,920 x 1,080 pixel1,920 x 1,200 pixel2,560 x 1,440 pixel2,560 x 1,600 pixel3,840 x 2,160 pixel (requires Intel® Core™ i3, i5 or i7 processor)Graphics features Support for up to three independent displaysDirectX® 11.1HDCP supportOpen CL® 1.2OpenGL® 4.0One DisplayPort connector can be converted to DVI-D or HDMI with an optional external adapterFor multi monitoring mode, graphics card and integrated graphics run in parallel (Microsoft® Windows® 7 or Windows8)Graphics notes up to 1 GB dedicated video memory (main memory owned and locked for graphics use)Tested resolutions, depending on display type additional resolutions and frequencies possibleShared memory depending on main memory size and operating systemResolution (color depth up to 32 Bit/pixel)For TFT we recommend using 60HzElectrical valuesPower efficiency note power supply efficiency (at 230V; 20% / 50% / 100% load) : 88% / 92% / 91%Rated voltage range100 V - 240 VRated frequency range50 Hz - 60 HzOperating voltage range90 V - 264 VOperating line frequency range47 Hz - 63 HzMax. output of single power supply280 WPower factor correction/active power activeMonitor outlet SwitchedPower consumptionPower consumption note See white paper Energy ConsumptionLink to Energy White Paper /dl.aspx?id=cbcd2eac-ee62-448e-af36-a45326c50cbbHeat dissipationHeat dissipation notes See white paper Energy ConsumptionNoise emissionRelated Processors for noise Intel® Core™ i7 4770Standard noise emission2x2 GB, HDD, ODD, WindowsAccording to ISO 7779:2010, ECMA-74Standard noise operation mode: CPU50% load3.4 B / 21 dB(A) Bystander; 24dB(A) Operator positionStandard noise operation mode: HDDload3.3 B / 20 dB(A) Bystander; 24 dB(A) Operator positionStandard noise operation mode: Idlemode3.2 B / 19 dB(A) Bystander; 21 dB(A) Operator positionStandard noise operation mode: ODDload4.4 B / 30 dB(A) Bystander; 36 dB(A) Operator positionStandard noise operation mode: Officeapplications 2.03.2 B / 18 dB(A) Bystander; 21 dB(A) Operator positionBlue angel noise emission according certification According to ISO 7779:2010, ECMA-74 for max. possible configurationBlue angel noise operation mode: HDDload3.9 B = 39 dB (A)Blue angel noise operation mode: Idle3.4 B = 34 dB (A)modeBlue angel noise operation mode: ODD4.5 B = 45 dB (A)loadDimensions / Weight / EnvironmentalDimensions (W x D x H)340 x 382 x 98 mm13.39 x 15.04 x 3.86 inchOperating position horizontal / vertical (optional, feet needed)Weight10 kgWeight (lbs)22.05 lbsWeight notes Actual weight may vary depending on configurationOperating ambient temperature10 - 35 °C (50 - 95 °F)Operating relative humidity 5 - 85 % (relative humidity)ComplianceProduct ESPRIMO E920Model DT8Germany TÜV GSBlauer Engel / Blue AngelEurope CEUSA/Canada FCC Class BcCSAusGlobal RoHS (Restriction of hazardous substances)WEEE (Waste electrical and electronic equipment)Microsoft Operating Systems (HCT / HCL entry / WHQL)EPEAT® Gold (dedicated regions)ENERGY STAR® 6.0 (dedicated regions)Compliance link https:///sites/certificatesAdditional SoftwareAdditional software (preinstalled)Workplace Protect (secure authentication solution)Adobe® Reader® (pdf reader)McAfee Multi Access Security (anti-virus and internet security software; 60 days trial version)Win7: Fujitsu Recovery (hard disk based recovery)Win8: Microsoft Push Button Recovery (hard disk based recovery)Microsoft Office (buy license to activate the pre-installed Microsoft Office)Additional software (optional)Recovery DVD for Windows®Drivers & Utilities DVD (DUDVD)CyberLink PowerDVD BD (playback software for Blu-ray Disc™)CyberLink PowerDVD DVD (playback software for DVD)Nero Essentials XLManageabilityManageability technology DeskUpdate Driver managementPXE 2.1 Boot codeWake up from S5 (off mode)Intrusion switch (optional)iAMT 9.0 (depending on CPU)WoL (Wake on LAN)Manageability software DeskView ClientDeskView Instant BIOS ManagementDeskView components Inventory ManagementBIOS ManagementDriver ManagementSecurity ManagementAlarm ManagementSupported standards DMI (Desktop Management Interface)SMBIOS (System Management BIOS)PXE (Preboot Execution Environment)WMI (Windows Management Instrumentation)WBEM (Web Based Enterprise Management)CIM (Common Information Model)Manageability link /fts/manageabilitySecurityPhysical Security Kensington Lock supportEye for padlockIntegrated cabinet lock (optional)System and BIOS Security EraseDiskBoot sector virus protectionWrite protect option for the Flash EPROMEmbedded security (TPM 1.2)Control of all USB interfacesExternal USB ports can be disabled separatelyControl of external interfacesUser Security User and supervisor BIOS passwordHard disk passwordAccess protection via external SmartCard reader (optional)Access protection via internal SmartCard reader (optional)MiscellaneousKeyboard on (Special Fujitsu keyboard required)Thermal managementExtended lifetimeServiceabilityEasyFixEasyChange for 3.5” HDDEasyChange for optical drivesPackaging informationPackaging dimension (mm)467 x 265 x 540 mmPackaging dimension (inch)18.39 x 10.43 x 21.26 inchMax. quantity / pallet28Material - Weight (g) Carton1180 gMaterial - Weight (lbs) Carton 2.6 lbsMaterial - Weight (g) EPS / PS180 gMaterial - Weight (lbs) EPS / PS0.4 lbsMaterial - Weight (g) PE60 gMaterial - Weight (lbs) PE0.13 lbsPackaging notes printed user documentation is bleached in chlorine free processWarranty period 3 years (depending on country)Warranty type Bring-In / Onsite Service (for countries within region EMEIA, for all other countries depending on local regulations) Recommended Service9x5, Onsite Response Time: Next Business DaySpare Parts availability 5 years after end of product lifeService Weblink /fts/services/supportRecommended AccessoriesDisplay B23T-7 LEDThe FUJITSU B23T-7 LED Display with excellent ergonomics makes intensive office work extremely comfortable.This highly reliable display offers superb usability and power-saving features to help reduce your labor as well as energy costs. With wide viewing angle technology, flexible connectivity, and easy manageability, the FUJITSU B23T-7 LED Display can help you improve productivity.Order Code:S26361-K1496-V140Display B24-8 TE ProThe FUJITSU Display B24-8 TE Pro is made for intensive office work. With visual and mechanical ergonomics this marble-grey display enables fatigue-free working for hours in front of the screen. The large 60.5 cm (23.8-inch) screen allows you to keep always track of all openapplications. This high-quality display works unfailingly around the clock. Easy connectivity, manageability and usability help you increase your productivity.Order Code:S26361-K1577-V140Mouse M440 ECOFujitsu Mouse M440 ECO is made from 100% bio material and has a completely PVC free cable. The elegant M440 ECO works on nearly every surface and follows all your hand movements smoothly and precisely. It features two main buttons and as well as a scroll wheel providing comfortable computing to both right and left-handed users.Order Code:S26381-K450-L200UC&C USB Headset StereoH650eThe UC&C USB Headset Stereo H650e is the ultimate in style andfunctionality. Long, uncomfortable work calls are a thing of the pastthanks to the cushioned ear pads and crystal clear sound. Adjustableheadband and microphone provides the perfect fit for everyone. Optimized for Microsoft® Lync™ the headset displays a red ‘in-call’ LED to let your co-workers know when you’re available, thus helping to boost office productivity.Order Code: S26391-F7139-L10Keyboard KBPC PX ECOFujitsu’s KBPC PX ECO keyboard is the perfect contribution to Green IT. The keyboard is made out of 45% renewable raw material and comes with a PVC free USB cable. In addition, the KBPC PX ECO offers first class comfort and ergonomics. It attracts attention with its impressive modern design and useful extras.S26381-K341-L1** (**: country specific variation)ContactAddress: x-xx-x, street, city, state, ZIP code, country Phone: xx-xxxx-xxxx Fax : xx-xxxx-xxxxEmail:********************.com Website: /[country]2017-04-01 CE-ENdelivery subject to availability. Any liability that the data and illustrations are complete, actual or correct is excluded. Designations may be trademarks and/or copyrights of the respective manufacturer, the use of which by third parties for their own purposes may infringe the rights of such ownerMore informationAll rights reserved, including intellectual property rights. Changes to technical data reserved. Delivery subject to availability. Any liability that the data and illustrations are complete, actual or correct is excluded.Designations may be trademarks and/or copyrights of the respective manufacturer, the use of which by third parties for their own purposes may infringe the rights of such owner.For further information see /terms_of_use.html Copyright © Fujitsu Technology Solutions。

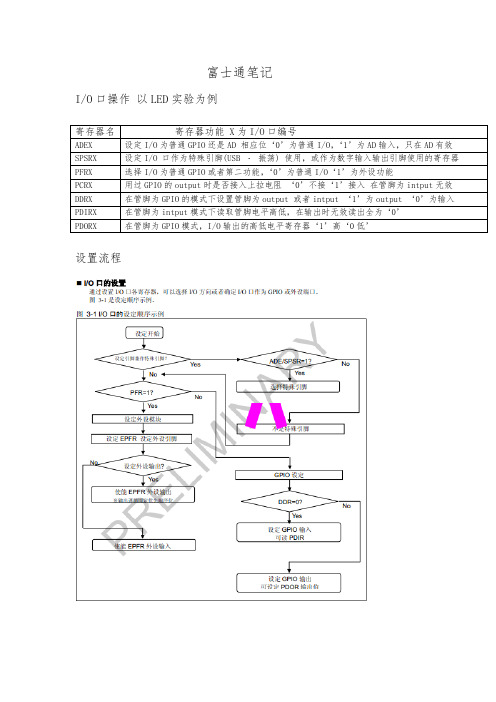

富士通基本操作

富士通笔记I/O口操作以LED实验为例设置流程以按键控制LED为例初始化LED管脚PFR相应位为‘0’设置管脚为GPIO模式,PDOR 设置相应位1输出为1,DDR设置为输出模式相应位为1,key管脚初始化设置PFR相应位为‘0’,DDR相应位设置为‘0’,通过读取PDIR 判断输入情况*** 外部中断操作以EXTI KEY 为例操作流程设置管脚映射;如FM3_GPIO->EPFR06 |= (2 << 2);/* 将INT01映射到INT01_1 */使能外部中断通道如NVIC_EnableIRQ(EXINT0_7_IRQn); /* 使能ch.0 to ch.7的中断*/DMAC (直接内存访问控制器)以DMA_Memory_To_Memory为例DMAC:操作步骤1 具体如下设置首先DMACA:——》寄存器设置是否使能传送使能——》DMAC触发方式——》数据缓冲长度——》设置DMACB寄存器设置——》传输模式——》传输数据宽度——》设置传送源地址递增或者不变——》目标地址递增或者递减——》完成后是否使能中断源——》DMACSAX DMA传送源地址——》DMACDAX DMA 目标地址——》DMACR使能全局DMA——》(以下是打开了传输完成中断设置)——清除NVIC_ClearPendingIRQ(DMAC0_IRQn);DMAC中断——》使能NVIC_EnableIRQ(DMAC0_IRQn);——》设置优先级NVIC_SetPriority(DMAC0_IRQn, 1); (中断函数)中断标志位清零FM3_DMAC->DMACB0 &= ~(7ul << 16);双时钟定时器以32为周期中断模式为例例程步骤写入0xFFFFFFFF到Timer1IntClr清除中断源——》设置Timer1Control寄存器设置是否使能设置时一般为否,工作模式,中断使能,分频数值,计数模式32位or16位,bit0位设置处单次模式外一般为‘0‘。

ADD9000说明书

Automotive Digital Diagnostic Tools 汽车数字诊断专用工具系列汽车数字诊断工具箱技术手册北京爱德盛业科技有限公司ADD3500无线汽车异响探测仪汽车数字诊断工具箱ADD9000Automotive Digital Diagnostics Tools Kits目录一、汽车传感器模拟测试仪 (3)二、汽车专用万用表ADD51 (20)三、汽车专用红外测温仪 (23)四、汽车短路/断路检测仪ADD330 (36)五、汽车数字钳表 (44)六、汽车电解液/冷却液/检测仪ADD501 (49)七、空调专用数字温度计 (51)八、数字式激光转速表使用说明书 0九、数显测试电笔 (2)十、万用测试线 (4)一、汽车传感器模拟测试仪一.安全指引..................................................................................................................................3 二.重要提示..................................................................................................................................3 三.目测检查:..............................................................................................................................4 四.技术指标..................................................................................................................................4 五.仪器操作.. (11)一.安全指引z 戴上安全防护眼镜、 穿上安全工作服、不要带手饰和留长头发。

96000 Series RF Reference Source 操作员手册说明书

May 2014 (Simplified Chinese) © 2014 Fluke Corporation. All rights reserved. Specifications are subject to change without notice. All product names are trademarks of their respective companies.96000 SeriesRF Reference Source操作员手册有限担保及责任范围Fluke 公司保证其每一个Fluke的产品在正常使用及维护情形下,其用料和做工都是毫无瑕疵的。

保证期限是一年并从产品寄运日起开始计算。

零件、产品修理及服务的保证期是 90 天。

本保证只提供给从Fluke 授权经销商处购买的原购买者或最终用户, 且不包括保险丝、电池以及因误用、改变、疏忽、或非正常情况下的使用或搬运而损坏(根据 Fluke 的意见而定)的产品。

Fluke 保证在 90 天之内,软件会根据其功能指标运行,同时软件已经正确地被记录在没有损坏的媒介上。

Fluke 不能保证其软件没有错误或者在运行时不会中断。

Fluke 仅授权经销商将本保证提供给购买新的、未曾使用过的产品的最终用户。

经销商无权以 Fluke 的名义来给予其它任何担保。

保修服务仅限于从 Fluke 授权销售处所购买的产品,或购买者已付出适当的Fluke国际价格。

在某一国家购买而需要在另一国家维修的产品,Fluke 保留向购买者征收维修/更换零件进口费用的权利。

Fluke 的保证是有限的,在保用期间退回 Fluke 授权服务中心的损坏产品,Fluke有权决定采用退款、免费维修或把产品更换的方式处理。

欲取得保证服务,请和您附近的Fluke服务中心联系,或把产品寄到最靠近您的Fluke服务中心(请说明故障所在,预付邮资和保险费用,并以 FOB 目的地方式寄送)。

富士通单片机中文手册

富士通电子设备用户手册F2MC-16LX Starter kit用户手册2注意事项・本资料有关内容如有变更恕不另行通知。

・本资料内所记载的设备运行情况及电路实例均是以半导体设备的标准规格及正确的使用方法为前提的,我们并不保证实际使用时所有机械的正常运作。

因此,在使用此设备时,顾客将完全承担相应的使用责任。

如有因使用此设备而造成的损害,本公司将不承担任何责任。

・本资料内所记载的设备运行情况以及电路图内所含有的技术资料并不代表可以任意使用本公司以及第三责任方的专利权以及著作权。

禁止通过本资料对第三责任方的知识产权以及相关的权利进行侵犯。

本公司对于此类相关行为以及所产生的后果将不负任何责任。

・本资料内若含有属于《外国汇率以及外国贸易法》范畴内的商品,或者含有相关范畴内的技术,则在出口本商品时必须得到相关法律的认可。

Copyright© 2005 FUJITSU LIMITED ALL right reserved © Fujitsu3目录前言 (6)1Starter-kit的安装方法 (7)1.1PC机上的软件安装 (13)1.1.1USB驱动的安装 (14)1.1.2综合开发环境SOFTUNE(限定版)的安装 (15)1.1.3ACCEMIC MDE demo version(trial版)的安装 (20)1.1.4评测板的设定以及与PC机的连接 (24)1.1.5SOFTUNE的设定与启动 (27)1.1.6ACCEMIC MDE的设定与启动 (30)1.1.7ACCEMIC MDE退出 (44)1.1.8SOFTUNE的退出 (44)1.1.9关闭Accemic的情况下启动单片机 (45)2编写使LED闪烁的程序 (46)2.1关于LED的介绍 (46)2.2LED为何会发光 (47)2.3利用单片机使LED发光的方法 (48)2.4LED发光程序的制作及运行 (51)2.4.1程序概要 (51)2.4.2程序的制作与运行 (52)2.5LED闪烁程序的制作与运行 (54)2.5.1程序概要 (54)2.5.2程序的制作与运行 (55)3用开关SW控制LED的亮灭 (57)3.1单片机如何检测SW的状态 (57)3.2通过SW控制LED程序的制作与运行 (58)3.2.1程序概要 (59)3.2.2程序的制作与运行 (59)4如何使用蜂鸣器 (61)4.1蜂鸣器内所用的材料 (61)4.1.1压电性的特点 (61)4.1.2压电材料的应用 (62)4.2单片机与压电蜂鸣器 (62)-- © Fujitsu44.2.1自励式与他励式 (63)4.2.2由单片机发出的脉冲波 (63)4.3如何使用PPG使蜂鸣器发出声音 (63)4.3.1L幅宽与H幅宽的设定 (64)4.3.2PPG count clock (64)4.4蜂鸣器程序的制作与运行 (65)4.4.1程序概要 (65)4.4.2程序的制作与运行 (67)4.4.3改变蜂鸣器的音色 (68)5利用中断来控制LED (69)5.1“中断”的概念 (69)5.2利用“中断”来检测SW的状态的方法 (70)5.3通过SW控制LED的程序(中断法) (71)5.3.1程序概要 (71)5.3.2程序的制作与执行 (72)6利用timer(定时器)来使LED闪烁 (75)6.1什么叫timer(定时器) (75)6.2通过Timer中断控制LED闪烁的程序 (76)6.2.1程序概要 (76)6.2.2程序的制作与运行 (78)7如何使用A/D(模/数)转换器 (81)7.1模拟信号与数字信号 (81)7.1.1A/D转换器的概要 (82)7.1.2滑动变阻器 (83)7.2制作一个表示电压数值的程序 (83)7.2.1程序概要 (83)7.2.2程序的制作与执行 (87)8如何使用温度传感器 (89)8.1关于温度传感器 (89)8.2温度传感器的使用方法 (90)8.3制作一个表示温度的程序 (91)8.3.1程序概要 (91)8.3.2程序的制作与执行 (94)A附录A(程序制作流程) (96)B附录B(寄存器的写入/读出方法) (104)C附录C(头文件包含路径的设定方法) (105)© Fujitsu5前言首先,非常感谢您购买本公司的Starter-kit产品。

FMU90资料中文说明书

配备1个或 2个超声波探 头可 对明 渠和 测量 堰中 的介 质 进行流量测量 仅用1个探 头即 可同 时测 量溢 流情 形下 介质 的物 位和 流 量 具有回水检测(2个探头)功能或淤泥检测功能的流量 测量 最多可配置3个 累加 器( 不可 清零)和 3个计数器(可 清零) 提供用 于控 制外部 单元 的计 数脉 冲输 出或 时间 脉冲 输 出

Endress + Hauser

7

模拟量输出 继电器输出

Pronsonic S FMU90

输出

数目 输出信号

报警信号

1路或2路,取决于变送器的具体型号

根据变送器的具体型号进行配置: 带HART的4...20mA1) 不带HART的0...20mA

4...20mA(可选) — -10%(3.6mA) — 110%(22mA) — 保持(末次电流值) — 用户自定义 0...20mA — 110%(21.6mA) — 保持(末次电流值) — 用户自定义

数目 类型 指定功能

开关功率 故障信息

1个,3个或6个,取决于仪表的具体型号 无电势继电器,,可转换

界值(界内、界外、趋势指示、物位边界) 计数脉冲1)(脉冲宽度可调) 时间脉冲1)(脉冲宽度可调) 报警/诊断(如回水1)、淤泥1)、回波损耗指示) 泵控制(多级泵控制/固定边界检测/泵速率控制) FMU 90-*3**********和FMU 90-*4**********附加泵控制 格栅控制(差值测量或相对值测量) 现场总线继电器

输出阻尼 负载 最大脉动电压 最大噪声电压

在0...1000s 间自由选择 最大为600Ω,其它影响可忽略不计 Uss=200mV,频率处于47...125Hz间(负载:500Ω) Ueff=2.2mV,频率处于500...10kHz间(负载:500Ω)

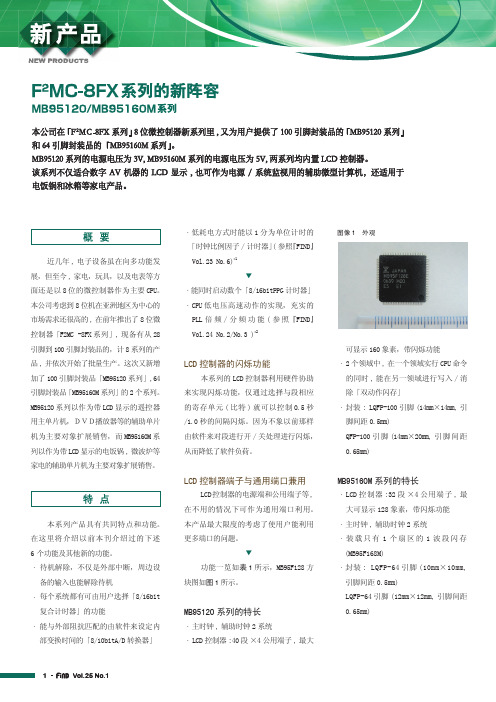

用于家电产品的富士通8位微控制器系列

Dual-O.P.-FLASH 上列:48K字节 下列:12K字节 装载

F2MC-8FX MB95120系列

用于系统待机时的低功耗操作 ɾ使用计时器/计数器 硬件实现1分计数!

LCD控制器 ɾ最大可以显示128像素 ɾ带闪烁功能 →利用硬件实现闪烁,减低软件负荷! 用途: ɾ显示设定温度 ɾ显示实际温度 ɾ显示设定模式及设定参数 ɾ显示计时器设定时间

F2MC-8FX 开发环境的硬件构成如 图 4 所示,表 2 是开发工具一览表。

在该系列里,备有带有通用评估

表 1 品种构成和功能概要

项目 分类 ROM(FLASH)容量 RAM容量 时钟系统 CPU功能 IO端口(最大) 时基计时器 监视计时器 8/16bit复合计时器

8/16bitPPG计时器

16bitPPG计时器

12路

8路

可选择8或10比特分辨率。可选择采样/变换时间

12路

8路

可检出上沿,下沿,双沿

40seg×4com -

32seg×4com 5V产品为选项。可监测电源电压,电压低下时由内部发生复位信号。

停止/休止/辅助时钟/时钟方式

LQFP-100(引脚间距0.5mm) QFP-100(引脚间距0.65mm)

̚

客户目标

表 2 开发环境一览表

后台监视器 调试专用适配器 MCU面板 (装有评估芯片)

封装转换用转换板 评估面板

软件

MB95120系列

MB95160M系列

MB2146-09(BGM适配器)

MB2146-301A (MB95FV100D-101:

装有3V 专用品)

MB2146-303A (MB95FV100D-103:

Fujitsu USB Port Replicator PR09 数据册说明书

Data SheetFujitsu Accessory USB Port Replicator PR09 ConnectivityHigh-End Smart ConnectivityThe Fujitsu USB Port Replicator PR09 is the perfect solution for shared desk environments within a hyperconnected world. It connects your mobile system to your main peripherals with a single USB plug. This Port Replicator is equipped with the most powerful DisplayLink chipset supporting high performance video streaming with Dualhead-DisplayPort. Highest data throughput is guaranteed due to an USB Type-C based Gen2 Hub-Controller enabling up to 10 Gbit/s data streaming. The newest version of USB Power Delivery chipset (PD3.0) provides powerful charging during your workday.Main FeaturesDualhead high-end graphics up to 4kSinglehead up to 5kGigabit-LAN integratedUSB Type-C upstreamUSB Power Delivery (PD3.0)Multiport USB 3.1 Gen1 DFP hubMultiport USB 3.1 Gen2 DFP hubSPDIF digital audio 2.0HighlightsDeveloped for shared multi-vendor system workplacesSystem independent investment protection (TCO)Future proof & backwards compatible (e.g. to USB-A systems)Easy IT integration (PXE / MAC spoofing support)Mac Address Pass Through (MAPT) for Fujitsu Notebooks enabling MAPT in the BIOS from S3 or lower.Fast one-cable connection for data and powerGlobal country certificationsAppealing design ID workplace deviceReliabilityHighest availabilityExperience out of huge installed base of Fujitsu USB Port ReplicatorsUSB Port Replicator PR09Technical specificationsLED On/Off switch (blue)USB Power Delivery (amber)USB connection (green)LAN traffic, rear side (green/yellow) Color BlackRefresh rateSupported refresh rate (32 bit color depth)1x up to 5,120 x 2,880 @ 60 Hz 2x up to 4,096 x 2,160 @ 60 HzInterfacesPower on switch 1 default: ON (PR09 from Rev.:02)Power supply 1 AC/DC Power Adapter 120 W (package content)DC-in20 VUSB downstream7 (4x USB-A & 3x USB-C)USB upstream via USB Type-C cable (1 m)USB Type-C (UFP) 1 w/ USB PD (60 W)USB Type-C 3.1 Gen2 (DFP) 3 thereof 1x BC1.2 w/ 10.5 WUSB Type-C cable 1 (5A Gen2) (package content)USB Type-A 3.1 Gen1 (DFP)4DisplayPort 2 (DP1.2a as Dualmode DP++)Audio 1 SPDIF (2.0)Ethernet (RJ-45) 1 x Gigabit LAN (based on chip Realtek RTL8211F)Notes For Notebook-systems still using USB Type-A:order USB-A to USB-C Adapter S26391-F6058-L102 (1pc.)Several adapters availble: /de/products/computing/peripheral/accessories/connectivity Kensington Lock support yesSystem requirementsRequired interface USB Type-CSystem requirements For office and productivity:Intel Core i3 2+ GHz / Intel Core M / AMD Trinity or betterUSB 3.1 Gen 2 recommanded40MB of free storage spaceSupported operating systems Windows 11Windows 10Windows 7Special featuresUSB power delivery ver 3.0DisplayLink“Plug and Display” certifiedUSB downstream7 (4x USB-A & 3x USB-C)USB upstream via USB Type-C cable (1 m)Electrical valuesPower consumption Maximum usage: 120 WAverage office usage: 82 WWithout USB PD: 3 WDC Off: 0.07 WPower supply input100-240 V AC50-60 HzPower supply output20 V DC at 6 AComplianceEurope CESwitzerland ENVRussia EACUSA/Canada FCC Class BICES-003 Class BcTUVusUL/cULJapan JEITAVCCIPSE (AC-Adapter)JISCSouth Korea KCSingapore S-MarkChina CCC (AC-Adapter)Australia/New Zealand RCMTaiwan BSMISaudi Arabia SASOCompliance link https:///sites/certificatesDimensions / Weight / EnvironmentalMiscellaneous MAC address showDimensions (W x D x H)200 x 97.6 x 29 mmCable length USB-C cable: 1 mWeight340 g (device only w/o AC-Adapter)Operating ambient temperature 5 - 35 °C (41 - 95 °F)Storage ambient temperature 5 - 45 °C (41 - 113 °F)Operating relative humidity10 - 85 % (non condensing)Package contentUSB Port Replicator PR09AC/DC Adapter 20 V, 120 WEU-power cord, 1,8 mUSB Type-C cable, 1 mQuick Start GuideService Desk & Warranty InformationsSafety NotesInformationcard for driver downloadOrder codeS26391-F6007-L500EAN: 4057185642316WarrantyWarranty period 3 yearsWarranty type Bring-In / Send-In Service (depending on country)Warranty Terms & Conditions /warrantyDigital bug fixes Subject to availability and following their generic release for the product, bug fixes and function-preserving patchesfor product-related software (firmware) can be downloaded from the technical support at: https://support.ts.fujitsu.com/ free of charge by entering the respective product serial number. For application software supplied togetherwith the product, please directly refer to the support websites of the respective software manufacturer.Spare Parts availability at least 5 years after shipment, for details see https:///Service Weblink /emeia/products/product-support-services/CONTACTFujitsu Technology Solutions GmbH Website: 2023-11-27 EM-ENworldwide project for reducing burdens on the environment.Using our global know-how, we aim to contribute to the creation of a sustainable environment for future generations through IT.Please find further information at http://www./global/about/environmenttechnical specification with the maximum selection of components for the named system and not the detailed scope ofdelivery. The scope of delivery is defined by the selection of components at the time of ordering.Technical data is subject to modification and delivery subject to availability. Any liability that the data and illustrations are complete, actual or correct is excluded. Designations may be trademarks and/or copyrights of the respective owner, the use of which by third parties for their own purposes may infringe the rights of such owner.The overall product has been designed and manufactured for general office use, regular personal use and ordinary industrial use.More informationAll rights reserved, including intellectual property rights. Designations may be trademarks and/or copyrights of therespective owner, the use of which by third parties for their own purposes may infringe the rights of such owner. For further information see https:///global/about/resources/terms/ Copyright 2023 Fujitsu Technology Solutions GmbH。

StartKit 富士通8位单片机入门手册

FUJITSU MICROELECTRONICSSUPPORT SYSTEM SS01-26033-1EF2MC-8FX Family8-bit MICROCONTROLLERMB95200H/210H SeriesSTARTER KIT MB2146-410A-01-ESETUP GUIDEPREFACEThank you for purchasing the F2MC*1-8FX Family Starter Kit: MB2146-410A-01-E*2.This product is a starter kit for F2MC-8FX MB95200H/210H series, which comes with MB2146-08-E (F2MC-8FX Family MB95200 Series BGM Adapter)*3, MB2146-410A-E (F2MC-8FX FamilyMB95200H/210H Series Evaluation Board)*4, and F2MC-8L/8FX Family S OFTUNE ProfessionalPack Evaluation Version*5.This manual explains how to use the Starter Kit. Be sure to read this manual before using the product.For mass production/evaluation MCUs for this product, consult with sales representatives or supportrepresentatives.*1 : F2MC is the abbreviation of FUJITSU Flexible Microcontroller.*2 : Referred below as the “Starter Kit”.*3 : Referred below as the “BGMA”.*4 : Referred below as the “EV-Board”.*5 : Referred below as the “S OFTUNE”.■Handling and useHandling and use of this product and notes regarding its safe use are described in the manuals forproducts bundled with the Starter Kit.Follow the instructions in the manuals to use this product.Keep this manual at hand so that you can refer to it anytime during use of this product.■European RoHS complianceProducts with a -E suffix on the part number are European RoHS compliant products.■Notice on this documentAll information included in this document is current as of the date it is issued. Such information issubject to change without any prior notice.Please confirm the latest relevant information with the sales representatives.■Caution of the products described in this documentThe following precautions apply to the product described in this manual.Indicates a potentially hazardous situation which could result in death or seriousinjury and/or a fault in the user’s system if the product is not used correctly.Electric shock, Damage Before performing any operation described in this manual, turn off all the powersupplies to the system.Performing such an operation with the power on may cause an electric shock ordevice fault.Electric shock, Damage Once the product has been turned on, do not touch any metal part of it.Doing so may cause an electric shock or device fault.Indicates the presence of a hazard that may cause a minor or moderate injury, dam-ages to this product or devices connected to it, or may cause to loose software re-sources and other properties such as data, if the device is not used appropriately.Cuts, Damage Before moving the product, be sure to turn off all the power supplies and unplug thecables. Watch your step when carrying the product. Do not use the product in anunstable location such as a place exposed to strong vibration or a sloping surface.Doing so may cause the product to fall, resulting in an injury or fault.Cuts The product contains sharp edges that are left unavoidably exposed, such as jump-er plugs.Handle the product with due care not to get injured with such pointed parts.Damage Do not place anything on the product or expose the product to physical shocks. Donot carry the product after the power has been turned on.Doing so may cause a malfunction due to overloading or shock.Damage Since the product contains many electronic components, keep it away from directsunlight, high temperature, and high humidity to prevent condensation. Do not useor store the product where it is exposed to much dust or a strong magnetic or elec-tric field for an extended period of time.Inappropriate operating or storage environments may cause a fault.Damage Use the product within the ranges given in the specifications.Operation over the specified ranges may cause a fault.Damage To prevent electrostatic breakdown, do not let your finger or other object come intocontact with the metal parts of any of the connectors. Before handling the product,touch a metal object (such as a door knob) to discharge any static electricity fromyour body.Damage When turning the power on or off, follow the relevant procedure as described in thisdocument.Before turning the power on, in particular, be sure to finish making all the requiredconnections. Furthermore, be sure to configure and use the product by following theinstructions given in this document.Using the product incorrectly or inappropriately may cause a fault.Damage Always turn the power off before connecting or disconnecting any cables from theproduct. When unplugging a cable, unplug the cable by holding the connector partwithout pulling on the cable itself. Pulling the cable itself or bending it may exposeor disconnect the cable core, resulting in a fault.DamageBecause the product has no casing, it is recommended that it be stored in the orig-inal packaging. Transporting the product may cause a damage or fault. Therefore,keep the packaging materials and use them when re-shipping the product.•The contents of this document are subject to change without notice.Customers are advised to consult with sales representatives before ordering.•The information, such as descriptions of function and application circuit examples, in this document are presented sole-ly for the purpose of reference to show examples of operations and uses of FUJITSU MICROELECTRONICS semi-conductor device; FUJITSU MICROELECTRONICS does not warrant proper operation of the device with respect to use based on such information. When you develop equipment incorporating the device based on such information, you must assume any responsibility arising out of such use of the information. FUJITSU MICROELECTRONICS assumes no liability for any damages whatsoever arising out of the use of the information.•Any information in this document, including descriptions of function and schematic diagrams, shall not be construed as license of the use or exercise of any intellectual property right, such as patent right or copyright, or any other right of FUJITSU MICROELECTRONICS or any third party or does FUJITSU MICROELECTRONICS warrant non-in-fringement of any third-party's intellectual property right or other right by using such information. FUJITSU MICRO-ELECTRONICS assumes no liability for any infringement of the intellectual property rights or other rights of third parties which would result from the use of information contained herein.•The products described in this document are designed, developed and manufactured as contemplated for general use, including without limitation, ordinary industrial use, general office use, personal use, and household use, but are not designed, developed and manufactured as contemplated (1) for use accompanying fatal risks or dangers that, unless extremely high safety is secured, could have a serious effect to the public, and could lead directly to death, personal injury, severe physical damage or other loss (i.e., nuclear reaction control in nuclear facility, aircraft flight control, air traffic control, mass transport control, medical life support system, missile launch control in weapon system), or (2) for use requiring extremely high reliability (i.e., submersible repeater and artificial satellite).Please note that FUJITSU MICROELECTRONICS will not be liable against you and/or any third party for any claims or damages arising in connection with above-mentioned uses of the products.•Any semiconductor devices have an inherent chance of failure. You must protect against injury, damage or loss from such failures by incorporating safety design measures into your facility and equipment such as redundancy, fire pro-tection, and prevention of over-current levels and other abnormal operating conditions.•Exportation/release of any products described in this document may require necessary procedures in accordance with the regulations of the Foreign Exchange and Foreign Trade Control Law of Japan and/or US export control laws.•The company names and brand names herein are the trademarks or registered trademarks of their respective owners.1. Product OverviewThis product is a set of Starter Kit (MB2146-410A-01-E) of MB95200H/210H series. It is composed of a BGMA (MB2146-08-E) and an EV-board (MB2146-410A-E). Combining the S OFTUNE Workbench on PC, the Starter kit enables the quick start of development before the user system is ready.1.1 Objective and DeliverableThe Starter kit (MB2146-410A-01-E) provides users a complete development platform. Before startusing the Starter Kit, make sure that the following devices are placed in the package:•BGMA (MB2146-08-E):1PCS;•EV-board (MB2146-410A-E):1PCS;•USB cable:1PCS•CD-ROM (S OFTUNE, manuals, sample code):1PCS•Hardcopy (China RoHS report, quick start guide):1PCS1.2 System BlockTo setup a debugging system, connect a PC, a BGMA and an EV-board together as shown below:1.3 Handling PrecautionsThe Starter Kit can be used in connection with its bundled products. To ensure correct use of thisproduct in a proper environment, observe the following guideline:Follow the instructions described in each manual for the bundled product to use this product.1.4 FeatureThe MB95200H/210H Series starter kit is the best for a performance and functional evaluation, anda check of operation before including MB95200H/210H Series in a user's system.Below, the feature of the BGM debugger for MB95200 Series is shown.•Microcomputer operation voltage. It corresponds to +2.7V to +5.5V.(The maximum and minimum of microcomputer operation voltage and frequency of operationdiffers with each MCU. refer to the documents (a data sheet, hardware manual, etc.) of eachdevice relation for the operation voltage and frequency of MCU of operation.)•Compact development environment, a light and small BGM Adapter.•Since a monitor program is performed in exclusive memory space, it does not consume usermemory space.•Continuation execution, step execution and break correspondence.•It connects with a host computer by the USB interface.1.5 Hardware SetupIn the hardware setup procedure, you configure and connect the hardware products. This chapter in-cludes the configuring and connecting procedure for each product in order. Check the contents andcomplete the hardware setup.•Configuration of each product- Configuring EV-Board•Connection of each product- Connecting BGMA and EV-board- Connecting EV-board power supply2. BGMA Manual This chapter gives introduction how to setup BGMA.2.1 BGMA OverviewBelow is the close look of the BGMA. The Part Number of the MB95200 Series BGMA is MB2146-08-E. It provides a debug platform for the MB95200 Series MCU in a small size (55.7mm (W) ×127mm (D) × 30mm (H)).Figure 2.1-1 BGMA overview2.2 Function List*1 : The value varies depending on the operating frequency, the machine clock or the analog guar-anteed range.*2 : The value is 2.88 V when the low-voltage detection reset is used.IDFunction description Remarks 1Support MB95200 Series MCU MCU MAX machine clock: 16.25 MHz MCU power voltage: 2.4V*1*2 to 5.5V*12Break pointer 256 software breakpoints 3USB interface to PC/S OFTUNE Compatible to USB protocol version 1.141-Line UART interface to the MB95200 Series MCU The Baud rate is 62,500 bps 5Support the MCU flash programming for engineering development Provide high voltage for flash operation.The program and read speed is about 800 B/S.2.3 IDC10 Interface DescriptionPin Number Pin Name Description1UVCC Target MCU Vcc2GND Target MCU Vss3RSTIN Target MCU reset input4RSTOUT Target MCU reset output5RSV Reserved6RSV Reserved7RSV Reserved8DBG Target MCU debug pin9RSV Reserved10RSV Reserved2.4 BGMA USB ConfigurationThe BGMA is provided with a USB cable. Connect the BGMA to a PC with a USB cable. If theconnection is right, the following window will pop up. Follow the instructions displayed, and thenclick “Next”,Figure 2.4-1 Install BGMA in Windows (1)Select “Install from a list or specific location (Advanced)”, then click “Next”,Figure 2.4-2 Install BGMA in Windows (2) Select “…\Drivers” from the folder where SOFTUNE is installed, click “Next”,Figure 2.4-3 Install BGMA in Windows (3)Select BGMA (MB2146-08) as displayed below, and then click “Next”,Figure 2.4-4 Install BGMA in Windows (4)Windows will install the driver automatically. Click “Finish” after the driver has completed the installation normally. Then users can find the BGMA is recognized as MB2146-08 in Windows system.Figure 2.4-5 BGMA is installed in Windows2.5 LED DescriptionFirst, only plug USB cable to PC, check the Power LED on BGMA turns Green. Refer to Figure 2.5-1.Figure 2.5-1 BGMA Power LED (1)Second, plug IDC10 cable to the EV-board (target MCU board), then turn on EV-board. After thatcheck Power LED on the BGMA turns Orange. Refer to Figure 2.5-2.Figure 2.5-2 BGMA Power LED (2)3. EV-board ManualThis chapter gives introduction how to setup EV-board.3.1 EV-board OverviewMB95200H/210H MCU EV-board is provided as a user-friendly introductory and evaluation plat-form for the MB95200H/210H MCU Family microcontroller. Figure 3.1-1 below is a close look ofEV-board.when debugPower supply either frombatteries (below the PCB)or from 2-pin header3.2 Function ListThe EV-board consists of a board and a sample firmware. The board provides a useful platform forusing the MCU and its peripherals. It is a useful development platform together with a BGMA (PN:MB2146-08-E) and a S OFTUNE. It features the following functions,•Clock and sub-clock•USB 5V power IF, external 5V power IF and the battery•Reset circuit and reset key•Provide IDC10 debug interface•LEDs for general use, LED1 indicates DBG pin work status•Provide one buzzer to demonstrate timer output•2 keys for general use•Potentiometer and temperature sensor•RS-232 level converter and DB9 interface (MAX232)•LIN circuit reserved•SIO 4 pins reserved•All MCU ports are easy accessible through test pins•Optional Starter kit to support each available MCU packages3.3 EV-board Schematic3.4 HW Module Description and Jumper settings3.4.1 Power ModuleEV-board has 4 kinds of power supply for user to choose. Please read below instructions before us-ing.•DC Adaptor: 9V DC:Output voltage: 9VConnection: Connector (CN6)•Battery:QTY: 4PCS;Model: AA;Nominal voltage: 1.5V.Connection: Socket for Battery•External Power Supply:There are 2 test points (TP1&2) on EV-board which can supply power to target board (EVboard).Power on method: short L3 on EV-board; then connect anode of DC power to TP1 (MCU Vcc) andcathode to TP2 (MCU GND).•USB cable:The Mini-B USB receptacle is only for supplying power to EV board by PC USB port. The currentand power of this method is limited in 100mA/0.5W.Please make sure to supply stable power via the Mini-B USB receptacle while operation.If any of the power supplies is connected to the EV-board correctly, power LED (LED5) onthe EV-board will be on. Refer to Figure 3.4.1-1.The following two power supplies are recommended. Please follow the settings below,Table 3.4.1-1 Power Supply SelectionPlease do not connect several power supplies at the same time.3.4.2 BGMA InterfaceTo start the debug using a BGMA, users shall connect IDC10 socket from the BGMA to CN1 on an EV-board, and J2 shall be open in a debug mode. In a normal (free-run) mode, J2 shall be closed to enable reset key S3. Refer to Figure 3.4.2-1.Figure 3.4.2-1 Debug InterfaceTable 3.4.2-1Power supplyHeader nameSettings4 AA batteries from BT1on the back of the EV-board.J1: BAT.9V DC from CN6J1: 9V.MCU Mode Header nameSettingsDebug modeJ2Normal mode J23.4.3 Clock SettingsThe MB95200H/210H series MCU uses an internal main CR as a clock source by default. Users can select on-board crystal as a main clock and a sub-clock. Follow the settings below:Table 3.4.3-13.4.4 Buzzer ModuleA buzzer module is provided to demonstrate an 8/16 composite timer output (a continuous mode).To enable buzzer module, follow the table below:Table 3.4.4-13.4.5 A/D ModuleVR1 and VR3 are to demonstrate a MCU A/D converter usage. Select VR1 or VR3 by the following table.VR1 is connected to MCU A/D channel 1, and VR3 is connected to MCU A/D channel 0.Table 3.4.5-1ClockHeader nameSettingsMain clock SW3: X1, X0Sub-clock SW3: X1A, X0AModulesHeader nameSettingsBuzzer:BUZ1SW1: BUZ.ModulesHeader nameSettingsA/D: VR1SW2: VR1A/D: VR3SW2: VR33.4.6 LED ModuleThere are four LEDs on EV-board to demonstrate the I/O function.Enable LED2, LED3 and LED4 in the following table,Table 3.4.6-1* : LED module has four LEDs in total, but P12 (LED1) is not active in a debug mode using BG-MA.3.4.7 Key ModuleKey S1 and key S2 are provided to demonstrate an external interrupt function. Enable these two keys by the following table.Key S1 is connected to external Int7, and key S2 is connected to external Int6.Table 3.4.7-1ModulesHeader nameSettingsLED*:LED2, LED3, LED4SW2:LED2, LED3SW1: LED4ModulesHeader nameSettingsKey: S1, S2SW2: S1, S23.4.8 Lin-UART ModuleLin-UART module can be configured as a LIN or an UART module. Enable each module by the following table.The UART module features an RS232 transceiver and a standard DB9 interface with PC.Lin module enables an easy setup of Master/Slave communication by a Lin bus.Table 3.4.8-1* : LIN module is optional; contact your local distributor for the EV-board with a LIN module.ModulesHeader nameSettingsUARTSW2: SOT, SINJ5: UART J6: UARTLIN*SW2:SCK, SOT, SINJ5: LIN J6: LIN4. Sample Code Manual4.1 Topic ListThe following sample codes are provided with MB95200H/210H MCU Starter Kit,•IO_LED projectIn this example, the 3 LEDs will be on in the following sequence:...->LED2->LED3->LED4...•A/D_Potentiometer projectIn this example, the 3 LEDs will display “on” or “off” according to the arrow direction of VR3.•Timer_Buzzer project (Continuous timer)In this example, Buzzer will be on once by pressing Key S1; Buzzer will be on twice by press-ing Key S2.•ExInt_Key ProjectPress Key S1, the 3 LEDs will be on in the following sequence:...->LED4->LED3->LED2...Press Key S2, the 3 LEDs will be on in the following sequence:...->LED2->LED3->LED4...•UART projectIn this example, the MCU works in an asynchronous mode.(9,600bps, 1 stop bit, no parity)After a reset, the MCU will send "Welcome to the LIN-UART (asynchronous mode) ofMB95200series (8FX)" to RS232 transceiver.Then the MCU feedbacks any bytes it received.•SIO projectThis example uses two EV-boards to demonstrate the SIO (synchronous mode) function.(9600bps)One MCU keeps sending data while the other keeps receiving. One LED is toggled to indicatethe communication is correct.•LIN slaveIn this example, the MCU is running in a Lin Slave mode. After a reset, the MCU is waitingfor data from the Master. If the data is received correct, LED4 starts twinkling.•LIN masterIn this example, the MCU is running in a Lin Master mode. After a reset, the MCU starts send-ing data to a Slave. If the Master gets correct data from the Slave, the MCU restarts sending.While sending data to the Slave, LED2 keeps twinkling.4.2 Project StructureThe Sample code is organized by the following structure in each project. Here take IO_LED projectfor example shown in Figure 4.2-1.Figure 4.2-1 I/O_LED Project Structure4.3 Source Code File DescriptionFive files are available in each sample code source code folder shown below,Figure 4.3-1 Source Code Files17The MB95200.h and the MB95200.asm are header files, including MB95200H/210H MCU I/Oregisters definition;Here take PDR0 for example. In MB95200.h, PDR0 is defined as below./* REGISTER BIT STRUCTURES */typedef union{ /* Port0 */_BYTE byte;struct{_BYTE P00:1;_BYTE P01:1;_BYTE P02:1;_BYTE P03:1;_BYTE P04:1;_BYTE P05:1;_BYTE P06:1;_BYTE P07:1;} bit;struct{_BYTE P00:1;_BYTE P01:1;_BYTE P02:1;_BYTE P03:1;_BYTE P04:1;_BYTE P05:1;_BYTE P06:1;_BYTE P07:1;} bitc;} PDR0STR;……__IO_EXTERN PDR0STR IO_PDR0; /* Port0 */#define _pdr0(IO_PDR0)#define PDR0(IO_PDR0.byte)#define PDR0_P00(IO_PDR0.bit.P00)#define PDR0_P01(IO_PDR0.bit.P01)#define PDR0_P02(IO_PDR0.bit.P02)#define PDR0_P03(IO_PDR0.bit.P03)#define PDR0_P04(IO_PDR0.bit.P04)#define PDR0_P05(IO_PDR0.bit.P05)#define PDR0_P06(IO_PDR0.bit.P06)#define PDR0_P07(IO_PDR0.bit.P07)In MB95200.asm, PDR0 address 0x0000 is allocated to PDR0 as below.__pdr0 .res.b 1 ;000000 /* Port0 */PDR0 .equ 0x00004.3.2 Startup.asm FileThe Startup.asm is the MB95200H/210H MCU initialization file including stack settings, registerbank settings and watchdog settings etc;18The Vectors.c contains the MB95200H/210H MCU Interrupt vector definition.User can pre-set all interrupt control registers in function InitIrqLevels(). It can be used to set all in-terrupt priorities in static applications. For example, to set the external interrupt ch.0 to level 0, change the following code:ILR0 = 0xFF; // IRQ0: external interrupt ch.0 | ch.4// IRQ1: external interrupt ch.1 | ch.5// IRQ2: external interrupt ch.2 | ch.6// IRQ3: external interrupt ch.3 | ch.7ToILR0 = 0xFC; // IRQ0: external interrupt ch.0 | ch.4// IRQ1: external interrupt ch.1 | ch.5// IRQ2: external interrupt ch.2 | ch.6// IRQ3: external interrupt ch.3 | ch.7And declare the interrupt function as in Vectors.c below,……__interrupt void external_int00 (void);……#pragma intvect external_int00 0 // IRQ0: external interrupt ch0 | ch4Then user can write his own interrupt sub-routine in Main.C shown as below./*--------------------- INTERRUPT SERVICE ROUTINE ---------------------------*/__interrupt void external_int00(void){//User code}4.3.4 Main.c FileMain.c contains the user code.195. Development Platform Quick Start5.1 Tools Setup SequenceStart the debugging system in the following sequence:•Connect a BGMA to the PC using a USB cable, confirm the LED on the BGMA is Green;•Connect an EV-board to BGMA IDC10 socket;•Select the EV-board power supply and turn on the EV-board, confirm the LED on the BGMAis Orange and the Power LED on the EV-board is on.5.2 Open Project and Start DebugUsers can start a debug from a PC software S OFTUNE workbench in the following sequence. Here takeIO_LED project for example.•Start the S OFTUNE from “Startup Menu>Programs> SOFTUNE V3> FFMC-8L Family SOF-TUNE Workbench” in Windows;•Click “Open workspace” from “File” Menu in S OFTUNE;•Select “IO_LED.wsp” in “Open Space” window;•Click “Start debug” from “Debug” Menu.If the entire procedure goes right, a debug will start normally.5.3Operation Precautions•All pins of MB95200H/210H MCU are connected to Testing Pin on the EV-board. If the userwants to test separate pin performance, do disconnect the header of related peripheral mod-ules.•Note that J2 shall be open while debugging using the BGMA. User reset from S3 (reset key)is invalid when J2 is open. To use reset key S3 in a normal mode, J2 should be closed.•It’s recommended that only one power supply is used as a power module input at a time.20SS01-26032-1E FUJITSU MICROELECTRONICS• SUPPORT SYSYEMF2MC-8FX Family8-bit MICROCONTROLLERMB95200H/210H SeriesSTARTER KIT MB2146-410A-01-ESETUP GUIDEOctober 2008 the first edition Published FUJITSU MICROELECTRONICS LIMITEDEdited Business & Media Promotion Dept.。

富士通MB95260H、270H、280H系列单片机数据手册

CMOS I/O: 3 个,N-ch 开漏 : 1 个 • I/O 口 ( 最多 : 13 个 ) (MB95F282K/F283K/F284K)

• 通用 I/O 口 ( 最多 ):

CMOS I/O: 11 个,N-ch 开漏 : 2 个 • I/O 口 ( 最多 : 12 个 ) (MB95F282H/F283H/F284H)

通用 I/O 口

I/O 口 ( 最多 ): 16 个 CMOS I/O: 15 个 N-ch 开漏 : 1 个

I/O 口 ( 最多 ): 17 个 CMOS I/O: 15 个 N-ch 开漏 : 2 个

时基定时器 中断周期 : 0.256 ms ~ 8.3 s ( 外部时钟 = 4 MHz 时 )

专用重载定时器支持选择广泛范围内的通信速度。 具有全双工双缓冲器。

• 可编程端口输入电压电平 • CMOS 输入电平 / 迟滞输入电平

• 双操作闪存 • 不同的寄存器组里可同时进行擦 / 写操作和读取操作 ( 高位组 / 低位组 )

• 闪存加密功能 • 保护闪存数据

2

DS07–12627–6Z

查询MB95260供应商

MB95260H/270H/280H 系列

■ 产品阵容

待机模式

休眠模式、停止模式、计时模式、时基定时器模式

封装

DIP-8P-M03 FPT-8P-M08

20 KB 496 B

DS07–12627–6Z

5

MB95260H/270H/280H 系列

查询MB95260供应商

• MB95280H 系列 产品型号

MB95F282H MB95F283H MB95F284H MB95F282K MB95F283K MB95F284K

富士通半导体(上海)有限公司 MCU-AN-500086-Z-13 电磁炉(半桥)演示板 用户手册

富士通半导体(上海)有限公司MCU-AN-500086-Z-13 用户手册F²MC-8FX家族8位微型控制器MB95430系列电磁炉(半桥)演示板用户手册修改记录修改记录版本日期作者修改记录 1.0.0 2010-03-12 Kevin.Lin 初稿 1.1.0 2010-08-5Kevin. Lin增加图片 1.1.1 2010-10-11 Kevin. Lin 修改图6-21.2.0 2010-11-17 Kevin. Lin 更新功率级,图6-2,增加错误代码 1.3.0 2011-12-01 Vic, Lan添加3.2.6和3.2.7节本手册包含25页。

版权©2010富士通半导体(上海)有限公司目录修改记录 (2)目录 (3)1 序言 (5)1.1 关于本手册 (5)1.2 参考资料 (5)2 演示板概要 (6)2.1 概要 (6)2.2 特性 (6)2.3 演示板模块 (6)3 演示板的系统水平结构 (8)3.1 演示板的结构图 (8)3.2 控制模块 (9)3.2.1 MCU 插槽 (9)3.2.2 按键和显示 (9)3.2.3 风扇和蜂鸣器 (10)3.2.4 温度测量电路 (10)3.2.5 调试器接口 (11)3.2.6 锅检测电路 (11)3.2.7 相位锁定以及频率跟踪控制电路 (11)3.3 电源 (12)3.3.1 SMPS (12)3.3.2 过滤器和整流器 (12)3.4 谐振电路 (12)3.4.1 IGBT 驱动器 (12)3.4.2 谐振电路 (13)4 如何操作演示板 (14)4.1 平台装配 (14)4.2 操作演示板 (15)4.2.1 接通/断开电源 (15)4.2.2 固定功率模式 (15)4.2.3 恒温模式 (16)4.2.4 计时模式 (16)5 调试和编程 (18)5.1 调试工具连接 (18)5.2 工程概要 (19)6 原理图 (20)7 更多信息 (22)8 附录 (23)8.1 图标索引 (23)8.2 MCU引脚分配 (24)8.3 错误代码 (25)第1章序言1 序言1.1 关于本手册本手册详细描述了半桥电磁炉板的硬件设计。

MB90880资料