可重构计算硬件平台的改进设计

大规模可重构处理器设计与优化

大规模可重构处理器设计与优化随着大数据、人工智能等领域的快速发展,对计算性能的需求也越来越高。

传统单核处理器已经不能满足这种需求,而多核处理器也已经到达了性能瓶颈。

因此,大规模可重构处理器被认为是未来的一个方向。

大规模可重构处理器的设计与优化是一个非常重要的课题。

这种处理器可以进行编程,通过不同的软件编写实现不同的算法,这种能力可以让它更好地适应各种应用场景。

同时,大规模可重构处理器在处理器数量、核心数量等方面可以大规模扩展,可以提供更强大的运算能力。

在设计大规模可重构处理器时,最重要的一点是在软硬件协同的基础上进行设计。

在大规模可重构处理器中,硬件实现的设计非常重要,但是软件编程也非常重要。

对于软件设计,需要将算法进行分解并进行优化,同时还需考虑容错性和可调度性等因素。

对于硬件实现的优化,需要更好地利用硬件资源,确保每个核心都能够得到足够的资源支持,同时还需要考虑性能、功耗和面积等因素。

作为一个较新的领域,大规模可重构处理器的优化还有很多问题需要解决。

其中一个重要的问题是如何设计更高效的调度算法。

在大规模可编程处理器中,有大量的硬件资源,如何更好地利用这些资源完成任务是调度算法需要解决的问题。

此外,还需要进一步探究大规模可重构处理器中的芯片间通信机制,探寻如何优化通信效率和降低延迟。

除此之外,由于大规模可重构处理器的架构不同于传统的单核处理器和多核处理器,需要进一步发展适应这种架构的编程技术。

对于过多的数据移动和数据依赖性,要针对性地开发高效的调度算法和优化算法,从而使得编程更加容易和高效。

最后,值得一提的是,大规模可重构处理器的优化不仅仅是技术问题,还涉及到一定的商业模式和市场规模。

除了为研究和生产这种处理器提供支持的国家和机构,大规模可重构处理器的市场需求也是一个非常关键的问题。

只有在市场中获得足够的支持和认可,才能够在未来市场上取得成功。

综上所述,大规模可重构处理器的设计与优化是一项非常重要的课题。

基于可重构计算机的高性能异构计算平台

基于可重构计算机的高性能异构计算平台第一章引言可重构计算机是一种灵活的计算平台,它能够在不同的应用场景下快速而高效地适应各种计算需求。

基于可重构计算机的高性能异构计算平台,将是未来大规模计算任务和工程问题的最佳解决方案。

本文将从可重构计算机的基础原理、实现方式以及在异构计算场景中的应用等方面进行深入探讨。

第二章可重构计算机基础原理可重构计算机是一种能够动态改变计算结构和功能的计算平台。

其基本原理是采用可编程逻辑单元(FPGA)作为计算内核,通过编程重构其内部电路结构以及功能单元,实现各种计算任务的加速处理。

可重构计算机不仅具有高度的灵活性和可定制性,而且在很多应用场景下,其性能特点也能够得到充分的发挥,从而得到最优的计算效率。

第三章可重构计算机实现方式可重构计算机的实现方式主要有两种:一种是采用商业化的可重构芯片,另一种是基于FPGA板卡和开源软件的方案。

其中,商业化的可重构芯片有Xilinx Virtex、Altera Stratix、LatticeXP等,这些芯片具备了较高的计算性能和可编程性,常用于计算加速、信号处理、数字信号处理、光网络等领域。

而基于FPGA板卡和开源软件的方案则依赖于开源软件的优秀生态系统和广泛的用户社区,由用户根据自身需要搭配相应的FPGA板卡选用,灵活性更高。

第四章可重构计算机的应用场景可重构计算机在异构计算场景中应用广泛。

一方面,在大规模数据中心中,可重构计算机能够通过Hadoop、Spark等分布式计算框架实现数据处理、分析和挖掘等任务的高效加速,充分发挥计算资源的利用率。

另一方面,在机器视觉、自然语言处理、深度学习等领域,可重构计算机能够通过优化算法、重构神经网络模型等方式实现算法加速,从而提高模型训练和预测的效率。

第五章可重构计算机的发展前景可重构计算机发展前景十分广阔。

首先,随着大数据时代的到来,对于计算效率和计算质量的提升需求日益增加,可重构计算机将成为满足这种需求的最佳解决方案。

可重构系统的设计与优化

可重构系统的设计与优化一、可重构系统的概念可重构系统是一种具有高度灵活性和扩展性的计算机系统,在工作时能够根据具体的需要进行重构和重新配置,以满足不同的应用需求。

可重构系统具有以下几方面的优点。

1. 灵活性高:可重构系统能够根据工作需要进行重构和重新配置,从而实现复杂的运算和处理,适应不同的应用环境。

2. 可扩展性强:可重构系统支持扩展和升级,能够通过增加硬件资源和软件配置,提高系统性能和处理速度。

3. 运算效率高:可重构系统采用专用的硬件和软件结构,支持高效的运算和处理,加速数据传输和处理速度。

二、可重构系统的组成可重构系统由三个主要部分组成,包括可编程逻辑芯片(PLD)、可重构硬件系统(RHS)和可编程软件系统(PSW)。

1. 可编程逻辑芯片:PLD是可重构系统的核心部件,它能够根据需要被编程为执行特定的功能,例如逻辑运算、状态机控制、数据通路等等。

2. 可重构硬件系统:RHS是可重构系统的硬件组成部分,它由一系列可编程的逻辑单元和内部总线组成,用于实现具体的计算和处理任务。

3. 可编程软件系统:PSW是可重构系统的软件组成部分,它提供了操作系统、编译器、调试器和其他软件工具,用于配置和管理可重构系统的硬件和软件资源。

三、可重构系统的设计与优化可重构系统的设计和优化需要考虑以下几个方面。

1. 系统架构设计:可重构系统的架构设计需要根据应用需求和目标性能来选择适当的硬件和软件组件,确定硬件架构和系统结构。

2. 编程语言和系统软件:可重构系统的编程语言和系统软件需要选取适合具体应用的编程语言和工具,如Verilog、VHDL、C/C++等,确保编程效率和代码质量。

3. 优化算法和数据结构:可重构系统的优化算法和数据结构需要根据问题性质和数据特征进行优化设计,提高系统运算效率和处理速度。

4. 系统调试和测试:可重构系统的调试和测试需要进行全面、有效的测试和调试工作,包括系统级测试、模块测试和集成测试等。

可重构计算平台的硬件结构设计

S c h o o l o f E l e c t r o n i c s a n d I n f o r m a t i o n , J i a n g s u U n i v e r s i t y o f S c i e n c e a n d T e c h n o l o g y , J i a n g s u Z h e n j i a n g 2 1 2 0 0 3 , C h i n a )

周期 , 然而 , P c也经常用来处理一些计算密集型高吞 吐量 P C机 设 计 的 , P C机 通 过 总 线 ( 如 P C I一3 3 , P C I—X,

的数据 , 特别是在科学研究 工作方 面 , 在 这种情 况下典 型 F i r e Wi r e 或者 U S B) 访问 F P G A, 要使得 处理数据 和 F P G A

【 K e y w o r d s 】r e c o ig f n u r a b l e c o m p u t i n g ; h a r d w r a e p l a t f o m; r s t r u c t u r l a d e s i n; g F P G A

运行在冯 ・ 诺依曼 或哈佛结构 …设 计 的计算 机处理

l i P A R T s & A P P 器 L I C 件 A 与 T I 应 O N 用 S

【 本文献信息】吴将, 朱志宇, 沈舒 . 可重构计算平 台的硬件结构设计[ J ] . 电视技术, 2 0 1 4 , 3 8 ( 7 )

可重构计算平台的硬件结构设计

吴 将, 朱志宇 , 沈 舒

软硬件协同设计平台构建与优化

软硬件协同设计平台构建与优化随着科技的快速发展和数字化信息技术的普及,软硬件协同设计逐渐成为一种趋势,成为提高企业产品设计效率和质量的重要手段。

软硬件协同设计平台作为软件和硬件设计协同工作的载体和工具,它的构建和优化可以直接影响其发挥的效能和价值。

本文将从软硬件协同设计的概念、平台构建和优化方面进行详细分析,以期为有需要的读者提供参考和启示。

一、软硬件协同设计的概念软硬件协同设计是指软件和硬件共同进行的产品设计,它不仅包括软件和硬件的集成设计,还包括软硬件交互的设计过程。

在软硬件协同设计中,软件和硬件应该具备强大的互操作性和交互性,以实现充分的协同。

软硬件协同设计的核心是数据共享与协同管理。

在软硬件协同设计中,软件、硬件和相关数据需要分别进行集成处理和管理,实现设计全流程的协同与管理,以提高产品的质量和效率。

二、软硬件协同设计平台构建软硬件协同设计平台是实现软硬件协同设计的重要基础,它贯穿全流程的设计与开发,包括设计协作、数据管理、可视化、仿真、测试、发布等环节,同时支持跨部门、跨地区、跨平台的协同设计和沟通。

平台构建包含以下关键要素:(一)软硬件协同设计工具选择和配置合适的软硬件协同设计工具是平台构建的首要任务。

选择的工具需要具备以下五个关键特性:一、具备全方位的软硬件协同设计功能;二、良好的易用性和可定制性;三、支持超大规模的数据协同和管理;四、具备高性能和可扩展性;五、具备完善的安全机制和保密措施,保障数据的安全性和私密性。

(二)协同设计流程管理平台需要定义和整理软硬件协同设计流程,并映射到相应的工具和功能上,使得设计人员能够清晰明确地掌握每一个设计环节的流程和工作要求,同时方便宏观管理和优化设计流程。

流程管理需要考虑到各种设计环节的依赖和交流,合理分配资源和任务,最大限度提高效率和效益。

(三)数据管理与可视化平台需要提供完整的数据管理体系和数据可视化支持,以实现全局协同、全程管理、全数据视角的管理与协同。

可重构计算硬件平台的改进设计

中圈 分类号t P9 3 T 3

可 重构 计 算硬 件 平 台的 改进设 计

王 晟中,陈伟男 ,彭澄廉

( 旦大学计算机 科学技术学院 ,上海 2 0 3) 复 04 3

捕

要 :针对现有可重构计算硬 件平台配置时间长、灵活性受限的缺陷,提 出一种改进设计。基于支持二维重构 区域的 Vr x4 ie一 现场可编 t

( c o l f o ue c n e F d nUnv ri , h n h i 0 4 3 S h o o mp t S i c , u a ie s y S a g a 2 0 3 ) C r e t

[ srclAi n th o aeo n o f uai meadf xblyc nt ie r xsigrcn g rbecmp t gh rw r l fr Ab t t mi a es R g fo gcn g rtnt n eiit o sandf i n o f ual o ui ad ae a om, a g t h l i o i l i r oe t e i n pt

tippr rp ss ni rvdd s n B sdo ie一 il rga hs ae o oe p a mpo e ei . ae nVr x4Fe Po rmma l Ga ryF G c i spot g2 c nt c dae,t k s g t d be t Ar (P A) hp u p rn Dr o s ut ra ima e e a i e r e

的灵 活 性 、 开 发周 期 短 和 易 维护 的特 性 。

Байду номын сангаас

本文介绍基于 X l x Vr x4 F G in ie P A的可重构计算硬件 i t

基于Xilinx SoPC的可重构嵌入式计算系统的研究与设计

( 中科 技 大学计 算机科 学 与技 术 学院 武汉 40 7) 华 304

摘 要 由于应用种类、 实时性 以及处理效率等要 求, 高性能嵌入 式计算硬件 平台需要具备相 当的计算能力 以及一定

的 适 应 性 。 为 此提 出了一 种 基 于 Xin P l xF GA 的 动 态可 重 构 的 片 上 系统设 计 方案 。 系统 采 用专 用硬 件 来 执 行 计 算 密 i 集 型任 务 , 用动 态可 重 构技 术 来 支持 硬 件 处理 模 块 功 能 的 动 态 配置 。研 究 了 X l x可 编 程 片 上 系统 上 的 3种硬 件 运 in i

Z HANG FE Yu NG n Da

( cห้องสมุดไป่ตู้o lo mpue ce c n c oo y, a h n ie st fSce c ndTe h oo y, u n 4 0 4 Chn ) S h o fCo t rS in ea d Tehn lg Hu z o g Unv riyo in ea c n lg W ha 3 07 , ia

c n i u e u i g r n t . eh r wa ep o e sn n i e c n b o p e O t e h s y tm s aCPU o r c s o , o f r d d rn u -i g me Th a d r r c s i g e g n a ec u ld t h o ts s e a c po es r a

T 3 P6 文献 标 识 码 A 中 图法 分 类 号

S u y a sg ofRe o iur b eEm b dd d m p i g S se s d o ln o t d nd De in c nfg a l e e Co utn y tm Ba e n Xii x S PC

小卫星星务计算机可重构硬件平台的研究

产生乱咬情况的发生.

3

星务计算机可重构硬件平台实现

可重构是指系统中的硬件功能或硬件功能模

3.1重构件的实现

块间的连接可以重新配置,基本的可重构件是一 种可重新配置的大规模集成电路,针对这一硬件 可以设计多个功能电路F,,F:,…F。,这些电路的 配置数据可以预先设计好并存储在系统存储器 中,称为重构件.重构件可以在系统运行之前或

子翻转sEu的瞬态故障最严重H J.sEu可使存

储器某一位的数据从一个稳态变化到另一个稳

CAN总

态,而存储器中数据的变化将导致指令或数据出 错,导致星务计算机内局部或部分功能的丧失.

即使DSP或ARM也无法从根本上解决程序“跑

飞”或sEu的瞬态故障处理,而且其硬件结构是

(a)星务中心计算机结构方框图

常工作时能根据需要对易损的器件进行多级备

份,避免了传统设计中硬件固定配置不能灵活调 整各备份单元级别的限制.

4)能够实时检测CAN总线以及485总线的

错误状态,避免了由于CAN总线或485总线“死 锁”而影响其他下位机或功能单元的正常工作. 5)能够监测狗咬逻辑,在逻辑产生故障时, 及时修正逻辑,避免了由于狗咬逻辑产生错误而

on

satisfy

the need for

dynaIIlic

reuse

or

static re—constlllction change the configum-

of the hardware

satellite house—keeping computer by utilizing function module

CPLD/FPGA几乎可以实现任何形式的数字电路 或数字系统的设计口j.随着CPLD/FPGA容量的 不断增大,一片cPLD/FPGA已经可以替代几十 甚至上百块通用IC芯片,用它们设计出的具有特

FPGA设计优化及方案改进

FPGA设计优化及方案改进引言FPGA(Field-Programmable Gate Array)是一种灵活的集成电路,可以在设计完成后进行编程,其可重构能力使其在嵌入式系统领域得到广泛应用。

然而,在进行FPGA设计时,设计师常常会面临面临多方面的挑战,包括资源利用率、时序和功耗等方面需要优化的问题。

本文将介绍FPGA设计优化的方法,并提出一些方案改进的建议。

FPGA设计优化方法1.资源利用率优化在FPGA设计中,资源利用率是一个非常关键的指标。

设计师应该尽可能地利用FPGA的资源,以提高系统的性能和效率。

•减小资源占用:在设计中,可以通过选择适当的元件和数据路径,减小设计对资源的需求。

比如,可以使用小型的逻辑元件替代大型的逻辑块,或者通过选择合适的数据存储结构来减小内存的占用。

•优化布局:在布局设计中,可以通过合理的划分和布局电路模块,减少数据路径的长度和数据冒泡现象的发生,从而提高系统的性能和资源利用率。

•逻辑复用:逻辑复用是一个有效的资源利用策略。

设计师可以合理地设计逻辑电路,使得多个逻辑功能共享同一片FPGA资源,从而提高资源利用率。

2.时序优化时序是FPGA设计中一个重要的指标,它决定了系统是否能够按照预期的时序要求正常运行。

在进行FPGA时序优化时,可以采取以下方法:•时钟树优化:时钟树是FPGA设计中的一个重要部分,它决定了时钟信号的传输速度和质量。

设计师可以通过优化时钟树的布局和路由,减小时钟信号的延迟和抖动,从而提高系统的时序性能。

•时钟分频和锁相环(PLL):在FPGA设计中,时钟分频和锁相环是常用的时序优化方法。

通过合适的时钟分频和PLL设置,可以降低时序要求,提高系统的时序容忍度。

•引入流水线:通过引入流水线,可以将一个复杂的逻辑操作划分为多个较简单的阶段,从而减小每个阶段的时延,提高系统的时序性能。

3.功耗优化功耗是FPGA设计中需要考虑的一个重要指标,尤其对于嵌入式系统来说。

基于可重构硬件的系统设计及实现

基于可重构硬件的系统设计及实现一、可重构硬件介绍可重构硬件(Reconfigurable Hardware)指的是一类硬件设计中,可以通过编程修改其硬件电路的可编程芯片。

与传统的固定功能芯片相比,可重构硬件的电路可以被重新配置为执行不同的功能。

可重构硬件比传统的基于固定逻辑的芯片更为灵活,在计算机科学和电子工程领域中,广泛用于数字信号处理、高性能计算和嵌入式系统等领域。

二、可重构硬件系统设计及实现1. 系统设计可重构硬件系统设计中,主要包括硬件架构设计和软件部分,硬件架构设计包括芯片选型、电路设计、系统总线设计等部分,软件部分则包括编程工具、编程语言和SDK等软件开发工具。

2. 系统实现系统实现过程中,可以利用现有的可重构芯片(如FPGA、CPLD等)进行设计和实现。

在硬件设计方面,需要考虑系统的架构、电路连接等方面;在软件方面,可以利用编程工具来开发并测试系统的性能。

三、可重构硬件的应用1. 数字信号处理可重构硬件在数字信号处理领域应用广泛。

通过可重构硬件的编程,可以快速而高效地实现数字信号处理的算法,比如数字滤波、傅里叶变换和压缩编码等。

2. 高性能计算可重构硬件在高性能计算领域的应用也非常广泛,可重构硬件的处理速度比传统的固定功能芯片更快,在科学计算、金融分析以及三维视觉处理等领域起到了重要的作用。

3. 嵌入式系统随着物联网的发展,嵌入式系统在我们日常生活中越来越常见。

作为一种高灵活性的技术,可重构硬件也在嵌入式系统中得到了广泛的应用,可以用于处理机器视觉、智能控制、通信处理等。

四、可重构硬件的未来发展趋势1. 高性能和低功耗可重构硬件在未来的发展方向中,将更加注重高性能和低功耗的设计,例如在数字信号处理方面,可以通过优化算法并且使用更加低功耗的芯片来实现。

2. 虚拟化技术在可重构硬件的未来发展中,虚拟化技术极有可能成为下一个技术趋势,基于虚拟化技术可以将多个可重构硬件器件进行集成,通过虚拟化技术来实现更加高效的算法优化。

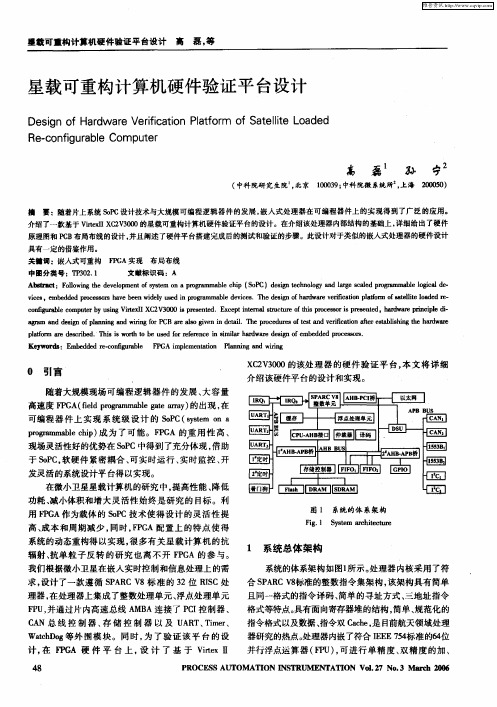

星载可重构计算机硬件验证平台设计

l H l嚣码 画A 口裁回 l c B圈 l P 接l l u 仲 译 -

F a h I DRA I s I M ¨S 1 M D}

图 1 系统 的体 系架构

维普资讯

墨载可重构计算机硬件验证平 台设计

高

磊。 等

星载可重构计算机硬件验 证平 台设 计

De in o a d r e ic t n Paf r o a ele L a e sg fH rwa e V r i i lt m fS t l o d d fao o i t R — o f u a l C mp t r e c n i r be o g ue

玉

竺一

e niu a l o u rb sn r x l C V 0 0 i p e e td x e t n r a t cu f h spo e sri p s n e lⅡ w r r cped — o t r be c mp t y u i Vie l X 2 3 0 s r s ne .E c p t n s u tr o i rc so re tdI l d ae pi il i g e g t ie l r e t s e J n a rm n e i f ln ig a d w r gfrP r logv n i e i h r c u s f e t n e f a o f r s bihn e h r 帆 弛 ga a d d s o pa n n n i o CB ae as ie d t l n g i n n a .T e p e r ts a d v r c t n a e t l i t a d o d e o i i i t ea s g h p a om T e cie .T i i w r ob sd frrfr n e i i l ad T e i fe b d e r c sos lt r 8B d s r d h s s ot t e u e c s a h rw8e d s o m e d d p o e s r . f b h e o e e n mi r n g Ke wo d :E e d d r- o f u a l F GA i lme tt n P a n n d w r y rs mb d e ec n g r b e i P mpe n i ln ig a i n a o n i g

可重构计算

可重构计算

可重构计算基于现场可编程门阵列——— FPGA.FPGA的编程技术主要有两种:一种是反 熔丝技术,即通常所说的电可擦写技术,但是这种技 术的可重构实时性太差;另一种是基于静态存储器 ( SRAM)可编程原理的FPGA编程技术,这种硬件 包含计算单元阵列,这些计算单元的功能由可编程 的配置位来决定.当前大多数的可重构设备是基 于静态存储器的,其实现计算单元的粒度随不同的 系统要求而不同.

可重构计算

传统的计算方式有两种: 一种是采用对通用微处理器进行软件编程 的方式,软件的方式通用性好, 但运算速度不 高 一种是采用A S IC 的方式. A S IC 方式处理 速度快, 但只能针对特定的算法, 通用性不 好

可重构计算

可重构计算(Reconfigurable Computing) 是在 软件的控制下, 利用系统中的可重用资源, 根据应 用的需要重新构造一个新的计算平台, 达到接近专 用硬件设计的高性能.具有可重构计算特征的系统 称为可重构系统. 简单地说,就是利用FPGA 逻辑实现计算任 务.有的称作自适应计算(adaptive computing) , 也有的称之为FPGA 计算.

3.独立处理单元模式 独立处理单元模式 属于这类系统的可重构逻辑部分一般包含多个 FPGA .这是一种最松散的耦合形式. 4.SoPC模式 模式 处理器,存储器和可编程逻辑集成在同一个 FPGA 芯片上, 称为单芯片可重构计算系统 (SoPC) .这种系统中CPU 和FPGA仍然是紧密 耦合的结构, 同时片上存储系统和CPU 与FPGA 接口能力则进一步提高了系统的性能.以往的 SoC (System on chip) 设计依赖于固定的ASIC , 而SoPC是以可编程逻辑器件取代ASIC , 越来越 多地成为系统级芯片设计的首选.

通用计算平台的设计与实现

通用计算平台的设计与实现随着信息技术和计算机技术的不断发展,计算平台已经成为许多领域的关键基础设施。

通用计算平台是一种可以在多种应用场景中使用的计算系统,它具有高度的灵活性、可扩展性和通用性。

本文将从设计和实现两个方面来探讨通用计算平台的相关问题。

设计通用计算平台的设计需要考虑以下问题:1.多任务处理:通用计算平台需要支持同时运行多个任务,因此必须具有多任务处理能力。

这就要求平台具有多核处理器、分布式计算和高效的调度算法等特性。

2.虚拟化:通用计算平台通常需要支持虚拟化技术,以便为多个用户提供共享计算资源。

这就要求平台具有硬件虚拟化和软件虚拟化的支持,同时需要采用适当的安全措施来保护用户数据和隐私。

3.可编程:通用计算平台应该具有高度的可编程性,以便满足不同应用场景中的需求。

这就要求平台支持编程语言和开发工具的多样性,同时需要提供丰富的开发框架和库。

4.可扩展:通用计算平台应该是可扩展的,以便随着需求的增长和变化而扩展。

这就要求平台在硬件和软件方面都具有良好的可扩展性,并且能够支持多种扩展方式,如FPGA、GPU和ASIC等。

5.高效性:通用计算平台应该具有高度的性能和效率,以便在对计算资源的要求越来越高的情况下,保证系统的运行和响应速度。

这就要求平台具有高速存储器、高带宽网络和优秀的优化算法等特性。

实现通用计算平台的实现需要考虑以下问题:1.架构:通用计算平台的架构应该采取分布式、模块化和可重构的设计方式,以便支持多种不同的应用场景和需求。

该架构应该具有良好的可维护性和可升级性,同时要考虑到安全性和稳定性的问题。

2.硬件:通用计算平台的硬件实现需要考虑到多任务处理和虚拟化的需求,同时要考虑到可编程和可扩展的特性。

该硬件应该采用先进的处理器和芯片组技术,并且支持多种扩展方式,如FPGA、GPU和ASIC等。

3.软件:通用计算平台的软件实现需要提供丰富的开发框架和库,同时要考虑到多语言和多平台的支持。

可重构硬件设计中的性能优化策略

可重构硬件设计中的性能优化策略一、可重构硬件设计概述可重构硬件设计指的是一种基于可编程逻辑的硬件设计方法。

与传统的固定电路相比,可重构硬件设计可以根据用户需要,通过动态、在线重构来灵活适应不同的任务,从而提升硬件资源的利用率和系统的性能。

它对于设计复杂的硬件系统具有重要的意义,可以有效地解决传统硬件设计中所遇到的规模化、复杂性、灵活性等问题。

二、可重构硬件设计性能优化的挑战在实际应用中,如何提高可重构硬件设计的性能是一个十分关键的挑战。

首先,可重构硬件设计主要依赖于可编程逻辑资源的利用,因此如何优化资源利用效率是一个需要考虑的问题;其次,可重构硬件设计需要在实时环境中运行,因此如何提高系统的响应时间是必须重视的;第三,可重构硬件设计需要与其他系统进行交互,因此如何保证系统的兼容性和稳定性也是需要考虑的。

三、可重构硬件性能的优化策略为了解决可重构硬件设计中的性能问题,可以采用以下几种优化策略:1.硬件资源利用优化在可重构硬件设计中,通过对FPGA、ASIC等可编程逻辑资源的明确管理和精确控制,可以充分利用这些资源去进行所需的运算和处理。

在具体实施的时候,可以采用布局重整、设计切割、资源共享等多种手段去优化硬件资源的利用效率。

2.运算优化在可重构硬件设计过程中,数据的计算处理是一个重要的环节。

因此,可以采用优化算法等手段,对数据的运算过程进行优化和加速。

同时,也可以采用流水线、多级缓存等技术,对数据的读取和存储进行优化,以提高运算效率和速度。

3.通信优化在可重构硬件设计中,系统之间的通信扮演着非常重要的角色。

因此,可以采用各种通信协议和互联标准,以加快通信速度和提高通信效率。

同时,也可以采用多级缓存、数据压缩等技术,对通信数据进行优化和压缩,以降低数据传输所需的带宽和开销。

4.功耗优化随着云计算、物联网、人工智能等应用场景的广泛普及,能耗优化成为设计优化的一个关键问题。

在可重构硬件设计中,功耗优化同样需要重视。

可重构计算架构设计与应用现状分析

可重构计算架构设计与应用现状分析一、概述可重构计算架构(Reconfigurable Computing Architecture,RCA)是一种可以根据任务需求动态调整电路架构和逻辑功能的计算架构。

随着计算机技术的迅猛发展,传统的固定计算框架不能适应新型应用的需求,可重构计算架构应运而生。

本文旨在介绍可重构计算架构的设计原理、应用现状分析以及未来发展前景。

二、可重构计算架构的设计原理可重构计算架构是利用FPGA(Field Programmable Gate Array)这种可编程逻辑器件实现电路可重构的计算架构。

其核心技术是“可重构逻辑电路”,即通过修改逻辑电路中的布局和连线来改变电路的运算功能。

1. 可重构逻辑电路的基本结构可重构逻辑电路由基本元件和互连网络两部分构成。

基本元件是可编程的逻辑单元,而互连网络则是将这些逻辑单元进行有机组合的级联网络。

从而在逻辑单元的级联组合中实现目标电路。

2. 可重构计算架构的实现方法可以通过一种“可编程”的方式来实现电路的可重构。

也可以通过“可配置”的方式实现。

可编程是基于FPGA技术的可重构计算架构,基于FPGA可以设计各种逻辑单元实现任何目标电路。

可配置则是通过运算器、多媒体加速器和网络交换机等集成电路实现电路的重构,通过重新连接电路的功能块和更改其配置参数等方式,以实现不同功能的电路。

三、可重构计算架构的应用现状分析1. 可重构计算架构的计算机视觉应用利用可重构计算架构可以实现实时的数字图像处理和计算机视觉。

例如,实现对高清晰度视频流的实时处理、对高分辨率的图像进行实时处理等。

2. 可重构计算架构的嵌入式应用利用可重构计算架构可以实现嵌入式应用,例如,在工业自动化领域中,可以利用可重构计算架构来控制各种传感器以及执行机器人的任务。

3. 可重构计算架构在科学计算领域的应用可重构计算架构在大数据、生物医药和人工智能等领域也有着广泛的应用。

例如,在大数据计算中实现了数据的可视化、处理和分析,能够通过可重构计算架构实现这种大数据的实时处理和计算。

可重构计算

当前可重构计算或系统需要解决的问题

(1) 粒度问题.细粒度的可重构电路面积的使用 效率很低. (2) 如何改进结构来减少重构时间.在数据重载 时,FPGA端口对外呈高阻状态,重载后,才恢复对 外的逻辑功能.这就是所谓的重构时隙,将影响 系统功能的连续.如何克服或减少重构时隙,是 实现动态重构系统的瓶颈问题. (3) 数据传输和存储问题.现在的可重构芯片提 供的片上存储器太少,因而,许多重构计算的应用 需要更大的外部存储器.当前设计中,最迫切需 要优化解决的问题是Memory带宽和能耗.

可重构计算

可重构计算基于现场可编程门阵列——— FPGA.FPGA的编程技术主要有两种:一种是反 熔丝技术,即通常所说的电可擦写技术,但是这种技 术的可重构实时性太差;另一种是基于静态存储器 ( SRAM)可编程原理的FPGA编程技术,这种硬件 包含计算单元阵列,这些计算单元的功能由可编程 的配置位来决定.当前大多数的可重构设备是基 于静态存储器的,其实现计算单元的粒度随不同的 系统要求而不同.

可重构计算的分类

可重构计算又可按重构发生的时间分为静态重构 和动态重构. 静态重构是指在可重构件运行之前对其进行预先 配置, 在运行过程中其功能保持不变, 即运行过程 中不能对其进行重构. 动态重构是指在可可重构件运行的过程中可根据 需要对其实时进行配置, 改变其电路结构, 实现不 同的功能.

可重构计算系统的分类

Garp 是加州大学伯克利分校提出的一种可重构体系结构, 其 结构如图2 所示. 该结构中, 可重构阵列与一个通用的MIPS 处理器构成了一个混合式计算系统, 可重构阵列与通用处理 器共享内存和数据缓冲, 二者之间形成一种主协处理器的关 系. 该结构的优点是兼具了通用处理器的灵活性和可重构部 件的高速性. 通用处理器完成通用程序的处理, 对于特定的 循环和子程序, 则由可重构阵列在通用处理器的控制下实现 加速处理. Garp 结构一般集成在一个芯片上, 形成一个片上 系统.

可重构计算混合系统硬件的设计与实现

中圈分类号: P9 T31

可 重构 计 算 混 合 系统硬 件 的设 计 与 实现

李美锋 ,邓庆绪 ,金 曦,刘柄蔚 ,孔繁鑫

( 北大 学信息科学与工程学 院,沈 阳 10 0 ) 东 10 4 摘 要 :可重构计算系统 中软硬件资源的管理缺乏统一的机制 ,资源 不能被 有效利 用。为此 ,设计并实现一种硬件任务模型 ,为上层软件

Байду номын сангаас

驱动、系统 内核、 软件库、软件任务等

F G A P

科学基金资助项 目 “ 多核系统 中实 时调度策略的设计与分析技术 的 研究” 6 9 3 1) 中央高校 基本科 研业务 费专项基金 资助项 目 “ (0 7 0 7 ; 支 持 MP o 体系结构设计空 间探索及软件开发的高性能虚拟系统设 SC 计平 台” ( 1 0 0 0 1;中央高校基 本科研业务费专项 基金资助项 N 0 64 1) E 基于片上 网络的存储器访问性能研究”( 0 2 4 0 ) l“ N10 0 0 1

BO P R H系统较好地支持软硬件统一这一概念 , 但是并没有关

于具体的硬件平台设计实现和运行机制的叙述。文献【] 5提出

图 3 硬件任务实体模 型

每 个硬件任务实体的软硬件信息交互模块和软硬件 间数

据搬运模块 功能基本相 同,而硬件 任务功能模块需要根据硬 件任务 的不 同分别实现。各模块的具体功能如下 :

了一种支持软硬件整合的嵌入式系统平 台,并对硬件结构进 行 了说 明。该平台能够有效地解决软硬件 问的通信问题 ,但 并没有针对软硬件无法统一管 理这一 问题提 出相应的解决方 案 。文献[】 出了一种硬件模板 ,用户在系统设计 时将具体 6提

的硬件功能整合到模板中即可 ,无需考 虑硬件功能与系统其 他部分 的接 口设计 。该模 板使 硬件 功能具有统一 的接 口,但

面向未来的可重构计算机系统设计

面向未来的可重构计算机系统设计一、引言随着科技进步的不断推进,计算机的应用已经深入到各个领域,逐渐改变了人们的生产、生活方式。

然而,传统的计算机架构设计已经不能满足未来的高性能、高效能需求,同时也存在着消耗能耗高、运算速度慢的问题。

因此,可重构计算机系统成为未来计算技术发展中的重要方向。

二、可重构计算机系统的概述可重构计算机系统是指能够依据应用需求动态调整硬件结构和软件的一类计算机系统。

其最大特点是可实现在运行时的动态重新配置,从而提高运算性能并减轻能耗压力。

与传统计算机不同的是,可重构计算机能够对硬件进行重新编程,实现“按需定制”功能。

此外,可重构计算机系统也可以实现不同应用软件的复用,进一步加快应用开发和执行的速度。

因此,可重构计算机系统成为了未来计算机技术发展的重要方向之一。

三、可重构计算机系统的设计与实现1. 可重构硬件设计可重构硬件设计是可重构计算机系统中最关键的一步,能够决定系统的性能和适应性。

与传统计算机架构不同,在可重构计算机中,用户可以动态调整硬件结构,因此需要尽可能使硬件可编程,支持程序运行时的动态配置。

常见的可重构硬件设计方法包括:FPGA(Field Programmable Gate Array)和ASIC(Application Specific Integrated Circuit)。

FPGA 是使用可编程逻辑器件构建硬件的一种方法,具有可重构性强、灵活性高等特点;而 ASIC 是将应用特定的硬件电路整合到同一个芯片的一种方法,具有性能高、功耗低等优点。

两者各有优缺点,设计者需要根据应用需求选择适合的可重构硬件实现方案。

2. 可重构软件设计在可重构计算机系统中,软件也需要实现可重构性。

与传统计算机编程方式不同,可重构计算机的软件需要支持程序运行时的动态重构。

可重构软件设计需要考虑到多种因素,包括:软件可重构性,运行时性能,系统安全性等。

一种常见的可重构软件设计方法是采用基于 Java 的软件架构,平台使用 Virtex-II Pro FPGA,具有高度可重构性、通用性和可扩展性。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

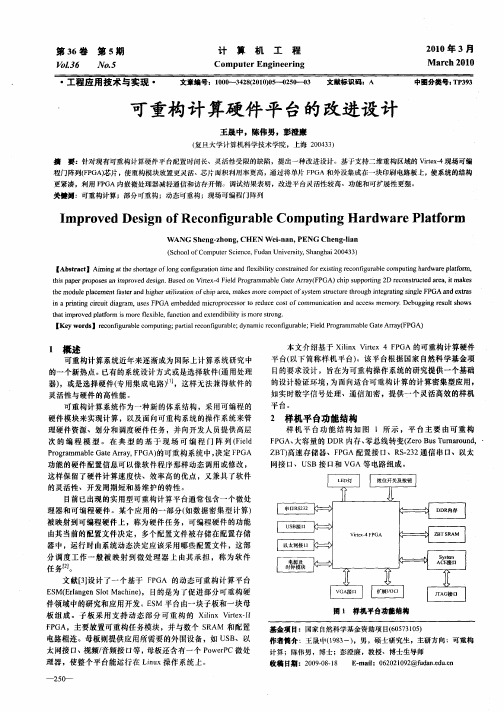

—250—可重构计算硬件平台的改进设计王晟中,陈伟男,彭澄廉(复旦大学计算机科学技术学院,上海 200433)摘 要:针对现有可重构计算硬件平台配置时间长、灵活性受限的缺陷,提出一种改进设计。

基于支持二维重构区域的Virtex-4现场可编程门阵列(FPGA)芯片,使重构模块放置更灵活、芯片面积利用率更高,通过将单片FPGA 和外设集成在一块印刷电路板上,使系统的结构更紧凑,利用FPGA 内嵌微处理器减轻通信和访存开销。

调试结果表明,改进平台灵活性较高、功能和可扩展性更强。

关键词:可重构计算;部分可重构;动态可重构;现场可编程门阵列Improved Design of Reconfigurable Computing Hardware PlatformWANG Sheng-zhong, CHEN Wei-nan, PENG Cheng-lian(School of Computer Science, Fudan University, Shanghai 200433)【Abstract 】Aiming at the shortage of long configuration time and flexibility constrained for existing reconfigurable computing hardware platform,this paper proposes an improved design. Based on Virtex-4 Field Programmable Gate Array(FPGA) chip supporting 2D reconstructed area, it makes the module placement faster and higher utilization of chip area, makes more compact of system structure through integrating single FPGA and extras in a printing circuit diagram, uses FPGA embedded microprocessor to reduce cost of communication and access memory. Debugging result shows that improved platform is more flexible, function and extendibility is more strong.【Key words 】reconfigurable computing; partial reconfigurable; dynamic reconfigurable; Field Programmable Gate Array(FPGA)计 算 机 工 程Computer Engineering 第36卷 第5期Vol.36 No.5 2010年3月March 2010·工程应用技术与实现·文章编号:1000—3428(2010)05—0250—03文献标识码:A中图分类号:TP3931 概述可重构计算系统近年来逐渐成为国际上计算系统研究中的一个新热点。

已有的系统设计方式或是选择软件(通用处理器),或是选择硬件(专用集成电路)[1],这样无法兼得软件的灵活性与硬件的高性能。

可重构计算系统作为一种新的体系结构,采用可编程的硬件模块来实现计算,以及面向可重构系统的操作系统来管理硬件资源、划分和调度硬件任务,并向开发人员提供高层次的编程模型。

在典型的基于现场可编程门阵列(FieldProgrammable Gate Array, FPGA)的可重构系统中,决定FPGA 功能的硬件配置信息可以像软件程序那样动态调用或修改,这样保留了硬件计算速度快、效率高的优点,又兼具了软件的灵活性、开发周期短和易维护的特性。

目前已出现的实用型可重构计算平台通常包含一个微处理器和可编程硬件。

某个应用的一部分(如数据密集型计算)被映射到可编程硬件上,称为硬件任务,可编程硬件的功能由其当前的配置文件决定,多个配置文件被存储在配置存储器中,运行时由系统动态决定应该采用哪些配置文件,这部分调度工作一般被映射到微处理器上由其承担,称为软件 任务[2]。

文献[3]设计了一个基于FPGA 的动态可重构计算平台ESM(Erlangen Slot Machine),目的是为了促进部分可重构硬件领域中的研究和应用开发。

ESM 平台由一块子板和一块母板组成。

子板采用支持动态部分可重构的Xilinx Virtex-II FPGA ,主要放置可重构任务模块,并与数个SRAM 和配置电路相连。

母板则提供应用所需要的外围设备,如USB 、以太网接口、视频/音频接口等,母板还含有一个PowerPC 微处理器,使整个平台能运行在Linux 操作系统上。

本文介绍基于Xilinx Virtex 4 FPGA 的可重构计算硬件平台(以下简称样机平台)。

该平台根据国家自然科学基金项目的要求设计,旨在为可重构操作系统的研究提供一个基础的设计验证环境,为面向适合可重构计算的计算密集型应用,如实时数字信号处理、通信加密,提供一个灵活高效的样机平台。

2 样机平台功能结构样机平台功能结构如图1所示,平台主要由可重构FPGA 、大容量的DDR 内存、零总线转变(Zero Bus Turnaround, ZBT)高速存储器、FPGA 配置接口、RS-232通信串口、以太网接口、USB 接口和VGA 等电路组成。

图1 样机平台功能结构基金项目:国家自然科学基金资助项目(60573105)作者简介:王晟中(1983-),男,硕士研究生,主研方向:可重构 计算;陈伟男,博士;彭澄廉,教授、博士生导师收稿日期:2009-08-18 E-mail :062021092@2.1 FPGA根据应用需求,平台采用Virtex-4 FX系列FPGA,器件中内嵌了PowerPC处理器,且FPGA本身在Virtex-II系列的基础上新增了对二维动态重构区域的支持,使得重构模块的放置更为灵活。

器件的主要资源包括56 880个逻辑单元、4.176 MB 的内部RAM块、2个PowerPC处理器核、4个以太网控制器核以及576个I/O端口。

2.2 外部存储器为了支持Linux操作系统,平台配备了128 MB的DDR SDRAM系统内存,还单独配置了一个更高速的9 MB的ZBT SRAM,用于存放硬件任务模块以及硬件任务间的数据交换,以提高系统的性能。

2.3 外设及接口FPGA周边设置了很多外设,用于提高平台的应用性,如,串口可连接平台和PC机,方便调试以及应用程序下载;System ACE芯片和JTAG接口用来对FPGA动态配置;以太网控制器增加了对网络的支持等;扩展I/O接口提供了240个I/O引脚,可另外连接其他外围电路,如A/D, D/A, LCD等,提高了平台的可扩展性。

3 样机平台体系结构由于Virtex-II器件的资源局限性,文献[2]的ESM采用2块FPGA来实现,且Virtex-II系列FPGA仅支持一维的动态可重构区域,即可重构模块必须占据器件的整列,使得模块放置有很大局限性,硬件资源利用率不高。

而本文的样机平台只需一块Virtex-4 FPGA就能实现与ESM类似的功能。

不仅结构更紧凑,同时还支持二维的动态可重构区域,可重构模块不再占据整列,而是任意长宽的矩形,使得放置更灵活,芯片面积利用率也得到提高。

3.1 片内总线互连整个样机平台的系统应用涉及到PowerPC处理器、外设IP核以及用户逻辑IP核之间的集成和协作,因此,平台采用由IBM 公司开发的芯片内部总线通信结构CoreConnect作为主要的片内总线互连技术。

CoreConnect总线结构包括高速的处理器局部总线(Processor Local Bus, PLB),相对低速但通用性强、协议简洁的片上外设总线(On-chip Peripheral Bus, OPB)可以连接不同总线的桥(OPB-PLB Bridge)与相应的仲裁器,因此,可以满足处理器、外设和用户逻辑之间的连接和通信。

3.2 平台体系结构样机平台的体系结构如图2所示。

图2 样机平台体系结构PowerPC处理器和DDR系统内存连接在PLB总线上,System ACE及其他外设连接在OPB总线上。

将用户逻辑看成平台的外设,所有硬件任务经过硬件任务接口封装后,通过OPB IP接口(IP Interface, IPIF)挂载于OPB总线上。

由于每个硬件任务要分别完成不同的功能,其接口信号势必会有区别,因此需要对硬件任务的接口进行抽象和统一定义,使硬件任务可以按照一种较为通用的方式进行数据交换和通信。

3.3 硬件任务统一接口与文献[3]的ESM可重构计算平台类似,所有硬件任务通过一个接口控制器与I/O引脚连接。

接口控制器本身与多个I/O引脚相连,在硬件任务配置时,由CPU在接口控制器内为硬件任务分配相应的引脚。

采用该方法的优点是硬件任务的配置文件与具体的I/O引脚位置无关,这样硬件任务在FPGA中放置就不受引脚的约束,更为灵活。

3.4 平台配置方式平台采用Xilinx公司的System ACE芯片来管理FPGA的初始配置,配置文件存储在CF卡上,FPGA上电后,SystemACE芯片读取CF卡中的配置文件,并通过JTAG模式对FPGA进行配置。

在系统运行过程中,由PowerPC处理器发起动态部分重构过程,读取CF卡上存储的动态可重构模块的配置文件,通过控制FPGA内部配置访问接口来快速配置可重构模块,以实现动态可重构的功能。

4 样机平台的开发调试由于平台采用Xilinx公司的FPGA产品,因此开发及调试基本建立在Xilinx的设计环境下,采用的工具包括Xilinx集成软件环境ISE、嵌入式开发套件EDK以及集成化逻辑分析仪ChipScope,版本均为9.2i。

4.1 平台创建鉴于EDK环境对软硬件协同设计以及IP核设计的良好支持性,开发及调试工程均选择建立在EDK环境下。

第1步即创建EDK支持的平台。

在新建工程时,EDK支持用户自定义硬件平台。

用户可自行指定FPGA的具体型号,平台的体系结构以及所需要的外设。

此时工程即创建完成,各个外设的控制器以IP核的形式挂载于指定的总线上。

最后在system.用户约束文件(User Constraint File, UCF)中为FPGA分配外设连接的管脚位置及属性约束。

一个典型的管脚约束如下:Net fpga_0_SRAM_Mem_A_pin<2> LOC=V4;Net fpga_0_SRAM_Mem_A_pin<2> IOSTANDARD=LVDCI_ 33;Net fpga_0_SRAM_Mem_A_pin<2> SLEW=FAST;Net fpga_0_SRAM_Mem_A_pin<2> DRIVE=8;该约束的每一语句分别定义了平台中SRAM的第3位地址线的管脚位置(LOC)、输入输出标准(IOSTANDARD)、电压转换速率(SLEW)以及驱动能力(DRIVE)。