4选1多路选择器VHDL语言设计

多路选择器与编码器的VHDL设计

实验三多路选择器与编码器的VHDL设计一. 实验目的1.掌握硬件描述语言描述多路选择器的方法。

2. 掌握硬件描述语言描述编码器的方法3.学会使用VHDL进行简单的逻辑电路设计。

4. 掌握用Quartus II进行文本输入法进行电路设计、编译和仿真方法。

二、实验仪器设备1.PC机一台2.QuartusⅡ开发软件一套3.EDA技术实验开发系统一套三. 实验任务1. 设计一个4选1多路选择器用VHDL设计的4选1多路选择器中,当控制端S=0时多路选择器有效,S=1时禁止工作,输出封锁为低电平。

d0,d1,d2,d3分别为四个数据输入端的端口名,a0,a1为通道选择控制信号输入端的端口名,y为输出端的端口名。

(1)4选1多路选择器的VHDL程序entity mux4_1 isport(d0,d1,d2,d3: in bit;a0,a1,s: in bit;y: out bit);end;architecture one of mux4_1 issignal a: bit_vector(1 downto 0);Beginprocess(a0,a1)begina<=a1&a0;if (s='0') thencase a iswhen "00"=> y <=d0;when "01"=> y <=d1;when "10"=> y <=d2;when "11"=> y <=d3;end case;else y<='0';end if;end process;end;(2)根据编写的VHDL程序并在Quartus II软件中进行输入、编译和仿真。

其功能仿真波形如下图所示,通过波形分析符合4选1多路选择器的要求。

图1VHDL程序录入图2程序仿真波形图。

四选一多路选择器

四选一选择器的VHDL程序实现及仿真一、四选一选择器的基本功能描述选择器常用于信号的切换,四选一选择器常用于信号的切换,四选一选择器可以用于4路信号的切换。

四选一选择器有四个输入端input(0)~ input(3),两个信号选择端a和b及一个信号输出端y。

当a、b输入不同的选择信号时,就可以使input(0)~ input(3)中某一个相应的输入信号与输出y端接通。

例如,当a=b=“0”时,input (0)就与y接通。

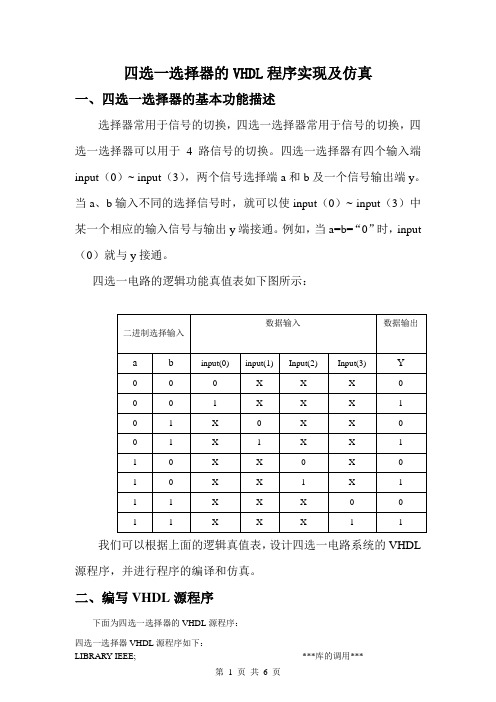

四选一电路的逻辑功能真值表如下图所示:我们可以根据上面的逻辑真值表,设计四选一电路系统的VHDL 源程序,并进行程序的编译和仿真。

二、编写VHDL源程序下面为四选一选择器的VHDL源程序:四选一选择器VHDL源程序如下:LIBRARY IEEE; ***库的调用***USE IEEE.STD_LOGIC_1164.ALL; ***库的调用***ENTITY mux4 IS ***实体定义*** PORT (input:IN STD_LOGIC_VECTOR(3 DOWNTO 0); ***输入管脚的定义***a,b:IN STD_LOGIC; ***输入管脚的定义***y:OUT STD_LOGIC ); ***输出管脚的定义***END mux4;ARCHITECTURE rtl OF mux4 IS ***结构的定义***SIGNAL sel:STD_LOGIC_VECTOR (1 DOWNTO 0); ***信号定义***BEGINsel<=b&a;PROCESS (input,sel) ***进程的定义***BEGINIF(sel="00") THENy<=input(0);ELSIF(sel<="01") THENy<=input(1);ELSIF(sel<="10") THENy<=input(2);ELSEy<=input(3);END IF;END PROCESS;END rtl;三、文本文件的编译及仿真全过程在编辑器中输入并保存了以上四选一选择器的VHDL源程序后就可以对它进行编译了,编译的最终目的是为了生成可以进行仿真、定时分析及下载到可编程器件的相关文件,如*.cnf,*.rpt,*.snf,*.pof 等。

4选1多路选择器VHDL语言设计

4选1多路选择器VHDL语言设计在VHDL语言中设计一个4选1多路选择器主要涉及到以下几个方面:实体声明、端口声明、内部信号声明、内部结构设计、行为建模以及仿真测试。

下面是一个VHDL语言设计的参考模板,详细解释了每个步骤的实现方法。

1. 实体声明(Entity Declaration)```vhdlentity mux_4to1 isportA, B, C, D : in std_logic;S : in std_logic_vector(1 downto 0);CLK : in std_logic;Y : out std_logicend mux_4to1;```2. 端口声明(Port Declaration)端口声明定义了输入和输出端口的类型。

在这个例子中,输入和输出端口的类型都是标准逻辑类型。

```vhdlarchitecture behavioral of mux_4to1 issignal input_mux : std_logic_vector(3 downto 0);beginA <= input_mux(0);B <= input_mux(1);C <= input_mux(2);D <= input_mux(3);end behavioral;```3. 内部信号声明(Internal Signal Declaration)内部信号声明是为了辅助模块内的信号传输和处理。

在这个例子中,我们需要声明一个内部信号来保存选择信号S对应的多路选择器输入信号。

```vhdlarchitecture behavioral of mux_4to1 issignal input_mux : std_logic_vector(3 downto 0);signal mux_out : std_logic;beginA <= input_mux(0);B <= input_mux(1);C <= input_mux(2);D <= input_mux(3);end behavioral;```4. 内部结构设计(Internal Structure Design)内部结构设计定义了多路选择器的逻辑结构。

VHDL语言设计4选1多路选择器讲解学习

V H D L语言设计4选1多路选择器4选1多路选择器的VHDL描述要求:THEN语句和CASE语句实现4选1多路选择器,其中选择控制信号s1和s0的数据类型为STD_LOGIC_VECTOR;当s1=‟0‟,s0=‟0‟;s1=‟0‟,s0=‟1‟;s1=‟1‟,s0=‟0‟和s1=‟1‟,s0=‟1‟时,分别执行y<=a、y<=b、y<=c、y<=d。

一、解法1:用IF_THEN语句实现4选1多路选择器(1)程序:LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY mux41 ISPORT (a,b,c,d: IN STD_LOGIC;s0: IN STD_LOGIC;s1: IN STD_LOGIC;y: OUT STD_LOGIC);END ENTITY mux41;ARCHITECTURE if_mux41 OF mux41 ISSIGNAL s0s1 : STD_LOGIC_VECTOR(1 DOWNTO 0);--定义标准逻辑位矢量数据BEGINs0s1<=s1&s0; --s1相并s0,即s1与s0并置操作PROCESS(s0s1,a,b,c,d)BEGINIF s0s1 = "00" THEN y <= a;ELSIF s0s1 = "01" THEN y <= b;ELSIF s0s1 = "10" THEN y <= c;ELSE y <= d;END IF;END PROCESS;END ARCHITECTURE if_mux41;(2)编译的结果如下:编译报告:二、解法2:用CASE语句实现4选1多路选择器(1)程序:LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY mux41 ISPORT (a,b,c,d: IN STD_LOGIC;s0: IN STD_LOGIC;s1: IN STD_LOGIC;y: OUT STD_LOGIC);END ENTITY mux41;ARCHITECTURE case_mux41 OF mux41 ISSIGNAL s0s1 : STD_LOGIC_VECTOR(1 DOWNTO 0);--定义标准逻辑位矢量数据类型BEGINs0s1<=s1&s0; --s1相并s0,即s1与s0并置操作PROCESS(s0s1,a,b,c,d)BEGINCASE s0s1 IS --类似于真值表的case语句WHEN "00" => y <= a;WHEN "01" => y <= b;WHEN "10" => y <= c;WHEN "11" => y <= d;WHEN OTHERS =>NULL ;END CASE;END PROCESS;END case_mux41;(2)编译结果:编译报告:。

实验二 四选一多路选择器的设计

实验二四选一多路选择器的设计姓名:庞啟明学号:1112120110 专业:自动化一、实验目的进一步熟悉QuartusⅡ的Verilog HDL文本设计流程,学习组合电路的设计、仿真和硬件测试。

二、实验原理if_else条件语句描述方式,以过程语句引导的顺序语句,适合描述复杂逻辑系统的行为描述语句。

(1)以模块定义语句关键词module_endmodule引导完整的电路模块。

(2)以input和output语句引导模块的外部端口。

(3)以reg等关键词定义模块内将出现的相关信息的特征和数据类型。

(4)以always @ 等关键词引导对模块逻辑功能描述的语句。

负责描述电路器件的内部逻辑功能和电路结构。

三、实验设备与软件平台实验设备:计算机、FPGA硬件平台是Cyclone系列FPGA软件平台:Quartus II 9.1 (32-Bit)、5E+系统四、实验内容编写Verilog程序描述一个电路,实现以下功能:具有6个输入端口 A、B、C、D、S1、SO,A、B、C、D均为输入端口,位宽为1;Sl、S0为通道选择控制信号端,位宽为1;Y为输出端口,位宽为1。

当S1S0为“00”时,A的数据从Y输出,S1S0为“01”时,B的数据从Y输出,S1S0为“10”时,C的数据从Y输出,S1S0为“11”时,D的数据从Y输出。

五、实验步骤设计流程:1、编辑和输入设计文件(1)、新建一个文件夹如D:\MUX41 ,本工程所有文件将存放在此目录中。

1)输入VHDL源程序打开QuartusII,选择菜单File->New。

选择Verilog HDL File,输入源程序。

2)文件存盘选择File->Save As命令,找到已设立的文件夹D:\MUX41,存盘文件名应与实体名一致,存盘为MUX41.v。

当出现语句“do you want to create…..”的对话框,选择“是”自动创建工程。

这里先选择“否”,即暂时不创建工程流程。

EDA技术4选1多路选择器实验报告

EDA技术4选1多路选择器实验报告实验报告:EDA技术4选1多路选择器实验一、实验目的本实验旨在通过EDA(Electronic Design Automation)技术,利用4选1多路选择器实现数据选择功能,加深对数字电路设计基础知识的理解,掌握EDA技术的实际应用。

二、实验原理4选1多路选择器是一种数字逻辑电路,它有4个数据输入端,1个数据输出端和2个选择端。

通过控制选择端的状态,可以选择其中一个数据输入端的数据输出到输出端。

三、实验步骤1.实验准备在实验前,需要准备以下设备和软件:•数字逻辑实验箱•EDA软件(如Quartus II)•连接线若干•万用表•实验电路板•4选1多路选择器芯片(如74LS153)•发光二极管及限流电阻(用于显示输出结果)2.实验操作(1)将4选1多路选择器芯片连接到实验电路板上,并按照要求连接发光二极管及限流电阻。

(2)使用EDA软件创建新项目,并选择合适的FPGA芯片型号。

(3)在新项目中添加4选1多路选择器模块,并将其与FPGA芯片连接。

(4)根据实验要求,编写控制逻辑的VHDL或Verilog代码。

(5)将控制逻辑代码编译并下载到FPGA芯片中。

(6)使用万用表检查连接是否正确,发光二极管是否亮起。

(7)通过改变选择端的输入状态,观察发光二极管亮灭情况,验证4选1多路选择器的数据选择功能。

四、实验结果与分析通过本次实验,我们成功地利用4选1多路选择器实现了数据选择功能。

在EDA软件中,我们设计了合适的控制逻辑,将选择的输入数据传送到输出端,并通过发光二极管显示输出结果。

当改变选择端的输入状态时,观察到发光二极管的亮灭情况随之改变,证明了4选1多路选择器的数据选择功能。

通过本次实验,我们深入了解了数字电路设计的基本知识,掌握了EDA技术在实践中的应用。

通过使用EDA软件进行设计、编译和下载程序,我们能够更加便捷地进行数字电路实验。

此外,通过实际操作,我们学会了使用数字逻辑实验箱、万用表等实验设备,提高了实践操作能力。

VHDL语言设计4选1多路选择器演示教学

VHDL 语言设计 4 选 1多路选择器4选1多路选择器的VHDL描述要求:THEN语句和CASE语句实现4选1多路选择器,其中选择控制信号 si和s0 的数据类型为STD_LOGIC_VECTORs仁?O?,sO=?O?; s仁?O?,sO=?1?; s1=? 1?,sO=?O?和s仁?1?,sO=?1?时,分别执行 y<=a、yv=b、yv=c、yv=d。

一、解法1:用IF_THEN语句实现4选1多路选择器(1)程序:LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY mux41 ISPORT (a,b,c,d: IN STD_LOGIC;sO: IN STD_LOGIC;s1: IN STD_LOGIC;y: OUT STD_LOGIC);END ENTITY mux41;ARCHITECTURE if_mux41 OF mux41 ISSIGNAL sOs1 : STD_LOGIC_VECTOR(1 DOWNTO 0)定义标准逻辑位矢量数据 BEGINsOs1<=s1 &s0; --s1 相并sO,即s1与sO并置操作PROCESS(sOs1,a,b,c,d)BEGINIF sOs1 = "00" THEN y <= a;ELSIF s0s1 = "01" THEN y <= b;ELSIF s0s1 = "10" THEN y <= c;ELSE y <= d;END IF;END PROCESS;END ARCHITECTURE if_mux41;(2)编译的结果如下:_1 ―LIBRARYZ USE IEEE・2rTD_L0GTC_l.l石岂・ALL;3 3 EWTITY ttittK41lS3 SPORT (引4 6* IN 5TD_LOfJIC;55U;IN STP_LOGIC;631:IN ST^OGIC:7y:OUT 号T D I L OGM):a EMD ENTITY mux41;9: ■: ARCHITECTURE l£_mux41 OF ntux^a IS10SIGMAL sOsl : STD_LOGIC_VECTOR (1 DOUWTO 0);—定义标准逻辑位矢虽数据11 B BEGIN12gOsK^gltsO;——s 上相并即R与如并査操柞13PROCESS [s口sl r a.to^cr,d)148EGIN15S IF sOst = J|00»THEN y <= a;IS S!ELS IF sOsl = f,m rr THEN y «h;17 BELSIF sOsl = M10r,THEN y <= c;19. ELSE y <- d;3 EMb TF^20EHD PROCESS;21EWP ARCHITECTURE22编译报告:Flow Status.Succsssfiil - !lon Miy 23 2^:24:40 201&Quartus II Versi on90 Buili 132 02/25/2009 S5 Full VersicnRe^isiom Name mix4iTop-level Entity Name n*ux4iFamily FLEK1CKDevice ErF10KIQlJCa4-4Timing Finfcl用包七tim lug r equir eniexit Y esTot 1®番iu ents 2 / 7T6 ( < 1 )Total pins T F阴〔12慕〕Total memory bi Is0/6.144 ( D % )二、解法2:用CASEg句实现4选1多路选择器(1)程序:LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY mux41 ISPORT (a,b,c,d: IN STD_LOGIC;sO: IN STD_LOGIC;s1: IN STD_LOGIC;y: OUT STD_LOGIC);END ENTITY mux41;ARCHITECTURE case_mux41 OF mux41 ISSIGNAL s0s1 : STD_LOGIC_VECTOR(1 DOWNTO 0)定义标准逻辑位矢量数据类型BEGINs0s1<=s1 &s0; --s1 相并s0,即s1与s0并置操作PROCESS(s0s1,a,b,c,d)BEGINCASE s0s1 IS --类似于真值表的case语句WHEN "00" => y <= a;WHEN "01" => y <= b;WHEN "10" => y <= c;WHEN "11" => y <= d;WHEN OTHERS =>NULL ;END CASE;END PROCESS;END case_mux41;(2)编译结果:1LTBRARV IEEE;2USE IEEE,STD LOGIC i 15^1 .ALL;3j ENTITY K1UK41IS4SPORT (a f to r c r d: IN STD_LOGIC;5sn:IN STD_LCX;IC;651;IN TTD^LOGTC;7y: OUT STD^LOGIC);8ENDENTITY-H1UX41;9□ARCHITECTURE case_wux4i OF I»LD<41IS10SIGNAL sosl : 5TD~LOGIC_VECTOR(1 DOWNTO 口心--定文标准逻辑位矢區数据类型11/:BEGIN122031<=Sl£sa;__ml相并"0r Wsl与兰□并萱燥件13H PROCESS(snsl r a r b r e f ri)BEGIM15□CASE sOsl IS —斐馆于克值恚的c*匕语旬ie WHEN f,ao if -> y 5 a;17WHEN f,0i,F=> y <- b;!□WHEN "1口“三A y <= c;19WHEN rr ll FT F y a= d;20WHEN OTHERS =AHULL ;21 EWD 匚ASE;22EMD PROCESS;END case_inux41;24编译报告:Flo* Status SucceKifvl ~ Mon fflfcy 23 22 31:55 20fEQuartus II Version9.0 Btiild 132 02/25/20M ST lull VersionRevi'sicin Name mux41T op^laval Inti ty Nwna wux-41F anally FmiOKD evi. c e E?PLOE1Dire4-4Timkiig Jftoifvli FinUMet timing re^uir畑Total lagi c el 2 / 5T6 ( < 1 )Total pins7 / 5S ( 12 )T otal memory bits0 / e, 144 ( D 囂)。

(VHDL实验报告)四选一数据选择器的设计

两个为控制信号输入端)和一个输出端。其真值表如下图 所示:

四选一多路选择器的 VHDL 描述非常灵活,可以采用多种语

句来实现。本实验要求分别用VHDL顺序语句和并行语句来 实现。

四、实验内容

在本实验中,用六个拨动开关来表示四选一数据选择器四

五、实验步骤

1、建立工程文件

1)运行QUARTUSII 软件。 2)选择软件中的菜单 File>New Project Wizard, 新建一个工程。 3)点击NEXT进入工作目录,设定工程名和实体名。 4)点击NEXT,进入下一设定对话框,(本次实验选 用Cyclone II系列芯片EP2C35F672C8),在对话框的左上方 的 Family 下拉菜单中选取 CycloneII ,在中间右边的Pin count下拉菜单中选取 672,在 Speed grade 下拉菜单中选 取 8,在左下方的 Available devices 框中选取 EP2C35F672C8 。点击 NEXT 完成器件的选取,进入 EDA TOOL设定界面。 5)按默认选项,点击NEXT出现新建工程以前所有的 设定信息,再点击FINISH完成新建工程的建立。

五、实验步骤

3、管脚分配

1)在前面选择好一个合适的目标器件(在这个实验中选择 为EP2C35F672C8)完成设计的分析综合过程,得到工程的数据文 件以后,需要对设计中的输入、输出引脚指定到具体的器件管脚 号码,指定管脚号码称为管脚分配或管脚锁定。这里介绍两种方 法进行管脚锁定。 2)点击 Assignments 菜单下面的 Assignment Editor, 进入到引脚分配窗口。将弹出的窗口中的 All 改成 pin ,再点 击 List,在 Nodes Found窗口会出现所有信号的名称,点击中间 的按钮则Selected Nodes 窗口下方出现被选择的端口名称。双击 OK 按钮,完成设置。进入管脚分配窗口。 3)依照“硬件与 FPGA 的管脚连接表”分配对应的输入 管脚名 ,依照“LED灯与FPGA管脚连接表”分配对应的输出管脚 名。本次实验的分配关系是:(输入端 D3、D2、D1、D0、sel1、 sel0 分别对应的 FPGA 管脚名为 H8、J8、J9、A4、B5、A6,输 出端 y 对应的 FPGA 管脚名为 G13 ),如下图所示。 4)分配完管脚后,再次进行一次全编译,使分配的管脚

EDA技术4选1多路选择器实验报告

EDA技术4选1多路选择器实验报告实验报告:EDA技术4选1多路选择器1.引言多路选择器是一种常见的组合电路,用于从多个输入信号中选择出一个输出信号。

在数字电路设计中,采用EDA(Electronic Design Automation)技术可以方便地进行多路选择器的设计、模拟和验证。

本实验旨在使用EDA技术设计、模拟和验证一个4选1多路选择器。

2.设计本实验采用Verilog HDL语言进行设计。

首先,我们定义一个4位的输入端口sel,用于选择4个输入信号in0、in1、in2和in3中的一个。

然后,我们定义一个输出端口out,用于输出被选择的信号。

接下来是设计的核心部分,根据4位选择信号sel的不同取值,选择相应的输入信号作为输出信号。

我们使用一个case语句来实现多路选择器的选择功能。

3.仿真为了验证设计的正确性,我们使用EDA技术对多路选择器进行了仿真。

在仿真中,我们可以输入不同的选择信号和输入信号组合,观察输出结果是否符合预期。

通过仿真,我们可以验证多路选择器在不同输入和选择信号组合下的正确性和稳定性。

如果输出结果与预期一致,那么我们可以得出结论:设计的多路选择器是正确的。

4.验证验证是设计过程中非常重要的一步,通过验证可以判断设计是否达到了预期的功能和性能要求。

我们使用EDA技术对多路选择器进行了验证。

在验证过程中,我们更加注重多路选择器的性能指标,如延迟和功耗等。

我们可以通过模拟分析和优化来改进多路选择器的性能。

5.总结本实验通过使用EDA技术设计、模拟和验证了一个4选1多路选择器。

通过实验我们学习了EDA技术在数字电路设计中的作用和应用。

同时,我们了解了多路选择器的基本原理和设计方法,掌握了Verilog HDL语言的设计和仿真技巧。

通过本实验,我们发现EDA技术能够极大地提高数字电路设计的效率和准确性。

通过合理应用EDA技术,我们可以设计出更加可靠、高效的数字电路,并且可以方便地对其进行仿真和验证。

实验五 4选1多路复用器和4位比较器设计与仿真

实验五 4选1多路复用器和4位比较器设计与仿真班级信息安全一班姓名邓一蕾学号201208060106指导老师袁文澹一、实验目的1.熟悉QuartusⅡ仿真软件的基本操作,并用VHDL语言和逻辑图设计四选一多路选择器,4位比较器。

二、实验内容1.参照芯片74LS153的电路结构,用逻辑图和VHDL语言设计四选一多路复用器;2.从QuartusⅡ中取7485器件(比较器)进行仿真与分析;用VHDL语言设计4位比较器,接着进行仿真与分析,电路逻辑结构参照芯片74x85三.实验原理1.(1)四选一多路选择器逻辑电路的原理4选1多路选择器,GN为使能端,AB为选择通道控制端,c0,c1,c2,c3为数据输入端.Y 为输出端。

当GN为1时,y=0;当GN为0,AB=00时,Y为c0的值;当GN为0,AB=01时,Y为c1的值;当GN为0,AB=10时,Y为c2的值;当GN为0,AB=11时,Y为c3的值;(2)通过实验实现逻辑的原理2.(1)4位比较器的逻辑电路图A0,B0,A1,B1,A2,B2,A3,B3为相比较数输入端,ALBI,AEBI,AGBI为级联输入端ALBO,AEBO,AGBO为比较输出端。

2)通过实验实现逻辑的逻辑功能表为四、实验方法与步骤实验方法:采用基于FPGA进行数字逻辑电路设计的方法。

采用的软件工具是QuartusII软件仿真平台,采用的硬件平台是Altera EPF10K20TI144_4的FPGA试验箱。

1.4选1多路选择器实验步骤:编写源代码。

打开QuartusⅡ软件平台,点击File中得New建立一个文件。

编写的文件名与实体名一致,点击File/Save as以“.vhd”为扩展名存盘文件。

2、按照实验箱上FPGA的芯片名更改编程芯片的设臵。

操作是点击Assign/Device,选取芯片的类型。

建议选“Altera的EPF10K20TI144_4”3、编译与调试。

确定源代码文件为当前工程文件,点击Complier进行文件编译。

(完整word版)四选一多路选择器实验报告

学院:电气工程学院 专业: 电子信息工程班级:

姓名

学号

实验组

实验时间

指导教师

成绩

实验项目名称

四选一多路选择器

实验目的

1.学习组合逻辑电路、编码器的功能与定义,学习Verilog和VHDL语言

2.熟悉利用Quartus II开发数字电路的基本流程和Quartus II软件的相关操作

3.学会使用Vector Wave波形仿真

ELSIF(sel=“01”)THEN

y<= input(1);

ELSIF(sel=“10”)THEN

y<= input(2);

ELSE

y〈= input(3);

END IF;

END PROCESS;

END rtl;

二:程序运行图:

三:波形图:

实验总结

本次实验学习了组合逻辑电路、编码器的功能与定义,学习了Verilog和VHDL语言,同时熟悉了利用Quartus II开发数字电路的基本流程和Quartus II软件的相关操作,学会了使用Vector Wave波形仿真。实验过程中也遇到了很多自己不能解决的问题,在同学和老师的帮助下算是知道问题的所在,有待在今后的学习中不断完善。

实验要求

按照老师的要求完成实验,编写实验报告

实验原理

选择器常用于数字信号的切换 四选一选择器可以用于4路信号的切换.四选一选择器有4个输入端input0、1、2、3.两个信号控制端a,b及一个信号输出端y。当a,b输入不同的选择信号时 就可以使input0-input3中的一个输入信号与输出y端口接通. 用拨码开关作四位数据及两位控制端的输入 LED作输出 通过拨码开关组成控制输入端s1和s0不同组合 观察LED与数据输入端a,b,c,d的关系 验证4选一数据选择器设计的正确性。

VHDL实验 4选1多路选择器

VHDL实验报告学院: 理学院专业:电子信息科学与技术班级:电科091END IF;END PROCESS; PROCESS进程语句结束END ARCHITECTURE rtl;1.实验源程序如下:实验步骤与数据82. 创建文件夹,保存文件。

3.选择芯片为‘EP1C6Q240C8’。

4. 完成设置,显示文件信息。

从显示中我们看到项目和实体名为:MUX4A1,其中只有一个文件,芯片为Cyclone系列的EP1C6Q240C8。

5.运行通过6.运行后的RTL视图7.波形分析(1)添加文件和引脚。

(2)设置输入信号。

可以对输入进行设置.结果分析:①当b='0',a='0'时候,选择出input(0),②当b='0',a='1',时候,选择出input(1)③当b='1',a='0'时候,选择出input(2),④当b='1',a='1'时候,选择出input(3),符合程序结果8.配置引脚⑴选择“Assignments”菜单的“Pins”命令,打开引脚编辑窗口。

四选一数据选择器的引脚分配如下:(2)在设置完引脚后,再次对程序进行编译。

这样就把程序与FPGA的引脚联系起来,这样才能将程序下载到FPGA 开发系统中进行运行仿真。

下载到FPGA中,并验证程序的运行结果。

(3)配置硬件驱动为“ByteBlassterMV[LPT1]”,然后“start”下载,到下载为100%即可完成和对程序进行试验。

9.实验结果。

第3章2选1和4选1选择器VHDL设计

3.3 4选1多路选择器及其VHDL描述

例3-3 仿真结果

summary

❖信号signal; ❖逻辑运算符; ❖进程process语句;语句的分类; ❖条件if语句; ❖库和程序包; ❖标准逻辑位和矢量型数据; ❖并置&操作符; ❖注释--符号; ❖case语句;

思考

❖如何用VHDL设计二进制加法器?

ARCHITECTURE one OF mux21a2 IS SIGNAL d,e : BIT;

BEGIN d <= a AND s ; e <= b AND (NOT S) ; y <= d OR e ;

END ARCHITECTURE one ;

3.1 多路选择器的VHDL描述

3.1 多路选择器的VHDL描述

mux21a2

a

y

b

s

3.1 多路选择器的VHDL描述

相关语法

1.信号signal

信号是VHDL中常用三大数据对象之一,所谓数据对象 是指用来保存不同类型数据的对象。

注意:信号相当于一根带电导线,用于暂存数据。

2.逻辑运算符

运算符类型 逻辑运算符

运算符符号

AND

OR NOT NAND NOR XOR XNOR

PORT ( a, b, s: IN BIT; y: OUT BIT);

END ENTITY mux21a; ARCHITECTURE one OF mux21a IS BEGIN

PROCESS (a,b,s) BEGIN IF (s = '1') THEN y <= a ; ELSE y <= b ; END IF;

【例3-3】

LIBRARY IEEE; USE IEEE.STD_LOGIC_1164.ALL; ENTITY MUX41A IS PORT(a,b,c,d,s0,s1:IN STD_LOGIC;

(完整word版)4选1多路选择器VHDL语言设计

(完整word版)4选1多路选择器VHDL语言设计一.4选1多路选择器VHDL语言设计4选1多路选择器源代码:LIBRARY IEEE;USE IEEE.STD_LOGIC_1164。

ALL;ENTITY max4_1 ISPORT(a,b,c,d,s1,s2 :IN STD_LOGIC;y :OUT STD_LOGIC); END ENTITY max4_1;ARCHITECTURE hf1 OF max4_1 ISSIGNAL ss : STD_LOGIC_VECTOR (0 TO 1); BEGINss〈=s2&s1;PROCESS(ss)BEGINCASE ss ISWHEN "00” =〉y〈=a;WHEN ”01" => y<=b;WHEN "10” =〉y<=c;WHEN "11" =〉y<=d;WHEN OTHERS => NULL; END CASE;END PROCESS;END ARCHITECTURE hf1;图1。

4选1电路图图2。

4选1波形仿真图二.三位触发器VHDL语言设计三位触发器设计原代码:LIBRARY IEEE;USE IEEE。

STD_LOGIC_1164.ALL;ENTITY DFF3 ISPORT( D,CLK :IN STD_LOGIC;Q0,Q1,Q2:OUT STD_LOGIC);END DFF3;ARCHITECTURE bhv OF DFF3 ISSIGNAL Q00,Q11,Q22 : STD_LOGIC;BEGINPROCESS(CLK,Q00,Q11,Q22)BEGINIF CLK’EVENT AND CLK='1'THEN Q00<=D;Q11<=Q00;Q22〈=Q11;END IF;END PROCESS;Q0〈=Q00;Q1<=Q11;Q2〈=Q22;END bhv;图3. 三位触发器电路图图4。

实验五--4选1多路复用器和4位比较器设计与仿真

实验五 4选1多路复用器和4位比较器设计与仿真班级信息安全一班姓名邓一蕾学号2指导老师袁文澹一、实验目的1.熟悉QuartusⅡ仿真软件的基本操作,并用VHDL语言和逻辑图设计四选一多路选择器,4位比较器。

二、实验内容1.参照芯片74LS153的电路结构,用逻辑图和VHDL语言设计四选一多路复用器;2.从QuartusⅡ中取7485器件(比较器)进行仿真与分析;用VHDL语言设计4位比较器,接着进行仿真与分析,电路逻辑结构参照芯片74x85三.实验原理1.(1)四选一多路选择器逻辑电路的原理4选1多路选择器,GN为使能端,AB为选择通道控制端,c0,c1,c2,c3为数据输入端.Y为输出端。

当GN为1时,y=0;当GN为0,AB=00时,Y为c0的值;当GN为0,AB=01时,Y为c1的值;当GN为0,AB=10时,Y为c2的值;当GN为0,AB=11时,Y为c3的值;(2)通过实验实现逻辑的原理2.(1)4位比较器的逻辑电路图A0,B0,A1,B1,A2,B2,A3,B3为相比较数输入端,ALBI,AEBI,AGBI为级联输入端ALBO,AEBO,AGBO为比较输出端。

2)通过实验实现逻辑的逻辑功能表为四、实验方法与步骤实验方法:采用基于FPGA进行数字逻辑电路设计的方法。

采用的软件工具是QuartusII软件仿真平台,采用的硬件平台是Altera EPF10K20TI144_4的FPGA试验箱。

1.4选1多路选择器实验步骤:编写源代码。

打开QuartusⅡ软件平台,点击File中得New建立一个文件。

编写的文件名与实体名一致,点击 as以“.vhd”为扩展名存盘文件。

2、按照实验箱上FPGA的芯片名更改编程芯片的设置。

操作是点击Assign/Device,选取芯片的类型。

建议选“Altera的EPF10K20TI144_4”3、编译与调试。

确定源代码文件为当前工程文件,点击Complier进行文件编译。

练习3_VHDL实现四选一的程序(选择信号)

课本P28-49

第五讲重点:

重点:1. 掌握VHDL语言的实体和结构体的描述。

(P30_P32)PORT端口说明。

(P31)

2. 熟悉库和程序包的说明语句。

(P33_P34)

例如:LIBRARY IEEE;

USE IEEE.std_logic_1164.all;

USE IEEE. STD_LOGIC_UNSIGNED.ALL;

USE IEEE. STD_LOGIC_SIGNED.ALL;

USE IEEE. STD_LOGIC_ARITH.ALL

3. 熟悉数据类型(P42-46)

BIT、BIT_VECTOR、STD_LOGIC、STD_LOGIC_VECTOR。

2. 熟悉信号赋值语句的用法(P57_P58)

(包括:并行信号赋值语句、条件信号赋值语句和选择信号赋值语句。

)

1、写出一位全加器电路(如下图)的实体和结构体描述。

(用并行信号赋值语句)

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

ENTITY IS

PORT ( );

END ;

ARCHITECTURE OF IS

BEGIN

S<=

Co<=

END ;

2、试写出8选1多路选择器的VHDL描述。

选择控制信号为s2,s1和s0,输入信号为i0~i7输出信号为y。

(要求分别用条件信号赋值和选择信号赋值语句)参考下面4选1多路选择器的VHDL描述

(1)用条件信号赋值语句

(2)用选择信号赋值语句

现。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

一.4选1多路选择器VHDL语言设计

4选1多路选择器源代码:

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

ENTITY max4_1 IS

PORT(a,b,c,d,s1,s2 : IN STD_LOGIC;

y : OUT STD_LOGIC); END ENTITY max4_1;

ARCHITECTURE hf1 OF max4_1 IS

SIGNAL ss : STD_LOGIC_VECTOR (0 TO 1); BEGIN

ss<=s2&s1;

PROCESS(ss)

BEGIN

CASE ss IS

WHEN "00" => y<=a;

WHEN "01" => y<=b;

WHEN "10" => y<=c;

WHEN "11" => y<=d;

WHEN OTHERS => NULL; END CASE;

END PROCESS;

END ARCHITECTURE hf1;

图1. 4选1电路图

图2. 4选1波形仿真图

二.三位触发器VHDL语言设计

三位触发器设计原代码:

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL; ENTITY DFF3 IS

PORT( D,CLK : IN STD_LOGIC;

Q0,Q1,Q2: OUT STD_LOGIC); END DFF3;

ARCHITECTURE bhv OF DFF3 IS

SIGNAL Q00,Q11,Q22 : STD_LOGIC; BEGIN

PROCESS(CLK,Q00,Q11,Q22)

BEGIN

IF CLK'EVENT AND CLK='1'

THEN Q00<=D;

Q11<=Q00;

Q22<=Q11;

END IF;

END PROCESS;

Q0<=Q00;

Q1<=Q11;

Q2<=Q22;

END bhv;

图3. 三位触发器电路图

图4. 三位触发器波形仿真图三.P94 图3-33 时序电路图的VHDL描述

VHDL原代码:

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

ENTITY DFF0 IS

PORT(CL,CLK0 : IN STD_LOGIC;

OUT1 : OUT STD_LOGIC);

END ENTITY;

ARCHITECTURE bhv OF DFF0 IS

SIGNAL Q1,D0 : STD_LOGIC;

BEGIN

PROCESS(CLK0,Q1)

BEGIN

IF CLK0'EVENT AND CLK0='1'

THEN Q1<=D0;

END IF;

END PROCESS;

D0<=NOT(Q1 OR CL);

OUT1<=NOT Q1;

END bhv;

图5. 时序电路图。