LVDS接口设计

LVDS原理及设计指南

LVDS原理及设计指南LVDS全称为低压差分信号(Low Voltage Differential Signaling),是一种高速串行接口技术,广泛应用于电子设备中进行高速数据传输。

LVDS主要通过两对差分信号进行数据传输,其中一对信号传输高电平信号,另一对信号传输低电平信号,通过差分运算来提高抗干扰能力和抗噪声能力,以实现高质量的数据传输。

LVDS的工作原理如下:1.发送端:将输入信号通过电流驱动压缩成低压差分信号,并通过双绞线传输给接收端。

2.传输线路:使用双绞线进行数据传输,利用差分运算来抵消传输线上的共模噪声和反射噪声。

3.接收端:对接收到的低压差分信号进行解码,还原成原始的输入信号。

设计LVDS接口时需要注意以下几点:1.信号线路的设计:为了保证信号的完整性和稳定性,需要控制信号线的阻抗匹配,减小信号线的长度和延迟,并避免信号线与高频噪声信号线的交叉和平行布线。

2.布线和PCB设计:保持信号线的长度均匀,并尽量使用同一层或相邻层进行差分信号线布线,以减小信号线之间的不平衡和串扰。

3.电源和接地:为了提供噪声的抑制和信号的稳定性,需要使用低噪声电源和低阻抗接地。

4.EMI抑制:由于LVDS接口传输速率高,会引起较大的电磁辐射干扰,因此需要在设计中加入适当的EMI抑制措施,如电磁屏蔽、地线设计和滤波器等。

5.信号匹配:为了保证所发送信号的完整性和稳定性,需要将发送端与接收端之间的差分阻抗匹配,以最大限度地减小信号反射和串扰。

总之,LVDS是一种高速串行接口技术,通过差分运算进行数据传输,具有抗噪声和抗干扰能力强的特点。

在设计LVDS接口时需注意信号线路的设计、布线和PCB设计、电源和接地、EMI抑制以及信号匹配等方面,以保证高质量的数据传输。

完整版)LVDS接口详解

完整版)LVDS接口详解LVDS输出接口是一种数字视频信号传输方式,它利用低压差分信号技术接口,在两条PCB走线或一对平衡电缆上通过差分进行数据的传输。

相比于TTL接口,LVDS输出接口具有高速率、低噪声、远距离、高准确度等优点,因此在17in及以上液晶显示器中得到了广泛的应用。

LVDS接口电路由驱动板侧的LVDS输出接口电路(LVDS发送器)和液晶面板侧的LVDS输入接口电路(LVDS接收器)组成。

LVDS发送器将驱动板主控芯片输出的17L电平并行RGB数据信号和控制信号转换成低电压串行LVDS信号,然后通过柔性电缆传送到液晶面板侧的LVDS接收器。

LVDS接收器再将串行信号转换为TTL电平的并行信号,送往液晶屏时序控制与行列驱动电路。

在数据传输过程中,LVDS接口采用差分信号对的形式进行传输,每个数据传输通道或时钟传输通道的输出都为两个信号(正输出端和负输出端)。

这种方式不仅可以提高数据传输速率,还可以减少电磁干扰和功耗,使得LVDS输出接口更加稳定可靠。

不同种类的液晶显示器的驱动板上的LVDS发送器并不相同。

有些LVDS发送器是一片或两片独立的芯片,例如DS90C383;而有些则是集成在主控芯片中,例如主控芯片gm5221内部集成了LVDS发送器。

LVDS输出接口也分为四种类型,其中第一种是单路6位LVDS输出接口。

这种接口电路采用单路方式传输,每个基色信号(即RGB三色中的其中任何一种颜色)采用6位数据(XOUT0+、TXOUT0-,TXOUT1+、TXOUT1-,TXOUT2+、TXOUT2-),共18位RGB(6bit X 3(RGB3色))数据,因此也被称为18位或18bit LVDS接口。

第二种是双路6位LVDS输出接口。

在这种接口电路中,两个基色信号(例如红色和绿色)共用一条传输线,而蓝色信号则使用另一条传输线,每个基色信号采用6位数据,因此也被称为双路18位或18bit LVDS接口。

LVDS标准及介绍-(2)

LVDS1.0 LVDS简介LVDS(Low Voltage Differential Signaling)是一种低摆幅的差分信号技术,它使得信号能在差分PCB线对或平衡电缆上以几百Mbps的速率传输,其低压幅和低电流驱动输出实现了低噪声和低功耗.1.1 LVDS信号传输组成LVDS信号传输一般由三部分组成,如图1所示:差分信号发送器,差分信号互联器,差分信号接收器.图1 简单的单工LVDS接口连接图差分信号发送器:将非平衡传输的TTL信号转换成平衡传输的LVDS信号.通常由一个IC来完成.差分信号接收器:将平衡传输的LVDS信号转换成非平衡传输的TTL信号。

通常由一个IC来完成.差分信号互联器:包括联接线(电缆或者PCB走线),终端匹配电阻。

1.2 LVDS的工作原理图2 LVDS接口电路图如图2所示,LVDS驱动器由一个驱动差分线对的电流源组成(通常电流为3。

5mA),LVDS 接收器具有很高输入阻抗,因此驱动器输出的电流大部分都流过100Ω的匹配电阻,并在接收器的输入端产生生大约350mV的电压。

驱动器的输入为两个相反的电平信号,四个nMOS管的尺寸工艺是完全相同的.当输入为“1”时,标号IN+的一对管子导通,另一对管子截止,电流方向如图2,并产生大约350mV的压降;反之,输入为“0”时,电流反向,产生大约350mV的压降.这样根据流经电阻的电流方向,就把要传输的数字信号(CMOS信号)转换成了电流信号(LVDS信号)。

接受端可以通过判断电流的方向就得到有效的逻辑“1”和逻辑“0"状态。

从而实现数字信号的传输过程。

由于MOS管的开关速度很高,并且LVDS的电压摆幅低(350mV),因此可以实现高速传输.其电平特性如下图所示1.3 LVDS的国际标准LVDS是目前高速数字信号传输的国际通用接口标准,国际上有两个工业标准定义了LVDS:ANSI/TIA/EIA(American National Standards Institute/Telecommunications Industry Association/Electronic Industries Association)和IEEE(Institute for Electrical and Electronics Engineering)。

高速LVDS接口电路设计

收稿日期:2009-11 作者简介:范丹(1985—),男,硕士研究生,研究方向为光电对抗与信息处理。

高速LVDS 接口电路设计范 丹1,何永强1,方晋贤2(1.军械工程学院,河北石家庄050003;2.广州军区76321部队,广东广州510500) 摘要:随着数字电路数据量的提高,数据的传输速率也越来越快,LVDS (低压差分信号)标准越来越多的应用在FPG A 和ASI C 器件中。

文章对LVDS 信号的特点进行了分析,说明了PC B 设计中差分走线的注意事项并结合实际应用设计了一块LVDS 接口板。

关键词:LVDS;PC B 设计;接口;阻抗匹配中图分类号:T N41 文献标识码:A 文章编号:1006-2394(2010)04-0007-02D esi gn of L V D S I n terface C i rcu itF AN Dan 1,HE Yong 2qiang 1,F ANG J in 2xian2(1.O rdnance Engineering College,Shijiazhuang 050003,China;2.Guangzhou M ilitary Regi on,Unit 76321,Guangzhou 510500,China )Abstract:A l ong with the rap id devel opment of digital circuit technol ogy,higher data trans m issi on rate is required .A s a result,more and more LVDS (Low 2Voltage D ifferential Signaling )standards are used in digital devices .The char 2acteristic of LVDS is analyzed .The attenti ons on PCB design with LVDS are exp lained .And then a LVDS interface board is made .Key words:LVDS (l ow 2v oltage differential signaling );PCB design;interface;i m pedance matching0 引言随着电子信息技术的进步,对数据传输速率的要求也越来越高。

lvds接口电路emi设计思路

lvds接口电路emi设计思路LVDS(Low Voltage Differential Signaling)是一种差分信号传输技术,广泛应用于高速数字信号传输中,特别适用于需要长距离传输高速数据的场景,如液晶显示器、计算机内部总线、医疗设备等。

然而,由于其高速传输和低功耗的特点,LVDS接口电路设计必须注重电磁兼容性(EMI)的问题。

EMI问题是由电路中的高速信号和电源噪声引起的,主要表现为辐射和传导两种模式。

辐射是指高速信号通过信号线辐射出的电磁波,可能干扰附近的设备或导致自身受到外界干扰;传导是指高速信号通过共模和差模传导途径进入其他信号线或供电线,干扰其他电路元件的正常工作。

因此,LVDS接口电路的EMI设计需要从以下几个方面考虑:1.布线和地引线设计:在LVDS接口电路设计中,布局和布线是非常重要的。

为了减少信号线的长度和面积,应尽量将信号线紧凑排列,并使用对称布局。

另外,地引线的设计也是关键,要保证低噪声接地和地引线干扰的最小化。

通常采用单独的地平面层或小洞式接地方式。

2.差分线路设计:LVDS接口电路一般使用差分信号传输,差分信号具有抗干扰能力强的特点。

因此,在PCB设计中要注意使差分信号线与附近的信号线和电源线保持一定的距离,以降低传导干扰。

3.终端的阻抗匹配:LVDS接口中的终端阻抗匹配能够减少信号反射和辐射,提高信号质量。

终端阻抗应与传输线的特性阻抗匹配。

常用的阻抗为100欧姆。

4.电源滤波:电源滤波是减少传导干扰的重要手段之一。

在设计LVDS接口电路的电源电路时,应加入合适的滤波电容和电感,以消除电源噪声。

5.电磁屏蔽:对于经过布线和终端匹配等措施后仍然存在辐射干扰的问题,可以采用电磁屏蔽的方法。

常见的电磁屏蔽方式有添加屏蔽罩、使用屏蔽连接器等。

6.地线设计:地线设计是减少辐射干扰的重要环节。

在布线过程中,应尽量使地线和信号线保持平行的走向,并避免穿过信号线打断其连续性。

另外,增加地线的宽度和厚度有助于提高信号的传输质量和抑制干扰。

LVDS屏接口定义解析

常见LVDS屏接口定义讲解很多初学者对于如何区分屏的接口类型很是头疼,是LVDS屏,TTL屏还是RSDS 屏?总是很难搞清出。

如何快速识别出液晶屏的接口类型则需要一些经验的,下面从屏的屏线接口的样式来对接口类型做出分类的介绍,帮助大家快速识别屏的接口类型。

以下方法是个人认识,不足之处请大家谅解。

(1)TTL屏接口样式:D6T(单6位TTL):31扣针,41扣针。

对应屏的尺寸主要为笔记本液晶屏(8寸,10寸,11寸,12寸),还有部分台式机屏15寸为41扣针接口。

S6T(双6位TTL):30+45针软排线,60扣针,70扣针,80扣针。

主要为台式机的14寸,15寸液晶屏。

D8T(单8位TTL):很少见S8T(双8位TTL):有,很少见80扣针(14寸,15寸)(2)LVDS屏接口样式:D6L(单6位LVDS):14插针,20插针,14片插,30片插(屏显基板100欧姆电阻的数量为4个)主要为笔记本液晶屏(12寸,13寸,14寸,15寸)D8L(单8位LVDS):20插针(5个100欧姆)(15寸)S6L(双6位LVDS):20插针,30插针,30片插(8个100欧姆)(14寸,15寸,17寸)S8L(双8位LVDS):30插针,30片插(10个100欧姆电阻)(17寸,18寸,1 9寸,20寸,21寸)(3)RSDS屏接口样式:50排线,双40排线,30+50排线。

主要为台式机(15寸,17寸)液晶屏。

上面我们知道了屏的型号和接口了,但是我们还不知道这个是多少位的屏和多少的供电,为了让大家轻松搞会这一步,我们拿一个单6位LVDS的屏来解析一下,此款屏的型号为:LP141X3(20针插接口)屏接口定义在液晶屏的规格书里面都有这一个页面这里面出现了两组数据每组中都有一对时钟信号,这个屏我们就能看出这是一个30针双8位屏,屏的供电为5V。

常见的LVDS接口定义20PIN单6定义:1:电源2:电源3:地4:地5:R0- 6:R0+ 7:地8:R1- 9:R1+ 10:地11:R2- 12:R2+ 13:地14:CLK- 15:CLK+ 16空17空18空19空20空每组信号线之间电阻为(数字表100欧左右)指针表20-100欧左右(4组相同阻值)20PIN双6定义:1:电源2:电源3:地4:地5:R0- 6:R0+ 7:R1- 8:R1+ 9:R2- 10:R2+ 11:CLK- 12:CLK+ 13:RO1- 14:RO1+ 15:RO2- 16:RO2+ 17:RO3-18:RO3+19:CLK1- 20:CLK1+每组信号线之间电阻为(数字表100欧左右)指针表20-100欧左右(8组相同阻值)20PIN单8定义:1:电源2:电源3:地4:地5:R0- 6:R0+ 7:地8:R1- 9:R1+ 10:地11:R2- 12:R2+ 13:地14:CLK- 15:CLK+ 16:R3- 17:R3+每组信号线之间电阻为(数字表100欧左右)指针表20-100欧左右(5组相同阻值)30PIN双8定义:1:电源2:电源3:电源4:空5:空6:空7:地8:R0- 9:R0+ 10:R1- 11:R1+ 12:R2- 13:R2+ 14:地15:CLK- 16:CLK+ 17:地18:R3- 1 9:R3+ 20:RB0- 21:RB0+ 22:RB1- 23:RB1+ 24:地 25:RB2- 26:R B2+ 27:CLK2-28:CLK2+ 29:RB3- 30:RB3+每组信号线之间电阻为(数字表100欧左右)指针表20-100欧左右(10组相同阻值)一般14PIN、20PIN、30PIN为LVDS接口,15寸(含15寸)以下多为3.3V供电17(含17)以上多为5V供电。

LVDS接口电路基本原理

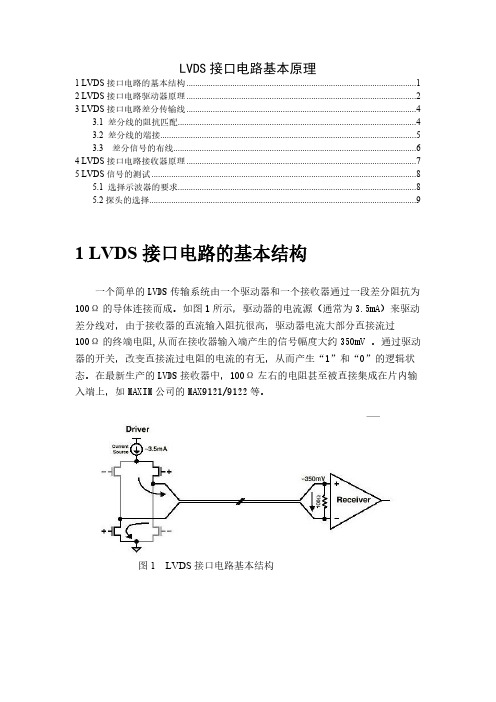

LVDS接口电路基本原理1 LVDS接口电路的基本结构 (1)2 LVDS接口电路驱动器原理 (2)3 LVDS接口电路差分传输线 (4)3.1 差分线的阻抗匹配 (4)3.2 差分线的端接 (5)3.3 差分信号的布线 (6)4 LVDS接口电路接收器原理 (7)5 LVDS信号的测试 (8)5.1 选择示波器的要求 (8)5.2探头的选择 (9)1 LVDS接口电路的基本结构一个简单的LVDS传输系统由一个驱动器和一个接收器通过一段差分阻抗为100Ω的导体连接而成。

如图1所示,驱动器的电流源(通常为3.5mA)来驱动差分线对,由于接收器的直流输入阻抗很高,驱动器电流大部分直接流过100Ω的终端电阻,从而在接收器输入端产生的信号幅度大约350mV 。

通过驱动器的开关,改变直接流过电阻的电流的有无,从而产生“1”和“0”的逻辑状态。

在最新生产的LVDS接收器中,100Ω左右的电阻甚至被直接集成在片内输入端上,如MAXIM公司的MAX9121/9122等。

图1 LVDS接口电路基本结构2 LVDS接口电路驱动器原理The Telecommunications Industry Association(TIA)颁布了一个标准,规定了用于转换二进制信号的LVDS接口电路的电气规格。

LVDS技术利用低电压差分信号来产生高速、低功率的数据传输。

差分信号的使用消除了共模噪声,因此确保了数据的传输速度以及抗噪性能。

如果想了解LVDS标准的详细信息,请查阅“Electrical Characteristics of Low Voltage Differential Signaling(LVDS)Interface Circuits”,TIA/EIA-644(March 1996)。

图2-1举例说明了一个通过一对差分连线115连接到一个LVDS接收器110的LVDS发生器100。

LVDS发生机100将一个数字的输入信号D_IN转换成为一对在差分输出终端TX_A和TX_B上的相反的LVDS输出信号。

千兆比特数据率LVDS接口电路设计

Dein o sg fLVDSI tra ef rGb sOp r t n n e f c o / e ai o

JA0 s u Z I Yih HOU ra J ANG in u Yu i I e Ja h a

( nttt f co lcrnc ieeAc d m S in e B i n ,1 0 2 , HN ) I siueo Mireeto iso Ch n s a e y o c c , e ig 0 0 9 C f f e j

d n ft ec mmo d ot g a it n ,whc nmie h n r d c d j t rwh nt ep o e to h o nmo ev la ev ra i s o ihmii z d t ei to u e i e e h r — t

第 3 卷 第 与进 展

R S A C &P O R S F S E EE R H R G E SO S

V o .3 No.1 1 O,

M a .,2 r 010

、

硅微 电子 学

\

千 兆 比特 数 据 率 L VDS接 口电路 设 计

模 范 围 内恒 定 , 因此 芯 片 在 接 收 端 引 入 的 抖 动 最 小 。 片 面 积 0 1 5 n ,. 电源 电 压 下 功 耗 为 3 芯 . 7 m 3 3V r 3mw , 试 表 测 明 此 接 口传 输 速 率 达 到 1Gb s /。 关 键 词 : 电压 差分 信 号传 输 ; 速 接 口 ; 送器 ; 收 器 低 高 发 接 中 图 分 类 号 : N4 2 T 3 文献标识码 : A 文 章 编 号 :0 03 1 (0 0 O 一1 90 1 0— 8 9 2 1 ) 1O 1—5

LVDS的接口电路设计

第27卷 第5期 武汉理工大学学报・信息与管理工程版 Vol .27No .52005年10月 JOURNAL OFWUT (I N FORMATI O N &MANAGE MENT ENGI N EER I N G ) Oct .2005文章编号:1007-144X (2005)05-0189-04收稿日期:2005-05-15.作者简介:彭 勇(1982-),男,山东滕州人,武汉理工大学信息工程学院硕士研究生.基金项目:湖北省自然科学基金资助项目(2004ABA045).LVDS 的接口电路设计彭 勇,黄秋元(武汉理工大学信息工程学院,湖北武汉430070)摘 要:LVDS 是一种小振幅差分信号技术,使用这种技术传输速率可以达到数百兆,甚至更高;LVDS 具有更低的功耗、更好的噪声性能和更可靠的稳定性。

简要地介绍了LVDS 的原理及优势,分析了LVDS 接口设计要注意的问题,着重研究了LVDS 与LVPECL 、C ML 间的接口设计;同时给出了不同耦合方式下的电路设计图。

关键词:LVDS;C ML;LVPEC L;直流耦合;交流耦合中图法分类号:T N75 文献标识码:A1 引 言对于高速电路,尤其是高速数据总线,常用的器件一般有ECL 、BT L 和GT L 等。

这些器件的工艺成熟,应用也较为广泛,但都存在一个共同的弱点,即功耗大。

此外,采用单端信号的BT L 和GT L 器件,电磁辐射也较强。

目前,NS 公司率先推出的C MOS 工艺的低电压差分信号器件,即LVDS 给了人们另一种选择。

2 L VD S 技术简介LVDS (Low Voltage D ifferential Signaling )是一种小振幅差分信号技术,使用非常低的幅度信号(约350mV )通过一对差分PCB 走线或平衡电缆传输数据。

它允许单个信道传输速率达到每秒数百兆比特,其特有的低振幅及恒流源模式驱动只产生极低的噪声,消耗非常小的功率。

一种lvds接口电路设计与实现

一种lvds接口电路设计与实现LVDS,即低电压差分信号,是一种传输高速数字信号的技术,在大容量数据传输领域得到广泛应用。

其特点是高速、低功耗、抗干扰能力强等,因此在液晶显示器、图像处理、医疗设备等领域得到了广泛应用。

本文将介绍一种LVDS接口电路的设计与实现,旨在为读者提供一种实用性强、性能稳定的电路设计方法。

一、设计原理本电路采用FPGA控制器与LVDS转换芯片结合的方式,实现了高速信号的传输和转换。

其主要原理如下:1. FPGA控制器生成高速数据信号本电路采用FPGA控制器作为数据信号发生器,提供高速数据信号作为输入信号。

在FPGA中,可以通过VHDL或Verilog语言实现高速数据发生器的设计。

产生的高速数据信号通过输出端口输出到LVDS转换芯片的输入端口。

2. LVDS转换芯片将信号转换为LVDS格式LVDS转换芯片是本电路必不可少的关键部件,它可以将FPGA输出的高速数据信号转换为LVDS格式的差分信号。

LVDS信号由一对反向的信号线组成,分别为正向传输线和反向传输线,通过大小电流的差分信号来传输数据。

LVDS信号特点是传输速率高、功耗低、抗干扰能力强等。

3. LVDS差分信号在接收端恢复为原信号在接收端,又通过LVDS接收芯片对差分信号进行解码,恢复出原始信号。

接收端的LVDS接收芯片与发射端的LVDS转换芯片需要匹配,以确保差分信号的传输质量和可靠性。

二、硬件设计1. FGA控制器的选型与设计在本电路中,FPGA控制器作为高速数据信号发生器,需选择具有高速IO接口、低功耗、可编程性好的器件。

目前在市场上常见的FPGA控制器系列有Xilinx Virtex、Spartan、Artix、Kintex等,以及ALTERA的Cyclone、Stratix等等。

具体在设计过程中,要根据自身需要选择适合的FPGA控制器。

本设计选用Xilinx Spartan-6系列的FPGA器件,其主要特点如下:(1)高速IO引脚数量多,速度快:支持高达3.2Gbps的数据传输速率,单向IO引脚数量高达830个,双向IO引脚数量高达384个。

lvds液晶屏幕接口详解完整版

l v d s液晶屏幕接口详解标准化管理处编码[BBX968T-XBB8968-NNJ668-MM9N]1.LVDS输出接口概述液晶显示器驱动板输出的数字信号中,除了包括RGB数据信号外,还包括行同步、场同步、像素时钟等信号,其中像素时钟信号的最高频率可超过28MHz。

采用TTL接口,数据传输速率不高,传输距离较短,且抗电磁干扰(EMI)能力也比较差,会对RGB 数据造成一定的影响;另外,TTL多路数据信号采用排线的方式来传送,整个排线数量达几十路,不但连接不便,而且不适合超薄化的趋势。

采用LVDS输出接口传输数据,可以使这些问题迎刃而解,实现数据的高速率、低噪声、远距离、高准确度的传输。

那么,什么是LVDS输出接口呢LVDS,即Low Voltage Differential Signaling,是一种低压差分信号技术接口。

它是美国NS公司(美国国家半导体公司)为克服以TTL电平方式传输宽带高码率数据时功耗大、EMI电磁干扰大等缺点而研制的一种数字视频信号传输方式。

LVDS输出接口利用非常低的电压摆幅(约350mV)在两条PCB走线或一对平衡电缆上通过差分进行数据的传输,即低压差分信号传输。

采用LVDS输出接口,可以使得信号在差分PCB线或平衡电缆上以几百Mbit/s的速率传输,由于采用低压和低电流驱动方式,因此,实现了低噪声和低功耗。

目前,LVDS输出接口在17in及以上液晶显示器中得到了广泛的应用。

2.LVDS接口电路的组成在液晶显示器中,LVDS接口电路包括两部分,即驱动板侧的LVDS输出接口电路(LVDS发送器)和液晶面板侧的LVDS输入接口电路(LVDS接收器)。

LVDS发送器将驱动板主控芯片输出的17L电平并行RGB数据信号和控制信号转换成低电压串行LVDS信号,然后通过驱动板与液晶面板之间的柔性电缆(排线)将信号传送到液晶面板侧的LVDS接收器,LVDS接收器再将串行信号转换为TTL电平的并行信号,送往液晶屏时序控制与行列驱动电路。

lvds液晶屏幕接口详解51276

1.LVDS输出接口概述液晶显示器驱动板输出的数字信号中,除了包括RGB数据信号外,还包括行同步、场同步、像素时钟等信号,其中像素时钟信号的最高频率可超过28MHz。

采用TTL接口,数据传输速率不高,传输距离较短,且抗电磁干扰(EMI)能力也比较差,会对RGB数据造成一定的影响;另外,TTL 多路数据信号采用排线的方式来传送,整个排线数量达几十路,不但连接不便,而且不适合超薄化的趋势。

采用LVDS输出接口传输数据,可以使这些问题迎刃而解,实现数据的高速率、低噪声、远距离、高准确度的传输。

那么,什么是LVDS输出接口呢?LVDS,即Low Voltage Differential Signaling,是一种低压差分信号技术接口。

它是美国NS公司(美国国家半导体公司)为克服以TTL电平方式传输宽带高码率数据时功耗大、EMI电磁干扰大等缺点而研制的一种数字视频信号传输方式。

LVDS输出接口利用非常低的电压摆幅(约350mV)在两条PCB走线或一对平衡电缆上通过差分进行数据的传输,即低压差分信号传输。

采用LVDS输出接口,可以使得信号在差分PCB线或平衡电缆上以几百Mbit/s的速率传输,由于采用低压和低电流驱动方式,因此,实现了低噪声和低功耗。

目前,LVDS输出接口在17in及以上液晶显示器中得到了广泛的应用。

2.LVDS接口电路的组成在液晶显示器中,LVDS接口电路包括两部分,即驱动板侧的LVDS输出接口电路(LVDS发送器)和液晶面板侧的LVDS输入接口电路(LVDS接收器)。

LVDS发送器将驱动板主控芯片输出的17L电平并行RGB数据信号和控制信号转换成低电压串行LVDS信号,然后通过驱动板与液晶面板之间的柔性电缆(排线)将信号传送到液晶面板侧的LVDS接收器,LVDS接收器再将串行信号转换为TTL电平的并行信号,送往液晶屏时序控制与行列驱动电路。

图1所示为LVDS接口电路的组成示意图。

图1 LVDS接口电路的组成示意图在数据传输过程中,还必须有时钟信号的参与,LVDS接口无论传输数据还是传输时钟,都采用差分信号对的形式进行传输。

基于VLSI的高速LVDS接口设计

26卷 第11期2009年11月微电子学与计算机M ICROEL ECTRON ICS &COMPU TERVol.26 No.11November 2009收稿日期:2008-11-24基于VL SI 的高速L VDS 接口设计赵耀华,陆铁军,王宗民(北京微电子技术研究所,北京100076)摘 要:LVDS 接口电路是高速数据转换芯片重要模块之一,通常采用的LVDS 接口电路设计方法存在着设计成果不能重复利用的弊端.而且目前已经提出的接口电路结构也不方便电路的可重配置.为了更好地在不同系统中重复利用已经设计好的单元,提出一种通用的且大部分参数可调节的LVDS 接口电路.接收电路和驱动电路的设计和仿真都是基于TSMC 的0.25μmCOMS 工艺库,且能封装成模拟IP 模块以便于在各种大型电路系统(如:DAC 、ADC )的设计过程的直接调用.仿真结果表明该电路能够工作在500MHz 时钟频率下而且满足IEEE 1596.3接口标准.关键词:LVDS 接口;可重配置设计;高速DAC 设计中图分类号:TN47 文献标识码:A 文章编号:1000-7180(2009)11-0078-04High 2Speed L V DS R eceiver and Driver Designed for V LSIZHAO Yao 2hua ,L U Tie 2jun ,WAN G Z ong 2min(Beijing Microelectronics Technology Institute ,Beijing 100076,China )Abstract :LVDS interface circuits have become an important part of high 2speed data 2conversion ICs.The common design of the LVDS interface circuits has the disadvantage that the design can not be reused.The previously reported LVDS cir 2cuit architecture is not suitable for reconfiguration.For the purpose of reusing the same design in different system ,a uni 2versal LVDS interface circuit is presented here and the most of the parameters are variable.Both receiver and driver aredesigned in 0.25μm standard CMOS technology and can be packed as analog IP and embedded in many kinds of systems such as ADC DAC etc.The results show that circuits can be operated up to 500MHz and fully compatible with the IEEE 1596.3standard.K ey w ords :LVDS interface ;reconfigurable design ;high 2speed DAC design1 引言随着CMOS 工艺的发展,使得芯片内部的工作频率越来越高,因此如何实现数据在芯片与芯片之间的高速数据传输成为高速数据处理芯片发展必须解决的问题.LVDS 接口的出现提供了一个用于芯片与芯片之间点对点数据高速传输的解决方案[122].低电压差分信号(LVDS )传输允许每个信道以极高频率工作从而达到很高的数据传输速率,与此同时在功耗、抗干扰性等方面LVDS 也有着其他接口所没有的优势.与一线接口模式所不同的是,LVDS 采用的双线低压互补传输信号(见图1),通过一个驱动器和接收器就能高速地在两个芯片之间进行数据传输.这样能够降低功耗和增强抗干扰能力,同时对其他模块的影响也要小.正是因为上述优点使得LVDS 的应用越来越广泛.文献[3]中提出一种用于ADC 中的低功耗LVDS 驱动器,但是其复杂性不适合集成到其他的系统中.文中提出便于集成到DAC 或ADC 等系统中的LVDS 接收器和驱动器.与文献[4]中所提出的驱动器相对比,在参数调节方面更加灵活,而且应用低功耗模式.这样就形成了完整的用于芯片之间的高速数据传输的解决方案.图1 LVDS 接口结构原理图2 LVDS 接收电路的实现接收电路主要的功能是接收LVDS 信号并将低摆幅(350mV )的差分信号转换成标准的CMOS 信号提供给后级电路.文献[5]中提出了一种用于平板显示器(FPD )的接收电路,由于平板显示对时序的严格要求,该接收电路中包含了复杂的用于满足时序要求的子电路,比如PLL 、VCO 等.文献[6]中提出了更加简单的接收电路,通过利用套筒式放大器来对输入的差分信号进行复原,但是这种电路对电源电压的要求较高,不能应用在低压电路中.考虑到后端版图的设计和集成,文中将接收电路分成两个级(见图2).第一级为预处理模块,第二级为信号转换模块,考虑到LVDS 接口应用往往是多个通道,比如14位DAC 则需要14路的接收器,通过多级设计,可以将第一级布局在芯片的外围的管脚附近,而多个第二级则集中布局在芯片的内部,从而达到降低系统失调和减少梯度误差的目的.图2 LVDS 接收器结构示意图第一级的电路如图3所示.该部分的作用是提供ESD 保护和实现输入电阻调节,通过对控制信号CR T 1,CR T 2,CR T 3的选通和关断来确定接入电路的电阻,从而使输入级在不同的电流源驱动情况下为下一级提供一个合适的偏置电压,这样能够提高该电路的应用场合.第二级如图4所示,该模块主要完成将低压差分信号转换成CMOS 信号.该模块主要是由两级比较器组成.比较器的工作可以分成复位和产生两个阶段.复位阶段比较器清除原来的状态,为比较微小信号做好准备.信号的恢复和输出是在比较器的产生阶段.CR T 控制着比较器的复位,M1,M2,M3,M4组成第一级比较器,M11,M12,M13,M14组成图3 接收器第一级电路结构了第二级比较器,为了能提升比较器的工作频率,在第二级的比较器加入正反馈管M9,M10.因此在设计该部分电路时,为了保持高匹配性,比较器的输入管M1,M2,M13,M14尺寸要选得足够大,而且在版图设计时要充分利用对称性来消除梯度误差.控制管M5,M6,M15尺寸的选择则要小得多,偏置管M7,M8和正反馈管M9,M10的尺寸选择要注意以确保电路能够正常工作且不产生自激.图4 接收器第二级电路结构3 LVDS 驱动电路的实现LVDS 驱动电路的主要作用是完成从CMOS 信号到LVDS 信号的转换.图5给出一种典型的LVDS驱动器.根据LVDS 信号标准,差分信号的共模电平为1.25V.如图5所示V cm 确定了输出差分信号的共97 第11期赵耀华,等:基于VL SI 的高速LVDS 接口设计图5 典型的LVDS 驱动电路结构模电平.I b 和电阻值确定了差分信号的摆幅.CMOS信号V in +和V in -(V in +的互补信号)通过控制电流I b 的流向从而转化成相应的LVDS 信号.文献[7]提出一种能够用于低压的LVDS 驱动器,但不易通过参数调节应用到其他系统中.文中驱动电路如图6所示,按功能可将其分成三个模块.一为转换模块,通过利用典型的转换电路进行电平转换.二为共模电平调节和产生模块,通过利用差分放大器及负反馈确保了V bais 2为输出的共模电平.三为功耗调节模块,通过控制信号CR T-1能够将模块一和模块二全部关断,从而达到降低功耗的目的.通过上述结构能让该模块参数容易调节且可重配置性好.在进行该部分电路设计的时候,补偿电容C c 的大小应该仔细计算和仿真.M21和M23组成AB 类输出级,这样的输出级在对电源电压有一定的要求.要是应用在低压的场合,可以对输出级进行适当的修改.电路的关键管如M1,M2,M4,M5,M20,M21,M22,M23的宽长比在设计时可以取得相对大一些.图6 LVDS 驱动器电路结构图 图7给出LVDS 接收器和驱动器版图在芯片内的布局,其中接收器的第一级和驱动器的版图放置在靠近管脚的位置,而每一个接收器的第二级都集中布局在版图的中间以抵消误差.4 电路仿真结果上述的接收器和驱动器的设计和仿真都是基于TSMC 3.3V/2.5V 0.25μm CMOS 工艺,所有仿真结果都是由仿真工具SPECTRE 在温度为27℃的条件下给出.图8给出当输入信号为标准的LVDS 差分信号时LVDS 接收器的输出波形.图8(a )为传输速率500Mb/s时输入信号的上升沿和下降沿皆图7 LVDS 模块应用版图布局结构图8微电子学与计算机2009年图8 接收器在不同传输速率下的波形为0.2ns 时接收器的输出波形.图8(b )为传输速率1Gb/s 时输入信号的上升沿和下降沿皆为0.1ns 时接收器的输出波形.图9给出了驱动电路在3.3V 电源电压输出LVDS 信号的眼图.图9(a )给出信号传输速率在500Mb/s 时的眼图,图9(b )给出了信号传输速率在1Gb/s 时的眼图.两者输入皆为上升沿和下降沿0.2ns 的标准CMOS 信号.从图中可以看出输出信号的共模电压为1.2V 、摆幅为350mV.图9 驱动器在不同速率下产生的波形5 结束语文中提出一种新的完整的LVDS 接口电路.针对目前LVDS 接口电路在设计方面存在的缺陷和不足,重点放在电路的可重配置性和可重复利用性上.电路的性能通过仿真完全满足IEEE 1596.3标准.通过控制开关对电路参数的调节可以使电路在不同的环境下工作.这样在大的电子系统如DAC 或者ADC 的设计过程中就可以只须做少数的修改直接调用该模块,从而减少一些重复的设计工作,加快设计过程.该电路已经应用在一款高速DAC 的设计中.参考文献:[1]IEEE Standard for Low 2voltage differential signals (LVDS )for scalable coherent interface[S].IEEE press ,1996.[2]ANSI/TIA/EIA Standard.TIA/EIA 2644,Electrical char 2acteristics of low 2voltage differential 2signaling interface cir 2cuits[S].National Semiconductor Corp.,1996.[3]Qin Tang ,Qin Y in ,Jian 2hui Wu.Low power LVDS driv 2er used in ADC systems[C ]//8th Intemational conference on S olid -state and integrated circuit technology proceed 2ings.Shanghai :IEEE press ,2006:1664-1666.[4]K oh Chin Y eong ,Ma Fan Yung ,K oh Tee Peng ,et al.1.2Gbps LVDS interface [C ]//IEEE International Sympo 2sium on Integrated Circuits.Rio de Janeiro :IEEE press ,2007:328-385.[5]Kwan -Woo Y oo ,Jeong Beom K im.Design of a high -speed LVDS I/O interface using telescopic amplifier [C ]//20068th Integrated Circuit on S olid -State and Integrated Circuit Technology Proceedings.Shanghai :IEEE press ,2006:1987-1989[6]Mingdeng Chen ,Jose Silva -Martinez ,Michael Nix ,etal.Low -voltage low -power LVDS drivers [J ].IEEE S olid -State Circuits ,2005,40(2):115-119.[7]张家川,刘伯安.高速多电平LVDS 收发器设计[J ].微电子学与计算机,2007,24(4):69-75.作者简介:赵耀华 男,(1986-),硕士研究生.研究方向为高速高精度DAC 转换器.18 第11期赵耀华,等:基于VL SI 的高速LVDS 接口设计。

LVDS接口设计

LVDS接⼝设计1 LVDS概述LVDS(Low Voltage Differential Signaling)是⼀种⼩振幅差分信号技术,它使⽤⾮常低的幅度信号(100Mv~450mV)通过⼀对平⾏的PCB⾛线或平衡电缆传输数据。

在两条平⾏的差分信号线上流经的电流及电压振幅相反,噪声信号同时耦合到两条线上,⽽接受端只关⼼两信号的差值,于是噪声被抵消。

由于两条信号线周围的电磁场也相互抵消,故差分信号传输⽐单线信号传输电磁辐射⼩得多。

此外,该传输标准采⽤电流模式驱动输出,不会产⽣振铃和信号切换所带来的尖峰信号,具有良好的EMI特性。

由于LVDS差分信号技术降低了对噪声的关注,所以可以采⽤较低的信号电压幅度。

这个特性⾮常重要,它使提⾼数据传输率和降低功耗成为可能。

低驱动振幅意味着数据可更块地反转。

由于驱动器是恒流源模式,功耗⼏乎不会随频率⽽变化,⽽且单路的功耗⾮常低(LVDS25标准2mAx250mV=0.5mW)。

因此,采⽤这种技术后,只要保证⼀对平⾏传输线的长度⾜够⼀致,并在接受端提供良好的匹配端接阻抗技术,以减⼩反射信号的产⽣,就可以提供⾮常⾼的数据传输率。

⽬前,不⽤经⾏复杂和特殊的处理,提供840MHz的数据传输速率已经⾮常容易。

由于LVDS具有这些优良的特性,使得其应⽤越来越普及。

特别是在器件与器件之间以及器件与板级之间的⾼速串⾏数据通信中,已作为⾸选的标准。

⽬前,Xilinx FPGA的每个输⼊输出引脚都⽀持这种信号标准。

2 LVDS的使⽤LVDS的发送和接受通常为点到点结构,如下图所⽰:在芯⽚与芯⽚之间交换数据时,传统的应⽤是采⽤TTL,LVCMOS等单端接⼝标准,这种通信⽅式不仅易受⼲扰,⽽且数据传输率⽆法提⾼。

如果要提⾼带宽(数据传输速率),必须提供⾜够的数据通道。

这样,不仅提⾼了系统成本,⽽且需要处理复杂和棘⼿的数据同步问题。

然⽽,如果采⽤LVDS标准,可有效地解决这些问题。

实现的⽅法是,利⽤可编程逻辑器件的特性,将寄存器的数据输出经过串化处理,并由LVDS接⼝输出,在接受端再将数据利⽤解串流程恢复,如下图所⽰:采⽤上述⽅法处理后,将原有的32条数据线变成了4对差分输出线,并可达到或超过单端输出的带宽,且更容易实现,功率更低。

LVDS接口电路及设计

LVDS接口电路及设计摘要:本文介绍了LVDS接口的基本原理和电特性,通过与其他接口技术进行对比,反映出LVDS接口在高速数据传输应用方面的优势,并结合实例指出了LVDS接口电路的设计原则。

关键词:低电压差分信号;电压摆幅;接口;驱动器;接收器概述LVDS接口又称RS-644总线接口,是20世纪90年代才出现的一种数据传输和接口技术。

LVDS即低电压差分信号,这种技术的核心是采用极低的电压摆幅高速差动传输数据,可以实现点对点或一点对多点的连接,具有低功耗、低误码率、低串扰和低辐射等特点,其传输介质可以是铜质的PCB连线,也可以是平衡电缆。

LVDS在对信号完整性、低抖动及共模特性要求较高的系统中得到了越来越广泛的应用。

目前,流行的LVDS技术规范有两个标准:一个是TIA/EIA (电讯工业联盟/电子工业联盟)的ANSI/TIA/EIA-644标准,另一个是IEEE 1596.3标准。

1995年11月,以美国国家半导体公司为主推出了ANSI/TIA/EIA-644标准。

1996年3月,IEEE公布了IEEE 1596.3标准。

这两个标准注重于对LVDS接口的电特性、互连与线路端接等方面的规范,对于生产工艺、传输介质和供电电压等则没有明确。

LVDS可采用CMOS、GaAs或其他技术实现,其供电电压可以从+5V到+3.3V,甚至更低;其传输介质可以是PCB 连线,也可以是特制的电缆。

标准推荐的最高数据传输速率是655Mbps,而理论上,在一个无衰耗的传输线上,LVDS的最高传输速率可达1.923Gbps。

LVDS接口的原理及电特性一个简单的LVDS传输系统由一个驱动器和一个接收器通过一段差分阻抗为100Ω的导体连接而成,如图1所示。

驱动器的电流源(通常为3.5mA)来驱动差分线对,由于接收器的直流输入阻抗很高,驱动器电流大部分直接流过100Ω的终端电阻,从而在接收器输入端产生的信号幅度大约350mV 。

远程数据传输中并行转串行LVDS接口设计毕业设计说明书

远程数据传输中并行转串行LVDS接口设计目录1 引言 ................................................... 错误!未定义书签。

课题研究背景和意义 ...................................... 错误!未定义书签。

国内外研究现状 .......................................... 错误!未定义书签。

LVDS简介................................................ 错误!未定义书签。

FPGA简介............................................... 错误!未定义书签。

本课题研究内容和安排 .................................... 错误!未定义书签。

2 理论基础 ............................................... 错误!未定义书签。

系统整体结构 ............................................ 错误!未定义书签。

LVDS原理............................................... 错误!未定义书签。

FPGA结构和特点......................................... 错误!未定义书签。

FPGA的结构.............................................. 错误!未定义书签。

FPGA的大体特点.......................................... 错误!未定义书签。

并行接口和串行接口 ...................................... 错误!未定义书签。

LVDS与PECL、LVPECL、CML、RS-422及单端器件之间的接口设计

LVDS 与 PECL 、LVPECL 、CML 、RS-422 及单端器件之间的接口设计图 1 : PECL/LVPECL 至U LVDS 的接口电路。

低电压差分信号(LVDS )在对信号完整性、低抖动及共模特性要求较高的系统中 得到了广泛的应用。

本文针对 LVDS 与其他几种接口标准之间的连接,对几种 典型的LVDS 接口电路进行了讨论。

如今对高速数据传输的需求正推动着接口技术向高速、 串行、差分、低功耗以及 点对点接口的方向发展,而低电压差分信号(LVDS )具备所有这些特性。

Pericom 半导体公司可提供多种LVDS 驱动器、接收器以及时钟分配缓冲器芯片。

本文将讨论LVDS 与正射极耦合逻辑(PECL )、低电压正射极耦合逻辑(LVPECL ) >电路模式逻辑(CML )、RS-422以及单端器件之间采用电阻网络的接 口电路设计。

图 2 :调整电路,R1 = (VR1 + R1a) , R2 = (VR2 + R2a) , R3 = (VR3 + R3a)。

图一% !PEC-_f< LV=ECL^3.3\':因为各厂商所提供的驱动器与接收器的结构不一样,所以本文提供的电路仅供设计时参考。

设计者需要对电路进行验证,并调节电路中的电阻和电容值以获得最佳性能。

电阻分压器的计算表1列出了本文所采用的不同接口标准的工作电压。

为使PECL和LVPECL接口标准能与Pericom公司的LVDS器件进行连接,采用电阻分压器在不同电压之间切换。

图3: PECL至U LVDS的接口电路图1所示的接口电路采用由电阻R1、R2和R3组成的电阻分压器。

R1、R2与R3的电阻值计算如下:R1||(R2 + R3) = Z [(R2 + R3)/(R1 + R2 + R3)] = Va/VccR3/(R1 + R2 + R3) = Vb/Vcc其中:Va为SEPC或LVPECL的偏置电压Vos,分别为3.6V和2.0V ;Vb为LVDS的偏置电压Vos,等于1.2V ;图4: LVDS至U PECL的接口电路图四Z为线路阻抗,等于50 Q。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

LVDS的接口电路设计

丁宏伟

摘要:LVDS是一种小振幅差分信号技术,使用这种技术传输速率可以达到数百兆,甚至更高; LVDS具有更低的功耗、更好的噪声性能和更可靠的稳定性。

简要地介绍了LVDS的原理及优势,分析了LVDS接口设计要注意的问题。

关键词:LVDS;接口;PCB

中图分类号:TP336 文献标志码:A

引言

LVDS,即Low Voltage Differential Signaling,是一种低压差分信号技术接口。

它是美国NS公司(美国国家半导体公司)为克服以TTL电平方式传输宽带高码率数据时功耗大、EMI电磁干扰大等缺点而研制的一种数字视频信号传输方式。

LVDS这种技术的核心是采用极低的电压摆幅(约350 mV)高速差动传输数据,具有低功耗、低误码率、低串扰和低辐射等特点,其传输介质可以是铜质的PCB连线,也可以是平衡电缆。

LVDS在对信号完整性、低抖动及共模特性要求较高的系统中得到了越来越广泛的应用。

1 LVDS驱动器和接收器工作原理

LVDS定义在2个国际标准中: IEEE P1596.3 (1996 年3 月通过) , 主要面向SC I ( ScalableCoherent Interface) ,定义了LVDS的电特性,还定义了SC I协议中包交换时的编码; ANSI /EIA -644 (1995年11月通过) ,主要定义了LVDS的电特性,并建议了655 Mb / s的最大速率和1. 823Gb / s的无失真媒质上的理论极限速率。

在2个标准中都指定了与物理媒质无关的特性,这保证了LVDS能成为多用途的接口标准[ 1]。

如图1所示,LVDS电路由驱动器和接收器以及终端匹配电阻组成。

M1、M2、M3和M4是尺寸、工艺相同的NMOS管开关。

驱动器的输出接在阻值为100Ω的终端电阻上,构成回路。

驱动器工作时,NMOS开关M1和M4以及M2和M3在CMOS信号的作用下轮流导通和截止,在输出端产生±3.5 mA的回路电流。

绝大部分驱动电流将流经100Ω的终端电阻,并在接收器输入端产生大约350 mV的压降。

当驱动状态反转时,流经电阻的电流方向改变,于是在接收端产生了一个有效“0”或“1”的逻辑状态。

从而把一个CMOS信号转换成了LVDS[ 2]。

图1 LVDS电路的工作示意图

在数据传输过程中,还必须有时钟信号的参与,LVDS接口无论传输数据还是传输时钟,都采用差分信号对的形式进行传输。

所谓信号对,是指LVDS接口电路中,每一个数据传输通道或时钟传输通道的输出都为两个信号(正输出端和负输出端)。

LVDS的驱动和接收不依赖于供电规格,从而可以保持同样的信号电平和性能。

LVDS的信号电平只有PECI 电压摆幅的一半,是TTI /CMOS电平的1/1O。

LVDS提供低功耗的解决方案,其负载终端电阻的功耗仅为1.2 mW。

电流驱动模式也降低了系统的功耗。

2 LVDS的应用模式

2.1 单向点对点(point-to-point)

这是典型的应用模式,每个点到点连接的差分对由一个驱动器、互连器和接收器组成。

驱动器和接收器主要完成TTL信号和LVDS信号之问的转换。

互连器包含电缆、PCB上差分导线对以及匹配电阻。

单向点对点应用模式是芯片问、插件问、机架问通讯的理想接口。

2.2 双向点对点

能通过一对双绞线实现双向的半双工通信。

可以由标准的LVDS的驱动器和接收器构成。

但更好的办法是采用总线LVDS驱动器,即BLVDS,这是为总线两端都接负载而设计的。

2.3 多分支形式(multidrop)

即一个驱动器连接多个接收器。

当有相同的数据要传给多个负载时,可以采用这种应用形式。

2.4 多点结构(multipoint)

此时多点总线支持多个驱动器,也可以采用BLVDS驱动器。

它可以提供双向的半双工通信,但是在任一时刻,只能有一个驱动器工作。

因而发送的优先权和总线的仲裁协议都需要依据不同的应用场合,选用不同的软件协议和硬件方案[ 3 ]。

3 LVDS系统的设计

了解LVDS接口特性后,下面的问题就是如何在设计中应用好LVDS接口产品,充分发挥其技术优点,优化系统设计。

3.1 PCB板的设计

PCB布线总的原则是:阻抗要匹配。

这是非常重要的,差分阻抗的不匹配会产生反射,会减弱信号并增加共模噪声,线路上的共模噪声将得不到差分线路磁场的抵消而产生电磁辐射。

以下是PCB板设计中需注意的问题:

a.至少用4层PCB板,将LVDS信号、地、电源、TTI 信号分层布局;

b.使TTL信号和LVDS信号相互隔离,否则TTL可能会耦合到LVDS线上,最好将TTL和LVDS信号放在由电源、地层隔离的不同层上;

c.保持发送器和接收器尽可能靠近接插件,连线长度愈短愈好[(小于37.6 ram(1.5英寸)],以保证板上噪声不会被带到差分线上,而且避免电路板及电缆线问的交叉EMI干扰;

d.旁路每个LVDS器件,分布式散装电容或表贴电容放在尽量靠近电源和地线引脚处;

e.电源层和地层应使用粗线,保持PCB地线层返回路径宽而短;

f.终端负载用100Ω表贴电阻靠近接收器输入端来匹配传输线的差分阻抗,终端电阻到接收器输入端的距离应小于7 mm;

g.将所有空闲引脚开路(悬空)。

3.2 差分线的设计

a.使用与传输媒质的差分阻抗和终端电阻相匹配的受控阻抗线,并且使差分线对离开集成芯片后立刻尽可能地相互靠近(距离小于10 mm),这样能减少反射并能确保耦合到的噪声为共模噪声;

b.使差分线对的长度相互匹配,以减少信号扭曲,防止引起信号问的相位差而导致电磁辐射;

c.尽量减少过孔和其它会引起线路不连续性的因素;

d.避免使用90°的走线,这将导致阻值的不连续。

3.3 电缆和接插件的选择

a.就减少噪声和提高信号质量而言,平衡电缆(如双绞线对)比非平衡电缆好。

当电缆长度小于0.5 m 时,大部分电缆都能有效工作,距离在0.5 m~10 m之问时,CAT 3(Category 3)双绞线对效果好,距离大于10 m并且要求高速率时,建议使用CAT 5双绞线对。

b.接插件一般选择标准连接器,在连接器上差分信号通常连接在一行中靠近的两个连接脚上。

4 结语

总之,LVDS数据传输标准比传统的RS-232、RS-422等标准有很大的优越性。

用LVDS技术来完成数据传输,将会降低系统设计的复杂度,使系统有很高的可靠性、高数据率、低噪声、低电磁辐射和低成本。

参考文献:

[ 1 ] 赵忠文,曾岱,熊伟. LVDS技术分析和应用设计[ J ]. 指挥技术学院学报, 2001, 12 (6) : 1 - 2.

[ 2 ] 宋正勋,谭宝华. 低压差分信号技术[ J ]. 长春光学精密机械学院学报, 2000, 23 (2) : 2 - 3.

[ 3 ] Stephen Kempainen. Low Voltage Differential Signaling[ J ]. Insight, 2000, 5 (2) : 15 - 20.。