微处理器结构与设计-第5次课-2013-03-27_846007182

微处理器结构与设计-第6次课-2013-04-03_71708531

• ALU具有4个控制信号,见下表, • 那么由谁来产生这4 bit的信号呢?见下页

4 ALU Operation

ALU 控制信号 0000 0001 0010 0110 0111

0001 (暂不考虑)

功能 AND OR Add (与) (或) (加) ALU Zero

ALU result

Subtract (减) Set_on_less_than

数据存储器和符号扩展单元

要求数据存储器具有读口和写口, 并且需要指定数据单元地址 16位的偏移量需要进行32位扩展 形成数据存储器地址

Sign_extend(offset)+GPR(base)

转移指令地址形成

Beq $t1,$t2,offset

Operation: I: target_offset <--- sign_extend (offset _shifted_2_bit) condition <--- (GPR[rs] = GPR[rt]) I+1: if condition then PC <--- PC + target_offset ( 此时,PC值为指向紧接着branch的下一条指令地址)

– 来自于ALU, R-type指令 如 add r1,r5,r2; – 来自于数据存储器 (D-cache) 例如 Lw 指令

来源多于两个以上, 必须使用多路选择器

11

支持算逻指令和存储器访问指令的数据通路

添加多路选择器后的数据通路 该图可否支持转移指令,为什么?说明原因?

支持转移指令、算逻和存储器访问的数据通路

编码的无关项考虑

• 只有当 ALUop=10时,才考虑用funct field 细分子类 • ALUop编码应该禁止出现11组合,否则会出现混淆的编码 (教材附录C证实C.2 Elaboration) • 事实上,ALUop与funct field 可区分28=256个值 • F5和F4都是10,可作为无关项 (教材P105页编码表可得) • Operation 编码的最高位都是0,也可恒置低,编码时don’t care

微处理器系统结构与嵌入式系统设计ppt课件

A/D 数字 基 带

A/D

数字滤波与控制 系统知识 (硬件与软件)

电路设计知识 (DAC、ADC 等)

制造工艺知识 (90nm, 65nm, 45nm)

22 .

晶圆工艺知识 (300mm 晶圆)

片上网络(NOC) 技术

P处理器 M存储器

C缓存 rni网络接口 S交换开关

Dsp核 re可重构逻辑

L专用逻辑

7-8课时

第五章:存储器系统

8-9课时

第六章:输入/输出接口

6-7课时

第七章:ARM微处理器编程模型

4课时

第八章: ARM汇编指令

4-5课时

第九章: ARM程序设计

4-5课时

第十章:基于ARM微处理器的硬件系统设计

3课时

第十一章:基于ARM微处理器的软件系统设计 3课时

第十二章:基于ARM微处理器核的SOC设计

并出现了早期的操作系统。 第三代(1965~1980年)集成电路计算机 以中小规模集成电路为主要部件,内存用磁芯、半导体,外存用磁盘。软件

广泛使用操作系统,产生了分时、实时等操作系统和计算机网络 第四代(1980年至今)个人计算机 以LSI、VLSI为主要部件,以半导体存储器和磁盘为内、外存储器。在软件

章

✓ 片上多核处理器(CMP)

✓ 流处理器(Stream Processor)

✓ PIM(Processor In Memory)

概

✓ 可重构计算处理器

述

1.4 嵌入式系统(了解)

✓ 嵌入式系统的概念

✓ 嵌入式系统的特点

✓ 嵌入式系统中的处理器

✓ 嵌入式系统的组成

✓ 嵌入式系统的发展现状与趋势

✓ 学习嵌4入1.式系统的意义

《微处理器 》课件

按寻址方式分类

根据指令的寻址方式,可以将指令集分为立即寻址 、寄存器寻址、内存寻址和位寻址等。

按长度分类

根据指令的长度,可以将指令集分为单字节 指令、双字节指令、三字节指令和四字节指 令等。

指令集实现方式

硬编码实现

通过硬件电路实现指令集中的所有指令,这种方 式速度快但灵活性差。

微编程实现

通过微程序控制单元实现指令集中的所有指令, 这种方式灵活性好但速度较慢。

《微处理器》PPT课件

目 录

• 微处理器简介 • 微处理器的体系结构 • 微处理器的指令集 • 微处理器的编程模型 • 微处理器的性能优化 • 微处理器的发展趋势

01

微处理器简介

微处理器的定义

微处理器是一种集成电路芯片, 它包含了计算机的中央处理器(

CPU)的主要功能。

微处理器是计算机系统的核心部 件,负责执行指令和处理数据。

并行计算技术

总结词

并行计算技术是利用多个处理器同时 执行多个任务,以提高整体计算性能 。

详细描述

并行计算技术通过将一个任务分解成 多个子任务,并分配给多个处理器同 时执行,大大加快了计算速度。这种 技术广泛应用于高性能计算、云计算 和大数据等领域。

低功耗技术

总结词

随着移动设备和便携式设备的普及,低功耗技术已成为微处理器发展的另一个重要趋势 。

微处理器的应用领域

01

02

03

04

计算机领域

个人电脑、服务器、超级计算 机等都离不开微处理器的支持

。

通信领域

手机、路由器、交换机等通信 设备中都有微处理器的身影。

工业控制领域

自动化生产线、机器人、智能 家居等都需要微处理器进行控

微处理器系统结构课程介绍

04 微处理器的工作原理

微处理器的时钟系统

时钟信号

时钟信号是微处理器中最重要的 信号之一,它控制着微处理器的

工作节奏和同步操作。

时钟源

时钟源是产生时钟信号的源头,通 常由晶体振荡器或石英振荡器提供 稳定的时钟频率。

时钟分频与倍频

为了满足微处理器内部不同模块的 工作需求,时钟信号需要进行分频 或倍频处理,以提供合适的时钟周 期。

微处理器的发展历程

第一代微处理器

第二代微处理器

第三代微处理器

第四代微处理器

64位微处理器

1971年,Intel公司推出 了第一款商用微处理器 4004,它由2300个晶体 管组成,字长4位,标志 着微处理器时代的开始。

随着技术的不断发展,8 位微处理器如Z80和 8080等相继问世,广泛 应用于家用和工业控制 等领域。

微处理器的应用领域

工业控制

微处理器可以用于各种工业控 制系统中,如自动化生产线、 智能仪表等。

通信设备

微处理器在通信设备中用于实 现信号处理、调制解调、协议 控制等功能。

计算机系统

微处理器是计算机系统的核心 部件,负责计算机的运算和控 制功能。

汽车电子

现代汽车中广泛应用微处理器 实现发动机控制、安全气囊、 ABS防抱死刹车等功能。

微处理器系统结构课程介绍

目 录

• 课程介绍 • 微处理器基础知识 • 微处理器系统结构 • 微处理器的工作原理 • 微处理器的编程与优化 • 微处理器的发展趋势与未来展望

01 课程介绍

课程目标

掌握微处理器系统结构的基本原理和概念。

理解微处理器内部结构、指令集、存储器层次结 构等关键要素。

培养学生对微处理器系统设计和应用的能力,提 高解决实际问题的能力。

微处理器及其体系结构

21

总线接口部件(Bus Interface Unit—BIU)

BIU指令队列中,若出现一个空字节(8086是两个空字节), 而且EU(执行部件)没有命令BIU对存储器或I/O端口进行访 问,则BIU自动执行总线操作,读出指令并填入指令队列 中,直至满为止(8088是4个字节,8086是6个字节)。

当EU执行完一条指令,就再到BIU的指令队列前部 取出BIU预先读入的指令代码。

若指令队列是空的,则EU处于等待状态;一旦指令 队列中有一条指令,EU立即取出执行。

2020/4/28

第二章 8086/8088微处理器及其体系结构

20

总线接口部件(Bus Interface Unit—BIU)

作用:根据EU的请求,完成CPU与存储器、CPU与 I/O之间的信息传送。

16

1、8086/8088CPU的内部结构(2)

8086/8088CPU内部结构基本相同,有20条外部地址 总线,可以寻址1M内存空间;

8086CPU的内部和外部数据总线均是16位,是典型 的16位微处理器;

8088CPU内部数据总线是16位,外部数据总线是8 位,所以被称为准16位微处理器。

2020/4/28

6

CPU工பைடு நூலகம்方式

1、最小工作方式

系统中只有一个微处理器8088(或8086),所有的 总线控制信号都直接由8088(或8086)产生,这种方式 适合较小规模的应用。

2、最大工作方式

系统中可以只有一个处理器,也可以有两个或以上 的微处理器,其中一个作为主处理器,其他作为后援处 理器,用来协助主处理器处理某些方面的工作,这种方 式是在需要8088构成中等或较大系统。

第二章 8086/8088微处理器及其体系结构

第五章 微处理器.ppt

CISC 结构计算机的缺点

指令的使用频度不均衡 限制了机器速度的进一步提谢您的观赏

19

RISC ---- 简化指令系统计算机

RISC 技术的特征

精简指令集,减少指令的执行周期数 计算机执行程序所需的时间

2)常用来保存计数值,如在移位指令、循环指令和串处理指令中

用作隐含的计数器

DX ---- 1)作为通用寄存器使用;

2)在一些指令中,通常用它来存放数据,所以又称为数据寄存器;

3)在做双字长运算时,将DX和AX组合在一起存放双字长数,用DX

存放高位字;

4)对某些I/O操作时,DX用来存放端口的地址

2019-8-29

第五章 微处理器

2019-8-29

谢谢您的观赏

1

CPU的特点

可以进行算术和逻辑运算 保存少量数据 对指令进行译码并执行规定的动作 与存储器、外设交换数据 提供系统所需要的定时和控制 可以响应其它部件发送过来的中断请求

2019-8-29

谢谢您的观赏

2

CPU的内部结构

算术逻辑部件 ( ALU ) 累加器和通用寄存器组 程序计数器、指令寄存

• 零标志ZF:如果上一条指令的运算结果为0,则此标志位置位ZF=1,否则 ZF=0

• 符号标志SF:若运算结果的最高位(字节的D7位,字的D15位)为1,则 SF=1,否则,SF=0

• 溢出标志OF:若发生算数溢出,即运算结果的长度超过了目的单元的容 量,丢失了有效数字,则OF=1,否则OF=0

• 辅助进位标志AF:又称半进位标志,在字节操作时,低四位相高四位有进 位或借位,自操作时,低位字节向高位字节有进位或借位,则AF=1,否 则AF=0

微处理器的编程结构

高速缓存(Cache):高 速缓存是用于存储经常访 问的数据的快速存储器, 以减少对主存的访问时间。

主存储器(Main Memory):主存储器是 微处理器的主要存储空间, 用于存储程序和数据。

辅助存储器(Secondary Storage):辅助存储器包 括硬盘、固态硬盘(SSD) 等,用于永久存储大量数 据和程序。

微处理器的历史和发展

微处理器的发展始于20世纪70年代 ,当时Intel公司推出了第一款商用 微处理器4004。

随着技术的不断发展,微处理器的性 能和功能得到了极大的提升,同时价 格也逐步降低,使得微处理器在各个 领域得到了广泛的应用。

微处理器的应用领域

微处理器被广泛应用于计 算机、通信、工业控制、 消费电子等领域。

单元测试和集成测试

编写测试用例,对程序模块进行单元测试和 集成测试,确保程序正确性和稳定性。

性能分析和优化

使用性能分析工具,找出程序瓶颈并进行优 化。

05

微处理器编程的未来发 展

新一代微处理器技术

异构计算

通过集成不同类型和功能的处理器,如CPU、GPU、FPGA等, 实现更高效和灵活的计算能力。

输入/输出结构

01

02

03

输入设备

输入设备用于向微处理器 输入数据,如键盘、鼠标、 触摸屏等。

输出设备

输出设备用于将微处理器 的处理结果输出,如显示 器、打印机等。

中断控制器

中断控制器用于管理输入/ 输出设备与微处理器之间 的通信,实现中断处理。

中断和异常处理

中断

中断是输入/输出设备向微处理器发出的请 求信号,用于通知微处理器对某个事件进行 处理。

03

较低。

编程模型的选择

《微处理器》课件

微处理器的新技术与应用

神经网络处理器

针对人工智能和机器学习应用,神经网络处理器能够加速深度学 习算法的运算。

嵌入式系统

微处理器在嵌入式系统中的应用将更加广泛,如智能家居、工业自 动化等领域。

物联网设备

随着物联网的发展,微处理器将应用于更多类型的物联网设备中, 实现设备间的互联互通。

微处理器的未来挑战与机遇

处理器体系结构

处理器核

01

处理器体系结构中的处理器核是微处理器的核心部分,负责执

行指令和处理数据。

核外设备

02

核外设备包括寄存器、高速缓存、总线接口等,用于扩展处理

器核的功能和性能。

处理器优化

03

为了提高微处理器的性能,需要对处理器进行优化,如采用流

水线技术、并行处理技术等。

03

微处理器的指令系统

《微处理器》课件

CONTENTS

• 微处理器概述 • 微处理器的体系结构 • 微处理器的指令系统 • 微处理器的编程模型 • 微处理器的应用开发 • 微处理器的未来发展

01

微处理器概述

微处理器的定义

总结词

微处理器的核心作用

详细描述

微处理器是计算机系统的核心部件,它能够执行程序指令,控制计算机的各个 部分协调工作。

技术创新

随着半导体工艺的物理极限临近,微处理器 设计将面临技术上的挑战,需要寻求新的技 术创新。

安全问题

随着微处理器广泛应用于各个领域,安全问题变得 越来越重要,需要加强安全设计和防护措施。

新市场机遇

随着技术的发展,微处理器将有更多新的应 用领域和市场机遇,如自动驾驶、虚拟现实 等。

谢谢您的聆听

THANKS

开发环境

Intel微处理器第五版课程设计

Intel微处理器第五版课程设计一、课程设计背景随着科技的不断发展,芯片技术的进步也得到了长足的发展,微处理器是计算机系统中最为核心的部件之一。

在计算机科学与技术专业中,微处理器的课程设计已经成为一门重要的课程。

Intel微处理器第五版是微处理器课程教材中的一本重要书籍,通过学习该教材,能够使学生全面了解计算机组成原理、微处理器体系结构和指令系统等基本知识,并且熟练掌握微处理器的芯片设计和程序编写技能。

二、课程设计目标本次课程设计旨在加深学生对Intel微处理器第五版的理解,并通过实践的方式,提高学生的程序设计能力和硬件调试能力。

具体的目标如下:1.全面了解Intel微处理器的体系结构和指令系统2.能够掌握汇编语言程序设计和调试技巧3.能够熟练使用芯片设计工具,进行芯片的设计和调试4.能够设计并实现一个简单的嵌入式系统,并进行功能测试三、课程设计内容1.Intel微处理器第五版理论学习:深入学习计算机组成原理和微处理器的体系结构,以及指令系统的组成和使用。

2.汇编语言程序设计和调试:通过编写各种不同类型的程序,加深理解汇编指令和程序设计的方法,并掌握调试技巧。

3.芯片设计和调试:学习如何使用芯片设计工具,例如EDA、VHDL或Verilog,实现芯片设计和测试。

4.嵌入式系统的设计:通过使用Intel微处理器作为中心处理器,设计一个简单的嵌入式系统,并进行功能测试。

四、课程设计安排本次课程设计共计10周,每周安排如下:第1周•理论课讲解:介绍课程设计的背景、目标和内容,讲解Intel微处理器的体系结构、指令系统和汇编语言等基本知识。

•实践环节:安装相关的软件工具,编写和调试简单的汇编程序。

第2-3周•理论课讲解:讲解芯片设计的相关知识,介绍EDA、VHDL 或Verilog的基本概念和使用方法。

•实践环节:学习使用芯片设计工具,进行芯片设计和调试。

第4-6周•理论课讲解:讲解嵌入式系统的基本知识和设计方法,介绍Intel微处理器的应用。

《微处理器系统结构与嵌入式系统设计》cha

03

学习如何在嵌入式系统中进行

硬件接口编程,如GPIO、 UART、SPI、I2C等

04

掌握嵌入式系统中常见的硬件抽

象层(HAL)和设备驱动程序开

发方法

05

学习如何使用仿真器和调试器

进行硬件调试和性能优化

06

06 微处理器与嵌入式系统的 未来发展

微处理器的发展趋势

高效能

随着技术的进步,微处理 器的处理能力将不断提升, 以满足更高性能计算的需 求。

05 嵌入式系统设计实践

嵌入式系统开发环境搭建

在此添加您的文本17字

总结词:掌握嵌入式系统开发环境搭建的方法和步骤

在此添加您的文本16字

详细描述

在此添加您的文本16字

了解嵌入式系统开发环境的基本组成和要求

在此添加您的文本16字

学习如何安装和配置嵌入式系统开发所需的软件和硬件工具, 如集成开发环境(IDE)、编译器、调试器等

03 微处理器指令集架构

指令集架构的定义与分类

01

总结词

指令集架构是微处理器中用于 执行指令的硬件结构,它定义 了指令集、寄存器、内存寻址 等基本功能。

03

02

总结词

04

详细描述

指令集架构可以分为复杂指令集 计算机(CISC)和精简指令集计 算机(RISC)两类。CISC架构强 调指令的复杂性和功能多样性, 而RISC架构则注重指令的简洁性 和执行效率。

指令集架构的性能评估是衡量其 执行效率的重要指标,包括指令 执行速度、内存访问速度、功耗 等。

详细描述

指令集架构的性能评估通常采用 基准测试程序进行评估,这些程 序通过模拟实际应用场景来测试 微处理器的性能。常见的性能评 估指标包括吞吐量、延迟、功耗 等。

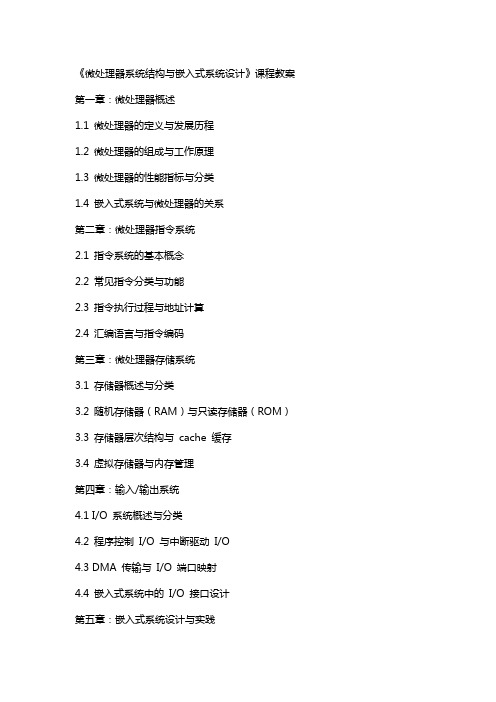

《微处理器系统结构与嵌入式系统设计》课程教案

《微处理器系统结构与嵌入式系统设计》课程教案第一章:微处理器概述1.1 微处理器的定义与发展历程1.2 微处理器的组成与工作原理1.3 微处理器的性能指标与分类1.4 嵌入式系统与微处理器的关系第二章:微处理器指令系统2.1 指令系统的基本概念2.2 常见指令分类与功能2.3 指令执行过程与地址计算2.4 汇编语言与指令编码第三章:微处理器存储系统3.1 存储器概述与分类3.2 随机存储器(RAM)与只读存储器(ROM)3.3 存储器层次结构与cache 缓存3.4 虚拟存储器与内存管理第四章:输入/输出系统4.1 I/O 系统概述与分类4.2 程序控制I/O 与中断驱动I/O4.3 DMA 传输与I/O 端口映射4.4 嵌入式系统中的I/O 接口设计第五章:嵌入式系统设计与实践5.1 嵌入式系统设计流程与方法5.2 嵌入式处理器选型与系统架构设计5.3 嵌入式系统软件设计与开发5.4 嵌入式系统硬件设计与实现第六章:嵌入式系统硬件平台设计6.1 嵌入式系统硬件设计基础6.2 处理器选型与评估6.3 硬件系统架构设计6.4 硬件电路设计与仿真第七章:嵌入式操作系统原理与应用7.1 嵌入式操作系统概述7.2 嵌入式操作系统核心组件7.3 嵌入式操作系统实例分析7.4 嵌入式操作系统应用与开发第八章:嵌入式系统软件开发8.1 嵌入式软件开发概述8.2 嵌入式软件开发工具与方法8.3 嵌入式软件编程实践8.4 嵌入式软件测试与优化第九章:嵌入式系统应用案例分析9.1 嵌入式系统在工业控制中的应用9.2 嵌入式系统在医疗设备中的应用9.3 嵌入式系统在智能家居中的应用9.4 嵌入式系统在物联网中的应用第十章:未来嵌入式系统发展趋势10.1 嵌入式系统技术发展趋势10.2 嵌入式系统在各领域的应用拓展10.3 我国嵌入式系统产业现状与展望10.4 嵌入式系统教育与人才培养重点和难点解析一、微处理器概述难点解析:微处理器的发展历程需要记忆各个重要的时间节点和对应的处理器;组成与工作原理涉及到硬件组成和指令执行过程的理解;性能指标与分类需要理解如何评估处理器的性能以及不同类型处理器的应用场景。

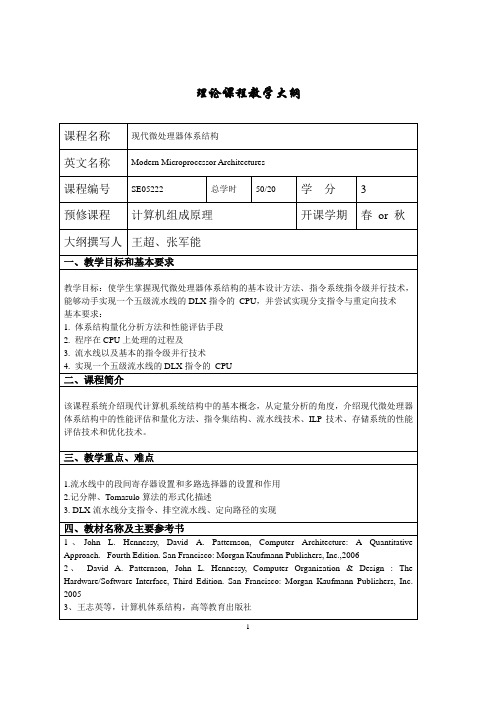

SE05222《现代微处理器体系结构》教学大纲

DLX解决数据相关的定向路径的设计与实现

4

设计型

5

记分牌算法和Tomasulo算法性能测试

4

验证型

三、实验讲义、参考书

实验讲义:由课程老师和助教共同设计

参考书:《计算机系统结构实践教程》张晨曦等清华大学出版社

《计算机体系结构实验》沈立等清华大学出版社

四、院系负责人审批意见

负责人签字:年月日

*实验内容类型:注明该项实验是验证型、开放型、综合型或设计型等。

3、王志英等,计算机体系结构,高等教育出版社

五、课程章节主要内容及学时分配

第零章体系结构概论以及国外对应课程的教学大纲和课程要求2个课时

本章主要介绍体系结构基本概念,以及国外知名大学如Berkeley,Stanford,WISC, MIT和CMU的对应课程的教学大纲和课程要求。旨在激发学生兴趣,并帮助学生找准自己的位置和目标。

内容和要求:掌握指令级并行的目标和原理,了解采用静态调度的方法提升指令并行度的策略,重点掌握记分牌和Tomasulo算法设计方案的异同点和优缺点;

重点:指令级并行概念,记分牌和Tomasulo算法

第五章存储系统

内容和要求:掌握存储层次设计的目标和工作原理;掌握Cache设计的基本方法;了解主存和虚拟存储器的工作原理;

重点:计算机系统指令集结构设计,RISC指令集结构实例

第三章流水线技术

内容和要求:掌握流水线技术的基本原理及其性能评价方法;掌握RISC指令集结构流水线的基本设计方法,并能够从数据相关与控制相关两个方面分析流水线性能,掌握提高流水线性能的软硬件方法。

重点:流水线的基本原理与设计、分析评价方法

第四章指令级并行

重点:存储层次设计的目标和工作原理、Cache查找和替换策略

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

答案

1. 对无符号16位的二进制数M,在Booth编 码的情况下,会产生2M,因此,需要17 位来表示2M。 2. Booth编码第一行部分积需要3个位表示 符号位,最后一行部分积,不需要符号位 ,其它行都需要2位符号位,这就是20位 ,19位,16位的来历。 3. 乘数变成19位,这是Booth编码推导过程 所造成的

微电子学研究所李树国

3、不含浮点指令

23

指令的共同性

• 取指令,送PC值给Memory • 根据指令的内容,读取1个或2个寄存器的 内容 • 除了一条跳转指令J外,其它所有的指令类 在读取寄存器后,都要使用ALU

24

微电子学研究所李树国

指令的不同性

• 使用ALU后,依据指令的不同,而进行不同 的操作,分别是:

sel

clo/z

I-TLB

I-TagComp

31

Din Dout

decode

Add rd, rs,rt ; rd <--rs+rt

CPO

RD A_in Sel B_in

MDU

Dout

(HI,LO) Din

Sel

21 流水线结构示意图

微电子学研究所李树国

MIPS的基本实现

22

微电子学研究所李树国

MIPS 指令核心子集

32

微电子学研究所李树国

指令的周期

• 单周期指令,每一条指令的执行都只需要一个 时钟周期。 • 多周期指令,每条指令需要分成若干个时钟周 期来执行。 • 流水线是一种解决多周期指令的重叠操作技术

33

微电子学研究所李树国

单周期指令的描述

clock cycle 1

IF

DE

EXE

WB

34

微电子学研究所李树国

流水线多周期指令的描述(1)

4 clock cycles

IF

DE

EXE

WB

40

微电子学研究所李树国

流水线多周期指令的描述(2)

4 clock cycles

IF

DE IF

EXE DE

WB EXE WB

41

微电子学研究所李树国

流水线多周期指令的描述(3)

4 clock cycles

IF

DE IF

EXE DE IF

Read_write _address RData Aligner

Read-ICache

IR

imm[15-00] SA[10-06] Br[25-00] [03-00]

imm

ext

16

sa

RT imm

8

m u x

a d d e r

D_cache

m u x

s h i f t e r

。·

D-TLB

D-TagComp

WB EXE DE WB EXE WB

42

微电子学研究所李树国

流水线多周期指令的描述(4)

4 clock cycles

IF

DE IF

EXE DE IF

WB EXE DE WB EXE WB

IF

DE

EXE

WB

43

微电子学研究所李树国

流水线多周期指令的描述(5)

4 clock cycles

IF

DE IF

除法算法

手工除法算法

除法恢复迭代算法及其电路

寄存器P要比除数多一位

恢复迭代 P=P-B (必做) P=P+B (选做) P=P-B (必做) P=P+B (选做) P=P-B (必做) P=P+B (选做) P=P-B (必做) P=P+B (选做) .

迭代算法 P=P-2B(必做) P=P+B (选做) P=P-2B (必做) P=P+B (选做) P=P-2B (必做) P=P+B (选做) .

4

阵 列 乘 法 器 可 以 归 纳 为 一 个 单 列 的 数 点 的 化 简

32 个

位

单列数点化简

一个32位二进制位的化简

作业

设计一个32位无符号位的乘法器

要求: (1)给出32位乘法器结构示意图(纯组合逻辑 )

(2)给出采用的路径压缩算法或方法 (3)请给出32位时延报告(精确)和面积报告

Address ALU

Data Memory

Register file

2

Data

指令的控制逻辑

控制 逻辑

30 微电子学研究所李树国

MIPS数据通路的控制

• 缺少多路选择器MUX • 缺少每条指令的控制 • 控制通过多路选择器来实现

mux

31

微电子学研究所李树国

具有多路选择器和控制逻辑的处理器雏形

微处理器结构与设计

第5次课

微处理器的基本运算逻辑单元的设计

2013年3月27日

一个完整无符号16位乘法阵列

一 个 位 无 符 号

20位

问题 1: 被乘数由16位为什么变成了20位 或19位或16位? 2:乘数由16位变成了19位,为什么?

16

Booth 4

19位

-M的求补处理

19位

乘 法 器

16位

+4 add add

Address instruction

PC

Instruction memory

Data Register Register Register

Address ALU

Data Memory

Register file

Data

Lw r1, offset(base) ; // Funcation : r1<---memory(base+offset) 27 微电子学研究所李树国

指令2 : AND rd, rs, rt ; 操作: rd<---rs AND rt

+4 add add

Address instruction

PC

Instruction memory

Data Register Register Register

Address ALU

Data Memory

Register file

• 指令集概括为3个指令类

– 存储器访问指令类

• Lw,Sw 等

– 算术逻辑指令类

• Add,sub,and, or,Slt等

– 转移指令类

• Beg, J,等

1、尽量小,尽量简洁 2、不含乘、除、移位指令

1、make the common case fast 2、Simplicity favors Regularity

20

微电子学研究所李树国

清华的Mips的指令流水线

IF

MUX EPC EEPC MUX DEPC Exception vector Branch (26)

<<2

DE

Branch PC

EX

MEM

ALN

WB

Jump pc Jr rs <<2

connect

31-28

a d d e r

4

NPC ADD

NPC

除法不恢复迭代算法及其电路

不恢复的原因:减掉b后,直接左移1位,

相当于减掉的b变成了2b,若这次符号位为负,只需 要加b,就相当于减掉了b,即-2b+b=-b;

若为符号位为0,就继续减b 最后一次是调整还原原来的b

微处理器的数据通路和控制

19

微电子学研究所李树国

MIPS 5-stage 流水的数据通路

Data Memory

Register file

Data

J traget; 29 微电子学研究所李树国

MIPS数据通路还缺少什么?

3

连接红线可以吗?

1

MUX

+4 add add

Address instruction

PC

Instruction memory

Data Register Register Register

c o m p a r e

NPC

NPC

Exception Handler

Decoder

PC op[31-26] rs[25-21] rt[20-16] rd[15-11]

Read_RS

Data_RS

Read_RT

Data_RT Write_ad

Write_Data

WData

RS sa

l o g i c

45

微电子学研究所李树国

46

setup时间和hold时间

Setup/hold time 是对输入信号和时钟信号之间的时间要求。 建立时间是指触发 器的时钟信号上升沿到来以前,数据稳定不 变的时间。输入信号应在时钟上升沿(如上升沿有效)之前 的T时间到达,这个T就是建立时间-Setup time.如setup time 不满足,这个数据就不能被这一时钟打入触发器, 保持时间是指触发器的时钟信号上升沿到来以后,数据稳定不 变的时间。如果hold time 不够,数据同样不能被打入触发 器。 建立时间(Setup Time)和保持时间(Hold time)。建立时间 是指在时钟边沿前,数据信号需要保持不变的时间。保持时 间是指时钟跳变边沿后数据信号需要保持不变的时间。如果 不满足建立和保持时间的话,那么DFF将不能正确地采样到 数据,将会出现亚稳态的情况。

EXE DE IF

WB EXE DE WB EXE WB

IF

DE

IF

EXE

DE

WB

EXE WB

44

微电子学研究所李树国

流水线多周期指令的描述(6)