缓冲电路设计方法

三极管buffer电路

三极管buffer电路一、引言在电子系统中,信号的传输和处理经常需要用到缓冲电路。

三极管buffer 电路作为一种基本的缓冲电路,被广泛应用于各种电子设备和系统中。

本文将对三极管buffer电路的工作原理、设计要点、应用以及结论进行详细阐述。

二、三极管buffer电路的工作原理三极管buffer电路主要由三极管和电阻组成。

三极管是一种具有电流放大功能的电子器件,其三个电极分别是基极(B)、集电极(C)和发射极(E)。

在三极管buffer电路中,输入信号通过基极进入三极管,经过电流放大后从集电极输出,再通过电阻反馈到发射极,形成一个负反馈回路。

这个负反馈回路可以有效地减小输出信号的幅度波动,使输出信号保持稳定。

三、三极管buffer电路的设计要点1.三极管的选择:根据实际需求选择适当类型和参数的三极管。

不同类型的三极管具有不同的放大倍数、频率特性和功率容量等特点,因此要根据电路的具体要求进行选择。

2.电阻的选择:电阻的选择对三极管buffer电路的性能至关重要。

应根据输入信号的幅度、频率以及所需的放大倍数来选择适当的电阻值。

此外,还要考虑到电阻的精度、功率和稳定性等参数。

3.偏置电路的设计:为了使三极管工作在合适的状态,需要设计适当的偏置电路。

偏置电路的作用是为三极管提供稳定的直流工作点,防止电路性能受到电源电压波动或环境温度变化的影响。

4.稳定性分析:为了确保三极管buffer电路的性能稳定,需要进行稳定性分析。

分析方法主要包括使用小信号模型进行频率域分析,以及通过稳定性因子进行时域分析。

通过合理的电路设计和参数调整,可以提高三极管buffer 电路的稳定性。

四、三极管buffer电路的应用1.信号传输:在信号长距离传输时,信号可能会受到各种干扰因素的影响,导致信号质量下降。

使用三极管buffer电路可以有效地隔离源和负载之间的干扰,提高信号传输的稳定性和可靠性。

2.缓冲:在多级电路中,各级电路之间可能存在相互干扰的问题。

缓冲级电路设计

制作电子管缓冲级电路图近来放假没有外出,趁着有空便大过发烧瘾,亲自动手做了一部Buffer(缓冲级),慢火煲了数天,其声音一天比一天美丽,觉得非常值得向各位发烧读者介绍和分享一下。

这个缓冲级的线路是用真空管12AU7A作三极A类扩流缓冲的,无负反馈,如图1所示。

本人觉得其音色在多方面都比Marantz 7的Buffer为佳,不过Marantz 7用电子管每声道只用半只,而这个线路每声道用一只12AU7,左右独立工作。

输入级用一只金属膜电容交连接入12AU7的第一栅极,该屏极由另一只PP电容连至12AU7的第二栅极,使其第二组triode已成为上级的电流自动调节系统,输出取自第一组阴极与第二组屏极交连处,再经一只2.2μFPP电容连到输出插座。

电阻R5的设置是在于把整线路设备于A类工作状态,即使没有信号或小信号输入时,都有一个固定屏流通过,使音色来得顺滑甜美,温暖自然。

早阵子去电子管铺,店员介绍一只北京电子管厂于60至70年代生产的钢骨双云母片旧装新管12AU7,用眼细看内部手工精细,包括极片、接脚、灯丝焊接和水银电镀都有上等工艺之感,价钱很便宜,还有测试配对服务。

我一共买了3只。

有一只是将用于另一部制作;12AU7加12BZ7加级间升压变压器加211的sinRle—endeddirectheatingtriode后级作头关的,完工后希望来日有机会在此与各位分享。

缓冲级的高压用了降压值有250V左右的π形滤波电源,灯丝为直流供电,如图2所示。

最后试机,测试的器材部分是本人的制作;组合是以Resolution Quantum解码推无源四层电阻搭棚前级,推电池供电的电子分音器,再推三部半电池供电的纯A 类后级直驱扬声器,声箱内并无传统式LC分音器,声音算得上平均中肯。

把焊好后的缓冲器接人解码器和前级之间播唱,发觉中高频分量不足。

于是把这缓冲器用调谐器作48小时长煲,输出接上47kΩ假负载。

两天后接回组合当中,先来一只萧邦《第一钢协》Adagio,Schindler’s List《第六》和十二段,试后场人声合唱,Evita的《Lament》试前场女声和吉他,Engelbert试男声…… 再试下去就已经并非试机,而是陶醉地欣赏音乐,真正的投入了音乐,虽然不是现场演奏的音乐,却真真正正地令人投入当中!本来这是已经很好的器材,再加上了电子管Buffer修饰过的表现,我的Resolution Quantum加上全套组合都升级了,它从未如此过!玩音响不要停下来,越玩越有味,一停就恐怕玩完了。

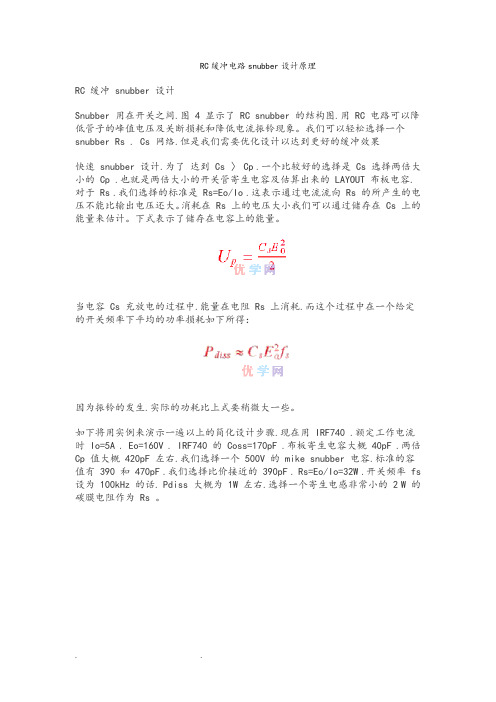

RC缓冲电路snubber设计原理

RC缓冲电路snubber设计原理RC 缓冲snubber 设计Snubber 用在开关之间,图4 显示了RC snubber 的结构图,用RC 电路可以降低管子的峰值电压及关断损耗和降低电流振铃现象。

我们可以轻松选择一个snubber Rs ,Cs 网络,但是我们需要优化设计以达到更好的缓冲效果快速snubber 设计,为了达到Cs 〉Cp ,一个比较好的选择是Cs 选择两倍大小的Cp ,也就是两倍大小的开关管寄生电容及估算出来的LAYOUT 布板电容,对于Rs ,我们选择的标准是Rs=Eo/Io ,这表示通过电流流向Rs 的所产生的电压不能比输出电压还大。

消耗在Rs 上的电压大小我们可以通过储存在Cs 上的能量来估计。

下式表示了储存在电容上的能量。

当电容Cs 充放电的过程中,能量在电阻Rs 上消耗,而这个过程中在一个给定的开关频率下平均的功率损耗如下所得:因为振铃的发生,实际的功耗比上式要稍微大一些。

如下将用实例来演示一遍以上的简化设计步骤,现在用IRF740 ,额定工作电流时Io=5A ,Eo=160V ,IRF740 的Coss=170pF ,布板寄生电容大概40pF ,两倍Cp 值大概420pF 左右,我们选择一个500V 的mike snubber 电容,标准的容值有390 和470pF ,我们选择比价接近的390pF ,Rs=Eo/Io=32W ,开关频率fs 设为100kHz 的话,Pdiss 大概为1W 左右,选择一个寄生电感非常小的 2 W 的碳膜电阻作为Rs 。

如果这种简化而实际有效的设计方法还不能有效减小峰值电压,那么我们可以增加Cs ,或则使用如下的优化设计方法。

优化的RC 滤波器设计在一些情况下必须降低峰值电压及功率损耗很严重,我们可以借鉴以下的优化snubber 设计方法,以下是W.McMurray 博士在一篇文章提出的经典的Rcsnubber 优化设计方法,如下讨论其精粹的设计步骤。

开关电源中RC缓冲电路的设计

开关电源中RC缓冲电路的设计中心议题:∙RC缓冲电路设计∙带RC缓冲的正激变换器主电路设计解决方案:∙电容C限制了集电极电压的上升速度∙电容C的大小不仅影响集电极电压的上升速度,而且决定了电阻R上的能量损耗在带变压器的开关电源拓扑中,开关管关断时,电压和电流的重叠引起的损耗是开关电源损耗的主要部分,同时,由于电路中存在杂散电感和杂散电容,在功率开关管关断时,电路中也会出现过电压并且产生振荡。

如果尖峰电压过高,就会损坏开关管。

同时,振荡的存在也会使输出纹波增大。

为了降低关断损耗和尖峰电压,需要在开关管两端并联缓冲电路以改善电路的性能。

缓冲电路的主要作用有:一是减少导通或关断损耗;二是降低电压或电流尖峰;三是降低dV/dt或dI/dt。

由于MOSFET管的电流下降速度很快,所以它的关断损耗很小。

虽然MOSFET管依然使用关断缓冲电路,但它的作用不是减少关断损耗,而是降低变压器漏感尖峰电压。

本文主要针对MOSFET管的关断缓冲电路来进行讨论。

1RC缓冲电路设计在设计RC缓冲电路时,必须熟悉主电路所采用的拓扑结构情况。

图l所示是由RC组成的正激变换器的缓冲电路。

图中,当Q关断时,集电极电压开始上升到2Vdc,而电容C 限制了集电极电压的上升速度,同时减小了上升电压和下降电流的重叠,从而减低了开关管Q的损耗。

而在下次开关关断之前,C必须将已经充满的电压2Vdc放完,放电路径为C、Q、R。

假设开关管没带缓冲电路,图1所示的正激变换器的复位绕组和初级绕组匝数相同。

这样,当Q关断瞬间,储存在励磁电感和漏感中的能量释放,初级绕组两端电压极性反向,正激变换器的开关管集电极电压迅速上升到2Vdc。

同时,励磁电流经二极管D流向复位绕组,最后减小到零,此时Q两端电压下降到Vdc。

图2所示是开关管集电极电流和电压波形。

可见,开关管不带缓冲电路时,在Q关断时,其两端的漏感电压尖峰很大,产生的关断损耗也很大,严重时很可能会烧坏开关管,因此,必须给开关管加上缓冲电路。

开关电源缓冲电路设计方法(有应用图)

開關電源缓冲电路设计方法1. RCD 缓冲电路•Lm=L1+L2 •Ls•Cs•Ds•Rs :::::电源线的线电感缓冲电路电感缓冲电容缓冲二极管缓冲电阻2. 关断波形•Io •Vcesp •Vcep •Ed •Vfp(Ds) :::::集电极关断电流Ls引起的尖峰电压峰值Cs充电的峰值电压电源电压缓冲二极管的正向恢复电压•Vfp(Ds) •Ls 应尽量小应尽量小•Lm •Cs 应尽量小应足够大3. 缓冲电路的选择 (1)缓冲电容(Cs)•Lm •Io •Vcep ::1μH/m2×Ic(Rated) 0.9×Vces•Ed ::400V for AC 220V, 800V for AC 440V (2)缓冲电阻(Rs)·f:开关频率4. 缓冲电路类型类型线路图备注A 2-in-1半桥:独立缓冲器6-in-1全桥:集中缓冲器B 2-in-1半桥:独立缓冲器6-in-1全桥:集中缓冲器C集中缓冲器5. 缓冲参数表1000V/GTR: Z- 系列型号Ic(DC) Vces 缓冲器类型Cs(Ed=650V)Rs(Lm=1μH,f=15kHz)Ds2DI30Z-100 30A600VA(Lm=0.5μH)0.033 μF- -2DI50Z-100 50A 0.094 μF- -2DI75Z-100 75AB(Lm=1.0μH)0.15 μF 1.2kΩ/60W ERG27-102DI100Z-100 100A 0.22 μF 1.0kΩ/100W ERG27-10 2DI150Z-100 150A 0.56 μF330Ω/230W ERG27-101DI200Z-100 200AC(Lm=1.0μH)2.7 μF68Ω/400WERG27-10ERG77-101DI300Z-100 300A 6.4 μF33Ω/900W ERG27-10 ERG77-101200V/GTR: Z- 系列型号Ic(DC) Vces 缓冲器类型Cs(Ed=800V)Rs(Lm=1μH,f=15kHz)Ds2DI30Z-120 30A1200VA(Lm=0.5μH)0.022 μF- -2DI50Z-120 50A 0.068 μF- -2DI75Z-120 75AB(Lm=1.0μH)0.1 μF 2.2kΩ/60W ERG28-122DI100Z-120 100A 0.47 μF330Ω/100W ERG28-12 2DI150Z-120 150A 0.56 μF330Ω/230W ERG28-121DI200Z-120 200AC(Lm=1.0μH)2.2 μF68Ω/400WERG28-12ERG78-121DI300Z-120 300A 4.7 μF33Ω/900W ERG28-12 ERG78-12600V/IGBT系列 *(L/F系列,部分N系列)型号Ic(DC) Vces 缓冲器类型Cs(Ed=400V)Rs(Lm=1μH,f=15kHz)Ds6MBI10*-060 10A600V A(Lm=0.5μH)0.033μF- -6MBI15*-060 15A 0.1μF- - 6MBI20*-060 20A 0.16μF- - 6MBI30*-060 30A 0.33μF- -6MBI50*-06050A 1.0μF- -2MBI50*-060 0.33μF- -6MBI75*-06075AB(Lm=1.0μH)1.6μF16Ω/420W ERE24-062MBI75*-060 0.47μF56Ω/420W ERE24-066MBI100*-060100A 2.2μF10Ω/750W ERE24-062MBI100*-060 0.68μF22Ω/750W ERE24-06 2MBI150*-060 150A 1.8μF16Ω/1.7kW ERE24-06 2MBI200*-060 200A 3.3μF 6.8Ω/3.0kW ERE24-062MBI300*-060 300AC(Lm=1.0μH)10.0μF 2.2Ω/6.8kWERE24-06ERE74-062MBI400*-060 400A 18.0μF 1.6Ω/12kW ERE24-06×2P ERE74-06×2P1200V/IGBT系列*(L/F系列,部分N 系列)型号Ic(DC) Vces 缓冲器类型Cs(Ed=800V)Rs(Lm=1μH,f=15kHz)Ds6MBI8*-120 8A1200VA(Lm=0.5μH)0.0068μF- -6MBI15*-120 15A 0.022μF- -6MBI25*-120 25A 0.068μF- -2MBI25*-120 30A 0.022μF- -6MBI50*-120 50A 0.068μF- -2MBI75*-120 75AB(Lm=1.0μH)0.1μF220Ω/420W ERG28-122MBI100*-120 100A 0.47μF56Ω/750W ERG28-122MBI150*-120 150A 0.56μF47Ω/1.7kW ERG28-121MBI200*-120 200AC(Lm=1.0μH)2.2μF10Ω/3.0kWERG28-12ERG78-121MBI300*-120 300A 4.7μF 5.6Ω/6.8kWERG28-12ERG78-126. 低电感线路的基本结构(1) 叠层导线板(2) 叠层导线条7. 电容缓冲器电路(集中缓冲)缓冲电容的选择•L•Io•Vceo•Ed:分布电感:关断时的Ic:尖峰电压:DC电源电压8. 集中缓冲器电容(参考值)元件规格栅极驱动条件电源电路的分布电感缓冲电容-Vge(V) Rg(Ω)(μH)(μF)600V50A5―15≥51- 0.47 75A ≥33100A ≥24150A ≥16 ≤0.2 1.5 200A ≥9.1 ≤0.16 2.2 300A ≥6.8 ≤0.1 3.3 400A ≥4.7 ≤0.08 4.71200V50A5―15≥24- 0.47 75A ≥16100A ≥9.1150A ≥5.6 ≤0.2 1.5 200A ≥4.7 ≤0.16 2.2 300A ≥2.7 ≤0.1 3.3。

缓冲电路设计及仿真

1 缓冲电路作用缓冲电路一般并联在开关器件两端,重要有克制过电压、减少器件损耗、消除电磁干扰的作用。

1) 克制过电压逆变器高频工作时,开关器件快速开通、关断。

由于主电路存在杂散电感,器件在开关过程中,急剧变化的主电路电流会在杂散电感上感应出很高的电压,使器件在关断时承受很高的关断电压。

在器件关断时,主电路杂散电感上会产生与直流电压同向的感应电压pdiL dt,若无缓冲电路,则该电压会加在器件两端形成过电压,当该电压超过器件额定电压时,器件损坏。

此外,反并联二极管在反向恢复时产生的di/dt 也会导致较高的过电压。

2) 减少器件损耗已知器件的功耗由下式决定:01TP uidt T=⎰ (1.1)在电路中增长缓冲电路,可以改变器件的电压、电流波形,进而减少损耗。

从下图可知,在没有缓冲电路时,电压快速升至最大值,而此时电流仍然是最大值,此时的损耗最大。

加入缓冲电路后,避免了电压、电流出现同时最大值的情况,损耗得以减少。

U DS无缓冲电路U DS I DI D有缓冲电路3) 消除电磁干扰电路运营时,在没有缓冲电路的情况下,器件两端电压会发生高频振荡,产生电磁干扰。

采用缓冲电路,可克制器件两端电压的高频振荡,起到减小电磁干扰的作用。

因此,减少或消除器件电压、电流尖峰,限制dI/dt 或dV/dt ,减少开关过程中的振荡以及损耗,我们在逆变器中设计缓冲电路,以保证器件安全可靠工作。

2 杂散电感的测量与计算设计缓冲回路之前,一方面需要拟定杂散参数的量。

杂散电感是特定电路布局的结果,不容易计算出来,我们一般采用测量的方法来拟定杂散电感的大小。

在没有任何缓冲回路时,用示波器观测器件关断时的振荡周期T1;接着,在开关管两端并联一个值拟定的电容,即测试电容test C ,重新测量器件关断时的振荡周期T2。

则杂散电感可由下式得出:2221p 2()L 4testT T C π-=(2.1)杂散电容为:21(2)p p i C L f π=(2.2)其中i f 为无缓冲电路时的振荡频率。

有源电力滤波器缓冲电路的参数优化设计

( .东北大 学 信 息科 学 与工程 学 院 , 宁 沈 阳 1 0 0 ; 1 辽 1 0 4

2 中国北方 车辆研 究所 电子信 息 与控制 部 , 京 10 7) . 北 0 0 2

摘 要 : 对 AP 主 电路 中 I B 针 F G T开 关 产 生 过 大 尖 峰 电 压 的 问题 , 出 一 种 有 效 的 R D缓 冲 电路 参 数 优 提 C 化 设 计 方 法 。通 过 对 缓 冲 电路 工 作 原 理 的分 析 , 导 和 计 算 出缓 冲 电路 参 数 的设 计 公 式 。仿 真 和实 验 结 果 表 推 明 , 设计能够有效抑制 IB 该 G T产 生 的尖 峰 电 压 , 高 E 特 性 , 证 电路 的 可 靠 运 行 。该设 计 成 功应 用 于 1 提 MI 保 台 1 0k ・ 有 源 电 力 滤 波 器 实 验 样 机 , 样 机 的 长 期 运 行 , 明 了该 方 法 的 有 效 性 和 实 用 性 。 0 V A 该 证 关 键 词 : 冲 电路 ; 化 设 计 ; 缘 栅 双 极 晶 体 管 ; 源 电 力 滤 波 器 缓 优 绝 有

( .C le eo n o ma inSce c n g n e ig,Not e se nUn v ri 1 o lg f I f r to in ea d En i ern rh a tr ie st y,S e y n 1 0 4 hn a g 10 0 , Lio i g,C ia;2 a nn hn .Elcr nc n r to n o to pa t n ,Ch n eto isI foma ina d C n r lDe rme t ia

No t e il sa c n tt t ,Bejn 0 0 2 rh V h ceRee rh I siu e ii g 1 0 7 ,Ch n ) ia

缓冲电路

当需要同时串联和并联晶闸管时,通常采用先串后并的方法连接。

பைடு நூலகம்

一、电力电子器件的保护措施

• (2) 过电压保护措施

二、缓冲电路

• 缓冲电路(一种开关辅助电路), 是为避免器件流过过 大的电流和在其上出现过高的电压或为错开同时出现的电 压、电流的峰值区而设置的,将开关损耗由器件本身转移 至缓冲电路, 减小器件在开关过程中产生的过电压、过 电流、过热、du/dt 和di/dt , 以确保器件安全、可 靠运行。

一电力电子器件的保护措施过电压保护措施二缓冲电路缓冲电路一种开关辅助电路是为避免器件流过过大的电流和在其上出现过高的电压或为错开同时出现的电压电流的峰值区而设置的将开关损耗由器件本身转移至缓冲电路减小器件在开关过程中产生的过电压过电流过热dudt和didt以确保器件安全可靠运行

任务2、电力电子器件的保护及缓冲措施

二、缓冲电路

• 1、缓冲电路的基本类型与结构 • 1)基本类型:开通缓冲和关断缓冲 • 2)基本设计思路 • 在器件开通时使电流缓升; 关断 时使电压缓升,减小开关过程中的 功率损耗。 • 2、开通缓冲电路

二、缓冲电路

3、关断缓冲电路:RCD充放电式、RCD钳位式

二、缓冲电路

4、复合缓冲电路

三、电力电子器件的串、并联

一、电力电子器件的保护措施

• 1、过电流保护 • 2)过电流的产生 • 造成电力电子器件过电流的重要原因:电网电压波动太大、 管子损坏、缺相、过载等。 • 2)过电流保护措施 • 电力电子装置可能采用的几种过电流保护措施

一、电力电子器件的保护措施

一、电力电子器件的保护措施

rc缓冲电路和rcd缓冲电路工作原理

rc缓冲电路和rcd缓冲电路工作原理RC缓冲电路和RCD缓冲电路是电子电路中常见的两种缓冲电路。

它们的作用是将不稳定或不理想的电信号转换为稳定的、能够满足后续电路需求的信号。

本文将从RC缓冲电路和RCD缓冲电路的基本原理、应用场景和设计注意事项等方面进行详细探讨。

一、RC缓冲电路的工作原理RC缓冲电路是由一个电阻(R)和一个电容(C)组成的。

当输入信号经过电阻和电容连续地输入电路时,就会产生一个对输入信号进行平滑的作用。

电容器的作用是在电阻充电时存储电能,当电阻上的电压开始下降时,电容器释放存储的电能,以保持输出信号的平稳。

在RC缓冲电路中,R和C的大小决定了输出信号的时间常数(τ=RC)。

时间常数可以理解为输出信号的响应速度,τ越大,输出信号越平滑,响应速度越慢。

因此,通过调整R和C的值,可以控制输出信号的平滑程度和响应速度,以满足特定应用需求。

二、RCD缓冲电路的工作原理RCD缓冲电路是比RC缓冲电路更复杂的一种缓冲电路。

它由一个电阻(R)、一个电容(C)和一个二极管(D)组成。

RCD缓冲电路的主要作用是滤除输入信号中的噪声和高频成分,以使输出信号更加稳定和可靠。

在RCD缓冲电路中,电容器作为一个储能元件,用于存储电能,并使输出信号平滑。

而二极管的作用是将正半周的输入信号直接带过,阻止负半周信号的通过。

这样可以去除输入信号中的噪声和低频成分,从而保证输出信号的纯净性和稳定性。

三、RC缓冲电路和RCD缓冲电路的应用场景1. 音频放大器在音频放大器电路中,RC缓冲电路和RCD缓冲电路常用于提高音频信号的质量和增强音频放大的效果。

它们可以平衡频率响应,提高音频信号的纯净度,同时保护功率放大器免受负载变化的影响。

2. 摄像机和手机摄像头在摄像机和手机摄像头等光电转换电路中,RC缓冲电路和RCD缓冲电路用于处理传感器输出的信号。

它们可以减少输入信号的噪声和干扰,同时提供稳定和可靠的输出信号,以实现高质量的图像捕捉和视频录制。

RC缓冲电路snubber设计基本知识

RC缓冲电路snubber设计原理RC 缓冲snubber 设计Snubber 用在开关之间,图4 显示了RC snubber 的结构图,用RC 电路可以降低管子的峰值电压及关断损耗和降低电流振铃现象。

我们可以轻松选择一个snubber Rs ,Cs 网络,但是我们需要优化设计以达到更好的缓冲效果快速snubber 设计,为了达到Cs 〉Cp ,一个比较好的选择是Cs 选择两倍大小的Cp ,也就是两倍大小的开关管寄生电容及估算出来的LAYOUT 布板电容,对于Rs ,我们选择的标准是Rs=Eo/Io ,这表示通过电流流向Rs 的所产生的电压不能比输出电压还大。

消耗在Rs 上的电压大小我们可以通过储存在Cs 上的能量来估计。

下式表示了储存在电容上的能量。

当电容Cs 充放电的过程中,能量在电阻Rs 上消耗,而这个过程中在一个给定的开关频率下平均的功率损耗如下所得:因为振铃的发生,实际的功耗比上式要稍微大一些。

如下将用实例来演示一遍以上的简化设计步骤,现在用IRF740 ,额定工作电流时Io=5A ,Eo=160V ,IRF740 的Coss=170pF ,布板寄生电容大概40pF ,两倍Cp 值大概420pF 左右,我们选择一个500V 的mike snubber 电容,标准的容值有390 和470pF ,我们选择比价接近的390pF ,Rs=Eo/Io=32W ,开关频率fs 设为100kHz 的话,Pdiss 大概为1W 左右,选择一个寄生电感非常小的2 W 的碳膜电阻作为Rs 。

如果这种简化而实际有效的设计方法还不能有效减小峰值电压,那么我们可以增加Cs ,或则使用如下的优化设计方法。

优化的RC 滤波器设计在一些情况下必须降低峰值电压及功率损耗很严重,我们可以借鉴以下的优化snubber 设计方法,以下是W.McMurray 博士在一篇文章提出的经典的Rcsnubber 优化设计方法,如下讨论其精粹的设计步骤。

最小应力无源无损缓冲电路参数设计与实验

电路搭 建 了一 个 1 W 最 小应力 无源无 损缓冲 电路进 行实验 。实验 结果 证 明, 小应力无 源无损 缓冲 电路实现 k 最 了 Bc u k电路 中开 关管 的零 电流 开通 ( c ) z s 与零 电压关 断 ( v ) 可 有效 降低开关 损耗 , 高系统转 换效 率 。 zs, 提

第4 6卷 第 9期

2 2年 9月 01

电力 电子技 术

P w rE e t n c o e l cr i s o

Vo .6,No9 1 4 . S pe e 0 2 e tmb r2 1

最小应力无源无损缓冲电路参数设计与实验

姚 绪 梁 。王秋 瑶

( 哈尔滨 工程大 学 , 自动 化学 院 ,黑龙江 哈 尔滨 100 ) 50 1 摘要: 随着 电力 电子器件 的高频 化发展 , 开关损 耗成 为 电路主要 损耗 方式 。降低开关 损耗 的有效途 径是采 用软 开关 技术 。 无源 无损缓 冲 电路 由于 结构简单 , 易于控制 , 可靠 性高 , 近年 来得 到广泛关 注和研 究。 计 了一 种新 设 型 最 小应力 无源 无损 缓冲 电路 , 析 了其 工 作原理 , 分 阐述 了其各 阶段 工作情 况 , 计 了 电路 参数 , 基于 B c 设 并 uk

zr-urn- th g Z S n e -o aes ihn ( V )cniosfrtrigo do , a dc wth e cr t w ci ( C )adzr vl g— t ig Z S odt n o nn na f i cn r ues i 。 o e s i n o t wc i u n t e c

F u d t n P oetS p ot yN t nl a r c neF ud t no hn ( o5 2 93 ) o n a o rjc :u pr d b a oa N t a Si c on a o fC ia N .17 0 9 i e i ul e i

RC缓冲电路的优化设计

RC缓 冲 电路 的优 化 设计

郑州职业技术学院 王 辉 李性珂

【 摘要】 电子 电路 中对R C 缓冲 电路进行设计是 一个很有挑 战性的课题 。对R C 缓冲 电路 的深入认识 与理解 是进行优化设计 的基础 ,在设计过程 中,对于参 数的选 择也是 需 要相 当谨慎的。只有在此基础上,才能够展开对缓 冲电路 的优化设计。在设计的过程 中,在关键 的时刻,也要 抓住 时机采取紧要措施。在一定的实验条件 下,采取特定 的 行动 ,也是优化设计得 以实现地保证。在 电子工程设计 的过程 中,抓住要关键地抓住 这几点,才可 以很好地解决缓冲 电路的优化设计 这一关键性 问题。 【 关键词】R C 缓中 的 电流 主 要 有 直 了吸收 电容对 尖峰 电压 有 良好 吸收作用 。 流 电和 交流 电两 种 。交流 电和 直流 电有着 本 3 . 缓冲 电路 的优化设计 质 的区 别 ,和鲜 明 的特 点 。为 了设计 更好 的 3 . 1流 过缓冲 二极管 电压、 电压 值要求 电路 ,我们 不妨 利用 其 中 的交流特 性 。首 先 ( 1 )关断 尖峰 电压最 小 ,即: 我们 要 不辞 劳苦 地把 规定 的电路 的杂 散 电感 m i n = U c r = 十 r L / f f 2 t 1 ) 7_ 给计 算 出来 。 当然 ,如果 我们 采用 公 式来 计 这 就 是 设 计 的 目的, 一 旦U V P 变 小 并 算 ,就会 事 半功 倍 。 电路 的杂 散 电感 就可 以 且U C s P 也 同时 变小 ,这 个时 候开 关 噪声 和它 用下 式进行计 算: 的干 扰 也会 同时 变小 。再 者 ,如 果U V P 足 够 r 、 1 小 ,这时候 我们就 可选用 C - E 极 耐压V C E S /  ̄的 ;f 卜l I G B T ( 在其余 参数 相同时 ,V C E S 的I G B T 价 格较 当电路 中的杂散 电感 后被我 们所知 道后, 低) ; 同样 若U C s P d  ̄ ,这 时候耐压 低 的缓冲 电 电路 中的杂 散 电容就 可 以利 用 以下公 式计 算 容 就有 了很好 的用 武之 地 ,因 为在 电容 量相 获得 : 同时 ,耐压 低 的 电容价 格较 低 、体 积较 小 的 特 点 ,且无 需通过 串联来提 高耐压 。 c = ( 2 )最 小 的平 均 电流来 通 过 缓 冲 二极 其 中, 没有增加 缓存 电路时 的振 荡频 率为 管 ,即 : f i。 吸 收 电 容 上 需 要 吸 收 的 能 量 为 m i n , l r J 厨“ , / f t 1 . E: ] / 2 C A U 2其 中寄生 电感产生 的过 电压 ¥ u , 如 果想选用 平均正 向 电流 I F ( A v ) 小 的快 所 以¥ u =U c e m a x - U d , 吸收 电容C ;其 中 ,在 实 恢 复二 极 管 ,那 么 在其 它情 况不 变 得假 设 下 验 中示波 器可 以显示 出U c e m a x U d 为直 流 电 I D s ( A V ) 就 要小 。I F ( A V ) 小的快 恢复 二极管 有 压 。缓冲 电阻的选择 个 比较 好 的特性 就是 ,在 理 想 的不 受别 的 利用 下式进 行计算 : 因素 因素影 响 的情 况下 I F ( A V ) 小 的快恢 复 二 R s  ̄ 4 z > T e 7 极 管货源较 充足 、体积不 大、价格便 宜 。 又 因为: 3 . 2分 、合 闸时 间的调整 l 我 们把 合 闸指 令到 所有 极 的触 头分 离所 肛 = “ +^ ) / ’ 用 的 时 间间隔 , 叫做 断路器 分 闸时 间 ;把所 式 中 :I G B T 的关 断 电流为 I O 。 由此得 出 有 极 的动触 头 闭合 的 时间 ,叫做 断 路器 合 闸 上 述两 者 之 和 就是 吸 收 电阻R 消 耗 的功 率 , 时间 。分 闸命 令 发出到 分 闸脱 扣机 构打 开 、 即: 分 闸脱扣 机构 打 开到 动触 分离 ,这 两 段 时间 l , l 起 叫做 分 闸时 间 。合 闸时 间 由合 闸 脱扣 机 P c 嫒, ’ 十 p + L 埔/ 构打 开到 动触 头完 全 闭合 和合 闸命 令 发 出到 在R C 吸收 电路 中 ,如果满 足S = P  ̄ C 不大 于 合 闸脱扣 机构 打开 这 两部 分组 成 。对 于分 闸 1 / 4 的I G B T 接通 时 间,就可 以保证释 放大 部分 时间 的调 整 ,主要 包括 ,分 闸 电磁 铁 间 隙、 电容c 中的 能量, 而 不会影 响 下一 次 吸收 , 因 分 闸脱扣 机构 两 部分 。可 以通 过调 整 电磁 铁 由此得 出吸收 电阻可 以通过 下式: 出力 大小 ,来 达 到 :缩小 电磁 铁动 作 时 间, 保证 电磁 铁 快速 启 动 的 目的 。 ( 这 就 是 电磁 R≤旦 4 C 铁 调 整 )分 压 电路 的 基本 属性R C 电路 均有 所 ( n 为 导通 时间 )来 确定吸 收 电阻 以本 质 上它 也是 一个 分压 电路 ,她 的输入 电 综合 可得R 为: 压可 以是 电路状 态变 化产 生 的阶 跃信 号 以及 电路 传 输 的信号 ,对 于输 出电压 ,我 们 可 以 2 , / L p / C p R 1 / 通过 电容C 和 电阻R 来进行 调整 ,并根据 电容c 为 了达 到 降低在 电阻上 的 功率 损耗 的 目 的放 点 和冲 电的特 点 ,为 了使R c 电路 达 到 电 的 , 缓 存 电容 的选择 可 以在允 许范 围 内选一 路 中信 号传 输 的媒介 ,变换 波形 的转 换 器 , 个较 小 的值 。适 当 的选 择参 数 ,你 就能 设计 选取 有 用信 号 的滤波 器 或选 频 网络等 目��

RC缓冲电路snubber设计原理

RC缓冲电路snubber设计原理RC 缓冲 snubber 设计Snubber 用在开关之间.图 4 显示了 RC snubber 的结构图.用 RC 电路可以降低管子的峰值电压及关断损耗和降低电流振铃现象。

我们可以轻松选择一个snubber Rs . Cs 网络.但是我们需要优化设计以达到更好的缓冲效果快速 snubber 设计.为了达到 Cs 〉 Cp .一个比较好的选择是 Cs 选择两倍大小的 Cp .也就是两倍大小的开关管寄生电容及估算出来的 LAYOUT 布板电容.对于 Rs .我们选择的标准是 Rs=Eo/Io .这表示通过电流流向 Rs 的所产生的电压不能比输出电压还大。

消耗在 Rs 上的电压大小我们可以通过储存在 Cs 上的能量来估计。

下式表示了储存在电容上的能量。

当电容 Cs 充放电的过程中.能量在电阻 Rs 上消耗.而这个过程中在一个给定的开关频率下平均的功率损耗如下所得:因为振铃的发生.实际的功耗比上式要稍微大一些。

如下将用实例来演示一遍以上的简化设计步骤.现在用 IRF740 .额定工作电流时 Io=5A . Eo=160V . IRF740 的 Coss=170pF .布板寄生电容大概 40pF .两倍Cp 值大概 420pF 左右.我们选择一个 500V 的 mike snubber 电容.标准的容值有 390 和 470pF .我们选择比价接近的 390pF . Rs=Eo/Io=32W .开关频率 fs 设为 100kHz 的话. Pdiss 大概为 1W 左右.选择一个寄生电感非常小的 2 W 的碳膜电阻作为 Rs 。

如果这种简化而实际有效的设计方法还不能有效减小峰值电压.那么我们可以增加 Cs .或则使用如下的优化设计方法。

优化的 RC 滤波器设计在一些情况下必须降低峰值电压及功率损耗很严重.我们可以借鉴以下的优化snubber 设计方法.以下是 W.McMurray 博士在一篇文章提出的经典的Rcsnubber 优化设计方法.如下讨论其精粹的设计步骤。

缓冲电路的设计

缓冲保护电路的选择一、基本概念缓冲电路又称为吸收电路,主要是用于抑制器件在开关过程中产生的过电压du/dt或者过电流di/dt,减小器件的损耗。

缓冲电路又可分为关断缓冲电路(过电压抑制电路)和开通缓冲电路(过电流抑制电路),而我们一般所说指的缓冲电路是关断缓冲电路,开通缓冲电路一般也称为di/dt过电流抑制电路。

二、电路选择及设计缓冲方法:一是减小漏电感,二是耗散过电压能量或者使能量反馈回电源中。

目前常用的2种缓冲电路分别为RCD缓冲电路和LCD缓冲电路,综合考虑2者的特性以及成本,决定使用RCD缓冲电路。

有缓冲电路的情况下,T 关断时,UCE 升高,负载电流通过Don,向Con 充电,对T 具有分流作用,减轻T的电流负担,同时由于Con 的电压惯性,可以抑制dUCE/dt,并且吸收电感所释放出的尖峰过电压能量。

T 开通时缓冲电容Con 先通过Ron向T 放电,使电流形成一个上升小台阶,此后因为有di/dt 抑制电路Loff的存在,i的上升速度减慢。

Ron 的作用是在T 开通期间限制放电电流的大小,应使Con 尽快放电到零,为T 下次关断时吸收能量做好准备。

RoffDoff 是在T 关断时为Loff 中的磁场能量提供放电回路而设置的续流通道三、参数计算T 关断时电容C 充电能量为E=0.5 CU2CE=0.5I C U CE(t r+t f)可以计算得到电容:C=I C( t r+t f)/U CER<t on/3C且有R≥U CE/0.25I c I C=40A U CE=673V t on<50ns 带入计算可得C=0.25μF R= 30Ω二极管采用快恢复二极管,保证足够的额定电压和电流。

反激电路RCD缓冲电路参数设计分析

反激电路RCD缓冲电路参数设计分析 RCD构成的钳位电路在开关变换器中运⽤⼴泛,RCD参数设计对于变换器性能尤其重要。

下⾯以反激变换器为例,介绍下RCD参数定性分析和定量设计,欢迎⼤家讨论。

1、电路拓扑2、定性分析 开关VS关断时,变压器漏感上的能量转移到电容C上,电容C电压开始上升。

当电容电压⼤于副边反射电压减去⼆极管导通电压的值时,⼆极管D截⾄,电容C开始给电阻R放电。

开关VS导通过程中,电容C不⼀定放电到零。

开关关断时,电容C充电⼯作情况 开关关断,⼆极管截⽌,电容C放电⼯作情况 开关导通,电容C放电⼯作情况(⼆极管⾃然截⽌) 当C较⼤时,RC时间常数较⼤,电容C上,电压上升缓慢。

当C特别⼤,电容C峰值电压⼩于副边反射电压,电容C上电压在副边反射电压附近波动,并与电阻R形成死负载。

当R,C值合适时,开关VS从关断到开通瞬间,电容C放电接近(N1/N2)*U o 当R,C值较⼩时,RC时间常数较⼩,在开关VS从关断到开通瞬间之间,电容C电压已经放电⾄(N1/N2)*U o,并停留在此电压处,这时,电阻R形成死负载,降低了效率。

3、定量计算 根据开关截⽌时,漏感能量等于电容C吸收的能量,则 其中: L1k为原边漏感, I1p为原边电流峰值 U DS为开关关断所能承受的最⼤漏源电压 U i为输⼊电压有效值 U reset为电容C的初始电压 ⼀般情况,当电容C的初始电压为0时,电容C的计算公式化简为右边的计算式⼦。

疑问:求电容C的关键是求L k,那么如何求得漏感L k呢? 根据在VS开通前,电容C上电压放电不能低于(N1/N2)*U o,则 其中:T OFF为开关管关断时间 T为开关管单周期时间 注意: Uds为开关漏源能承受的电压的最⼤值⽽不是实际变换器的漏源电压值,在这⾥实际计算时,是假设为常数的。

4、参考⽂献【1】张兰红,陈道炼.反激变换器开关应⼒抑制技术研究[J].电⼒电⼦技术,2002,36(2):29-31.【2】刘国伟,董纪清.反激变换器中RCD箝位电路的研究[J].电⼯电⽓,2001,20-23.。

数字电路设计中的时钟缓冲设计原理

数字电路设计中的时钟缓冲设计原理在数字电路设计中,时钟缓冲设计原理是非常重要的一部分。

时钟缓冲的作用是为了保证时钟信号的稳定性和准确性,以确保整个数字系统的正常运行。

在数字电路中,时钟信号起着非常关键的作用,它用于同步各个部分的工作,使整个系统按照设计要求进行运行。

时钟缓冲的设计原理主要是为了解决时钟信号传输过程中的延迟和失真问题。

当时钟信号在数字系统中传播时,会受到信号传输线的延迟、干扰等影响,从而影响时钟信号的准确性。

时钟缓冲的作用就是通过控制时钟信号的传输延迟,减小时钟信号的失真,保证时钟信号的稳定性。

时钟缓冲设计的关键在于选择合适的缓冲器件和设计合适的时钟信号传输线路。

常见的时钟缓冲器件有触发器、锁相环、时钟分频器等。

触发器是最常用的时钟缓冲器件之一,它可以将输入信号转换为稳定的、与输入信号频率相同的输出信号。

锁相环则可以将输入信号与本地稳定的时钟信号相比较,从而实现时钟信号的同步。

时钟分频器则可以将输入信号分频,以降低信号频率,减小信号传输过程中的延迟和失真。

在设计时钟缓冲时,需要注意以下几点原则:1. 选择合适的缓冲器件:根据设计的要求和系统的特点选择适合的缓冲器件,可以根据时钟信号的频率、传输距离等因素进行选择。

2. 设计合适的时钟信号传输线路:时钟信号传输线路的设计应考虑信号的传输延迟、干扰等因素,采取合适的布线方式和电磁屏蔽措施,以减小时钟信号传输过程中的失真和延迟。

3. 稳定性和准确性:时钟缓冲的设计要保证时钟信号的稳定性和准确性,确保整个数字系统的正常运行。

通过合理设计时钟缓冲,可以提高数字系统的整体稳定性和性能,保证系统正常运行。

在实际应用中,时钟缓冲的设计原理是数字电路设计中不可忽视的重要部分,对系统的性能和稳定性有着重要的影响。

classab输出级的buffer电路设计

classab输出级的buffer电路设计(原创版)目录1.buffer 电路的概述2.classab 输出级的 buffer 电路设计原理3.classab 输出级的 buffer 电路设计步骤4.classab 输出级的 buffer 电路设计注意事项5.classab 输出级的 buffer 电路设计的应用领域正文一、buffer 电路的概述Buffer 电路,又称为缓冲电路,是一种电子电路,用于在信号传输过程中对信号进行放大或衰减,以匹配负载或驱动传输线路。

在实际应用中,buffer 电路被广泛应用于模拟信号和数字信号的处理领域。

二、classab 输出级的 buffer 电路设计原理Classab 输出级的 buffer 电路设计是一种常见的放大器设计方法,其主要特点是在输出端采用两个互补的放大器电路,分别驱动正负半周期的信号波形,以实现对信号的高保真度放大。

这种设计方法能够有效地抑制谐波失真,提高信号的传输质量。

三、classab 输出级的 buffer 电路设计步骤1.根据输入信号的幅度和频率范围,选择合适的放大器电路。

2.设计输入级的放大器电路,使其具有足够的增益和带宽,以满足信号的放大和传输需求。

3.设计输出级的放大器电路,使其具有互补的正负半周期信号放大能力,以实现对信号的高保真度放大。

4.调整输出级的放大器电路的增益和带宽,使其与输入级的放大器电路相匹配,以实现最佳的信号传输效果。

5.设计 buffer 电路的输入和输出接口,以满足信号的输入和输出要求。

四、classab 输出级的 buffer 电路设计注意事项1.在设计过程中,应充分考虑信号的传输特性,选择合适的放大器电路和参数。

2.在输出级的放大器电路设计中,应注意正负半周期信号的平衡,以实现最佳的放大效果。

3.在调整输出级的放大器电路的增益和带宽时,应保证其与输入级的放大器电路相匹配,以避免信号的失真和传输效率的降低。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

ERG28-12 ERG28-12 ERG28-12

1MBI200*-120 200A

ERG28-12

2.2μF

10Ω/3.0kW

C

ERG78-12

1MBI300*-120 300A

(Lm=1.0μH) 4.7μF

ERG28-12 5.6Ω/6.8kW

ERG78-12

6. 低电感线路的基本结构

(1) 叠层导线板

2DI150Z-120 150A 1200V

0.1 μF 0.47 μF 0.56 μF

2.2kΩ/60W 330Ω/100W 330Ω/230W

ERG28-12 ERG28-12 ERG28-12

1DI200Z-120 200A

ERG28-12

2.2 μF

68Ω/400W

C

ERG78-12

1DI300Z-120 300A

ERG27-10 ERG27-10 ERG27-10

1DI200Z-100 200A

ERG27-10

2.7 μF

68Ω/400W

C

ERG77-10

1DI300Z-100 300A

(Lm=1.0μH) 6.4 μF

33Ω/900W

ERG27-10 ERG77-10

1200V/GTR: Z- 系列

Cs

Rs

2MBI200*-060 200A

3.3μF

6.8Ω/3.0kW ERE24-06

2MBI300*-060 300A

ERE24-06

10.0μF 2.2Ω/6.8kW

C

ERE74-06

2MBI400*-060 400A

(Lm=1.0μH) 18.0μF

ERE24-06×2P 1.6Ω/12kW

ERE74-06×2P

2MBI100*-060

(Lm=1.0μH)

1.6μF 0.47μF 2.2μF 0.68μF

16Ω/420W 56Ω/420W 10Ω/750W 22Ω/750W

ERE24-06 ERE24-06 ERE24-06 ERE24-06

2MBI150*-060 150A

1.8μF

16Ω/1.7kW ERE24-06

(Lm=1.0μH) 4.7 μF

33Ω/900W

ERG28-12 ERG78-12

600V/IGBT系列 *(L/F系列,部分N系列)

Cs

Rs

型号

Ic(DC) Vces 缓冲器类型

Ds

(Ed=400V) (Lm=1μH,f=15kHz)

6MBI10*-060 10A

0.033μF

-

-

6MBI15*-060 15A

2DI30Z-100 30A

A

0.033 μF

-

-

2DI50Z-100 50A

(Lm=0.5μH) 0.094 μF

-

-

2DI75Z-100 75A B

2DI100Z-100 100A (Lm=1.0μH)

2DI150Z-100 150A 600V

0.15 μF 0.22 μF 0.56 μF

1.2kΩ/60W 1.0kΩ/100W 330Ω/230W

1200V/IGBT系列 *(L/F系列,部分N系列)

Cs

Rs

型号

Ic(DC) Vces 缓冲器类型

Ds

(Ed=800V) (Lm=1μH,f=15kHz)

6MBI8*-120 8A

0.0068μF

-

-

6MBI15*-120 15A

0.022μF

-

-

A

6MBI25*-120 25A

0.068μF

-

:

线路图

·f:开关频率

备注 2-in-1 半 桥:独立缓 冲器

6-in-1 全 桥:集中缓 冲器 2-in-1 半 桥:独立缓 冲器

6-in-1 全 桥:集中缓 冲器

集中缓冲 器

5. 缓冲参数表 1000V/GTR: Z- 系列

Cs

Rs

型号

Ic(DC) Vces 缓冲器类型

Ds

(Ed=650V) (Lm=1μH,f=15kHz)

型号 Ic(DC) Vces 缓冲器类型

Ds

(Ed=800V) (Lm=1μH,f=15kHz)

2DI30Z-120 30A

A

0.022 μF

-

-

2DI50Z-120 50A

(Lm=0.5μH) 0.068 μF

-

-

2DI75Z-120 75A B

2DI100Z-120 100A (Lm=1.0μH)

(2) 叠层导线条

7. 电容缓冲器电路(集中缓冲)

缓冲电容的选择

8. 集中缓冲器电容(参考值)

元件规格

栅极驱动条件

• L :分布电感 • Io :关断时的 Ic • Vceo:尖峰电压 • Ed :DC 电源电压

电源电路的分布电感

缓冲电容

-Vge(V) Rg(Ω)

(μH)

(μF)

50A

≥51

75A

≥33

-

0.47

100A

≥24

600V 150A

5―15

≥16

≤0.2

1.5

200A

≥9.1

≤0.16

2.2

300A

≥6.8

≤0.1

3.3

400A

≥4.7

≤0.08

4.7

50A

≥24

75A

≥16

-

0.47

100A

0.1μF

-

-

6MBI20*-060 20A

6MBI30*-060 30A

(Lm=0.5μH) 0.33μF

-

-

6MBI50*-060 50A

2MBI50*-060

1.0μF

-

-

0.33μF

-

-

6MBI75*-060

75A

2MBI75*-060

600V

6MBI100*-060

B

100A

-

(Lm=0.5μH)

2MBI25*-120 30A

0.022μF

-

-

6MBI50*-120 50A

0.068μF

-

-

2MBI75*-120 75A

1200V

B

2MBI100*-120 100A

(Lm=1.0μH)

2MBI150*-120 150A

0.1μF 0.47μF 0.56μF

220Ω/420W 56Ω/750W 47Ω/1.7kW

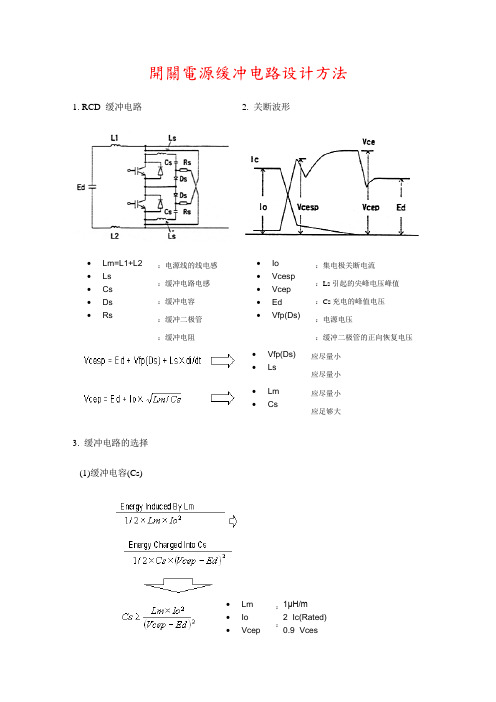

1. RCD 缓冲电路

缓冲电路设计方法

2. 关断波形

• Lm=L1+L2:电源线的线电感

• Ls • Cs

:缓冲电路电感

• Ds

:缓冲电容

• Rs

:缓冲二极管

:缓冲电阻

3. 缓冲电路的选择 (1)缓冲电容(Cs)

• Io

:集电极关断电流

• Vcesp • Vcep :Ls 引起的尖峰电压峰值

• Ed :Cs 充电的峰值电压

• Vfp(Ds):电源电压

:缓冲二极管的正向恢复电压

• Vfp(Ds)应尽量小

• Ls

应尽量小

• Lm • Cs

应尽量小 应足够大

• Lm :1μH/m • Io 2×Ic(Rated)

:

• Vcep 0.9×Vces

(2)缓冲电阻(Rs) 4. 缓冲电路类型

类型

A

B

C

• Ed :400V for AC 220V, 800V for AC 440V