AD9854中文数据手册.

AD9854中文数据手册

AD9854特征·300M内部时钟频率·可进行频移键控(FSK),二元相移键控(BPSK),相移键控(PSK),脉冲调频(CHIRP),振幅调制(AM)操作·正交的双通道12位D/A转换器·超高速比较器,3皮秒有效抖动偏差·外部动态特性:80 dB无杂散动态范围(SFDR)@ 100 MHz (±1 MHz) A OUT·4倍到20倍可编程基准时钟乘法器·两个48位可编程频率寄存器·两个14位可编程相位补偿寄存器·12位振幅调制和可编程的通断整形键控功能·单引脚FSK和BPSK数据输入接口·PSK功能可由I/O接口实现·具有线性和非线性的脉冲调频(FM CHIRP)功能,带有引脚可控暂停功能·具有过渡FSK功能·在时钟发生器模式下,有小于25 ps RMS抖动偏差·可自动进行双向频率扫描·能够对信号进行sin(x)/x校正·简易的控制接口:可配置为10MHZ串行接口,2线或3线SPI兼容接口或100MHZ 8位并行可编程接口·3.3V单电源供电·具有多路低功耗功能·单输入或差分输入时钟·小型80脚LQFP 封装应用·便携式频率特性分析仪·可编程时钟发生器·应用于雷达和扫频系统的脉冲调频信号源·测试和测量设备·商业和业余的射频(RF)发射机概述AD9854数字合成器是高集成度的器件,它采用先进的DDS技术,片内整合了两路高速、高性能正交D/A转换器通过数字化编程可以输出I、Q两路合成信号。

在高稳定度时钟的驱动下,AD9854将产生一高稳定的频率、相位、幅度可编程的正弦和余弦信号,作为本振用于通信,雷达等方面。

AD9854的DDS核具有48位的频率分辨率(在300M系统时钟下,频率分辨率可达1uHZ)。

AD9854中文数据手册要点

AD9854特征·300M内部时钟频率·可进行频移键控(FSK),二元相移键控(BPSK),相移键控(PSK),脉冲调频(CHIRP),振幅调制(AM)操作·正交的双通道12位D/A转换器·超高速比较器,3皮秒有效抖动偏差·外部动态特性:80 dB无杂散动态范围(SFDR)@ 100 MHz (±1 MHz) A OUT·4倍到20倍可编程基准时钟乘法器·两个48位可编程频率寄存器·两个14位可编程相位补偿寄存器·12位振幅调制和可编程的通断整形键控功能·单引脚FSK和BPSK数据输入接口·PSK功能可由I/O接口实现·具有线性和非线性的脉冲调频(FM CHIRP)功能,带有引脚可控暂停功能·具有过渡FSK功能·在时钟发生器模式下,有小于25 ps RMS抖动偏差·可自动进行双向频率扫描·能够对信号进行sin(x)/x校正·简易的控制接口:可配置为10MHZ串行接口,2线或3线SPI兼容接口或100MHZ 8位并行可编程接口·3.3V单电源供电·具有多路低功耗功能·单输入或差分输入时钟·小型80脚LQFP 封装应用·便携式频率特性分析仪·可编程时钟发生器·应用于雷达和扫频系统的脉冲调频信号源·测试和测量设备·商业和业余的射频(RF)发射机概述AD9854数字合成器是高集成度的器件,它采用先进的DDS技术,片内整合了两路高速、高性能正交D/A转换器通过数字化编程可以输出I、Q两路合成信号。

在高稳定度时钟的驱动下,AD9854将产生一高稳定的频率、相位、幅度可编程的正弦和余弦信号,作为本振用于通信,雷达等方面。

AD9854的DDS核具有48位的频率分辨率(在300M系统时钟下,频率分辨率可达1uHZ)。

翻译AD9854芯片资料

AD9854芯片资料一、芯片特征:AD9854拥有300MHZ内部时钟频率,可以进行FSK、BPSK、PSK、chirp、AM等的操作,双综合12bit数模转换器,超高速,3ps rms 抖动比较,它还有出色的动态性能,4到20倍可编程时钟乘法器,双48bit可编程频率寄存器,双14比特可编程相位寄存器,12bit可编程调幅以及输出开/关键控功能,单管脚FSK、BPSK数据接口,PSK可输入/输出接口,具有单管脚频率保持功能的线性或者非线性脉冲等一些优良特征。

AD9854数字合成器是一个利用DDS技术、两个内部高速高性能正交DACs 控制数字可编程输入输出的综合器件。

当给AD9854加上一个确定时钟时,它可以生成高度稳定、频率-相位-幅度可编程的sine或者cosine输出,这些特点可以被用于灵敏的LO以及雷达和其他一些应用。

AD9854具有创新意义的高速DDS 核心提供48bit的频率分辨率。

保持17bit确保了SFDR性能优良。

AD9854的电路结构允许同步正交输出信号的频率最高达到150MHZ。

而且这些信号的数字调频可以最高达到每秒1亿次。

正弦波输出可以转换成正交波,而这要通过内部比较器来实现,这种转换主要应用于灵敏时钟生成。

AD9854提供两个14bit的相位寄存器和一个单脚用于BPSK控制。

对于高阶PSK操作,I/O接口可以用于相位变换。

拥有两个DDS结构的12bit的I和Q DACs提供出色的宽带和窄带输出SFDR。

如果正交功能功能不适宜,那么Q DAC也可以配置成一个用户可编程的控制DAC。

当配置比较器的时候,12bit的控制DAC使高速时钟生成器应用中的静态循环控制更加便利。

两个12bit的数字乘法器允许可编程的幅度调制、开/关输出键控以及精确的正交输出幅度控制。

为了使宽带宽频全面应用更加方便,AD9854采用了脉冲功能控制。

AD9854的内部可编程4倍到20倍REFCLK乘法器电路生成300MHZ 的系统时钟,而时钟源是来自于一个外部低频时钟。

AD9854对照翻译

FEATURES300 MHz internal clock rateFSK, BPSK, PSK, chirp, AM operationDual integrated 12-bit digital-to-analog converters (DACs) Ultrahigh speed comparator, 3 ps rms jitterExcellent dynamic performance80 dB SFDR at 100 MHz (±1 MHz) AOUT4× to 20× programmable reference clock multiplierDual 48-bit programmable frequency registersDual 14-bit programmable phase offset registers12-bit programmable amplitude modulation andon/off output shaped keying functionSingle-pin FSK and BPSK data interfacesPSK capability via input/output interfaceLinear or nonlinear FM chirp functions with single-pin frequency hold functionFrequency-ramped FSK<25 ps rms total jitter in clock generator mode特征300 MHz内部时钟速率支持FSK, BPSK, PSK, chirp, AM调制集成双路12位数/模转换器(DAC)超高速比较器,3个PS RMS抖动出色的动态性能80dB的SFDR在100 MHz(±1 MHz)的AOUT4 ×20×可编程参考时钟倍频器双48位可编程频率寄存器双通道,14位可编程相位偏移寄存器12位可编程振幅调制ON / OFF输出形键控功能单引脚FSK和BPSK的数据接口通过输入/输出接口实现PSK功能单线实现线性或非线性的调频功能频率暂停功能频率ramped的FSK<25 ps的均方根时钟发生器模式的总抖动Automatic bidirectional frequency sweepingSin(x)/x correctionSimplified control interfaces10 MHz serial 2- or 3-wire SPI compatible100 MHz parallel 8-bit programming3.3 V single supplyMultiple power-down functionsSingle-ended or differential input reference clockSmall, 80-lead LQFP or TQFP with exposed padAPPLICATIONSAgile, quadrature LO frequency synthesisProgrammable clock generatorsFM chirp source for radar and scanning systemsTest and measurement equipmentCommercial and amateur RF exciters双向自动扫频sin(x)/ x修正简化的控制接口兼容10 MHz串行2 或3线SPI总线100兆赫并行8位总线3.3 V单电源供电多重省电功能参考时钟可单端或差分输入小型,80引脚LQFP或带有散热焊盘的TQFP封装应用正交LO频率合成可编程时钟发生器调频雷达和扫描系统的线性调频源测试与测量设备商业及业余射频发射器目录特点................................................. .............................................一应用................................................. ......................................一功能框图............................................... ...............一修订历史................................................ ...............................三一般描述................................................ . (4)规格................................................. (5)绝对最大额定值............................................... . (8)热阻................................................ . (8)测验等级说明.............................................. . (8)防静电提示................................................ . (8)引脚配置和功能说明 (9)典型性能特征 (12)典型应用................................................ .. (16)操作原理............................................... .. (19)操作模式............................................... .. (19)使用AD9854 ............................................... (29)内部和外部更新时钟 (29)ON / OFF输出形键控(侨丰) (29)I和Q数模转换器.............................................. .. (30)控制DAC ................................................ . (30)逆Sinc函数............................................... .. (31)REFCLK乘法器 (31)编程AD9854 ............................................... . (32)主复位................................................ (32)并行I / O操作............................................. (34)串行端口I / O操作............................................ .. (34)一般操作的串行接口 (36)指令字节................................................ .. (37)串行接口引脚说明 (37)串口操作的注意事项............................................. (37)的MSB / LSB的转移.............................................. (38)控制寄存器的说明............................................... .. (38)功耗和散热考虑 (40)热阻抗................................................ . (40)结温事项 (40)评价工作条件 (41)热增强型封装安装指南 (41)评估板................................................ . (42)评估板说明............................................... (42)一般操作说明 (42)使用提供的软件.............................................. (44)支持................................................. (44)外形尺寸................................................ .. (52)订购指南................................................ .. (52)GENERAL DESCRIPTIONThe AD9854 digital synthesizer is a highly integrated device that uses advanced DDS technology, coupled with two internal high speed, high performance quadrature DACs to form a digitally programmable I and Q synthesizer function. When referenced to an accurate clock source, the AD9854 generates highly stable, frequency-phase, amplitude-programmable sine and cosine outputs that can be used as an agile LO in communications, radar, and many other applications. The innovative high speed DDS core of the AD9854 provides 48-bit frequency resolution (1 μHz tuning resolution with 300 MHz SYSCLK). Maintaining 17 bits ensures excellent SFDR.概述在AD9854数字频率合成器是一种高度集成的器件,采用先进的DDS技术,具有两个内部耦合高速,高性能正交数模转换器以实现数字可编程的I/Q合成功能。

AD9854中文数据手册

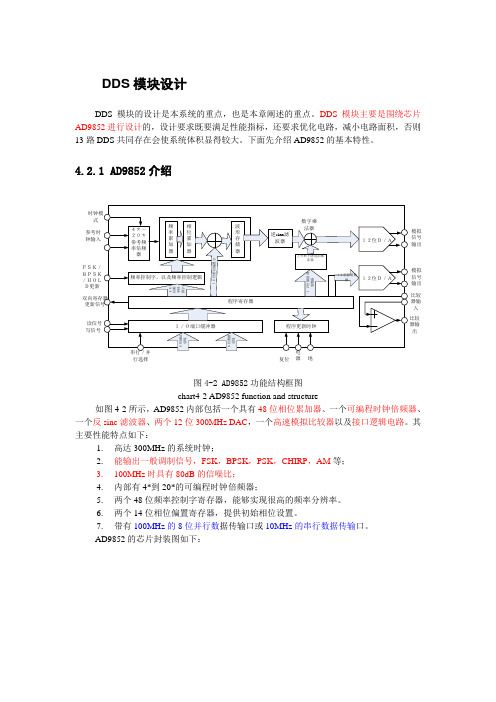

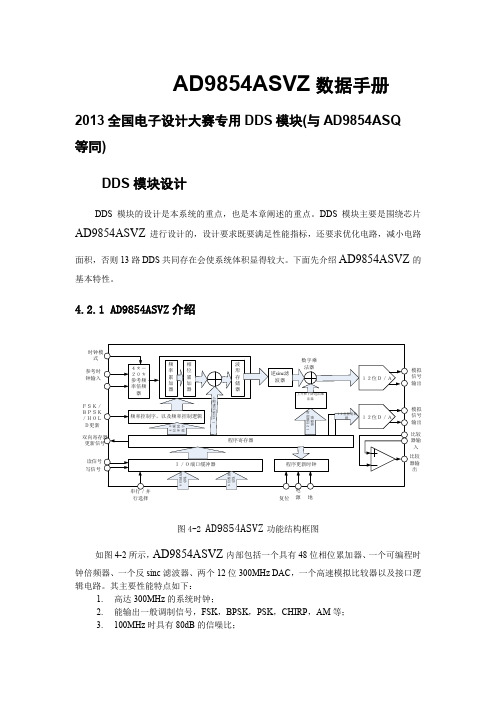

DDS模块设计DDS模块的设计是本系统的重点,也是本章阐述的重点。

DDS模块主要是围绕芯片AD9852进行设计的,设计要求既要满足性能指标,还要求优化电路,减小电路面积,否则13路DDS共同存在会使系统体积显得较大。

下面先介绍AD9852的基本特性。

4.2.1 AD9852介绍式参考时钟输入D更新读信号写信号行选择复位源地比较器输入模拟信号输出模拟信号输出比较器输出图4-2 AD9852功能结构框图chart4-2 AD9852 function and structure如图4-2所示,AD9852内部包括一个具有48位相位累加器、一个可编程时钟倍频器、一个反sinc滤波器、两个12位300MHz DAC,一个高速模拟比较器以及接口逻辑电路。

其主要性能特点如下:1.高达300MHz的系统时钟;2.能输出一般调制信号,FSK,BPSK,PSK,CHIRP,AM等;3.100MHz时具有80dB的信噪比;4.内部有4*到20*的可编程时钟倍频器;5.两个48位频率控制字寄存器,能够实现很高的频率分辨率。

6.两个14位相位偏置寄存器,提供初始相位设置。

7.带有100MHz的8位并行数据传输口或10MHz的串行数据传输口。

AD9852的芯片封装图如下:图4-3 AD9852芯片封装图chart4-3 AD9852 chip encapsulationAD9852有40个程序寄存器,对AD9852的控制就是对这些程序寄存器写数据实现的。

表4-1 AD9852并行接口寄存器功能并行地址寄存器功能默认值0x00 0x01 相位寄存器#1<13:8>(15,14位无效)相位寄存器#1<7:0>0x000x000x02 0x03 相位寄存器#2<13:8>(15,14位无效)相位寄存器#2<7:0>0x000x000x04 0x05 0x06 0x07 0x08 0x09 频率转换字#1<47:40>频率转换字#1<39:32>频率转换字#1<31:24>频率转换字#1<23:16>频率转换字#1<15:8>频率转换字#1<7:0>0x000x000x000x000x000x000x0A 频率转换字#1<47:40> 0x00表4-2 AD9852控制寄存器功能通过并行总线将数据写入程序寄存器时,实际上只是暂存在I/O缓冲区中,只有提供更新信号,这些数据才会更新到程序寄存器。

高性能DDS芯片AD9854结构功能简介

高性能DDS芯片AD9854结构功能简介作者:李津生丁敏来源:《电子世界》2012年第14期【摘要】本文介绍了ADI公司的高性能DDS芯片AD9854。

AD9854是一款CMOS工艺的300 MSPS正交完整DDS芯片,在现代波形发生与合成、通信领域有着广泛的应用。

本文介绍了DDS技术的基本原理及AD9854内部结构级功能。

【关键词】DDS;AD9854;DDS核;反辛格滤波器1.引言在现代电子技术中,波形的产生与合成以及基于此的调制应用无处不在。

在直接数字式频率合成器(Direct Digital Synthe-sizer,DDS)技术出现前,一般采用模拟方法,如晶体管振荡器、锁相环等电路来实现。

模拟方法可以产生很高的频率,但是不够精确、不易自动控制。

DDS技术的出现和快速发展为这类应用提供了一种低成本、低功耗、高分辨率的解决方案。

本文介绍了DDS技术的基本原理和ADI公司的高性能DDS芯片系列中的AD9854的结构与功能。

2.DDS技术原理DDS技术可以通过数字化的方法产生所需信号的一种技术。

正弦信号的表达式为:(1)可以看出幅度的变化与时间并不成正比,但是角度的变化与幅度是成正比的,我们从单位圆可以解释,如图1所示。

图中表达式为:(2)正弦波的t时刻对应值即为单位圆半径在纵轴上的投影,随是成线性变化的。

由式(2)可得:(3)在实际器件中,,代入上式则有:(4)DDS器件中的相位累加器西欧那个0-2循环计数,设相位累加器为N位,则。

代入式(4)我们即可得到最终DDS输出频率为:(5)式中,为输出频率,FTW为频率字(即),为系统时钟频率,N为相位累加器长度。

从式(5)我们可以看出,当FTW取最小值1时,输出频率最小,也即DDS器件的分辨率为:(6)输出最大频率由采样定理决定,为:(7)3.AD9854的结构与功能AD9854是ADI公司的一款CMOS工艺300MSPS正交的完整DDS芯片。

AD9854是一款高度集成的芯片,采用先进的DDS技术,内部集成了300MHz的DDS核(ASVZ系列为300MHz,ASTZ系列为200MHz)、高速高性能双路正交DAC、反辛格滤波器、双路48位频率寄存器、双路14位相位寄存器、4~20倍时钟倍频器、调幅模块和3ps均方根抖动超高速比较器。

AD9854ASVZ中文数据手册

相位寄存器#2<13:8>(15,14 位无效) 相位寄存器#2<7:0> 频率转换字#1<47:40> 频率转换字#1<39:32> 频率转换字#1<31:24> 频率转换字#1<23:16> 频率转换字#1<15:8> 频率转换字#1<7:0> 频率转换字#1<47:40> 频率转换字#1<39:32> 频率转换字#1<31:24> 频率转换字#1<23:16> 频率转换字#1<15:8> 频率转换字#1<7:0> 三角频率字<47:40> 三角频率字<39:32> 三角频率字<31:24> 三角频率字<23:16> 三角频率字<15:8> 三角频率字<7:0> 更新时钟计数器<31:24> 更新时钟计数器<23:16> 更新时钟计数器<15:8> 更新时钟计数器<7:0> 边沿速率计数器<19:16>(23,22,21,20 不起作用) 边沿速率计数器<15:8> 边沿速率计数器<7:0> 节电控制 时钟倍频控制器 DDS 模式控制与累加器清零控制 传输模式,和 OSK 控制 输出幅度乘法器 I<11:8>(15,14,13,12 不起作用) 输出幅度乘法器 I<7:0> 输出幅度乘法器 Q<11:8>(15,14,13,12 不起作用) 输出幅度乘法器 Q<7:0> 输出边沿变化率控制器<7:0> QDAC,Q 通道 D/A 输入<11:8> QDAC,Q 通道 D/A 输入<7:0>

ad9850中文资料

摘要:介绍了美国AD公司采用先进的直接数字频率合成(DDS) 技术推出的高集成度频率合成器AD9850 的工作原理、主要特点及其与MCS51 单片机的接口,并给出了接口电路图和部分源程序。

关键词:直接数字频率合成(DDS) 控制字控制时序接口AD98501 AD9850 简介随着数字技术的飞速发展, 用数字控制方法从一个参考频率源产生多种频率的技术,即直接数字频率合成(DDS) 技术异军突起。

美国AD公司推出的高集成度频率合成器AD9850 便是采用DDS 技术的典型产品之一。

AD9850 采用先地蝗CMOS 工艺, 其功耗在3.3V 供电时仅为155mW,扩展工业级温度范围为-40~80℃, 采用28脚SSOP 表面封装形式。

AD9850 的引脚排列如图1所示,图2为其组成框图。

图2中层虚线内是一个完整的可编程DDS 系统,外层虚线内包含了AD9850 的主要组成部分。

AD9850 内含可编程DDS 系统和高速比较器,能实现全数字编程控制的频率合成。

可编程DDS 系统的核心是相位累加器,它由一个加法器和一个N位相位寄存器组成,N一般为24~32。

每来一个外部参考时钟,相位寄存器便以步长M 递加。

相位寄存器的输出与相位控制字相加后可输入到正弦查询表地址上。

正弦查询表包含一个正弦波周期的数字幅度信息,每一个地址对应正弦波中0°~360°范围的一个相位点。

查询表把输入地址的相位信息映射成正弦波幅度信号,然后驱动DAC 以输出模式量。

相位寄存器每过2N/M 个外部参考时钟后返回到初始状态一次,相位地正弦查询表每消费品一个循环也回到初始位置,从而使整个DDS 系统输出一个正弦波。

输出的正弦波周期To=Tc2N/M ,频率fout=Mfc/2N,Tc、fc分别为外部参考时钟的周期和频率。

AD9850 采用32位的相位累加器将信号截断成14位输入到正弦查询表,查询表的输出再被截断成10位后输入到DA C,DAC 再输出两个互补的电流。

芯片9854中文资料

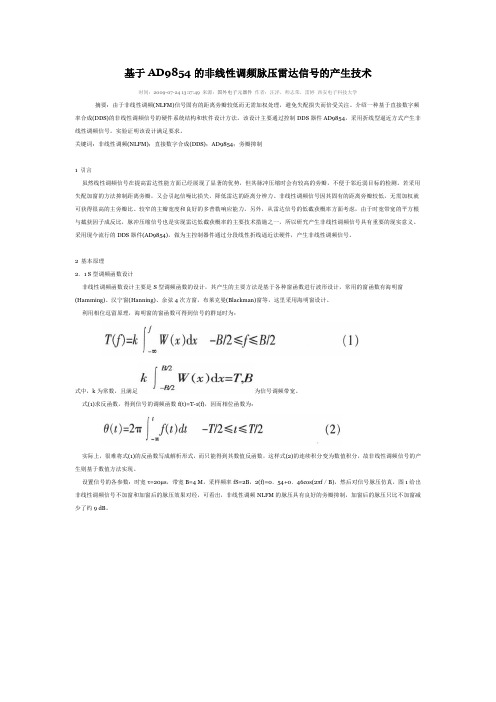

基于AD9854的非线性调频脉压雷达信号的产生技术时间:2009-07-24 13:17:49 来源:国外电子元器件作者:汪洋,师志荣,雷婷西安电子科技大学摘要:由于非线性调频(NLFM)信号固有的距离旁瓣较低而无需加权处理,避免失配损失而倍受关注。

介绍一种基于直接数字频率合成(DDS)的非线性调频信号的硬件系统结构和软件设计方法。

该设计主要通过控制DDS器件AD9854,采用折线型逼近方式产生非线性调频信号。

实验证明该设计满足要求。

关键词:非线性调频(NLFM);直接数字合成(DDS);AD9854;旁瓣抑制1 引言虽然线性调频信号在提高雷达性能方面已经展现了显著的优势,但其脉冲压缩时会有较高的旁瓣,不便于邻近弱目标的检测。

若采用失配加窗的方法抑制距离旁瓣,又会引起信噪比损失,降低雷达的距离分辨力。

非线性调频信号因其固有的距离旁瓣较低,无需加权就可获得很高的主旁瓣比、较窄的主瓣宽度和良好的多普勒响应能力。

另外,从雷达信号的低截获概率方面考虑,由于时宽带宽的平方根与截获因子成反比,脉冲压缩信号也是实现雷达低截获概率的主要技术措施之一,所以研究产生非线性调频信号具有重要的现实意义。

采用现今流行的DDS器件(AD9854),做为主控制器件通过分段线性折线逼近法硬件,产生非线性调频信号。

2 基本原理2.1 S型调频函数设计非线性调频函数设计主要是S型调频函数的设计,其产生的主要方法是基于各种窗函数进行波形设计,常用的窗函数有海明窗(Hamming)、汉宁窗(Hanning)、余弦4次方窗,布莱克曼(Blackman)窗等,这里采用海明窗设计。

利用相位逗留原理,海明窗的窗函数可得到信号的群延时为:式中,k为常数,且满足为信号调频带宽。

式(1)求反函数,得到信号的调频函数f(t)=T-1(f),因而相位函数为:实际上,很难将式(1)的反函数写成解析形式,而只能得到其数值反函数,这样式(2)的连续积分变为数值积分,故非线性调频信号的产生则基于数值方法实现。

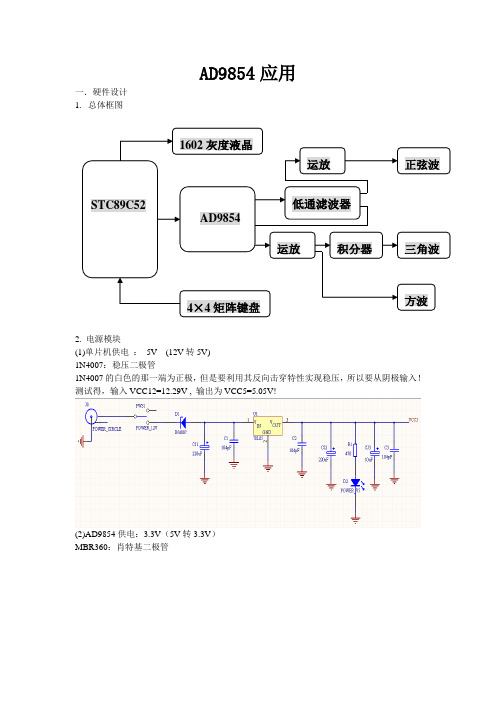

AD9854应用

AD9854应用一.硬件设计 1. 总体框图2. 电源模块(1)单片机供电 : 5V (12V 转5V) 1N4007:稳压二极管1N4007的白色的那一端为正极,但是要利用其反向击穿特性实现稳压,所以要从阴极输入! 测试得,输入VCC12=12.29V , 输出为VCC5=5.05V!(2)AD9854供电:3.3V (5V 转3.3V ) MBR360:肖特基二极管3. 单片机(1)复位(2)晶振(11.0592M )(3)矩阵键盘(4)1602液晶(5)串行下载(6)单片机稳压供电问题参考AD9854的技术文档中的评估板的设计,在VCC5端口并联一个10uF极性电容和8个0.1uF的非极性电容!4. AD9854首先,先仔细阅读AD9854的每个管脚的具体作用的介绍,如下:引脚名称引脚及配置D7-D0 8 位双向并行编程数据输入。

只用于并行编程模式。

DVDD 连接到数字电路的供应电压。

通常为3.3V。

DGND 连接到数字电路的地。

功能同AGND。

NC 无内部连接。

A5-A0 编程寄存器的6位并行地址输入。

只用于并行编程模式。

当使用串行编程模式时A0,A1,A2使用它们各自的另一个功能,如下介绍:A2/IO RESET 串行通讯总线的I/O复位信号。

由于不合适的编程协议而造成无应答就会产生此复位信号。

用这种方式复位串行总线不会影响之前编好的程序,也不会唤醒“默认”编程值。

此脚工作状态为高。

A1/SDO 当使用3线串行通讯模式时的单向串行数据输出。

A0/SDIO 当使用2线串行通讯模式时的双向串行数据输入/输出。

在设计中只用其并型模式。

设计中将其与MSP430F149的P4口相连。

I/O UD CLK 双向I/O刷新时钟。

用作控制寄存器选择方向。

若选择作为输入,则会在上升沿时把I/O端口缓冲器的内容传送到程序寄存器。

若作为输出(默认),则在8个系统时钟周期期间的输出脉冲(低到高)就表明一个内部频率刷新已经发生了。

AD9850 datasheet 数据手册

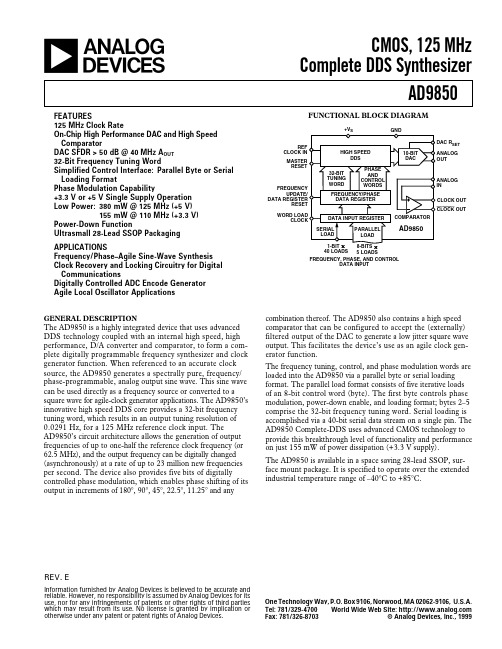

REV.EInformation furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices.aCMOS, 125 MHzComplete DDS SynthesizerAD9850FUNCTIONAL BLOCK DIAGRAMCLOCK OUTOUTSETREF CLOCK IN MASTER RESETFREQUENCY, PHASE, AND CONTROLDATA INPUTGENERAL DESCRIPTIONThe AD9850 is a highly integrated device that uses advanced DDS technology coupled with an internal high speed, high performance, D/A converter and comparator, to form a com-plete digitally programmable frequency synthesizer and clock generator function. When referenced to an accurate clock source, the AD9850 generates a spectrally pure, frequency/phase-programmable, analog output sine wave. This sine wave can be used directly as a frequency source or converted to a square wave for agile-clock generator applications. The AD9850’s innovative high speed DDS core provides a 32-bit frequency tuning word, which results in an output tuning resolution of 0.0291 Hz, for a 125 MHz reference clock input. TheAD9850’s circuit architecture allows the generation of output frequencies of up to one-half the reference clock frequency (or 62.5 MHz), and the output frequency can be digitally changed (asynchronously) at a rate of up to 23 million new frequencies per second. The device also provides five bits of digitallycontrolled phase modulation, which enables phase shifting of its output in increments of 180°, 90°, 45°, 22.5°, 11.25° and anycombination thereof. The AD9850 also contains a high speed comparator that can be configured to accept the (externally)filtered output of the DAC to generate a low jitter square wave output. This facilitates the device’s use as an agile clock gen-erator function.The frequency tuning, control, and phase modulation words are loaded into the AD9850 via a parallel byte or serial loading format. The parallel load format consists of five iterative loads of an 8-bit control word (byte). The first byte controls phase modulation, power-down enable, and loading format; bytes 2–5comprise the 32-bit frequency tuning word. Serial loading is accomplished via a 40-bit serial data stream on a single pin. The AD9850 Complete-DDS uses advanced CMOS technology to provide this breakthrough level of functionality and performance on just 155 mW of power dissipation (+3.3 V supply).The AD9850 is available in a space saving 28-lead SSOP, sur-face mount package. It is specified to operate over the extended industrial temperature range of –40°C to +85°C.FEATURES125 MHz Clock RateOn-Chip High Performance DAC and High Speed ComparatorDAC SFDR > 50 dB @ 40MHz A OUT 32-Bit Frequency Tuning WordSimplified Control Interface:Parallel Byte or Serial Loading FormatPhase Modulation Capability+3.3 V or +5 V Single Supply Operation Low Power:380 mW @ 125 MHz (+5 V)155 mW @ 110 MHz (+3.3 V)Power-Down FunctionUltrasmall 28-Lead SSOP PackagingAPPLICATIONSFrequency/Phase–Agile Sine-Wave Synthesis Clock Recovery and Locking Circuitry for Digital CommunicationsDigitally Controlled ADC Encode Generator Agile Local Oscillator ApplicationsOne Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.Tel: 781/329-4700World Wide Web Site: Fax: 781/326-8703© Analog Devices, Inc., 1999AD9850BRS ParameterTemp Test LevelMin Typ MaxUnitsCLOCK INPUT CHARACTERISTICS Frequency Range +5 V Supply FullIV 1125MHz +3.3 V SupplyFull IV 1110MHz Pulsewidth High/Low +5 V Supply +25°C IV 3.2ns +3.3 V Supply +25°CIV4.1nsDAC OUTPUT CHARACTERISTICS Full-Scale Output Current R SET = 3.9 k Ω+25°C V 10.24mA R SET = 1.95 k Ω+25°C V 20.48mA Gain Error+25°C I –10+10% FS Gain Temperature Coefficient Full V 150ppm/°C Output Offset+25°C I 10µA Output Offset Temperature Coefficient Full V 50nA/°C Differential Nonlinearity +25°C I 0.50.75LSB Integral Nonlinearity+25°C I 0.51LSB Output Slew Rate (50Ω, 2 pF Load)+25°C V 400V/µs Output Impedance +25°C IV 50120k ΩOutput Capacitance +25°C IV 8pF Voltage Compliance+25°C I 1.5V Spurious-Free Dynamic Range (SFDR):Wideband (Nyquist Bandwidth)1 MHz Analog Out +25°C IV 6372dBc 20 MHz Analog Out +25°C IV 5058dBc 40 MHz Analog Out +25°C IV 4654dBc Narrowband40.13579 MHz ± 50 kHz +25°C IV 80dBc 40.13579 MHz ± 200 kHz+25°C IV 77dBc 4.513579 MHz ± 50 kHz/20.5 MHz CLK +25°C IV 84dBc 4.513579 MHz ± 200 kHz/20.5 MHz CLK +25°C IV 84dBc COMPARATOR INPUT CHARACTERISTICS Input Capacitance +25°C V 3pF Input Resistance +25°C IV 500k ΩInput Current+25°C I –12+12µA Input Voltage Range +25°C IV 0V DD V Comparator Offset*Full VI 3030mV COMPARATOR OUTPUT CHARACTERISTICS Logic “1” Voltage +5 V Supply Full VI +4.8V Logic “1” Voltage +3.3 V Supply Full VI +3.1V Logic “0” VoltageFull VI +0.4V Propagation Delay, +5 V Supply (15 pF Load)+25°C V 5.5ns Propagation Delay, +3.3 V Supply (15 pF Load)+25°C V 7ns Rise/Fall Time, +5 V Supply (15 pF Load)+25°C V 3ns Rise/Fall Time, +3.3 V Supply (15 pF Load)+25°C V 3.5ns Output Jitter (p-p)+25°C V 80ps CLOCK OUTPUT CHARACTERISTICS Clock Output Duty Cycle (Clk Gen. Config.)+25°CIV50 ± 10%REV. E–2–(V S= +5 V ؎ 5% except as noted, RSET = 3.9 k ⍀)AD9850–SPECIFICATIONSAD9850AD9850BRSParameter Temp Test Level Min Typ Max Units CMOS LOGIC INPUTS (Including CLKIN)Logic “1” Voltage, +5 V Supply+25°C I 3.5V Logic “1” Voltage, +3.3 V Supply+25°C I 3.0V Logic “0” Voltage+25°C I0.4V Logic “1” Current+25°C I12µA Logic “0” Current+25°C I12µA Input Capacitance+25°C V3pF POWER SUPPLY (A OUT = 1/3 CLKIN)+V S Current @:62.5 MHz Clock, +3.3 V Supply Full VI3048mA110 MHz Clock, +3.3 V Supply Full VI4760mA62.5 MHz Clock, +5 V Supply Full VI4464mA125 MHz Clock, +5 V Supply Full VI7696mAP DISS @:62.5 MHz Clock, +3.3 V Supply Full VI100160mW110 MHz Clock, +3.3 V Supply Full VI155200mW62.5 MHz Clock, +5 V Supply Full VI220320mW125 MHz Clock, +5 V Supply Full VI380480mWP DISS Power-Down Mode+5 V Supply Full V30mW +3.3 V Supply Full V10mW NOTES*Tested by measuring output duty cycle variation.Specifications subject to change without notice.TIMING CHARACTERISTICS*(V S = +5 V ؎ 5% except as noted, R SET = 3.9 k⍀)AD9850BRSParameter Temp Test Level Min Typ Max Unitst DS(Data Setup Time)Full IV 3.5nst DH(Data Hold Time)Full IV 3.5nst WH(W_CLK min. Pulsewidth High)Full IV 3.5nst WL(W_CLK min. Pulsewidth Low)Full IV 3.5nst WD(W_CLK Delay After FQ_UD)Full IV7.0nst CD(CLKIN Delay After FQ_UD)Full IV 3.5nst FH(FQ_UD High)Full IV7.0nst FL(FQ_UD Low)Full IV7.0nst CF(Output Latency from FQ_UD)Frequency Change Full IV18CLKIN Cycles Phase Change Full IV13CLKIN Cycles t FD(FQ_UD Min. Delay After W_CLK)Full IV7.0nst RH(CLKIN Delay After RESET Rising Edge)Full IV 3.5nst RL(RESET Falling Edge After CLKIN)Full IV 3.5nst RS(Minimum RESET Width)Full IV5CLKIN Cycles t OL(RESET Output Latency)Full IV13CLKIN Cycles t RR(Recovery from RESET)Full IV2CLKIN Cycles Wake-Up Time from Power-Down Mode+25°C V5µsNOTES*Control functions are asynchronous with CLKIN.Specifications subject to change without notice.REV. E–3–AD9850–4–REV. EABSOLUTE MAXIMUM RATINGS*Maximum Junction Temperature . . . . . . . . . . . . . . . +165°C V DD . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . +6 V Digital Inputs . . . . . . . . . . . . . . . . . . . . . . . . . –0.7 V to +V S Digital Output Continuous Current . . . . . . . . . . . . . . . 5 mA DAC Output Current . . . . . . . . . . . . . . . . . . . . . . . . . 30 mA Storage Temperature . . . . . . . . . . . . . . . . . . –65°C to +150°C Operating Temperature . . . . . . . . . . . . . . . . .–40°C to +85°C Lead Temperature (Soldering 10 sec) . . . . . . . . . . . . +300°C SSOP θJA Thermal Impedance . . . . . . . . . . . . . . . . . . 82°C/W*Absolute maximum ratings are limiting values, to be applied individually, and beyond which the serviceability of the circuit may be impaired. Functional operability under any of these conditions is not necessarily implied. Exposure of absolute maximum rating conditions for extended periods of time may affect device reliability.EXPLANATION OF TEST LEVELSTest Level I –100% Production Tested.III –Sample Tested Only.IV –Parameter is guaranteed by design and characterizationtesting.V –Parameter is a typical value only.VI –All devices are 100% production tested at +25°C.100% production tested at temperature extremes for military temperature devices; guaranteed by design and characterization testing for industrial devices.CAUTIONESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000V readily accumulate on the human body and test equipment and can discharge without detection.Although the AD9850 features proprietary ESD protection circuitry, permanent damage may occur on devices subjected to high energy electrostatic discharges. Therefore, proper E SD precautions are recommended to avoid performance degradation or loss of functionality.Application Note : Users are cautioned not to apply digital input signals prior to power-up of this device. Doing so may r esult in a latch-up condition.ORDERING GUIDEModel Temperature Range Package Description Package Option AD9850BRS–40°C to +85°CShrink Small Outline (SSOP)RS-28AD9850–5–REV. ETable I.Lead Function DescriptionsPin No.Mnemonic Function4–1,D0–D78-Bit Data Input. This is the 8-bit data port for iteratively loading the 32-bit frequency and 8-bit phase/28–25control word. D7 = MSB; D0 = LSB. D7 (Pin 25) also serves as the input pin for the 40-bit serial data word.5, 24DGND Digital Ground. These are the ground return leads for the digital circuitry.6, 23DVDD Supply Voltage Leads for digital circuitry.7W_CLK Word Load Clock. This clock is used to load the parallel or serial frequency/phase/control words.8FQ_UD Frequency Update. On the rising edge of this clock, the DDS will update to the frequency (or phase)loaded in the data input register, it then resets the pointer to Word 0.9CLKIN Reference Clock Input. This may be a continuous CMOS-level pulse train or sine input biased at 1/2V supply. The rising edge of this clock initiates operation.10, 19AGND Analog Ground. These leads are the ground return for the analog circuitry (DAC and comparator).11, 18AVDD Supply Voltage for the analog circuitry (DAC and comparator).12R SETThis is the DAC’s external R SET connection. This resistor value sets the DAC full-scale output current. For normal applications (F S I OUT = 10 mA ), the value for R SET is 3.9 k Ω connected to ground. The R SET /I OUT relationship is: I OUT = 32 (1.248 V/R SET ).13QOUTB Output Complement. This is the comparator’s complement output.14QOUT Output True. This is the comparator’s true output.15VINN Inverting Voltage Input. This is the comparator’s negative input.16VINPNoninverting Voltage Input. This is the comparator’s positive input.17DACBL (NC)DAC Baseline. This is the DAC baseline voltage reference; this lead is internally bypassed and shouldnormally be considered a “no connect” for optimum performance.20IOUTB The Complementary Analog Output of the DAC.21IOUT Analog Current Output of the DAC.22RESETReset. This is the master reset function; when set high it clears all registers (except the input register) and the DAC output will go to Cosine 0 after additional clock cycles—see Figure 19.PIN CONFIGURATIONSD3D7 MSB/SERIAL LOAD D6D5D4D2D1LSB D0RESETDVDDDGND DGND DVDD W CLK FQ UD CLKINAGND AGND IOUTB IOUTAVDD R SET QOUTB QOUT AVDD VINNVINP DACBL (NC)NC = NO CONNECTRBW # 100Hz START 0HzVBW 100HzATN # 30dB SWP 762 secSTOP 62.5MHz Figure 1.SFDR, CLKIN = 125 MHz/f OUT = 1 MHzRBW # 300Hz START 0HzVBW 300Hz ATN # 30dBSWP 182.6 sec STOP 62.5MHzFigure 2.SFDR, CLKIN = 125 MHz/f OUT= 41 MHzCh 1 500mV ⍀M 20.0ns Ch 1 1.58V D 500ps Runs AfterFigure 3.Typical Comparator Output Jitter, AD9850Configured as Clock Generator w/42 MHz LP Filter (40 MHz A OUT /125 MHz CLKIN)AD9850–Typical Performance Characteristics–6–REV. ERBW # 300Hz START 0HzVBW 300HzATN # 30dB SWP 182.6 secSTOP 62.5MHzFigure 4.SFDR, CLKIN = 125 MHz/f OUT = 20 MHzRBW # 3Hz CENTER 4.513579MHzVBW 3Hz ATN # 20dBSWP 399.5 sec SPAN 400kHzFigure 5.SFDR, CLKIN = 20.5 MHz/f OUT = 4.5 MHzOFFSET FROM 5MHz CARRIER – Hz–––––––––––100100k1kd B c10k Figure 6. Output Residual Phase Noise (5 MHz A OUT /125 MHz CLKIN)AD9850–7–REV. ECh1 1.00V ⍀ M 1.00ns Ch 1 1.74V Figure parator Output Rise Time (5 V Supply/15 pF Load)CLKIN – MHz140204060801001206852S F D R – d B66605856546462Figure 8.SFDR vs. CLKIN Frequency (A OUT = 1/3 of CLKIN)FREQUENCY OUT – MHz9080304010S U P P L Y C U R R E N T – m A203070605040Figure 9.Supply Current vs. A OUT Frequency (CLKIN = 125/110 MHz for 5 V/3.3 V Plot)Ch1 1.00V ⍀ M 1.00ns Ch 1 1.74VFigure parator Output Fall Time (5 V Supply/15 pF Load)CLOCK FREQUENCY – MHz0140204060801001209010S U P P L Y C U R R E N T –m A80504030207060Figure 11.Supply Current vs. CLKIN Frequency (A OUT = 1/3 of CLKIN)DAC I OUT – mA205S F D R – d B1015Figure 12.SFDR vs. DAC I OUT (A OUT = 1/3 of CLKIN)AD9850–8–REV. E5-POLE ELLIPTICALFigure 13.Basic AD9850 Clock Generator Application with Low-Pass FilterFigure 14.AD9850 Clock Generator Application in a Spread-Spectrum Receivera.Frequency/Phase –Agile Local Oscillatorb.Frequency/Phase –Agile Reference for PLLREFRFc.Digitally-Programmable ”Divide-by-N “ Function in PLLFigure 15.AD9850 Complete-DDS Synthesizer in Frequency Up-Conversion ApplicationsTHEORY OF OPERATION AND APPLICATIONThe AD9850 uses direct digital synthesis (DDS) technology, in the form of a numerically controlled oscillator, to generate a frequency/phase-agile sine wave. The digital sine wave is con-verted to analog form via an internal 10-bit high speed D/Aconverter, and an onboard high speed comparator is provided to translate the analog sine wave into a low jitter TTL/CMOS-compatible output square wave. DDS technology is an innova-tive circuit architecture that allows fast and precise manipulation of its output frequency under full digital control. DDS also enables very high resolution in the incremental selection of output frequency; the AD9850 allows an output frequency resolution of 0.0291 Hz with a 125 MHz reference clock ap-plied. The AD9850’s output waveform is phase-continuous when changed.The basic functional block diagram and signal flow of theAD9850 configured as a clock generator is shown in Figure 16.The DDS circuitry is basically a digital frequency divider function whose incremental resolution is determined by the frequency of the reference clock divided by the 2N number of bits in the tuning word. The phase accumulator is a variable-modulus counter that increments the number stored in it each time itreceives a clock pulse. When the counter overflows it wraps around, making the phase accumulator’s output contiguous.The frequency tuning word sets the modulus of the counter that effectively determines the size of the increment (∆ Phase) that gets added to the value in the phase accumulator on the next clock pulse. The larger the added increment, the faster the ac-cumulator overflows, which results in a higher output fre-quency. The AD9850 uses an innovative and proprietary algorithm that mathematically converts the 14-bit truncated value of the phase accumulator to the appropriate COS value.This unique algorithm uses a much reduced ROM look-up table and DSP techniques to perform this function, which contributes to the small size and low power dissipation of the AD9850. The relationship of the output frequency, reference clock, and tuning word of the AD9850 is determined by the formula:f OUT = (∆ Phase × CLKIN )/232where:∆ Phase =value of 32-bit tuning wordCLKIN =input reference clock frequency in MHz f OUT =frequency of the output signal in MHz The digital sine wave output of the DDS block drives the inter-nal high speed 10-bit D/A converter that reconstructs the sineAD9850–9–REV. EFigure 16.Basic DDS Block Diagram and Signal Flow of AD9850The reference clock frequency of the AD9850 has a minimum limitation of 1 MHz. The device has internal circuitry that senses when the minimum clock rate threshold has been exceeded and automatically places itself in the power-down mode. When in this state, if the clock frequency again exceeds the threshold,the device resumes normal operation. This shutdown mode prevents excessive current leakage in the dynamic registers of the device.The D/A converter output and comparator inputs are available as differential signals that can be flexibly configured in anymanner desired to achieve the objectives of the end-system. The typical application of the AD9850 is with single-ended output/input analog signals, a single low-pass filter, and generating the comparator reference midpoint from the differential DAC out-put as shown in Figure 13.Programming the AD9850The AD9850 contains a 40-bit register that is used to program the 32-bit frequency control word, the 5-bit phase modulation word and the power-down function. This register can be loaded in a parallel or serial mode.In the parallel load mode, the register is loaded via an 8-bit bus;the full 40-bit word requires five iterations of the 8-bit word.The W_CLK and FQ_UD signals are used to address and load the registers. The rising edge of FQ_UD loads the (up to) 40-bit control data word into the device and resets the address pointer to the first register. Subsequent W_CLK rising edges load the 8-bit data on words [7:0] and move the pointer to the next register. After five loads, W_CLK edges are ignored until either a reset or an FQ_UD rising edge resets the address pointer to the first register.In serial load mode, subsequent rising edges of W_CLK shift the 1-bit data on Lead 25 (D7) through the 40 bits of program-ming information. After 40 bits are shifted through, an FQ_UD pulse is required to update the output frequency (or phase).The function assignments of the data and control words are shown in Table III; the detailed timing sequence for updating the output frequency and/or phase, resetting the device, and powering-up/down, are shown in the timing diagrams of Figures 18–24.Note:There are specific control codes, used for factory test purposes, that render the AD9850 temporarily inoperable. The user must take deliberate precaution to avoid inputting the codes listed in Table II.wave in analog form. This DAC has been optimized for dynamic performance and low glitch energy as manifested in the low jitter performance of the AD9850. Since the output of the AD9850 is a sampled signal, its output spectrum follows the Nyquist sampling theorem. Specifically, its output spectrum contains the fundamental plus aliased signals (images) that occur at multiples of the Reference Clock Frequency ± the selected output frequency. A graphical representation of the sampled spectrum, with aliased images, is shown in Figure 17.REFERENCE CLOCKFREQUENCYFigure 17. Output Spectrum of a Sampled SignalIn this example, the reference clock is 100 MHz and the output frequency is set to 20 MHz. As can be seen, the aliased images are very prominent and of a relatively high energy level as deter-mined by the sin(x)/x roll-off of the quantized D/A converter output. In fact, depending on the fo/Ref Clk relationship, the first aliased image can be on the order of –3dB below the fun-damental. A low-pass filter is generally placed between the out-put of the D/A converter and the input of the comparator to further suppress the effects of aliased images. Obviously, con-sideration must be given to the relationship of the selected output frequency and the Reference Clock frequency to avoid unwanted (and unexpected) output anomalies.A good rule-of-thumb for applying the AD9850 as a clock generator is to limit the selected output frequency to <33% of Reference Clock frequency, thereby avoiding generating aliased signals that fall within, or close to, the output band of interest (generally dc-selected output frequency). This practice will ease the complexity (and cost) of the external filter requirement for the clock generator application.AD9850–10–REV. ETable II.Factory-Reserved Internal Test Control CodesLoading Format Factory-Reserved Codes Parallel 1) W0 = XXXXXX102) W0 = XXXXXX01Serial1) W32 = 1; W33 = 02) W32 = 0; W33 = 13) W32 = 1; W33 = 1Table III.8-Bit Parallel-Load Data/Control Word Functional AssignmentWord data[7]data[6]data[5]data[4]data[3]data[2]data[1]data[0]W0Phase-b4Phase-b3Phase-b2Phase-b1Phase-b0Power-Down Control Control (MSB) (LSB)W1Freq-b31Freq-b30Freq-b29Freq-b28Freq-b27Freq-b26Freq-b25Freq-b24(MSB)W2Freq-b23Freq-b22Freq-b21Freq-b20Freq-b19Freq-b18Freq-b17Freq-b16W3Freq-b15Freq-b14Freq-b13Freq-b12Freq-b11Freq-b10Freq-b9Freq-b8W4Freq-b7Freq-b6Freq-b5Freq-b4Freq-b3Freq-b2Freq-b1Freq-b0(LSB)OLD FREQ (PHASE)NEW FREQ (PHASE)*OUTPUT UPDATE CAN OCCUR AFTER ANY WORD LOAD AND IS ASYNCHRONOUS WITH THE REFERENCE CLOCKDATAW CLKREF CLKCOS OUTFQ UDFigure 18.Parallel-Load Frequency/Phase Update Timing SequenceAD9850COS OUTRESETt RH CLK DELAY AFTER RESET RISING EDGE3.5ns t RLRESET FALLING EDGE AFTER CLK 3.5nst RRRECOVERY FROM RESET 2 CLK CYCLES tRSMINIMUM RESET WIDTH 5 CLK CYCLES t OLRESET OUTPUT LATENCY 13 CLK CYCLESSYMBOL DEFINITION MIN SPECRESULTS OF RESET:– FREQUENCY/PHASE REGISTER SET TO 0– ADDRESS POINTER RESET TO W0– POWER-DOWN BIT RESET TO “0”– DATA INPUT REGISTER UNEFFECTEDFigure 19. Master Reset Timing SequenceDATA (W0)W CLKFQ UDREF CLKDAC STROBEFigure 20.Parallel-Load Power-Down Sequence/Internal OperationDATA (W0)W CLKFQ UDREF CLKFigure 21.Parallel-Load Power-Up Sequence/Internal OperationAD9850DATA (W0)(PARALLEL)W CLK FQ UDARE REQUIRED TO SHIFT IN REQUIRED W32–W34 DATA DATA (SERIAL)REQUIRED TO RESET CONTROL REGISTERSNOTE: FOR DEVICE START-UP IN SERIAL MODE, HARD-WIRE LEAD 2 AT “0”, LEAD 3 AT “1”, AND LEAD 4 AT “1”(SEE FIGURE 23).Figure 22.Serial-Load Enable SequenceFigure 23.Leads 2–4 Connection for Default Serial-Mode OperationDATA–W CLKFQ UDFigure 24.Serial-Load Frequency/Phase Update Sequence Table IV.40-Bit Serial-Load Word Function AssignmentW0Freq-b0 (LSB) W1Freq-b1W2Freq-b2W3Freq-b3W4Freq-b4W5Freq-b5W6Freq-b6W7Freq-b7W8Freq-b8W9Freq-b9W10Freq-b10W11Freq-b11W12Freq-b12W13Freq-b13W28Freq-b28W29Freq-b29W30Freq-b30W31Freq-b31 (MSB)W32ControlW33ControlW34Power-DownW35Phase-b0 (LSB)W36Phase-b1W37Phase-b2W38Phase-b3W39Phase-b4 (MSB) W14Freq-b14W15Freq-b15W16Freq-b16W17Freq-b17W18Freq-b18W19Freq-b19W20Freq-b20W21Freq-b21W22Freq-b22W23Freq-b23W24Freq-b24W25Freq-b25W26Freq-b26W27Freq-b27AD9850DATA (7) –W CLKFQUDFigure 25.Serial-Load Power-Down SequenceDIGITALINV DAC Output Comparator Output Comparator Input Digital InputsFigure 26.AD9850 I/O Equivalent CircuitsPCB LAYOUT INFORMATIONThe AD9850/CGPCB and AD9850/FSPCB evaluation boards (Figures 27–30) represent typical implementations of the AD9850 and exemplify the use of high frequency/high resolu-tion design and layout practices. The printed circuit board that contains the AD9850 should be a multilayer board that allows dedicated power and ground planes. The power and ground planes should be free of etched traces that cause discontinuities in the planes. It is recommended that the top layer of the multi-layer board also contain interspatial ground plane, which makes ground available for surface-mount devices. If separate analog and digital system ground planes exist, they should be con-nected together at the AD9850 for optimum results.Avoid running digital lines under the device as these will couple noise onto the die. The power supply lines to the AD9850should use as large a track as possible to provide a low-impedance path and reduce the effects of glitches on the power supply line.Fast switching signals like clocks should be shielded withground to avoid radiating noise to other sections of the board.Avoid crossover of digital and analog signal paths. Traces on opposite sides of the board should run at right angles to each other. This will reduce the effects of feedthrough through the circuit board. Use microstrip techniques where possible.Good decoupling is also an important consideration. The analog (AVDD) and digital (DVDD) supplies to the AD9850 are independent and separately pinned out to minimize coupling between analog and digital sections of the device. All analog and digital supplies should be decoupled to AGND and DGND,respectively, with high quality ceramic capacitors. To achieve best performance from the decoupling capacitors, they should be placed as close as possible to the device, ideally right upagainst the device. In systems where a common supply is used to drive both the AVDD and DVDD supplies of the AD9850, it is recommended that the system’s AVDD supply be used.Analog Devices, Inc., applications engineering support is avail-able to answer additional questions on grounding and PCB layout. Call 1-800-ANALOGD.Evaluation BoardsTwo versions of evaluation boards are available for the AD9850,which facilitate the implementation of the device for bench-top analysis, and serve as a reference for PCB layout. The AD9850/FSPCB is intended for applications where the device will primarily be used as frequency synthesizer. This version facilitates connection of the AD9850’s internal D/A converter output to a 50Ω spectrum analyzer input; the internal com-parator on the AD9850 DUT is not enabled (see Figure 28 for electrical schematic of AD9850/FSPCB). The AD9850/CGPCB is intended for applications using the device in the clock genera-tor mode. It connects the AD9850’s DAC output to the internal comparator input via a single-ended, 42 MHz low-pass, 5-pole Elliptical filter. This model facilitates the access of the AD9850’s comparator output for evaluation of the device as a frequency- and phase-agile clock source (see Figure 29 for electrical schematic of AD9850/CGPCB).Both versions of the AD9850 evaluation boards are designed to interface to the parallel printer port of a PC. The operating software runs under Microsoft ® Windows and provides a user-friendly and intuitive format for controlling the functionality and observing the performance of the device. The 3.5" floppy provided with the evaluation board contains an executable file that loads and displays the AD9850 function-selection screen.The evaluation board may be operated with +3.3 V or +5 V supplies. The evaluation boards are configured at the factory for an external reference clock input; if the onboard crystal clock source is used, remove R2.All trademarks are the property of their respective holders.。

基于ad9854扫频信号源的设计-翻译

基于ad9854扫频信号源的设计-翻译苏州大学本科生毕业设计(论文)附件:外文文献资料与中文翻译稿外文文献资料收集:苏州大学应用技术学院 10电子,学号1016405013,黄海浩Introduction to AD9854GENERAL DESCRIPTIONThe AD9854 is pin-for-pin com The AD9854 digital synthesizer is a highly integrated device that uses advanced DDS technology, coupled with two internal high speed, high performance quadrature DACs to form a digitally programmable I and Q synthesizer function. When referenced to an accurate clock source, the AD9854 generates highly stable, frequency-phase, amplitude-programmable sine and cosine outputs that can be used as an agile LO in communications, radar, and many other applications. The innovative high speed DDS core of the AD9854 provides 48-bit frequency resolution (1 μHz tuning resolution with 300 MHz SYSCLK). Maintaining 17 bits ensures excellent SFDR.The circuit architecture of the AD9854 allows the generation of simultaneous quadrature output signals at frequencies up to 150 MHz, which can be digitally tuned at a rate of up to 100 million new frequencies per second. The sine wave output (externally filtered) can be converted to a square wave by the internalfor agile clock generator applications. The device provides two 14-bit comparatorphase registers and a single pin for BPSK operation.For higher-order PSK operation, the I/O interface can be used for phase changes. The 12-bit I and Q DACs, coupled with the innovative DDS architecture, provide excellent wideband and narrow-band output SFDR. The Q DAC can also be configured as a user-programmable control DAC if the quadrature function is not desired. When configured with the comparator, the 12-bit control DAC facilitates static duty cycle control in high speed clock generator applications.Two 12-bit digital multipliers permit programmable amplitude modulation, on/off output shaped keying, and precise amplitude control of the quadrature output. Chirp functionality is also included to facilitate wide bandwidth frequency sweeping applications. The programmable 4× to 20× REFCLK multiplier circuit ofthe AD9854 internally generates the 300 MHz system clock from an external lower第 1 页苏州大学本科生毕业设计(论文)附件:外文文献资料与中文翻译稿frequency reference clock. This saves the user the expense and difficulty of implementing a 300 MHz system clock source.Direct 300 MHz clocking is also accommodated with either single-ended or differential inputs. Single-pin conventional FSK and the enhanced spectral qualities of ramped FSK are supported. The AD9854 uses advanced 0.35 μm CMOStechnology to provide a high level of functionality on a single 3.3 patible with the AD9852 single-tone synthesizer. It is specified to operate over the extended industrial temperature range of ?40?C to +85?C.THEORY OF OPERATIONThe AD9854 quadrature output digital synthesizer is a highlyflexible device that addresses a wide range of applications. The device consists of an NCO with a 48-bit phase accumulator, a programmable reference clock multiplier, inverse sinc filters,digital multipliers, two 12-bit/300 MHz DACs, a high speed analog comparator, and interface logic. This highly integrated device can be configured to serve as a synthesized LO, an agile clock generator, or an FSK/BPSK modulator.Analog Devices, Inc., provides a technical tutorial about the operational theory of the functional blocks of the device. The tutorial includes a technical description of the signal flow through a DDS device and provides basic applications information for a variety of digital synthesis implementations. The document, A Technical Tutorial on Digital Signal Synthesis, is available from the DDS Technical Library, on the Analog Devices DDS website at /dds.MODES OF OPERATIONThe AD9854 has five programmable operational modes. To select a mode, three bits in the control register (parallel Address 1F hex) must be programmed,as described in Table 5.Table5.Mode Selection TableMode2 Mode1 Mode0 Result0 0 0 Single tone0 0 1 FSK0 1 0 Ramped FSK第 2 页苏州大学本科生毕业设计(论文)附件:外文文献资料与中文翻译稿0 1 1 Chirp1 0 0 BPSKINTERNAL AND EXTERNAL UPDATE CLOCKThis update clock function is comprised of a bidirectional I/O pin (Pin 20) and a programmable 32-bit down-counter. To program changes that are to be transferred from the I/O buffer registers to the active core of the DDS, a clock signal (low-to-high edge) must be externally supplied to Pin 20 or internally generated by the 32-bit update clock.When the user provides an external update clock, it is internally synchronized with the system clock to prevent a partial transfer of program register information due to a violation of data setup or hold time. This mode allows the user to completely control when updated program information becomes effective. The default mode for the update clock is internal (the internal update clock control register bit is logic high). To switch to external update clock mode, the internal update clock control register bit must be set to logic low. The internal update mode generates automatic, periodic update pulses at intervals set by the user.An internally generated update clock can be established by programming the 32-bit update clock registers (Address 16 hex to Address 19 hex) and setting the internal update clock control register bit (Address 1F hex) to logic high. The update clock down-counter function operates at half the rate of the system clock (150 MHz maximum) and counts down from a 32-bit binary value (programmed by the user). When the count reaches 0, an automatic I/O update of the DDS output or functions is generated. The update clock is internally and externally routed to Pin 20 to allow users to synchronize the programming of update information with the update clock rate. The time between update pulsesis given as(N + 1)(System Clock Period × 2)where N is the 32-bit value programmed by the user, and theallowable range of N is from 1 to (232 ? 1).The internally generated update pulse that is output from Pin 20 has a fixed high time of eight system clock cycles.rogramming the update clock register to a value less than five causes the I/O第 3 页苏州大学本科生毕业设计(论文)附件:外文文献资料与中文翻译稿UD CLK pin to remain high. Although the update clock can function in this state, it cannot be used to indicate when data is transferring. This is an effect of the minimum high pulse time when I/O UD CLK functions as an output.ON/OFF OUTPUT SHAPED KEYING (OSK)The on/off OSK feature allows the user to control the amplitude vs. time slope of the I and Q DAC output signals. This function is used in burst transmissions of digital data to reduce the adverse spectral impact of short, abrupt bursts of data. Users must first enable the digital multipliers by setting the OSK EN bit (Control Register Address 20 hex) to logic high in the control register. Otherwise, if the OSK EN bit is set low, the digital multipliers responsible for amplitudecontrol are bypassed and the I and Q DAC outputs are set to full-scale amplitude.In addition to setting the OSK EN bit, a second control bit, OSK INT (also at Address 20 hex), must be set to logic high. Logic high selects the linear internal control of the output ramp-up or ramp-down function.A logic low in the OSK INT bit switches control of the digital multipliers to user-programmable 12-bitallowing users to dynamically shape the amplitude transition in registers,practically any fashion. These 12-bit registers, labeled Output Shape Key I and Output Shape Key Q, are located at Address 21 hex through Address 24 hex, as listed in Table 8. The maximum output amplitude is a function of the RSET resistor and is not programmable when OSK INT is enabled.The transition time from zero scale to full scale must also be programmed. The transition time is a function of two fixed elements andone variable. The variable element is the program-mable 8-bit ramp rate counter. This is a down-counter that is clocked at the system clock rate (300 MHz maximum) and that generates one pulse whenever the counter reaches 0. This pulse is routed to a 12-bit counter that increments with each pulse received. The outputs of the 12-bit counter are connected to the 12-bit digital multiplier. When the digital multiplier has a value of all 0s at its inputs, the input signal is multiplied by 0, producing zero scale. When the multiplier has a value of all 1s, the input signal is multiplied by a value of 4095 or 4096, producing nearly full scale. There are 4094 remaining fractional multiplier values that produce output amplitudes scaled according to their binary values.第 4 页苏州大学本科生毕业设计(论文)附件:外文文献资料与中文翻译稿I AND Q DACSThe sine and cosine outputs of the DDS drive the Q and I DACs, respectively (300 MSPS maximum). The maximum amplitudes of these output are set by the DAC RSET resistor at Pin 56. These are current-output DACs with a full-scale maximum output of 20 mA; however, a nominal 10 mA output current provides the best spurious-free dynamic range (SFDR) performance. The value of RSET is 39.93/IOUT, where IOUT is expressed in amps. DAC output compliance specifications limit the maximum voltage developed at the outputs to ?0.5 V to +1 V. Voltages developed beyond thislimitation cause excessive DAC distortion and possibly permanent damage. The user must choose a proper load impedance to limit the output voltage swing to the compliance limits. Both DAC outputs should be terminated equally for best SFDR, especially at higher output frequencies, where harmonic distortion errors are more prominent.Both DACs are preceded by inverse sin(x)/x filters (also called inverse sinc filters) that precompensate for DAC output amplitude variations over frequency to achieve flat amplitude response from dc to Nyquist. Both DACs can be powered down when not needed by setting the DAC PD bit high (Address 1D hex of the control register). I DAC outputs are designated as IOUT1 and IOUT1, Pin 48 and Pin 49, respectively. Q DAC outputs are designated as IOUT2 and IOUT2, Pin 52 and Pin 51, respectively.CONTROL DACThe 12-bit Q DAC can be reconfigured to perform as a control or auxiliary DAC. The control DAC output can provide dc control levels to external circuitry, generate ac signals, or enable duty cycle control of the on-board comparator. When the SRC Q DAC bit in the control register (Parallel Address 1F hex) is set high, the Q DAC inputs are switched from internal 12-bit Q data source (default setting) to external 12-bit, twos complement data supplied by the user. Data is channeled through the serial or parallel interface to the 12-bit Q DAC register (Address 26 hex and Address 27 hex) at a maximum data rate of 100 MHz. This DAC is clocked at the system clock, 300 MSPS (maximum), and has the samemaximum output current capability as that of the I DAC. The single RSET resistor on the AD9854 sets the full-scale output current for both DACs. When not needed, the control DAC can be separately powered down to conserve power by setting the Q DAC power-down bit high第 5 页苏州大学本科生毕业设计(论文)附件:外文文献资料与中文翻译稿(Address 1D hex). Control DAC outputs are designated as IOUT2 and IOUT2, Pin 52 and Pin 51, respectively.REFCLK MULTIPLIERThe REFCLK multiplier is a programmable PLL-based reference clock multiplier that allows the user to select an integer clock multiplying value over the range of 4× to 20×. With this function, users can input as little as 15 MHz at the REFCLK input to produce a 300 MHz internal system clock. Five bits in Control Register 1E hex set the multiplier value, as detailed in Table 7. The REFCLK multiplier function can be bypassed to allow direct clocking of the AD9854 from an external clock source. The system clock for the AD9854 is either the output of the REFCLK multiplier (if it is engaged) or the REFCLK inputs. REFCLK can be either a single-ended or differential input by setting Pin 64, DIFF CLK ENABLE, low or high, respectively.PLL Range BitThe PLL range bit selects the frequency range of the REFCLKmultiplier PLL. For operation from 200 MHz to 300 MHz (internal system clock rate), the PLL range bit should be set to Logic 1. For operationbelow 200 MHz, the PLL range bit should be set to Logic 0. The PLL range bit adjusts the PLL loop parameters for best phase noise performance within each range.PLL FilterThe PLL FILTER pin (Pin 61) provides the connection for the external zero-compensation network of the PLL loop filter. The zero-compensation network consists of a 1.3 kΩ resistor in series with a 0.01 μF capacitor. The other sideof the network should be connected as close as possible to Pin 60, AVDD. For optimum phase noise performance, the clock multiplier can be bypassed by setting the bypass PLL bit in Control Register Address 1E hex.Differential REFCLK EnableA high level on the DIFF CLK ENABLE pin enables the differ-ential clock inputs, REFCLK and REFCLK (Pin 69 and Pin 68, respectively). The minimum differential signal amplitude required is 400 mV p-p at the REFCLK input pins. The center point or common-mode range of the differential signal can range from1.6 V to 1.9 V.When Pin 64 (DIFF CLK ENABLE) is tied low, REFCLK (Pin 69) is the only active第 6 页苏州大学本科生毕业设计(论文)附件:外文文献资料与中文翻译稿clock input. This is referred to as single-ended mode. In this mode, Pin 68 (REFCLK) should be tied low or high.High Speed ComparatorThe comparator is optimized for high speed and has a toggle rate greater than 300 MHz, low jitter, sensitive input, and built-in hysteresis. It also has an output level of 1 V p-p minimum into 50 Ω or CMOS logic levels into high impedance loads. The comparator can be powered down separately to conserve power. This com-parator is used in clock-generator applications to square up the filtered sine wave generated by the DDS.Power-DownThe programming registers allow several individual stages to be powered down to reduce power consumption while maintaining thefunctionality of the desired stages. These stages are identified inTable 8, Address 1D hex. Power-down is achieved by setting the specified bits to logic high. A logic low indicates that the stages are powered up.Furthermore, and perhaps most significantly, the inverse sincfilters and the digital multiplier stages can be bypassed to achieve significant power reduction by programming the control registers in Address 20 hex. Again, logic high causes the stage to be bypassed. Of particular importance is the inverse sinc filter; this stage consumes a significant amount of power.A full power-down occurs when all four PD bits in Control Register1D hex are set to logic high. This reduces power consumption to approximately 10 mW (3 mA).PROGRAMMING THE AD9854The AD9854 register layout table (Table 8) contains information for programming the chip for the desired functionality. Although many applications require very little programming to configure the AD9854, some use all 12 accessible register banks. The AD9854 supports an 8-bit parallel I/O operation or an SPI?-compatible serial I/O operation. All accessible registers can be written and read back in either I/Ooperating mode.S/P SELECT (Pin 70) is used to configure the I/O mode. Systems that use the parallel I/O mode must connect the S/P SELECT pin to VDD. Systems that operate in the serial I/O mode must tie the S/P SELECT pin to GND.Regardless of the mode, the I/O port data is written to a buffer memory and第 7 页苏州大学本科生毕业设计(论文)附件:外文文献资料与中文翻译稿only affects operation of the part after the contents of the buffer memory are transferred to the register banks. This transfer of information occurs synchronously to the system clock in one of two ways: • Internally, at a rate programmable by the user.• Externally, by the user. I/O operations can occur in the absence of REFCLK, but the data cannot be moved from the buffer memory to the register bank without REFCLK. (See the Internal and External Update Clock section for more details.)PARALLEL I/O OPERATIONWith the S/P SELECT pin tied high, the parallel I/O mode is active. The I/O port is compatible with industry-standard DSPs and microcontrollers. Six address bits, eight bidirectional data bits, and separate write/read control inputs comprise the I/O port pins. Parallel I/O operation allows write access to each byte of any register in a single I/O operation of up to one per 10.5 ns. Readback capability for each register is included to ease designing with the AD9854. (Reads are not guaranteed at 100 MHz because they are intended for software debugging only.)SERIAL PORT I/O OPERATIONWith the S/P SELECT pin tied low, the serial I/O mode is active. The serial port is a flexible, synchronous, serial communication port, allowing easy interface to many industry-standard micro-controllers and microprocessors. The serial I/O is compatible with most synchronous transfer formats, including both the Motorola? 6905/11 SPI and Intel? 8051 SSR protocols. The interface allows read/write access to all 12 registers that configure the AD9854 and can be configured as a single-pin I/O (SDIO) or two unidirectional pins for input and output(SDIO/SDO). Data transfers are supported in MSB-or the LSB-first format for up to 10 MHz.When configured for serial I/O operation, most AD9854 parallel port pins are inactive; only some pins are used for the serial I/O operation. Table 9 describes pin requirements for serial I/O operation.Note that when operating the device in serial I/O mode, it is bestto use the external I/O update clock mode to avoid an update occurring during a serial communication cycle. Such an occurrence may cause incorrect programming due to a partial data transfer. To exit thedefault internal update mode, program the第 8 页苏州大学本科生毕业设计(论文)附件:外文文献资料与中文翻译稿device for external update operation at power-up before starting the REFCLK signal but after a master reset. Starting the REFCLK causes this information to transfer to the register bank, forcing the device to switch to external update mode.第 9 页苏州大学本科生毕业设计(论文)附件:外文文献资料与中文翻译稿中文翻译稿翻译:苏州大学应用技术学院 10电子,学号1016405013,黄海浩AD9854简述概述在AD9854数字频率合成器是一种高度集成的器件,采用先进的DDS技术,具有两个内部耦合高速,高性能正交数模转换器以实现数字可编程的I/Q合成功能。

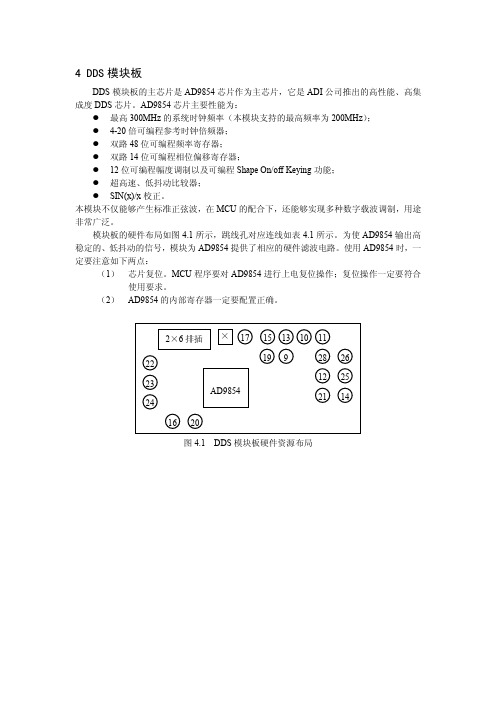

AD9854-DDS模块板

4 DDS模块板DDS模块板的主芯片是AD9854芯片作为主芯片,它是ADI公司推出的高性能、高集成度DDS芯片。

AD9854芯片主要性能为:●最高300MHz的系统时钟频率(本模块支持的最高频率为200MHz);●4-20倍可编程参考时钟倍频器;●双路48位可编程频率寄存器;●双路14位可编程相位偏移寄存器;●12位可编程幅度调制以及可编程Shape On/off Keying功能;●超高速、低抖动比较器;●SIN(x)/x校正。

本模块不仅能够产生标准正弦波,在MCU的配合下,还能够实现多种数字载波调制,用途非常广泛。

模块板的硬件布局如图4.1所示,跳线孔对应连线如表4.1所示。

为使AD9854输出高稳定的、低抖动的信号,模块为AD9854提供了相应的硬件滤波电路。

使用AD9854时,一定要注意如下两点:(1)芯片复位。

MCU程序要对AD9854进行上电复位操作;复位操作一定要符合使用要求。

(2)AD9854的内部寄存器一定要配置正确。

图4.1 DDS模块板硬件资源布局附带的参考文档提供了电路原理图、AD8954的Datasheet和中文使用说明。

Demo程序说明如下:●位置:fpga/ demo_project/ test_parallel_dds。

●功能说明:提供了DDS模块板的演示程序。

该程序能够使模块输出频率为156.25KHz的正弦波。

程序的顶层文件提供了更为详细的工程说明,ucf文件提供了模块的连线方法。

●连线方法:(1)跳线连接底板跳线孔模块板跳线孔TP140 TP17TP136 TP9TP139 TP11TP200 TP22TP207 TP23TP206 TP24TP214 TP15TP208 TP13TP212 TP10TP213 TP19TP216 TP16TP222 TP20(2)排线连接底板排插J4 模块板排插J3J4.1 J3.1J4.2 J3.2J4.3 J3.3J4.4 J3.4J4.5 J3.5J4.6 J3.6J4.7 J3.7J4.8 J3.8J4.9 J3.9J4.10 J3.10J4.11 J3.11J4.12 J3.12。

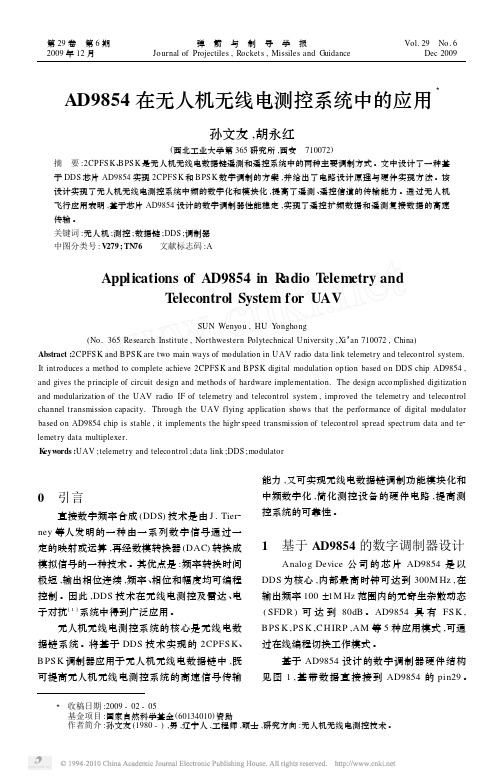

AD9854在无人机无线电测控系统中的应用

φ 2P 0 × 360°

( 4)

式中 :φ 0 为相位调整寄存器的初始相位 ; P 为相 位调整寄存器位数 14 。 当 BPSK 载波 的两个相位分别为

90° 和 270° 时 , 由式 (4 ) 得到相位调整

程序中的 Send_ dds_ byte 是按位发送数据 的子程序 ,因为是 8 位单片机 ,所以每个字节为 8 位二进制 ,子程序代码如下 。

可提高无人机无线电测控系统的高速信号传输

3

收稿日期 :2009 - 02 - 05 基金项目 : 国家自然科学基金 (60134010) 资助 作者简介 : 孙文友 ( 1980 - ) ,男 ,辽宁人 ,工程师 ,硕士 ,研究方向 : 无人机无线电测控技术 。

・236 ・ 犚 犛 2 3 2协议格式 的控制指令 , 经电 平 转 换 成 CMOS 电平后给单片机 , 单片 机 根 据 控 制 指令改变 AD9854

Send_dds_byte : clr mov mov rlc mov set b nop clr djnz ret dds_sclk R1 ,Send_dds_bit dds_sclk R1 , # 008 H A ,R0 A dds_data ,C dds_sclk

孙文友 ,胡永红

( 西北工业大学第 365 研究所 ,西安 710072)

3

摘 要 :2CPFS K、 B PS K 是无人机无线电数据链遥测和遥控系统中的两种主要调制方式 。文中设计了一种基 于 DDS 芯片 AD9854 实现 2CPFS K 和 B PS K 数字调制的方案 , 并给出了电路设计原理与硬件实现方法 。该 设计实现了无人机无线电测控系统中频的数字化和模块化 ,提高了遥测 、 遥控信道的传输能力 。通过无人机 飞行应用表明 ,基于芯片 AD9854 设计的数字调制器性能稳定 ,实现了遥控扩频数据和遥测复接数据的高速 传输 。 关键词 : 无人机 ; 测控 ; 数据链 ;DDS ; 调制器 中图分类号 : V279 ; TN76 文献标志码 :A

AD9854非线性调频输出功能的仿真与分析

AD9854非线性调频输出功能的仿真与分析

汤少维

【期刊名称】《华东交通大学学报》

【年(卷),期】2005(022)004

【摘要】AD9854是美国AnalogDevice公司生产的一种新型DDS芯片,该芯片能够在单片上完成频率调制、相位调制、幅度调制以及IQ正交调制等多种功能.本文从DDS的组成和基本原理出发,介绍了AD9854的结构和工作原理及其常用实现电路.同时利用simulink针对其FM Chirp调频模式中的非线性调频输出功能进行了仿真,对仿真中的各主要功能模块作出了详细的分析并给出了最终的输出数据和波形.

【总页数】5页(P90-93,97)

【作者】汤少维

【作者单位】电子科技大学,通信与信息工程学院,四川,成都,610054

【正文语种】中文

【中图分类】TM

【相关文献】

1.线性调频和非线性调频的信号脉压分析 [J], 蒋锋;李石

2.非线性调频信号脉压分析与仿真 [J], 计鹏

3.正交频分非线性调频(OFD-NLFM)信号集设计及仿真分析 [J], 张良;廖小兵;胡淼;周杰

4.基于AD9854的非线性调频脉压雷达信号的产生技术 [J], 汪洋;师志荣;雷婷

5.一种雷达非线性调频信号检测及仿真方法 [J], 祝伟锋;刘以安

因版权原因,仅展示原文概要,查看原文内容请购买。

AD9854并行和串行驱动

AD9854并行和串行驱动AD9854简介AD9854最高支持300MHz的时钟速率,内置的倍频器能实现4到20倍的倍频,拥有48位可编程频率寄存器和14位可编程相位偏移寄存器以及12位可编程幅度调节寄存器,集成了12位的DAC,支持最高速率为10MHz的串行编程或者最高速率为100MHz的并行编程。

如何使用AD9854内部和外部的更新时钟此功能是由一个双向的I/O管脚即20管脚和一个可编程的32位递减计数器来实现的。

为了使输出波形能随着写入控制寄存器的值改变,需要提供给20管脚一个上升沿的时钟信号或者由内部的32位更新时钟来实现。

默认模式设置为内部更新时钟(内部更新时钟寄存器赋逻辑高电平)。

如果使用外部更新时钟模式,则内部更新时钟寄存器赋逻辑低电平。

内部产生更新时钟可以通过编程32位更新时钟寄存器以及设定内部更新时钟寄存器赋逻辑高电平来实现。

更新时钟递减计数器以1/2的系统时钟速率工作,从用户设定的32位值往下递减,当计数器的值为零的时候,DDS输出随着用户设定而更新,同时20管脚输出一个持续8个时钟长度的高电平。

输出波形整形开关首先用户必须通过设定OSK EN(控制寄存器地址20h)逻辑高来使能数字乘法器。

如果设定为低,则输出的波形是满幅的。

除了设定OSK EN之外,还要设置OSK INT(也是在控制寄存器20h)。

OSK INT 逻辑高电平选择内部控制波形线性上升或者下降;逻辑低电平则使用12位的寄存器以便用户输出任意形式的幅度过渡波形(12位的控制寄存器位于地址21h到24h),每当斜坡速率递减计数器计数到零,输出一个脉冲,同时输出端叠加12位寄存器的值,同乘法器相乘后输出。

30管脚为高电平实现输出波形由零到满幅的改变,为低电平则实现输出波形由满幅到零的改变。

DA模块DA模块最大支持300M的采样速率,输出正弦波和余弦波。

它们的最大幅值由56管脚的电阻R SET来决定。

DA模块是输出电流最大值为20mA的电流输出模式,但是,输出电流为10mA能有最好的无杂散动态范围。

AD9854管脚信息中文

69号:单端参考时钟输入(CMOS逻辑电平要求)或一个差分时钟信号。

在差分参考时钟模式,输入可以是CMOS逻辑电平或大于400 mV p-p的方波或正弦波直流1.6 V左右为中心。

1到8:D7toD08位双向并行编程数据输入。

只用于并行编程模式。

9, 10, 23, 24, 25, 73, 74, 79, 80 :DVDD对数字电路的电源电压的连接。

标称3.3 V到AGND更积极和DGND。

11, 12, 26, 27, 28, 72, 75 to 78 :DGND对数字电路的接地连接。

为AGND相同电位。

13, 35, 57, 58, 63:NC没有内部连接。

14 to 16 :A5 to A3并行程序的寄存器的地址输入(6位并行输入程序的地址为注册部分,A5:A0)。

用only in并行编程模式。

17:A2/IO RESET并行输入寄存器(地址的程序的一部分6位并行输入地址的程序A5:寄存器,复位/ A0)I\O复位。

A2是在并行编程只读模式。

当使用IO复位串行编程模式选择,允许串行通信总线IO复位这是由于不正确的编程协议无效在这个重置串行总线方式不影响以前的编程,也不调用默认程序表8中列出的值。

活性高。

18:A1/SDO 并行输入寄存器(地址的程序的一部分6位并行输入地址的程序寄存器,A5:A0)单向串行数据输出。

A1是在并行编程只读模式。

SDO是用于3线串行通信在串行编程模式,当模式是选定的。

19:A0/SDIO 并行输入寄存器(地址的程序的一部分6位并行输入地址的程序A5:A0)寄存器,串行数据I / O /拼写的A0是在并行编程只读模式。

SDIO是用在2线串行通信模式。

20:I/O UD CLK 双向I / O时钟更新。

选择的方向是在控制寄存器。

如果该引脚作为输入,上升沿传输I/O端口缓冲器的编程寄存器的内容。

:如果I/OUD的时钟作为输出(默认值),输出脉冲(低到高)为期八系统时钟周期表明,出现了一个内部频率更新。

AD9954芯片资料中文版

AD9954- Direct Digital Synthesizer400 MSPS 14-Bit, 1.8 V CMOS功能: (2)应用 (2)概述 (2)AD9954电气特性 (3)最大操作范围 (4)Table 2. (4)管脚定义 (4)管脚功能描述 (4)典型的性能特性 (6)原理 (7)器件块 (7)控制寄存器位描述 (10)Other Register Descriptions 其他寄存器描述 (14)Programming AD9954 Features-- AD9954编程特性 (18)SERIAL PORT OPERATION串口操作 (19)INSTRUCTION BYTE指令字节 (20)SERIAL INTERFACE PORT PIN DESCRIPTION串行接口管脚描述 (20)MSB/LSB TRANSFERS (20)RAM I/O VIA SERIAL PORT (21)Power-Down Functions of the AD9954 AD9954省电功能 (21)功能:400MSPS 内部时钟 集成14位DAC可编程相位/幅度抖动 32位控制字相位噪声小于等于-120dbc/Hz@1kHz(DAC 输出)出色的动态性能>80db SFDR@160MHz (偏离100KHz ) 串行I/O 口控制 超高速模拟比较器 自动线性和非线性扫频能力 4种频率/相位偏移坡面 1.8v 电压供电软件或者硬件控制休眠内部集成1024字节*32位RAM 大多数输入口支持5v 电平PLL REFCLK 乘法器(4倍-20倍) 单晶振驱动内部时钟 相位调制能力 多芯片同步 应用敏捷LO 频率输出 可编程的时钟发生器雷达和扫频系统中的FM 啁啾源自动雷达测试和测量设备 声光设备驱动概述AD9954具有一个14位DAC 最高达400 MSPS 的DDS 。

AD9954使用了先进的DDS 技术,内部集成高速,高性能的DAC 形成数字可编程,完整的高频合成器,能产生高达200MHz 模拟正弦波的能力。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

AD9854特征·300M内部时钟频率·可进行频移键控(FSK),二元相移键控(BPSK),相移键控(PSK),脉冲调频(CHIRP),振幅调制(AM)操作·正交的双通道12位D/A转换器·超高速比较器,3皮秒有效抖动偏差·外部动态特性:80 dB无杂散动态范围(SFDR)@ 100 MHz (±1 MHz) A OUT·4倍到20倍可编程基准时钟乘法器·两个48位可编程频率寄存器·两个14位可编程相位补偿寄存器·12位振幅调制和可编程的通断整形键控功能·单引脚FSK和BPSK数据输入接口·PSK功能可由I/O接口实现·具有线性和非线性的脉冲调频(FM CHIRP)功能,带有引脚可控暂停功能·具有过渡FSK功能·在时钟发生器模式下,有小于25 ps RMS抖动偏差·可自动进行双向频率扫描·能够对信号进行sin(x)/x校正·简易的控制接口:可配置为10MHZ串行接口,2线或3线SPI兼容接口或100MHZ 8位并行可编程接口·3.3V单电源供电·具有多路低功耗功能·单输入或差分输入时钟·小型80脚LQFP 封装应用·便携式频率特性分析仪·可编程时钟发生器·应用于雷达和扫频系统的脉冲调频信号源·测试和测量设备·商业和业余的射频(RF)发射机概述AD9854数字合成器是高集成度的器件,它采用先进的DDS技术,片内整合了两路高速、高性能正交D/A转换器通过数字化编程可以输出I、Q两路合成信号。

在高稳定度时钟的驱动下,AD9854将产生一高稳定的频率、相位、幅度可编程的正弦和余弦信号,作为本振用于通信,雷达等方面。

AD9854的DDS核具有48位的频率分辨率(在300M系统时钟下,频率分辨率可达1uHZ)。

输出17位相位截断保证了良好的无杂散动态范围指标。

AD9854允许输出的信号频率高达150MHZ,而数字调制输出频率可达100MHZ。

通过内部高速比较器正弦波转换为方波输出,可用作方便的时钟发生器。

器件有两个14位相位寄存器和一个用作BPSK操作的引脚。

对于高阶的PSK调制,可通过I/O接口改变相位控制字实现。

具有改进DDS结构的12位I和Q通道D/A转换器可以提供较大的带宽并有较好的窄带无杂散动态范围(SFDR)。

如果不使用Q通道的正交功能,它还可以通过配置,由用户编程控制D/A转换。

当配置高速比较器时,12位D/A输出的方波可以用来做时钟发生器。

它还有两个12位数字正交可编程幅度调制器,和通断整形键控功能,并有一个非常好的可控方波输出。

同时脉冲调制功能在宽带扫频中也有重要应用。

AD9854的300M系统时钟可以通过4X和20X可编程控制电路由较低的外部基准时钟得到。

直接的300M时钟也可以通过单端或差分输入。

AD9854还有单脚输入的常规FSK和改进的斜率FSK输出。

AD9854采用先进的0.35微米COMS工艺在3.3V单电源供电的情况下提供强大的功能。

AD9854采用节省空间的80脚LQFP表面装配封装和改进散热的80脚LQFP封装。

AD9854的引脚与AD9852的单频信号发生器模式相兼容。

AD9854的特定操作允许温度是工业级范围:-40到85摄氏度。

引脚配置和功能描述图1 管脚配置RESET VINP操作说明AD9854正交数字信号发生器是一款有着广泛应用的非常灵活的器件。

器件包括一个48位的相位累加器,可编程基准时钟乘法器,反辛格滤波器,数字乘法器,两个12位/300HZ 数模转换器,一个高速模拟比较器和内部逻辑电路。

这款高度集成的器件可以用作本机震荡发生器,灵活的时钟发生器和FSK/BPSK调制器。

Analog Devics股份有限公司的技术指南提供了关于器件功能模块的操作说明。

指南包括利用DDS器件产生信号的技术描述并提供了适合多种数字化实体的基本应用。

文件,《关于数字信号发生器的技术指南》在AD公司DDS网页/dds DDS技术库中提供。

操作模式AD9854有5种可编程操作模式。

为了选择某一模式,必须对控制寄存器(并行操作地址:1FH)中的3个相关位进行编程设置。

具体描述在下表:表2. 模式选择表在每种模式下都有许多功能不被允许。

单信号模式(模式000)这是用户复位之后的一种默认模式。

也可以通过用户编程使能这种模式。

相位累加器用以产生信号的频率,它有48位有效值,取自频率调整寄存器1,它的默认值为0。

保留寄存器的默认值更能决定输出信号的质量。

用户复位后,默认设置配置器件,输出0HZ,0相位的信号。

在上电复位时,在I和Q 通道输出的是一半满幅电流的直流信号。

这是默认模式的0幅度输出。

选择幅度开关键控模式则需要更多细节的输出幅度控制。

若输出用户定义的信号需要对28个寄存器全部或部分进行编程。

表35显示了从默认0HZ到用户定义输出频率的变化。

和所有AD DDS器件一样,频率控制字有如下定义:FTW = (Desired Output Frequency × 2N)/SYSCLK式中:N相位累加器的资源(本器件48位)。

Frequency 以HZ表示。

FTW (频率调整字)是一个定义数字。

一旦定义数字选定,它必须转换为内部的权重为1或0的48位串行二进制码。

建立的DAC输出信号频率范围从直流到1/2系统时钟。

改变频率时相位是连续的,这意味着新的频率的相位取样值参考之前输出频率的相位取样值。

AD9854的I和Q通道输出的信号总是保持90度的相位差。

调整每个通道的输出相位两个14位相位寄存器并不是独立的。

换而言之,两DAC输出通过相位补偿互相影响。

单信号模式允许用户控制以下信号参数:·48位输出频率精度·12位输出幅度精度-固定的,用户定义的幅度-可变的,可编程幅度控制-自动的,可编程,单引脚控制,幅度成型键控·14位输出相位精度这些参数可以在100MHZ并行速度下通过8位并行端口或10MHZ串行端口通过编程改变和调整。

联合这些属性在单信号模式下可以实现FM,AM,PM,FSK,PSK和ASK操作。

无斜率FSK(模式001)当这种模式被选中,输出的DDS频率是一个选择频率控制寄存器1和2的函数,它的输出取决于29脚逻辑电平的高低。

29脚为逻辑低电平时选择F1(频率控制字1,并行地址为04H到09H),29脚为逻辑高电平时选择F2(频率控制字2,并行地址为0AH到0FH)。

改变频率相位连续,并且和FSK数据引脚内部一致。

但是,FSK数据信号和DAC输出存在线性时延。

无斜率FSK ,是传统FSK,它传输的是数字信号,它在数字通信中有着重要作用。

但是它会影响RF发射机的使用带宽,因此用斜率FSK来改善使用带宽。

斜率FSK(模式010)这种FSK模式下,频率从F1到F2不是直接变化,而是通过扫频和斜率形成。

线性扫频和斜率形成可以很容易的自动完成,不过这都是许多设置中的一项。

其它频率传输的设置,用户可以配置增量控制寄存器,来编程控制扫频间隔和扫频速度。

频率斜率变化不管是线性还是非线性都会输出许多介于F1和F2之间的频率,而不仅是这两个基本输出。

图37和38描述了一线性斜率FSK信号的频率输出与时间的关系。

需要注意,在斜率FSK模式下,频率步进字是要求编程设置的,它被用作双作用的补足值。

须要注意的另一个问题是,最低频率一定要放在频率控制寄存器1中。

斜率FSK通过同缓慢的、用户定义变化率的实时频率来改善传统FSK对带宽的限制。

输出信号在F1和F2频率点保持时间与其它实时点相同或稍大。

与传统FSK不同,斜率FSK 要求:F1和F2分别存储低频率和高频率,而不能任意。

用户必须通过编程来设定DDSd的中间频率变化的步进量of C48位)和每一步所持续的时间△T (20位)。

另外,如果要想让频率输出从0开始变化必须先给CLR ACC1位送一个正脉冲。

对于分段的非线性频率传输,必须对影响输出的寄存器进行编程设置。

并行寄存器1AHex~1CHex构成一个20位的斜率时钟寄存器。

它是一个减计数器,当计数值为0时输出一个脉冲信号。

在29脚的输入电平没有变化时计数器一直有效。

这个计数器在系统时钟下运行,最大频率是300MHZ。

每两个脉冲之间的时间周期用下式表示:(N+1)*(System Clock Period)此处N是用户编程设置的20位斜率变化率。

N的允许范围是1到(2^20-1)。

斜率变化时钟决定频率F1和F2 之间的实时频率持续时间。

当频率达到目标频率时计数器自动停止,而F1和F2两频率点的持续时间由29脚输入的电平决定,电平的高低决定到达的频率点的状态。

图39 FSK功能模块图并行寄存器10Hex~15Hex构成一个48位的双作用的斜率步进寄存器。

当接收到斜率变化时钟时,这个48位控制字被累加。

此控制字被用来加或减到控制正弦或余弦输出的相位步进的频率控制字寄存器F1或F2。

在这种模式下,29脚的电平状态决定输出的频率是增量或减量斜率。

其频率变化率是20位斜率变化寄存器的功能,一旦目标频率到达,计数器将停止计数即频率累加过程停止。

一般来说,频率步进字与频率控制字相比是一个比较小的值,举个例子,如果F1和F2分别是1KHZ和13MHZ,那么步进频率字只有25HZ。

图41显示了,电平过早的变化使频率的斜率变化翻转,并且以相同的变化率返回原状态。

控制寄存器(1FHex)中含有一个“三角形”位。

在010模式下设置此位为高电平将会再频率F1和F2之间进行三角形自动扫频,而不会受29脚电平变化的影响,如图40。

一旦这个位设置为1,29脚的状态将不会起作用。

这一功能需要设置频率变化率和频率步进字来保证F1和F2之间的连续线性扫频具有相同的持续时间。

使用此功能,可以对直流到最大输出频率之间的自动扫频。

在斜率FSK模式下29脚的电平和“三角形”位的上升沿决定扫频是从F1或F2开始(如图42)。

如果29脚电平是高电平而不是低电平,扫频则从F2开始而不是F1。

在F1和F2之间的斜率变化时,通过改变20位频率变化控制字和频率步进控制字,可增加斜率FSK模式的灵活性。

结合多个线性斜率变化和各分段的不同斜率设置,可实现非线性的频率变化。

在不同的设置下,DDS的输出频率在Fl和F2之间以不同的方式变化,实现多种方式扫频。

脉冲调频(模式011)“Chirp”也称为“脉冲调频”( Pulsed FM) 。

该模式下,输出信号的频率在指定的范围和精度上发生线性或非线性的变化,扫描方向可以编程控制。