三输入与非门版图

三输入或门版图设计

三输入或门版图设计等级:(优秀、良好、中等、及格、不及格)评阅人:职称:日期:年月日目录1 绪论 01.1设计背景 01.2版图设计方法 (1)1.3设计目标 (1)2 三输入或门电路 (2)2.1电路结构 (2)2.2三输入或门电路仿真 (3)2.3三输入或门电路的版图绘制 (3)2.4三输入或门版图电路仿真 (9)2.5LVS检查匹配 (10)3 总结 (12)参考文献 (12)1 绪论1.1设计背景随着集成电路技术的日益进步,使得计算机辅助设计(CAD)技术已成为电路设计师不可缺少的有力工具[1]。

国内外电子线路CAD软件的相继推出与版本更新,使CAD技术的应用渗透到电子线路与系统设计的各个领域,如芯片版图的绘制、电路的绘图、模拟电路仿真、逻辑电路仿真、优化设计、印刷电路板的布线等。

CAD技术的发展使得电子线路设计的速度、质量和精度得以保证。

在众多的CAD工具软件中,Spice程序是精度最高、最受欢迎的软件工具,tanner 是用来IC版图绘制软件,许多EDA系统软件的电路模拟部分是应用Spice程序来完成的,而tanner软件是一款学习阶段应用的版图绘制软件,对于初学者是一个上手快,操作简单的EDA软件。

Tanner集成电路设计软件是由Tanner Research 公司开发的基于Windows 平台的用于集成电路设计的工具软件。

该软件功能十分强大,易学易用,包括S-Edit,T-Spice,W-Edit,L-Edit与LVS,从电路设计、分析模拟到电路布局一应俱全。

其中的L-Edit版图编辑器在国内应用广泛,具有很高知名度。

L-Edit Pro是Tanner EDA软件公司所出品的一个IC设计和验证的高性能软件系统模块,具有高效率,交互式等特点,强大而且完善的功能包括从IC设计到输出,以及最后的加工服务,完全可以媲美百万美元级的IC设计软件。

L-Edit Pro包含IC设计编辑器(Layout Editor)、自动布线系统(Standard Cell Place & Route)、线上设计规则检查器(DRC)、组件特性提取器(Device Extractor)、设计布局与电路netlist的比较器(LVS)、CMOS Library、Marco Library,这些模块组成了一个完整的IC设计与验证解决方案[2]。

三输入或门版图设计的

1绪论1.1 设计背景随着集成电路技术的日益进步,使得计算机辅助设计(CAD)技术已成为电路设计师不可缺少的有力工具[1]。

国内外电子线路CAD软件的相继推出与版本更新,使CAD技术的应用渗透到电子线路与系统设计的各个领域,如芯片版图的绘制、电路的绘图、模拟电路仿真、逻辑电路仿真、优化设计、印刷电路板的布线等。

CAD技术的发展使得电子线路设计的速度、质量和精度得以保证。

在众多的CAD工具软件中,Spice程序是精度最高、最受欢迎的软件工具,tanner 是用来IC版图绘制软件,许多EDA系统软件的电路模拟部分是应用Spice程序来完成的,而tanner软件是一款学习阶段应用的版图绘制软件,对于初学者是一个上手快,操作简单的EDA软件。

Tanner集成电路设计软件是由Tanner Research 公司开发的基于Windows 平台的用于集成电路设计的工具软件。

该软件功能十分强大,易学易用,包括S-Edit,T-Spice,W-Edit,L-Edit与LVS,从电路设计、分析模拟到电路布局一应俱全。

其中的L-Edit版图编辑器在国内应用广泛,具有很高知名度。

L-Edit Pro是Tanner EDA软件公司所出品的一个IC设计和验证的高性能软件系统模块,具有高效率,交互式等特点,强大而且完善的功能包括从IC设计到输出,以及最后的加工服务,完全可以媲美百万美元级的IC设计软件。

L-Edit Pro包含IC设计编辑器(Layout Editor)、自动布线系统(Standard Cell Place & Route)、线上设计规则检查器(DRC)、组件特性提取器(Device Extractor)、设计布局与电路netlist的比较器(LVS)、CMOS Library、Marco Library,这些模块组成了一个完整的IC设计与验证解决方案[2]。

L-Edit Pro丰富完善的功能为每个IC 设计者和生产商提供了快速、易用、精确的设计系统。

CD4023 CMOS 三3输入与非门

TL F 5956CD4023BM CD4023BC Buffered Triple 3-Input NAND Gate CD4025BM CD4025BC Buffered Triple 3-Input NOR GateFebruary 1988CD4023BM CD4023BCBuffered Triple 3-Input NAND Gate CD4025BM CD4025BCBuffered Triple 3-Input NOR GateGeneral DescriptionThese triple gates are monolithic complementary MOS (CMOS)integrated circuits constructed with N-and P-chan-nel enhancement mode transistors They have equal source and sink current capabilities and conform to standard B se-ries output drive The devices also have buffered outputs which improve transfer characteristics by providing very high gain All inputs are protected against static discharge with diodes to V DD and V SSFeaturesY Wide supply voltage range 3 0V to 15V Y High noise immunity 0 45V DD (typ )YLow power TTL fan out of 2driving 74L compatibility or 1driving 74LS Y 5V–10V–15V parametric ratings Y Symmetrical output characteristicsYMaximum input leakage 1m A at 15V over full temperature rangeConnection DiagramsCD4023BM CD4023BC Dual-In-Line PackageTL F 5956–1Top ViewCD4025BM CD4025BC Dual-In-Line PackageTL F 5956–2Top ViewOrder Number CD4023B or CD4025BC 1995National Semiconductor Corporation RRD-B30M105 Printed in U S AAbsolute Maximum Ratings (Notes 1 2)If Military Aerospace specified devices are required please contact the National Semiconductor Sales Office Distributors for availability and specifications DC Supply Voltage (V DD )b 0 5V DC to a 18V DC Input Voltage (V IN )b 0 5V DC to V DD a 0 5V DCStorage Temp Range (T S )b 65 C to a 150 CPower Dissipation (P D )Dual-In-Line 700mW Small Outline 500mW Lead Temperature (T L )(Soldering 10seconds)260 CRecommended Operating ConditionsDC Supply Voltage (V DD )5V DC to 15V DC Input Voltage (V IN )0V DC to V DD V DCOperating Temperature Range (T A )CD4023BM CD4025BM b 55 C to a 125 C CD4023BC CD4025BCb 40 C to a 85 CDC Electrical Characteristics CD4023BM CD4025BM (Note 2)Symbol ParameterConditionsb 55 Ca 25 Ca 125 CUnits Min Typ Min Typ Max Min Max I DDQuiescent Device Current V DD e 5V0 250 0040 257 5m A V DD e 10V 0 50 0050 515m A V DD e 15V 1 00 0061 030m A V OLLow Level Output Voltage V DD e 5V0 0500 050 05V V DD e 10V 0 0500 050 05V V DD e 15V 0 050 050 05V V OHHigh Level Output Voltage V DD e 5V4 954 9554 95V V DD e 10V 9 959 95109 95V V DD e 15V 14 9514 951514 95VV ILLow Level Input VoltageV DD e 5V V O e 4 5V 1 521 51 5V V DD e 10V V O e 9 0V l I O l k 1m A3 043 03 0V V DD e 15V V O e 13 5V (4 064 04 0V V IHHigh Level Input VoltageV DD e 5V V O e 0 5V 3 53 533 5V V DD e 10V V O e 1 0V lI O l k 1m A7 07 067 0V V DD e 15V V O e 1 5V(11 011 0911 0V I OLLow Level Output Current V DD e 5V V O e 0 4V 0 640 510 880 36mA (Note 3)V DD e 10V V O e 0 5V1 61 32 20 90mA V DD e 15V V O e 1 5V4 23 482 4mA I OHHigh Level Output Current V DD e 5V V O e 4 6V b 0 64b 0 51b 0 88b 0 36mA (Note 3)V DD e 10V V O e 9 5Vb 1 6b 1 3b 2 2b 0 90mA V DD e 15V V O e 13 5V b 4 2b 3 4b 8b 2 4mAI INInput CurrentV DD e 15V V IN e 0V b 0 10b 10b 5b 0 10b 1 0m AV DD e 15V V IN e 15V0 1010b 50 101 0m ASchematic DiagramCD4023BC CD4023BMTL F 5956–3Device Shown All Inputs Protectedby Standard CMOS Input Protection Circuit2DC Electrical Characteristics CD4023BC CD4025BC (Note 2)Symbol ParameterConditionsb 40 Ca 25 Ca 85 CUnits Min Typ Min Typ Max Min Max I DDQuiescent Device Current V DD e 5V1 00 0041 07 5m A V DD e 10V2 00 0052 015m A V DD e 15V 4 00 0064 030m A V OLLow Level Output Voltage V DD e 5V0 0500 050 05V V DD e 10V 0 0500 050 05V V DD e 15V 0 050 050 05V V OHHigh Level Output Voltage V DD e 5V4 954 9554 95V V DD e 10V 9 959 95109 95V V DD e 15V 14 9514 951514 95VV ILLow Level Input VoltageV DD e 5V V O e 4 5V 1 521 51 5V V DD e 10V V O e 9 0V l I O l k 1m A3 043 03 0V V DD e 15V V O e 13 5V (4 064 04 0V V IHHigh Level Input VoltageV DD e 5V V O e 0 5V 3 53 533 5V V DD e 10V V O e 1 0V l I O lk 1m A7 07 067 0V V DD e 15V V O e 1 5V(11 011 0911 0V I OLLow Level Output Current V DD e 5V V O e 0 4V 0 520 440 880 36mA (Note 3)V DD e 10V V O e 0 5V1 31 12 20 90mA V DD e 15V V O e 1 5V3 63 082 4mA I OHHigh Level Output Current V DD e 5V V O e 4 6V b 0 52b 0 44b 0 88b 0 36mA (Note 3)V DD e 10V V O e 9 5Vb 1 3b 1 1b 2 2b 0 90mA V DD e 15V V O e 13 5V b 3 6b 3 0b 8b 2 4mAI INInput CurrentV DD e 15V V IN e 0V b 0 3b 10b 5b 0 3b 1 0m AV DD e 15V V IN e 15V0 310b 50 31 0m ANote 1 ‘‘Absolute Maximum Ratings’’are those values beyond which the safety of the device cannot be guaranteed they are not meant to imply that the devices should be operated at these limits The table of ‘‘Recommended Operating Conditions’’and ‘‘Electrical Characteristics’’provides conditions for actual device operationNote 2 V SS e 0V unless otherwise specified Note 3 I OH and I OL are tested one output at a timeSchematic DiagramCD4025BM CD4025BCTL F 5956–4Device Shown All Inputs Protectedby Standard CMOS Input Protection Circuit3AC Electrical Characteristics T A e25 C C L e50pF R L e200k unless otherwise specifiedCD4023BC CD4025BCSymbol Parameter Conditions CD4023BM CD4025BM UnitsMin Typ Max Min Typ Maxt PHL Propagation Delay High-to-Low Level V DD e5V130250130250nsV DD e10V6010060100nsV DD e15V40704070nst PLH Propagation Delay Low-to-High Level V DD e5V110250120250nsV DD e10V5010060100nsV DD e15V35704070nst THL Transition Time V DD e5V9020090200ns t TLH V DD e10V5010050100nsV DD e15V40804080ns C IN Average Input Capacitance Any Input57 557 5pF C PD Power Dissipation Capacity(Note4)Any Gate1717pF AC Parameters are guaranteed by DC correlated testingNote4 C PD determines the no load AC power consumption of any CMOS device For complete explanation see54C 74C Family Characteristics Application Note AN-904Physical Dimensions inches(millimeters)Ceramic Dual-In-Line Package(J)Order Number CD4023BMJ CD4023BCJ CD4025BMJ or CD4025BCJNS Package Number J14A5C D 4023B M C D 4023B C B u f f e r e d T r i p l e 3-I n p u t N A N D G a t e C D 4025B M C D 4025B C B u f f e r e d T r i p l e 3-I n p u t N O R G a t ePhysical Dimensions inches (millimeters)(Continued)Molded Dual-In-Line Package (N)Order Number CD4023BMN CD4023BCN CD4025BMN or CD4025BCNNS Package Number N14ALIFE SUPPORT POLICYNATIONAL’S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF NATIONAL SEMICONDUCTOR CORPORATION As used herein 1 Life support devices or systems are devices or 2 A critical component is any component of a life systems which (a)are intended for surgical implant support device or system whose failure to perform can into the body or (b)support or sustain life and whose be reasonably expected to cause the failure of the life failure to perform when properly used in accordance support device or system or to affect its safety or with instructions for use provided in the labeling can effectivenessbe reasonably expected to result in a significant injury to the userNational Semiconductor National Semiconductor National Semiconductor National Semiconductor CorporationEuropeHong Kong LtdJapan Ltd1111West Bardin RoadFax (a 49)0-180-530858613th Floor Straight Block Tel 81-043-299-2309。

4025 CMOS 三3输入或非门

Features

Y Y Y

Y Y Y

Wide supply voltage range 3 0V to 15V High noise immunity 0 45 VDD (typ ) Low power TTL fan out of 2 driving 74L compatibility or 1 driving 74LS 5V – 10V – 15V parametric ratings Symmetrical output characteristics Maximum input leakage 1 mA at 15V over full temperature range

VOHHale Waihona Puke 4 95 9 95 14 95

4 95 9 95 14 95 15 30 40

5 10 15 2 4 6 15 30 40

4 95 9 95 14 95 15 30 40 35 70 11 0 0 36 0 90 24

b 0 5 VDC to a 18 VDC b 0 5 VDC to VDD a 0 5 VDC b 65 C to a 150 C

Recommended Operating Conditions

DC Supply Voltage (VDD) Input Voltage (VIN) Operating Temperature Range (TA) CD4023BM CD4025BM CD4023BC CD4025BC 5 VDC to 15 VDC 0 VDC to VDD VDC

General Description

These triple gates are monolithic complementary MOS (CMOS) integrated circuits constructed with N- and P-channel enhancement mode transistors They have equal source and sink current capabilities and conform to standard B series output drive The devices also have buffered outputs which improve transfer characteristics by providing very high gain All inputs are protected against static discharge with diodes to VDD and VSS

三输入或门版图设计的

1绪论1、1 设计背景随着集成电路技术得日益进步,使得计算机辅助设计(CAD)技术已成为电路设计师不可缺少得有力工具[1]。

国内外电子线路CAD软件得相继推出与版本更新,使CAD技术得应用渗透到电子线路与系统设计得各个领域,如芯片版图得绘制、电路得绘图、模拟电路仿真、逻辑电路仿真、优化设计、印刷电路板得布线等、CAD技术得发展使得电子线路设计得速度、质量与精度得以保证、在众多得CAD 工具软件中,Spice程序就是精度最高、最受欢迎得软件工具,tanner就是用来IC版图绘制软件,许多EDA系统软件得电路模拟部分就是应用Spice程序来完成得,而tanner软件就是一款学习阶段应用得版图绘制软件,对于初学者就是一个上手快,操作简单得EDA软件、Tanner集成电路设计软件就是由Tanner Research 公司开发得基于Windows平台得用于集成电路设计得工具软件、该软件功能十分强大,易学易用,包括S-Edit,T-Spice,W-Edit,L—Edit与LVS,从电路设计、分析模拟到电路布局一应俱全。

其中得L—Edit版图编辑器在国内应用广泛,具有很高知名度。

L-Edit Pro就是Tanner EDA软件公司所出品得一个IC设计与验证得高性能软件系统模块,具有高效率,交互式等特点,强大而且完善得功能包括从IC设计到输出,以及最后得加工服务,完全可以媲美百万美元级得IC设计软件、L-Edit Pro包含IC设计编辑器(Layout Editor)、自动布线系统(Sta ndard Cell Place & Route)、线上设计规则检查器(DRC)、组件特性提取器(Device Extractor)、设计布局与电路netlist得比较器(LVS)、CMOS Li brary、Marco Library,这些模块组成了一个完整得IC设计与验证解决方案[2]。

L-Edit Pro丰富完善得功能为每个IC设计者与生产商提供了快速、易用、精确得设计系统。

三输入或门版图设计

1绪论1.1 设计背景随着集成电路技术的日益进步,使得计算机辅助设计(CAD)技术已成为电路设计师不可缺少的有力工具[1]。

国内外电子线路CAD软件的相继推出与版本更新,使CAD技术的应用渗透到电子线路与系统设计的各个领域,如芯片版图的绘制、电路的绘图、模拟电路仿真、逻辑电路仿真、优化设计、印刷电路板的布线等。

CAD技术的发展使得电子线路设计的速度、质量和精度得以保证。

在众多的CAD工具软件中,Spice程序是精度最高、最受欢迎的软件工具,tanner是用来IC版图绘制软件,许多EDA系统软件的电路模拟部分是应用Spice程序来完成的,而tanner软件是一款学习阶段应用的版图绘制软件,对于初学者是一个上手快,操作简单的EDA软件。

Tanner集成电路设计软件是由Tanner Research 公司开发的基于Windows 平台的用于集成电路设计的工具软件。

该软件功能十分强大,易学易用,包括S-Edit,T-Spice,W-Edit,L-Edit与LVS,从电路设计、分析模拟到电路布局一应俱全。

其中的L-Edit版图编辑器在国内应用广泛,具有很高知名度。

L-Edit Pro是Tanner EDA软件公司所出品的一个IC设计和验证的高性能软件系统模块,具有高效率,交互式等特点,强大而且完善的功能包括从IC设计到输出,以及最后的加工服务,完全可以媲美百万美元级的IC设计软件。

L-Edit Pro包含IC设计编辑器(Layout Editor)、自动布线系统(Standard Cell Place & Route)、线上设计规则检查器(DRC)、组件特性提取器(Device Extractor)、设计布局与电路netlist的比较器(LVS)、CMOS Library、Marco Library,这些模块组成了一个完整的IC设计与验证解决方案[2]。

L-Edit Pro 丰富完善的功能为每个IC设计者和生产商提供了快速、易用、精确的设计系统。

三输入或非门版图

文档来源为:从网络收集整理.word版本可编辑.欢迎下载支持. 三输入或非门版图设计目录1.绪论 .............................................................................................. 错误!未定义书签。

1.1版图设计基础知识.............................. 错误!未定义书签。

1.2版图设计方法 01.3设计目标 (2)2.三输入或非门电路 (3)2.1三输入或非门电路结构 (3)2.2三输入或非门电路电路仿真 (4)2.3三输入或非门电路的版图绘制 (5)2.4三输入或非门电路的版图电路仿真 (6)2.5LVS检查匹配 (7)总结 (8)参考文献 (9)附录一:原理图网表 (10)附录二:版图网表 (10)1 绪论1.1 版图设计基础知识集成电路从60年代开始,经历了小规模集成,中规模集成,大规模集成,到目前的超大规模集成。

单个芯片上已经可以制作含几百万个晶体管的一个完整的数字系统或数模混合的电子系统。

在整个设计过程中,版图(layout)设计或者称作物理设计(physical design)是其中重要的一环。

他是把每个原件的电路表示转换成集合表示,同时,元件间连接的线网也被转换成几何连线图形[1]。

对于复杂的版图设计,一般把版图设计分成若干个子步骤进行:划分为了将处理问题的规模缩小,通常把整个电路划分成若干个模块。

版图规划和布局是为了每个模块和整个芯片选择一个好的布图方案。

布线完成模块间的互连,并进一步优化布线结果。

压缩是布线完成后的优化处理过程,他试图进一步减小芯片的面积。

1.2 版图设计方法可以从不同角度对版图设计方法进行分类。

如果按设计自动化程度来分,可将版图设计方法分成手工设计和自动设计2大类。

如果按照对布局布线位置的限制和布局模块的限制来分,则可把设计方法分成全定制(fullcustom)和半定制(semicustom)2大类。

三输入与非门电路设计

1绪论1.1设计背景集成电路的出现与飞速发展彻底改变了人类文明和人们日常生活的面目。

近几年,中国集成电路产业取得了飞速发展。

集成电路掩模版图设计是实现集成电路制造所必不可少的设计环节,它不仅关系到集成电路的功能是否正确,而且也会极大程度地影响集成电路的性能、成本与功耗。

集成电路掩模版图设计是一门技术,它需要设计者具有电路系统原理与工艺制造方面的基础知识。

但它更需要设计者的创造性、空间想象力和耐性,需要设计者长期工作的经验和知识的积累,需要设计者对日新月异的集成电路发展密切关注和探索。

互补金属-氧化物-半导体集成电路,简称CMOS电路,是集成电路中于六十年代后期才发展起来的后起之秀。

到了六十年代,随着平面型晶体管的发展,以及人们对于半导表面性质认识的深化,特别是具有优良性能的热生长二氧化硅薄膜的成功生长,才导致MOS绝缘栅场效应晶体管和MOS集成电路的问世。

为了把设计的线路生产为集成电路,还必须进行版图设计。

即根据线路中各器件的尺寸和互连进行合理的布局。

版图设计的优劣,很大程度上决定了产品的成品率和可靠性。

在版图设计中的考虑原则是尽可能缩小有源区(即仅包括器件和互连引线部分,不包括键合点)。

这不仅可以减小芯片面积,而且有利于成品率提高。

电源线和地线的走线要通畅,减小串联电阻,保证电路的参量指标。

在可能的条件下,引线孔尽量开大,保证接触良好。

现代化的计算机辅助制版技术,能大大减小人力,做出最佳图形,特别是为大规模集成电路所必需。

中国集成电路产业已经形成了IC设计、制造、封装测试三业及支撑配套业共同发展的较为完善的产业链格局,随着IC设计和芯片制造行业的迅猛发展,国内集成电路价值链格局继续改变,其总体趋势是设计业和芯片制造业所占比例迅速上升。

1.2设计目标1.用tanner软件中的原理图编辑器S-Edit编辑三输入与门电路原理图。

2.用tanner软件中的L-Edit绘制三输入与门电路版图,并进行DRC 验证。

2、3、4输入或非门版图设计

《集成电路工艺与版图设计》课堂作业班级:电子科学与技术01班姓名:曾海学号:201031722、3、4输入异或门版图设计如下:一、二输入异或门:(1)原理图:<2>L-edit中进行设计的如下二输入或非门版图<3>提取后在T-SPICE中进行参数及输入输出设置如下:VA A GND BIT ({1011} pw=20N lt=10N ht=10N on=5 off=0)VB B GND BIT ({0010} pw=20N lt=10N ht=10N on=5 off=0)Vdd Vdd GND 5.tran 10N 100N.print tran v(OUT) v(A) v(B)<4>在W-EDIT中得到仿真波形图:二、三输入或非门<1>三输入异或门版图<3>参数及输入输出设置VA A GND BIT ({1011} pw=20N lt=10N ht=10N on=5 off=0) VB B GND BIT ({0010} pw=20N lt=10N ht=10N on=5 off=0)Vdd Vdd GND 5.tran 10N 100N.print tran v(OUT) v(A) v(B)<3>仿真图三、四输入或非门<1>版图设计<2>参数及输入输设置Vdd Vdd GND 5VA A GND BIT ({1001} pw=20N lt=10N ht=10N on=5 off= 0)VB B GND BIT ({1010} pw=20N lt=10N ht=10N on=5 off= 0)VC C GND BIT ({1011} pw=20N lt=10N ht=10N on=5 off= 0)VD D GND BIT ({1011} pw=20N lt=10N ht=10N on=5 off= 0).tran 20N 100N.print tran v(OUT) v(A) v(B) v(C) v(D)<3>仿真图4、版图设计总结(1)本次设计中,由仿真图可以看出,仿真波形不是标准的方波图形,而是有相应的误差,可能是由于版图的设计中,布线或器件的放置不合理导致的。

三输入与非门版图设计

目录1 绪论 (1)1.1 设计背景 (1)1.2 设计目标 (2)2 三输入与非门电路原理图编辑 (3)2.1 三输入与非门电路结构 (3)2.2 三输入与非门电路仿真分析波形 (4)2.3 三输入与非门电路的版图绘制 (5)2.4 三输入与非门版图电路仿真并分析波形 (6)2.5 LVS检查匹配 (7)总结 (8)参考文献 (9)附录一:电路原理图网表 (10)附录二:版图网表 (11)1 绪论1.1 设计背景随着集成电路技术的日益进步,使得计算机辅助设计(CAD)技术已成为电路设计师不可缺少的有力工具[1]。

国内外电子线路CAD软件的相继推出与版本更新,使CAD技术的应用渗透到电子线路与系统设计的各个领域,如芯片版图的绘制、电路的绘图、模拟电路仿真、逻辑电路仿真、优化设计、印刷电路板的布线等。

CAD技术的发展使得电子线路设计的速度、质量和精度得以保证。

tanner是用来IC版图绘制软件,许多EDA系统软件的电路模拟部分是应用Spice 程序来完成的,而tanner软件是一款学习阶段应用的版图绘制软件。

Tanner集成电路设计软件是由Tanner Research 公司开发的基于Windows平台的用于集成电路设计的工具软件。

该软件功能十分强大,易学易用,包括S-Edit,T-Spice,W-Edit,L-Edit与LVS,从电路设计、分析模拟到电路布局一应俱全。

其中的L-Edit 版图编辑器在国内应用广泛,具有很高知名度。

L-Edit Pro是Tanner EDA软件公司所出品的一个IC设计和验证的高性能软件系统模块,具有高效率,交互式等特点,强大而且完善的功能包括从IC设计到输出,以及最后的加工服务,完全可以媲美百万美元级的IC设计软件L-Edit Pro 包含IC设计编辑器(Layout Editor)、自动布线系统(Standard Cell Place & Route)、线上设计规则检查器(DRC)、组件特性提取器(Device Extractor)、设计布局与电路netlist的比较器(LVS)、CMOS Library、Marco Library,这些模块组成了一个完整的IC设计与验证解决方案。

三输入与非门VHDL讲解

贴心建议:初学时,对于简单的程序,先尽自己努力看懂每一句话,从字面上先去理解,通过英文单词的意思,自己先去琢磨该段程序所要实现的功能,然后再去和正确的意思相比对,这样比一开始就去看解释来的记忆深刻,这些是我自己的切身体会。

1.三输入与非门在数字电路设计中,门电路是最基本的电路单元。

在这里我们挑选了比较典型的三输入的与非门,完成我们的第一个设计。

三输入与非门的逻辑表达式:F ABC逻辑符号为:源代码:逐行解释:1:库声明。

告诉编译器,我要使用这个库里的内容。

语法是:LIBRARY 库名;(结束有个分号的,别丢了,这个分号是每条语句的结束标志,每条语句最后都是要有分号的,这是它们的标配)。

2~4:声明所选择的程序包名称,ALL就是打开整个程序包。

一个库里当然有很多的程序包了,给编译器指明一下那个包要用,好缩小它的搜寻范围。

别让它满库的找,怪费俺们的CPU的。

语法:USE 库名.程序包.程序包的组成部分;。

一句话总结:1和2两句其实相当于C中的“#include<>”,使被声明的库和库中的元件对当前设计项目可见。

发散:IEEE库是最重要的资源库,我们经常使用其中的一些信号定义和数据的定义。

列举一下其中比较重要的几个程序包:(1)STD_LOGIC_1164:指定了STD_LOGIC和STD_ULOGIC逻辑系统(2)STD_LOGIC_ARITH:包含SIGNED和UNSIGNED数据类型定义和相应的算术和比较操作还包含了几个数据转换函数,允许数据从一个类型转换为另一个类型。

(3)STD_LOGIC_UNSIGNED:CONV_INTEGER(A)由INTEGER,UNSDGNED,SIGNED转换成STD_LOGIC_VECTOR由UNSIGNED,SIGNED转换成INTEGER(4)STD_LOGIC_SIGNED:包含了STD_LOGIC和STD_LOGIC_VECTOR其中,在一个程序中只要包含(1),(2),(3)就足够能应付绝大多的应用了。

三输入与非门版图

三输入与非门的版图1、版图2、Spice网表文件* Circuit Extracted by Tanner Research's L-Edit Version 13.00 / Extract Version 13.00 ;* TDB File: G:\bantu\NAND3.1.tdb* Cell: Cell0 Version 1.36* Extract Definition File: C:\Users\tbmei\Documents\Tanner EDA\Tanner Tools v13.0\L-Edit and LVS\SPR\Lights\Layout\lights.ext* Extract Date and Time: 06/09/2014 - 18:17.include "G:\bantu\ml5_20.md"* Warning: Layers with Unassigned FRINGE Capacitance.* <Pad Comment>* <Poly1-Poly2 Capacitor ID>* NODE NAME ALIASES* 1 = vdd (0 , 60)* 2 = Gnd (0 , 0)* 3 = OUT (14 , 20)* 4 = C (40 , 31)* 5 = B (27 , 31)* 6 = A (2 , 38)M1 OUT C1 vdd vdd PMOS L=3u W=20u AD=96p PD=52u AS=100p PS=30u $ (37 46 40 66)M2 vdd B OUT vdd PMOS L=3u W=20u AD=100p PD=30u AS=110p PS=31u $ (24 46 27 66)M3 OUT A vdd vdd PMOS L=3u W=20u AD=110p PD=31u AS=108p PS=54u $ (10 46 13 66)M4 OUT C1 9 8 NMOS L=3u W=20u AD=120p PD=56u AS=100p PS=30u $ (37 0 40 20)M5 9 B 7 8 NMOS L=3u W=20u AD=100p PD=30u AS=110p PS=31u $ (24 0 27 20)M6 7 A Gnd 8 NMOS L=3u W=20u AD=110p PD=31u AS=172p PS=60u $ (10 0 13 20).include "G:\bantu\ml5_20.md".tran 600n 600n start=0VDDD vdd Gnd 3VAin A Gnd pwl (0ns 0V 100ns 0V 105ns 3V 200ns 3V 205ns 0V 300ns 0V 305ns 3V 400ns 3V 405ns 0V 500ns 0V 505ns 3V 600ns 3V)VBin B Gnd pwl (0ns 0V 100ns 0V 105ns 0V 200ns 0V 205ns 3V 300ns 3V 305ns 3V 400ns 3V 405ns 0V 500ns 0V 505ns 3V 600ns 3V)VCin C1 Gnd pwl (0ns 0V 100ns 0V 105ns 0V 200ns 0V 205ns 0V 300ns 0V 305ns 0V 400ns 0V 405ns 3V 500ns 3V 505ns 3V 600ns 3V).print tran v(A,Gnd).print tran v(B,Gnd).print tran v(C1,Gnd).print tran v(OUT,Gnd)* Pins of element D2 are shorted:* D2 vdd vdd D_lateral $ (3 58 7 66)* Total Nodes: 9* Total Elements: 8* Total Number of Shorted Elements not written to the SPICE file: 0* Output Generation Elapsed Time: 0.000 sec* Total Extract Elapsed Time: 0.687 sec.END3、仿真波形图4、波形分析输入信号A、B、C1中至少一个为低电平时,输出OUT为高电平;只有输入信号A、B、C1同时为高电平时,输出OUT为低电平。

基于Cadence平台三输入或非门的设计

基于Cadence 平台三输入或非门的设计设计目的:1、熟悉candence 软件,并掌握其各种工具的使用方法。

2、用cadence 设计一个三输入或非门,并画出仿真电路、版图、并验证其特性。

一、设计背景1.cadence 简介:Cadence 公司的电子设计自动化(Electronic Design Automation )产品涵盖了电子设计的整个流程,包括系统级设计,功能验证,IC 综合及布局布线,模拟、混合信号及射频IC 设计,全定制 集成电路设计,IC 物理验证,PCB 设计和硬件仿真建模等。

本次设计是基于cadence 工具的三输入或非门的电路和版图设计。

2.三输入或非门:a.逻辑表达式:b.逻辑符号:c.真值表:CB A Y ++=二、三输入或非门电路设计和逻辑仿真进入红帽4系统,打开终端输入cd Artist446进入Artist446目录,输入icms &命令运行Cadence软件。

在打开的CIW的窗口选择tools →Library Manager建立一个新的库文件myLib,在创建一个新的cellview1、在schematic窗口中选择Tools →Analog Evironment,打开模拟窗口1、setup →simulator /directory/host…,在弹出窗口中确认simulator项是spectre.单击ok。

2、setup →Model Library setup,做如下输入,然后add。

3、选择Analyses →Choose,在坦诚的窗口中吧stop time设为50u4、选择outputs →save all.5、选择outputs →to be plotted →select on schematic,然后在schematic窗口中依次选择A、B、C、Y为输入和输出,选择之后按ESC。

6、选择完毕后窗口如下图所示7、选择Simulation →Netlist →Create8、选择Simulation →Run三、版图设计:登录Linux系统,启动终端,cd Layout进入版图目录,然后以layoutPlus &运行版图设计软件,进行版图设计。

三输入或门版图设计的样本

1绪论1.1 设计背景随着集成电路技术日益进步,使得计算机辅助设计(CAD)技术已成为电路设计师不可缺少有力工具[1]。

国内外电子线路CAD软件相继推出与版本更新,使CAD技术应用渗入到电子线路与系统设计各个领域,如芯片版图绘制、电路绘图、模仿电路仿真、逻辑电路仿真、优化设计、印刷电路板布线等。

CAD技术发展使得电子线路设计速度、质量和精度得以保证。

在众多CAD工具软件中,Spice程序是精度最高、最受欢迎软件工具,tanner是用来IC版图绘制软件,许多EDA 系统软件电路模仿某些是应用Spice程序来完毕,而tanner软件是一款学习阶段应用版图绘制软件,对于初学者是一种上手快,操作简朴EDA软件。

Tanner集成电路设计软件是由Tanner Research 公司开发基于Windows平台用于集成电路设计工具软件。

该软件功能十分强大,易学易用,涉及S-Edit,T-Spice,W-Edit,L-Edit与LVS,从电路设计、分析模仿到电路布局一应俱全。

其中L-Edit版图编辑器在国内应用广泛,具备很高知名度。

L-Edit Pro是Tanner EDA软件公司所出品一种IC设计和验证高性能软件系统模块,具备高效率,交互式等特点,强大并且完善功能涉及从IC设计到输出,以及最后加工服务,完全可以媲美百万美元级IC设计软件。

L-Edit Pro包括IC设计编辑器(Layout Editor)、自动布线系统(Standard Cell Place & Route)、线上设计规则检查器(DRC)、组件特性提取器(Device Extractor)、设计布局与电路netlist比较器(LVS)、CMOS Library、Marco Library,这些模块构成了一种完整IC设计与验证解决方案[2]。

L-Edit Pro丰富完善功能为每个IC设计者和生产商提供了迅速、易用、精准设计系统。

虽然SPICE开发至今已超过,然而其重要性并未随着制程进步而减少。

三输入异或门版图设计

三输入CMOS异或门

版图设计

学院:

专业:集成电路

姓名:何 宝 华

学号: vbop25@ __

课程名称: VLSI 导论

日期:2011年 12月16日

1名称

三输入CMOS异或门版图设计

2目的

绘制三输入一输出CMOS异或门的版图设计,并对其进行DRC检测和T-Spice模拟仿真。

3设备和工具

PC计算机一台,Tanner软件。

4版图设计要求

(1)0.25u工艺

(2)3输入xor

(3)原理图

(4)原理图有spice仿真

(5)版图

(6)LVS

(7)有封皮

5 S-Edit电路图

电路图1

电路图2

6 T-Spice模拟

7 T-Spice仿真

8 真值表

0011

0101

10

9 验证结果

结合T-Spice仿真图和真值表,表明电路图设计是正确的。

10 L-Edit版图设计

11 DRC检测

12 LVS比较

13 结论

三输入一输出异或门版图设计是正确的。

2、3、4输入或非门版图设计

《集成电路工艺与版图设计》课堂作业班级:电子科学与技术01班姓名:曾海学号:201031722、3、4输入异或门版图设计如下:一、二输入异或门:(1)原理图:<2>L-edit中进行设计的如下二输入或非门版图<3>提取后在T-SPICE中进行参数及输入输出设置如下:VA A GND BIT ({1011} pw=20N lt=10N ht=10N on=5 off=0)VB B GND BIT ({0010} pw=20N lt=10N ht=10N on=5 off=0)Vdd Vdd GND 5.tran 10N 100N.print tran v(OUT) v(A) v(B)<4>在W-EDIT中得到仿真波形图:二、三输入或非门<1>三输入异或门版图<3>参数及输入输出设置VA A GND BIT ({1011} pw=20N lt=10N ht=10N on=5 off=0) VB B GND BIT ({0010} pw=20N lt=10N ht=10N on=5 off=0)Vdd Vdd GND 5.tran 10N 100N.print tran v(OUT) v(A) v(B)<3>仿真图三、四输入或非门<1>版图设计<2>参数及输入输设置Vdd Vdd GND 5VA A GND BIT ({1001} pw=20N lt=10N ht=10N o n=5 off=0)VB B GND BIT ({1010} pw=20N lt=10N ht=10N o n=5 off=0)VC C GND BIT ({1011} pw=20N lt=10N ht=10N o n=5 off=0)VD D GND BIT ({1011} pw=20N lt=10N ht=10N o n=5 off=0).tran 20N 100N.print tran v(OUT) v(A) v(B) v(C) v(D)<3>仿真图4、版图设计总结(1)本次设计中,由仿真图可以看出,仿真波形不是标准的方波图形,而是有相应的误差,可能是由于版图的设计中,布线或器件的放置不合理导致的。

三输入或非门版图

文档来源为:从网络收集整理.word版本可编辑.欢迎下载支持. 三输入或非门版图设计目录1.绪论 .............................................................................................. 错误!未定义书签。

1.1版图设计基础知识.............................. 错误!未定义书签。

1.2版图设计方法 01.3设计目标 (2)2.三输入或非门电路 (3)2.1三输入或非门电路结构 (3)2.2三输入或非门电路电路仿真 (4)2.3三输入或非门电路的版图绘制 (5)2.4三输入或非门电路的版图电路仿真 (6)2.5LVS检查匹配 (7)总结 (8)参考文献 (9)附录一:原理图网表 (10)附录二:版图网表 (10)1 绪论1.1 版图设计基础知识集成电路从60年代开始,经历了小规模集成,中规模集成,大规模集成,到目前的超大规模集成。

单个芯片上已经可以制作含几百万个晶体管的一个完整的数字系统或数模混合的电子系统。

在整个设计过程中,版图(layout)设计或者称作物理设计(physical design)是其中重要的一环。

他是把每个原件的电路表示转换成集合表示,同时,元件间连接的线网也被转换成几何连线图形[1]。

对于复杂的版图设计,一般把版图设计分成若干个子步骤进行:划分为了将处理问题的规模缩小,通常把整个电路划分成若干个模块。

版图规划和布局是为了每个模块和整个芯片选择一个好的布图方案。

布线完成模块间的互连,并进一步优化布线结果。

压缩是布线完成后的优化处理过程,他试图进一步减小芯片的面积。

1.2 版图设计方法可以从不同角度对版图设计方法进行分类。

如果按设计自动化程度来分,可将版图设计方法分成手工设计和自动设计2大类。

如果按照对布局布线位置的限制和布局模块的限制来分,则可把设计方法分成全定制(fullcustom)和半定制(semicustom)2大类。

版图设计实验报告

版图设计实验——三输入与或非门的版图实现一、实验要求1、熟悉UNIX基本命令的使用2、了解Cadence软件的使用方法3、掌握半导体集成电路的设计规则4、能够实现基本CMOS集成电路的版图设计二、实验内容使用Cadence Tools实现三输入或与非门(C=)()电路的版图+F∙AB设计,并实现其设计规则检查(DRC)和电路图与版图一致性对照检查(LVS)。

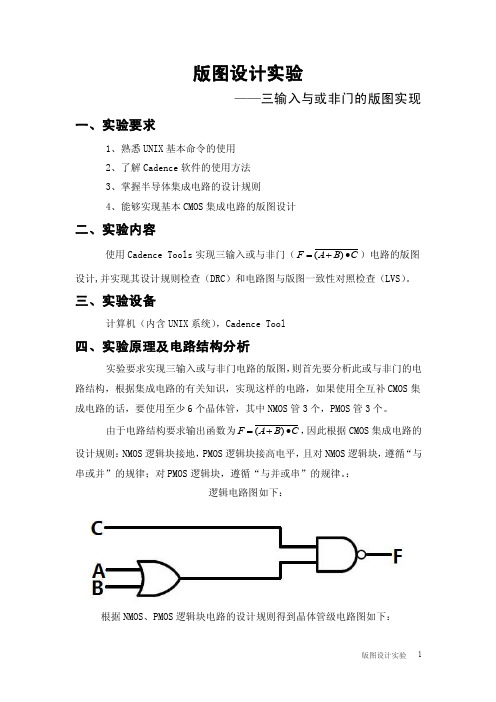

三、实验设备计算机(内含UNIX系统),Cadence Tool四、实验原理及电路结构分析实验要求实现三输入或与非门电路的版图,则首先要分析此或与非门的电路结构,根据集成电路的有关知识,实现这样的电路,如果使用全互补CMOS集成电路的话,要使用至少6个晶体管,其中NMOS管3个,PMOS管3个。

由于电路结构要求输出函数为C+(,因此根据CMOS集成电路的=)F∙AB设计规则:NMOS逻辑块接地,PMOS逻辑块接高电平,且对NMOS逻辑块,遵循“与串或并”的规律;对PMOS逻辑块,遵循“与并或串”的规律。

:逻辑电路图如下:根据NMOS、PMOS逻辑块电路的设计规则得到晶体管级电路图如下:该电路图实现的逻辑功能 A B C管子工作状态 输出C B A F ∙+=)( 0 0 0 P 管导通;N 管截止 10 0 1 t1、t2导通,t3截止;t4导通,t5、t6截止 10 1 0 t1、t2截止,t3导通;t4、t5、t6截止 10 1 1 t1、t2、t3截止;t4、t5导通,t6截止 01 0 0 t1、t2截止,t3导通;t4、t5、t6截止 11 0 1 t1、t2、t3截止;t4、t6导通,t5截止 01 1 0 t1、t2截止,t3导通;t4、t5、t6截止 11 1 1 P 管截止;N 管道通0 在初步分析了电路的结构和逻辑功能之后,接下来就是要具体的进行该电路的版图设计工作了,首先要明确几个概念。

1、版图设计规则。

主要有两种,一种是微米(um-microm )设计规则,它是一种以微米为单位的直接描述版图的最小允许尺寸,是一种绝对单位的设计规则;另一种是λ为单位的设计规则,该规则是一种相对单位,若某工艺的特征尺寸为A ,则m A μλ2=,规定最小线宽为λ2,其它最小允许尺寸均表示为λ的整数倍。

74HC10D_三输入与非门-菲利普

74HC10D_三输⼊与⾮门-菲利普DATA SHEETProduct speci?cationFile under Integrated Circuits, IC06December 1990INTEGRATED CIRCUITS74HC/HCT10Triple 3-input NAND gateFor a complete data sheet, please also download:The IC06 74HC/HCT/HCU/HCMOS Logic Family Specifications The IC06 74HC/HCT/HCU/HCMOS Logic Package Information ?The IC06 74HC/HCT/HCU/HCMOS Logic Package OutlinesFEATURESOutput capability: standard I CC category: SSI GENERAL DESCRIPTIONThe 74HC/HCT10 are high-speed Si-gate CMOS devices and are pin compatible with low power Schottky TTL (LSTTL).They are specified in compliance with JEDEC standard no. 7A.The 74HC/HCT10 provide the 3-input NAND function.QUICK REFERENCE DATAGND =0 V; T amb =25°C; t r =t f =6 ns Notes1.C PD is used to determine the dynamic power dissipation (P D in µW):P D =C PD ×V CC 2×f i + ∑(C L ×V CC 2×f O ) where:f i =input frequency in MHz f o =output frequency in MHz C L =output load capacitance in pF V CC =supply voltage in V∑(C L ×V CC 2×f o )=sum of outputs 2.For HC the condition is V I =GND to V CCFor HCT the condition is V I =GND to V CC ?1.5 V.ORDERING INFORMATIONSee “74HC/HCT/HCU/HCMOS Logic Package Information”.SYMBOL PARAMETERCONDITIONS TYPICAL UNIT HCHCTt PHL / t PLH propagation delay nA, nB, nC to nY C L =15pF; V CC =5V911ns C I input capacitance3.5 3.5pF C PD power dissipation capacitance per gatenotes 1 and 21214pFPIN DESCRIPTIONPIN NO.SYMBOL NAME AND FUNCTION1, 3, 91A to 3A data inputs2, 4, 101B to 3B data inputs13, 5, 111C to 3C data inputs12, 6, 81Y to 3Y data outputs7GND ground (0 V)14V CC positive supply voltageFig.1 Pin configuration.Fig.2 Logic symbol.Fig.3 IEC logic symbol.Fig.4 Functional diagram.Fig.5 Logic diagram (one gate).FUNCTION TABLENotes1.H=HIGH voltage levelL=LOW voltage levelINPUTS OUTPUT nA nB nC nYL L L HL L H HL H L HL H H HH L L HH L H HH H L HH H H LDC CHARACTERISTICS FOR 74HCFor the DC characteristics see“74HC/HCT/HCU/HCMOS Logic Family Specifications”. Output capability: standard I CC category: SSIAC CHARACTERISTICS FOR 74HCGND=0 V; t r=t f=6 ns; C L=50 pFSYMBOL PARAMETERT amb (°C)UNITTEST CONDITIONS74HCV CC(V)WAVEFORMS +25?40to +85?40to +125min.typ.max.min.max.min.max.t PHL/ t PLH propagation delaynA, nB, nC to nY 3095120145ns2.0Fig.6 11192429 4.5 9162025 6.0t THL/ t TLH output transition time197595110ns 2.0Fig.67151922 4.5 6131619 6.0DC CHARACTERISTICS FOR 74HCTFor the DC characteristics see “74HC/HCT/HCU/HCMOS Logic Family Specifications”.Output capability: standard I CC category: SSI Note to HCT typesThe value of additional quiescent supply current (?I CC ) for a unit load of 1 is given in the family specifications.To determine I CC per input, multiply this value by the unit load coefficient shown in the table below.AC CHARACTERISTICS FOR 74HCT GND =0 V; t r =t f =6 ns; C L =50 pFAC WAVEFORMSPACKAGE OUTLINESSee “74HC/HCT/HCU/HCMOS Logic Package Outlines”.INPUT UNIT LOAD COEFFICIENT nA, nB, nC1.5SYMBOL PARAMETERT amb (°C)UNITTEST CONDITIONS 74HCTV CC (V)WAVEFORMS+ 25?40to +85?40to +125min.typ.max.min.max.min.max.t PHL / t PLH propagation delay nA, nB, nC to nY 14243036ns 4.5Fig.6t THL / t TLHoutput transition time7151922ns4.5Fig.6Fig.6 Waveforms showing the input (nA, nB, nC) to output (nY) propagation delays and the output transition times.(1)HC : V M =50%; V I =GND to V CC . HCT: V M =1.3 V; V I =GND to 3 V.。

4023 CMOS 三3输入与非门

October 1987Revised June 1999CD4023BC Buffered Triple 3-Input NAND Gate © 1999 Fairchild Semiconductor Corporation DS005956.prf CD4023BCBuffered Triple 3-Input NAND GateGeneral DescriptionThese triple gates are monolithic complementary MOS(CMOS) integrated circuits constructed with N- and P-channel enhancement mode transistors. They have equalsource and sink current capabilities and conform to stan-dard B series output drive. The devices also have bufferedoutputs which improve transfer characteristics by providingvery high gain. All inputs are protected against static dis-charge with diodes to V DD and V SS.Featuress Wide supply voltage range: 3.0V to 15Vs High noise immunity:0.45 V DD (typ)s Low power TTL compatibility:fan out of 2 driving 74L or 1 driving 74LSs5V–10V–15V parametric ratingss Symmetrical output characteristicss Maximum input leakage 1 µA at 15V over fulltemperature rangeOrdering Code:Devices also available in T ape and Reel. Specify by appending the suffix letter “X” tot he ordering code.Connection DiagramTop ViewBlock Diagram1/3 Device Shown*All Inputs Protected by Standard CMOS Input Protection Circuit.Order Number Package Number Package DescriptionCD4023BCM M14B14-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-013, 0.300 WideCD4023BCS M14D14-Lead Small Outline Package (SOP), EIAJ TYPE II, 5.3mm WideCD4023BCN N14A14-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-001, 0.300 Wide 2C D 4023B CAbsolute Maximum Ratings (Note 1)(Note 2)Recommended Operating ConditionsNote 1: “Absolute Maximum Ratings” are those values beyond which the safety of the device cannot be guaranteed; they are not meant to imply that the devices should be operated at these limits. The table of “Recom-mended Operating Conditions” and “Electrical Characteristics” provides conditions for actual device operation.Note 2: V SS = 0V unless otherwise specified.DC Electrical Characteristics (Note 3)Note 3: V SS = 0V unless otherwise specified.Note 4: I OH and I OL are tested one output at a time.DC Supply Voltage (V DD )−0.5V DC to +18V DC Input Voltage (V IN )−0.5V DC to V DD +0.5V DCStorage Temp. Range (T S )−65°C to +150°CPower Dissipation (P D )Dual-In-Line 700 mW Small Outline 500 mWLead Temperature (T L )(Soldering, 10 seconds)260°C DC Supply Voltage (V DD )5V DC to 15 V DC Input Voltage (V IN )0 V DC to V DD V DC Operating Temperature Range (T A )−40°C to +85°CSymbol ParameterConditions−40°C +25°C +85°C Units MinTyp MinTyp Max MinMax I DDQuiescent Device CurrentV DD = 5V 1.00.004 1.07.5µAV DD = 10V 2.00.005 2.015V DD = 15V4.00.006 4.030V OLLOW Level Output Voltage V DD = 5V0.0500.050.05VV DD = 10V 0.0500.050.05V DD = 15V0.0500.050.05V OHHIGH Level Output Voltage V DD = 5V4.95 4.955 4.95VV DD = 10V 9.959.95109.95V DD = 15V14.9514.951514.95V ILLOW Level Input VoltageV DD =5V, V O =4.5V 1.52 1.5 1.5VV DD =10V, V O =9.0V |I O |<1µA3.04 3.0 3.0V DD =15V, V O =13.5V4.06 4.0 4.0V IHHIGH Level Input VoltageV DD =5V, V O =0.5V 3.53.53 3.5VV DD =10V, V O =1.0V |I O |<1µA7.07.067.0V DD =15V, V O =1.5V11.011.0911.0I OLLOW Level Output Current V DD =5V, V O = 0.4V 0.520.440.880.36mA(Note 4)V DD = 10V, V O = 0.5V 1.3 1.1 2.20.90V DD = 15V, V O = 1.5V3.6 3.08 2.4I OHHIGH Level Output Current V DD = 5V, V O = 4.6V −0.52−0.44−0.88−0.36mA(Note 4)V DD = 10V, V O = 9.5V −1.3−1.1−2.2−0.90V DD = 15V, V O = 13.5V −3.6−3.0−8−2.4I INInput CurrentV DD = 15V, V IN = 0V −0.3−10−5−0.3−1.0µAV DD = 15V, V IN = 15V0.310−50.3 1.0CD4023BCAC Electrical Characteristics (Note 5)T A = 25°C, C L = 50 pF, R L = 200k, unless otherwise specified Note 5: AC Parameters are guaranteed by DC correlated testing.Note 6: C PD determines the no load AC power consumption of any CMOS device. For complete explanation, see Family Characteristics Application Note AN-90.Symbol ParameterConditionsMinTyp Max Units t PHLPropagation Delay, HIGH-to-LOW LevelV DD = 5V 130250nsV DD = 10V 60100V DD = 15V4070t PLHPropagation Delay, LOW-to-HIGH LevelV DD = 5V 110250ns V DD = 10V 50100V DD = 15V3570t THL ,Transition TimeV DD = 5V 90200ns t TLH V DD = 10V 50100V DD = 15V 4080C IN Average Input CapacitanceAny Input 57.5pF C PDPower Dissipation Capacity (Note 6)Any Gate17pF 4C D 4023B CPhysical Dimensions inches (millimeters) unless otherwise noted14-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-013, 0.300 WidePackage Number M14B14-Lead Small Outline Package (SOP), EIAJ TYPE II, 5.3mm WidePackage Number M14DFairchild does not assume any responsibility for use of any circuitry described, no circuit patent licenses are implied and Fairchild reserves the right at any time without notice to change said circuitry and specifications.CD4023BC Buffered Triple 3-Input NAND GateLIFE SUPPORT POLICYFAIRCHILD’S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF FAIRCHILD SEMICONDUCTOR CORPORATION. As used herein:1.Life support devices or systems are devices or systemswhich, (a) are intended for surgical implant into thebody, or (b) support or sustain life, and (c) whose failureto perform when properly used in accordance withinstructions for use provided in the labeling, can be rea-sonably expected to result in a significant injury to the user.2. A critical component in any component of a life support device or system whose failure to perform can be rea-sonably expected to cause the failure of the life support device or system, or to affect its safety or Physical Dimensions inches (millimeters) unless otherwise noted (Continued)14-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-001, 0.300 WidePackage Number N14A。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

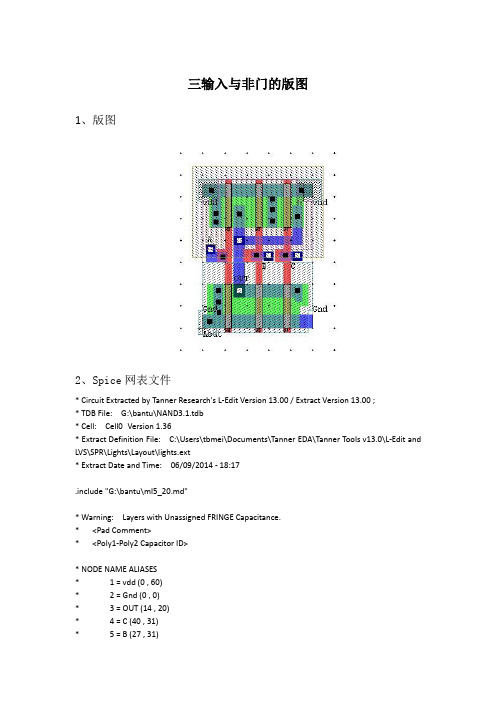

三输入与非门的版图

1、版图

2、Spice网表文件

* Circuit Extracted by Tanner Research's L-Edit Version 13.00 / Extract Version 13.00 ;

* TDB File: G:\bantu\NAND3.1.tdb

* Cell: Cell0 Version 1.36

* Extract Definition File: C:\Users\tbmei\Documents\Tanner EDA\Tanner Tools v13.0\L-Edit and LVS\SPR\Lights\Layout\lights.ext

* Extract Date and Time: 06/09/2014 - 18:17

.include "G:\bantu\ml5_20.md"

* Warning: Layers with Unassigned FRINGE Capacitance.

* <Pad Comment>

* <Poly1-Poly2 Capacitor ID>

* NODE NAME ALIASES

* 1 = vdd (0 , 60)

* 2 = Gnd (0 , 0)

* 3 = OUT (14 , 20)

* 4 = C (40 , 31)

* 5 = B (27 , 31)

* 6 = A (2 , 38)

M1 OUT C1 vdd vdd PMOS L=3u W=20u AD=96p PD=52u AS=100p PS=30u $ (37 46 40 66)

M2 vdd B OUT vdd PMOS L=3u W=20u AD=100p PD=30u AS=110p PS=31u $ (24 46 27 66)

M3 OUT A vdd vdd PMOS L=3u W=20u AD=110p PD=31u AS=108p PS=54u $ (10 46 13 66)

M4 OUT C1 9 8 NMOS L=3u W=20u AD=120p PD=56u AS=100p PS=30u $ (37 0 40 20)

M5 9 B 7 8 NMOS L=3u W=20u AD=100p PD=30u AS=110p PS=31u $ (24 0 27 20)

M6 7 A Gnd 8 NMOS L=3u W=20u AD=110p PD=31u AS=172p PS=60u $ (10 0 13 20)

.include "G:\bantu\ml5_20.md"

.tran 600n 600n start=0

VDDD vdd Gnd 3

VAin A Gnd pwl (0ns 0V 100ns 0V 105ns 3V 200ns 3V 205ns 0V 300ns 0V 305ns 3V 400ns 3V 405ns 0V 500ns 0V 505ns 3V 600ns 3V)

VBin B Gnd pwl (0ns 0V 100ns 0V 105ns 0V 200ns 0V 205ns 3V 300ns 3V 305ns 3V 400ns 3V 405ns 0V 500ns 0V 505ns 3V 600ns 3V)

VCin C1 Gnd pwl (0ns 0V 100ns 0V 105ns 0V 200ns 0V 205ns 0V 300ns 0V 305ns 0V 400ns 0V 405ns 3V 500ns 3V 505ns 3V 600ns 3V)

.print tran v(A,Gnd)

.print tran v(B,Gnd)

.print tran v(C1,Gnd)

.print tran v(OUT,Gnd)

* Pins of element D2 are shorted:

* D2 vdd vdd D_lateral $ (3 58 7 66)

* Total Nodes: 9

* Total Elements: 8

* Total Number of Shorted Elements not written to the SPICE file: 0

* Output Generation Elapsed Time: 0.000 sec

* Total Extract Elapsed Time: 0.687 sec

.END

3、仿真波形图

4、波形分析

输入信号A、B、C1中至少一个为低电平时,输出OUT为高电平;只有输入信号A、B、C1同时为高电平时,输出OUT为低电平。