专用集成电路实验2---导线

模拟cmos集成电路设计实验

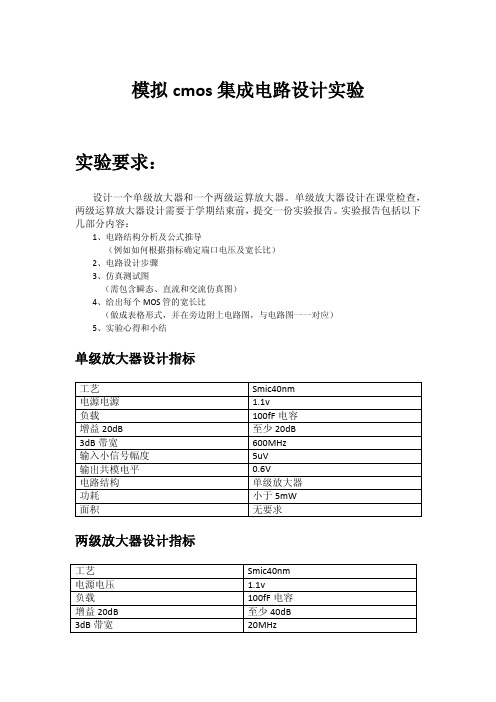

模拟cmos集成电路设计实验实验要求:设计一个单级放大器和一个两级运算放大器。

单级放大器设计在课堂检查,两级运算放大器设计需要于学期结束前,提交一份实验报告。

实验报告包括以下几部分内容:1、电路结构分析及公式推导(例如如何根据指标确定端口电压及宽长比)2、电路设计步骤3、仿真测试图(需包含瞬态、直流和交流仿真图)4、给出每个MOS管的宽长比(做成表格形式,并在旁边附上电路图,与电路图一一对应)5、实验心得和小结单级放大器设计指标两级放大器设计指标实验操作步骤:a.安装Xmanagerb.打开Xmanager中的Xstartc.在Xstart中输入服务器地址、账号和密码Host:202.38.81.119Protocol: SSHUsername/password: 学号(大写)/ 学号@567& (大写)Command : Linux type 2然后点击run运行。

会弹出xterm窗口。

修改密码输入passwd,先输入当前密码,然后再输入两遍新密码。

注意密码不会显示出来。

d.设置服务器节点用浏览器登陆http://202.38.81.119/ganglia/,查看机器负载情况,尽量选择负载轻的机器登陆,(注:mgt和rack01不要选取)选择节点,在xterm中输入 ssh –X c01n?? (X为大写,??为节点名)如选择13号节点,则输入ssh –X c01n13e.文件夹管理通常在主目录中,不同工艺库建立相应的文件夹,便于管理。

本实验采用SMIC40nm工艺,所以在主目录新建SMIC40文件夹。

在xterm中,输入mkdir SMIC40然后进入新建的SMIC40文件夹,在xterm中,输入cd SMIC40.f.关联SMIC40nm 工艺库在xterm窗口中,输入gedit&,(gedit为文档编辑命令)将以下内容拷贝到新文档中。

SOFTINCLUDE /soft1/cadence/IC5141/share/cdssetup/dfII/cds.lib SOFTINCLUDE /soft1/cadence/IC5141/share/cdssetup/hdl/cds.lib SOFTINCLUDE /soft1/cadence/IC5141/share/cdssetup/pic/cds.lib SOFTINCLUDE /soft1/cadence/IC5141/share/cdssetup/sg/cds.libDEFINE smic40llrf /soft2/eda/tech/smic040/pdk/SPDK40LLRF_1125_2TM_CDS_V1.4/smic40llrf_1 125_2tm_cds_1P8M_2012_10_30_v1.4/smic40llrf保存为cds.lib 。

实验2 组合逻辑电路的设计

4. 实验内容及要求 (1) 用与非门设计实现异或逻辑功能。 a) 按照组合逻辑电路的设计方法, 列出两输入异或逻辑函数的真值表, 写出最简 与或式、与非-与非式,画出与非门实现的逻辑电路图。 b) 使用集成电路芯片 74LS10 和 74LS20 中的与非门, 按照所设计的逻辑电路图连 接电路。 c) 选择使用数字电路实验装置中的逻辑电平输入开关和逻辑电平输出 LED 指示 灯,设计实验测试方案。 d) 记录并分析实验数据参考表 2-2, 说明所设计的电路是否实现预计的异或逻辑 功能。

以二值逻辑的 0、1 两种状态分别代表输入变量和输出变量的两种不同状态。这里 0 和 1 的具体含意完全是由设计者人为选定的。

3) 根据给定的因果关系列出逻辑真值表。 举例: “大月指示器”的逻辑功能如下:输入一年中的具体月份,电路能自动判别出“大月” 还是“小月” (大月有 31 天) 。 通过分析,逻辑抽象结果为:月份输入 ABCD 可以由 4 位二进制代码表示,例如 ABCD=0001 表示输入月份为 1 月, ABCD=0010 表示 2 月, ABCD=0011 表示 3 月,...... , ABCD=1100 表示 12 月;输出 Y 的逻辑值 1 或 0 分别表示信息“大月”或“小月” ,Y=1 表 示大月,Y=0 表示小月。列出真值表如表 2-1 所示。

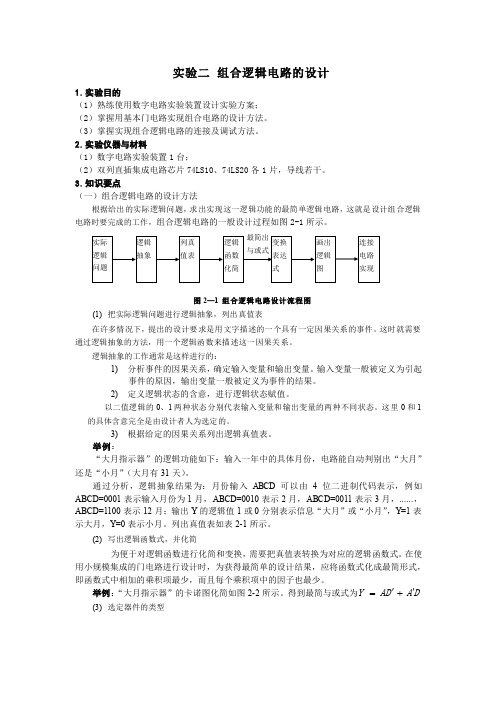

得到最简与或式为选定器件的类型实际逻辑问题逻辑抽象逻辑函数化简变换表达画出逻辑连接电路实现为了实现最终的逻辑函数既可以用小规模集成门电路组成相应的逻辑电路也可以用中规模集成的常用组合逻辑器件或可编程逻辑器件等构成相应的逻辑电路

实验二 组合逻辑电路的设计

1. 实验目的 (1)熟练使用数字电路实验装置设计实验方案; (2)掌握用基本门电路实现组合电路的设计方法。 (3)掌握实现组合逻辑电路的连接及调试方法。 2. 实验仪器与材料 (1)数字电路实验装置 1 台; (2)双列直插集成电路芯片 74LS10、74LS20 各 1 片,导线若干。 3 . 知识要点 (一)组合逻辑电路的设计方法

实验2 电路原理图的编辑2实验报告

实验2 电路原理图的编辑2一、实验目的:1、进一步熟悉装载元器件库,放置、编辑和调整元器件、绘制电原理图的方法。

2、掌握在电原理图中使用网络标号、总线、总线分支的方法。

3、掌握对电原理图进行中电气规则检查(ERC)的方法。

4、掌握生成原理图的网络表文件、元件清单报表的方法。

5、练习绘制原理图的各种技巧。

二、实验设备:装有protel 99 se 软件的PC机一台。

三、实验要求:1、实验前,仔细阅读教材相关内容,设计能够完成实验内容的实验步骤,写好实验预习报告。

2、实验后,完成实验报告,其中的实验步骤应是经过实验证明为正确的步骤。

四、实验内容:1、绘制如图2-96所示的电路原理图。

2、对绘制的原理图进行电气规则检查(ERC),直到通过为止。

3、生成绘制的原理图的网络表文件。

4、生成绘制的原理图的元件清单报表。

五、实验步骤:(1) 单击“File”菜单下的“New Design…”命令,创建一个新设计文件库文件(文件名为MCU.ddb,存放在D:\p99文件夹内)。

(2) 在“设计文件管理器”窗口内,双击“Document”文件夹,然后执行“File”菜单下的“New…”命令,在如图1-6所示窗口内,选择Schematic Document(原理图文档)文件图标,生成一个新的原理图文件。

(3) 图纸类型、尺寸、底色、标题栏等的选择(4) 单击“Tools”菜单下的“Preferences…”(优化…)命令,设置Protel99原理图编辑器工作参数(5) 单击主工具栏内的放大、缩小工具,适当放大编辑区。

(6) 放置核心元件8031。

(7) 执行类似步骤(6)的操作,继续放置U102(74LS373)、U103(27256)、U104(6264)、U201(74LS05)、UC202(DS75492M)集成电路芯片。

(8) 使用“画线”(原理图编辑)工具内的“导线”、“总线”、“总线分支”、“网络标号”等工具,将有关芯片连接在一起。

#电子电路试验报告 2

目录第1章设计任务 01.1 设计要求 01.2 使用器材 (1)第2章设计原理 (1)2.1 FM信号输入 (2)2.2 本振协调电路 (2)2.3 中频放大、限幅与鉴频 (3)2.4 功率放大 (3)第3章产品安装 (3)3.1 安装流程图 (3)3.2 安装步骤及要求 (4)3.2.1 安装前检查 (4)3.2.2 SMT工艺流程 (4)3.2.3 安装THT分立元器件 (4)3.3 元器件焊接步骤 (5)3.4 注意事项 (5)第4章安装调试 (5)4.1 调试 (5)4.2 总装 (6)第5章心得体会 (6)第1章设计任务1.1设计要求1.学会看图、识图,了解常用电子器件的类别、型号、规格、性能及其使用范围,能查阅有关的电子器件图书。

2.学习并掌握收音机的工作原理。

3.熟悉手工焊锡的常用工具的使用及其维护与修理,能够自己安装、焊接,基本掌握手工电烙铁的焊接技术。

能够正确识别和选用常用的电子器件,并且能够熟练使用万用表。

4.了解电子产品的焊接、调试与维修方法。

初步学习调试电子产品的方法,提高动手能力。

5.培养严谨的科学态度,耐心细致的工作作风和主动研究的探索精神。

提高学生1.2使用器材1.电烙铁、焊锡丝、松香2.螺丝刀、镊子、钳子等必备工具3.万用表4.收音机实验套件第2章设计原理电路的核心是单片收音机集成电路SC1088。

FM收音机集成电路 SC1088引脚功能如表2-1所示。

表2-1 FM收音机集成电路 SC1088引脚功能引脚功能引脚功能引脚功能引脚功能1 静噪输出5本振调谐回路9 IF输入13限幅器失调电压电容2 音频输出6 IF反馈10IF限幅放大器的低通电容器14 接地3 AF环路滤波71dB放大器的低通电容器11射频信号输入15全通滤波电容搜索调谐输入4 Vcc 8 IF输出12 射频信号输入16电调揩AFC输出2.1FM信号输入如图2-1所示,调频信号由耳机线馈入经C14、C15、L1和L3的输入电路进入IC的11、12脚混频电路。

集成电路的外观形貌观察实验报告

集成电路的外观形貌观察实验报告实验目的:观察集成电路的外观形貌,了解其结构和特点。

实验原理:集成电路是由多个电子器件(如晶体管、电容器、电阻器等)通过一定的工艺步骤,集成在一块半导体片上,形成一个完整的电路。

根据用途和结构的不同,集成电路可以分为不同的类型,如数字集成电路、模拟集成电路、混合集成电路等。

不同类型的集成电路有不同的外观形貌。

实验步骤:1. 在实验台上准备好显微镜、集成电路样品和相关仪器。

2. 将集成电路样品放置在显微镜下,并调节显微镜的放大倍数,使集成电路的每个区域都能够清晰观察到。

3. 仔细观察集成电路的外观形貌,包括整体结构、连接线路、器件等。

4. 对集成电路的封装外观进行观察和描述,如封装形式、引脚排列等。

5. 对集成电路的芯片结构进行观察和描述,如晶体管的布局、电阻器和电容器的位置等。

6. 根据观察到的外观特征,分析集成电路的类型和用途。

实验结果与分析:集成电路的外观形貌观察结果将根据具体实验所用的集成电路类型进行描述。

以下是针对几种常见集成电路类型的观察结果和分析:1. 数字集成电路(如逻辑门、计数器等):数字集成电路的外观形貌通常是由多个晶体管和电阻器组成的线路图案。

通过显微镜观察,可以看到晶体管的形状和排列方式,以及层层叠加的金属线路连接。

2. 模拟集成电路(如放大器、滤波器等):模拟集成电路的外观形貌通常是由多个晶体管、电容器和电阻器等器件组成的。

观察过程中,可以看到不同器件的布局和连接方式,如晶体管的位置和排列顺序,电容器和电阻器的封装形式等。

3. 混合集成电路(如模拟数字转换器、放大器芯片等):混合集成电路的外观形貌通常是数字电路和模拟电路结合在一起的。

通过观察,可以看到数字电路和模拟电路之间的连接和布局关系。

根据实验观察的外观特征,可以初步判断集成电路的类型和用途。

同时,可以了解集成电路的封装形式和框架结构,对后续的电路设计和应用有一定的参考价值。

实验结论:通过观察集成电路的外观形貌,可以了解其结构和特点,初步判断其类型和用途。

实验二TTL集成逻辑门的逻辑功能与参数测试.doc

实验二 TTL集成逻辑门的逻辑功能与参数测试一、实验目的1.掌握TTL与非门逻辑功能的测试方法;2.熟悉TTL与非门主要参数的测量方法;3.熟悉TH-SZ型数字电路实验箱的结构和使用方法;二、预习要求1.什么叫TTL集成电路?它使用的电源电压是多少?2.说明TTL与非门不使用的输入端应如何处置?3.复习TTL与非门的逻辑功能,主要参数的概念和测量方法;4.TTL与非门的输出特性曲线?从中读取相关的参数值;三、实验原理1.与非门的逻辑功能当输入端中有一个或一个以上是低电平时,输出端为高电平;只有当输入端全部为高电平时,输出端才是低电平。

即有“0”得“1”,全“1得“0”.其逻辑表达式为Y=AB.2.本实验采用4输入双与非门74LS20,即在一块集成块内含有两个互相独立的与非门,每个与非门有4个输入端。

其逻辑符号及引脚排列如图2-1 (a) (b)所示:Y=ABCD 1 2 3 4 5 6 7(a)国家标准逻辑符号(b) 74LS20引脚排列图2-1 74LS20国家标准逻辑符号及引脚排列四、实验器件1.TH-SZ型数字电路实验箱2.数字万用表UT563.TTL与非门74LS204.若干导线五、实验内容1.验证TTL与非门74LS20的逻辑功能在合适的位置选取一个14脚的集成块插座,按图2—2接好线。

每个门的4个输入端(假设为A, B, C, D)接逻辑开关输出插口,以提供“0”与“1”电平信号(开关向上,输出“1”;向下为“0”)。

门的输出端(假设为Y)接LED发光二极管,LED亮为输出“1”,灭为输出“0”。

按表2-1的真值表逐个测试集成块中2个与非门的逻辑功能。

表2-1 74LS20真值表图2-2 74LS20逻辑功能测试电路2.74LS20主要参数的测试(将测试值填入表2-2)低电平输出电源电流I CCL、高电平输出电源电流I CCH、74LS20总的静态功耗、低电平输入电流I iL,高电平输入电流I iH(I iH很小,可不测)扇出系数No(先测出允许灌入的最大负载电流I OL)(a)(b)(c)(d)图2-3 74LS20主要参数测试电路(1)低电平输出电源电流I CCL指所有输入端悬空,输出端空载,74LS20输出低电平时,电源提供给器件的电流。

高等数字集成电路设计-I2C总线控制器后端设计

⾼等数字集成电路设计-I2C总线控制器后端设计《⾼等数字集成电路设计》I2C总线控制器电路设计姓名学号:指导⽼师:时间:⽬录⼀、实验⽬的与设计内容 (2)1.设计⽬的 (2)2.设计描述 (2)3.设计内容 (2)⼆、实验步骤及分析 (3)1.前端设计 (3)设计输⼊ (3)2.DC综合 (3)3.Pre-STA (7)4.⾃动布局布线(P&R) (8)1. 设计输⼊ (8)2. 平⾯布局(Floorplan) (10)3. Add Rings和Add Stripes (10)4. 连接全局⽹络(connect global nets) (11)5.布线和放置标准单元库 (12)6.预插时钟树(Pre-CTS) (12)7.创建时钟树和⽣成相应的⽂件 (13)8.Post-CTS (14)9.最终布局布线(nanoRoute) (15)10.Add filler (16)11.导出相关⽂件,并导⼊cadence软件 (16)三、实验总结 (18)附录:DC综合脚本: (19)I2C总线控制器电路设计⼀、实验⽬的与设计内容1.设计⽬的通过实验掌握数字电路前端和后端设计的流程,能够解决电路中的设计时出现的时序问题和版图布局问题,进⾏优化,达到设计时序和版图的要求。

2.设计描述系统初始化时,由指令控制CPU送出相关的数据,经APB接⼝,送到I2C 控制器核的寄存器内。

通过初始化这些寄存器,可以实现I2c总线的master模式控制3.设计内容1、准备verilog代码。

2、进⾏逻辑综合(DC)。

使⽤Design Compiler综合⼯具,根据给定的设计指标进⾏逻辑综合并进⾏优化,直到满⾜要求。

3、进⾏静态时序分析(STA)。

使⽤PrimeTime进⾏静态时序分析,分别对建⽴时间和保持时间进⾏分析优化,直到满⾜要求。

4、时序仿真。

使⽤Modelsim进⾏时序仿真,时序约束⽂件为PT输出的.sdf⽂件,验证时序仿真是否正确。

2024年电路实验报告

幅度范围:1~9V

四、总结

第一次进行电路设计,遇到了很多麻烦。Multisim、Protel等软件不熟悉,第一次焊电路焊工也不行。通过实验,基本学会了这些软件的操作,制作过程中,自己的焊工有了很大进步。虽然做了好几次才把电路调出来,但还是很满意。

电路实验报告4

一、实验目的

1. 更好的理解、巩固和掌握汽车全车线路组成及工作原理等有关内容。

3、VCC=6V,VM=3V时测量静态工作点,然后输入频率为5KHz的正弦波,调整输入幅值使输出波形最大且不失真。(以下输入输出值均为有效值)

四、试验小结

功率放大电路特点:在电源电压确定的状况下,以输出尽可能大的不失真的信号功率和具有尽可能高的转换效率为组成原则,功放管常工作在尽限应用状态。

电路实验报告2

2.实验按预定的步骤进行,做好后经教师的检查允后方可启动或通电实验。

3.实验做完后,应自行检查数据等结果,并与理论相对照,分析实验结果,做好实验报告。

4.实验做完后,工具不要乱放,擦干净后,整理好装入工具箱内。

5.实验时发生事故,切勿惊慌失措,首先切断电源,保持现场,由教师检查处理。

6.要爱护财产,正确使用实验设备,如有损坏要添表上报,并听候处理,特别是操作不当或使用不当者,要部分或全部赔偿。

对于某些电器设备,为了保证其工作的可靠性,提高灵敏度,仍然采用双线制连接方式。例如,发电机与调节器之间的搭铁线、双线电喇叭、电子控制系统的电控单元、传感器等。

(2) 汽车电路采用直流电源,汽车用电设备采用与电源电压一致的直流电器设备。

(3) 汽车用电都是低压电源一般为12V、24V,目前有的人提出用42V电源。个别电器工作信号是高压或不同的电压,如点火系统电路中的高压电路,电控系统各传感器的工作电压、输出信号等。

电子电路课程设计实验报告

目录第1章技术指标 21.1系统功能要求 21.2 系统结构要求21.3电气指标 21.4设计条件 21.5 元器件介绍 31.5.1 数码管 31.5.2 发光二极管 31.5.3 排阻 41.5.4 4511译码器 41.5.5 八位拨号开关 41.5.6 74174芯片 51.5.7 74283芯片 5 第2章整体方案设计 62.1 算法设计 62.2 整体方案72.2.1 预期效果72.2.2 设计内容72.2.3 整体布局92.3整体方案图及原理10 第3章单元电路设计113.1 十进制显示电路设计113.2 8421BCD码控制电路设计113.3 二进制显示电路设计123.4 整体电路图143.5 实验实物图143.6 整机元件清单15 第4章测试与调整164.1十进制显示电路调测164.2 8421BCD码控制电路调测164.3二进制显示电路调测174.4 整体指标测试174.5 测试数据18 第5章设计小结195.1 设计任务完成情况195.2 问题及解决195.3 心得体会20 附录1:参考文献22 附录2:预习报告附录3:设计图第1章 技术指标1.1 系统功能要求人们在向计算机输送数据时,首先把十进制数变成二—十进制码,即 BCD 码, 运算器将接收到的二一十进制码转换成二进制数后才能进行运算。

这种把十进制数转换成二进制数的过程称为“十翻二”运算。

1.2 系统结构要求系统结构方框图如下:系统复位 十进制数输入(0-9共10个数)1.3 电气指标(1)具有十翻二功能。

(2)实现三位十进制数到二进制数的转换。

(3)能自动显示十进制数及对应的二进制数。

(4)具有手动清零功能。

1.4 设计条件(1)电源条件:直流稳压电源提供+5V 电压。

(2)实验仪器:十翻二运算电路RESET二进制数显示十进制数显示名称备注稳压电源实验室配备万用表一个面包板1块剪刀一把镊子一把导线若干1.5 元器件介绍1.5.1 数码管规定用1 表示数码管a—g线段中的点亮状态,用0表示a—g线段中的熄灭状态。

数字集成电路设计 第四章导线.ppt

导线. 17

合肥工业大学应用物理系

接触电阻(contact resistance)

• 布线层之间的转接将给导线带来额外的电阻 – 尽可能地使信号线保持在同一层上并避免过多的接触或通孔 – 使接触孔较大可以降低接触电阻(电流集聚在实际中将限制接触孔 的最大尺寸)

• 典型接触电阻,RC, (最小尺寸) – 金属或多晶至n+、p+以及金属至多晶为 5 ~ 20 – 通孔(金属至金属接触)为1 ~ 5

例4.1 金属导线电容

考虑一条布置在第一层铝上的10cm长,1m宽的铝线,计算总的电容值。

平面(平行板)电容: ( 0.1×106m2 )×30aF/m2 = 3pF

边缘电容:

2×( 0.1×106m )×40aF/m = 8pF

总电容:

11pF

现假设第二条导线布置在第一条旁边,它们之间只相隔最小允许的距离, 计算其耦合电容。

Capacitance-only

注意:这些附加的电路元件并不处在实际的单个点上,而是分布在导 线的整个长度上

导线. 6

合肥工业大学应用物理系

寄生简化

• 电感的影响可以忽略 – 如果导线的电阻很大(例如截面很小的长铝导线的情形) – 外加信号的上升和下降时间很慢

• 采用只含电容的模型 – 当导线很短,导线的截面很大时 – 当所采用的互连材料电阻率很低时

D2 C1R1 C2 R1 R2

r1

1 r2

2

Vin

c1

c2

ri-1 i-1 ri

i

ci-1

ci

rN

N VN

cN

Di C1R1 C2R1 R2 ... Ci R1 R2 ... Ri

电子技术实验报告—实验2电路元器件的认识和测量

电子技术实验报告实验名称:电路元器件的认识和测量系别:班号:实验者:学号:实验日期:实验报告完成日期:一、实验原理简要介绍实验室常用的电阻、电容、电感、晶体管等电子元器件。

(一)电阻器1、电阻器的分类:通用电阻器、精密电阻器、高阻电阻器、高压电阻器、高频电阻器。

2、电阻器主要特性指标:标称阻值(电阻器表面所标注的阻值)、容许误差、额定功率。

3、电阻器的规格标注通常采用文字直标法和色标法,对于额定功率小于0.5W 的电阻器均采用色标法,只标注标称阻值和精度等级,材料类型和功率常从其外观尺寸判断。

色环电阻器一般为四环、五环,根据颜色查表可以算出对应的阻值和精度等级。

4、性能测量:一般采用万用表测量。

5、使用常识:使用前检查其阻值是否与标称阻值相等,使用时注意每个电阻不超过额定功率和最高工作电压。

(二)电位器1、电位器的类型:非接触型电位器、接触型电位器。

2、性能指标:选用万用表测量电位器两固定端的电阻值是否与标称阻值相符。

测量滑动端与任一固定端的阻值变化:慢慢移动滑动端,数字变化平稳,则电位器良好。

3、使用常识:(1)电位器的选用:根据电路的要求选择合适的阻值和额定功率,还要考虑安装调节方便和成本,电性能应根据不同的要求选择。

(2)安装、使用电位器:安装应牢靠,避免松动和电路中的其他元器件短路;焊接时间不能太长;三个引出端连线时应注意电位器旋转方向是否符合要求。

(三)电容器1、电容器的型号命名方法:CD铝电解电容、CL涤纶电容、CC瓷片电容,其余查表可知。

2、电容器的分类:(1)按介质分类(2)按结构分类(3)按用途分类3、电容器的主要特性指标:标称容量及容许误差、额定工作电压、绝缘电阻、频率特性。

4、电容器的规格标注:(1)直标法:一般用于两位的参数。

(2)数码标法:前两位为容量有效数字,后一位为乘10的n次方,单位为pF。

5、性能测量:容量测量和漏电测量。

6、使用常识(1)选用适当的型号;(2)合理选用标称容量及容许误差;(3)额定工作电压一般高于实际电压的1~2倍;(4)选用绝缘高的电容器。

电工实训指导书

RTSX—2B型电工实训考核实验装置电气控制线路安装要求一、安装要求1.建议连接导线要采用规定的颜色(1)接地保护导线(PE)采用黄绿双色线;(2)动力电路的中线(N)采用浅兰色;(3)交流和直流动力电路应采用黑色;(4)交流控制电路采用红色;(5)直流控制电路采用兰色。

2.导线的绝缘和耐压要符合电路要求,每一根连接导线在接近端子处的线头上必须套上标有线号的套管;进行布线要求走线横平竖直、整齐、合理,接点不得松动,不得承受拉力,接地线和其他导线接头,同样应套上标有线号的套管。

3.指示灯及按钮的颜色(1)指示灯颜色的含义红—运行、危险或报警绿—安全(2)按钮颜色的用法红—“停止”或“断开”绿—“启动”二、安装后(在接通电源前的)质量检验1.再次检查各个接线是否连接牢固。

线头上的线号是否同电路原理图相符合,绝缘导线是否符合规定,保护导线是否已可靠连接。

2.短接主电路、控制电路,用500V兆欧表测量与保护接地电路导线之间的绝缘电阻应不得小于2兆欧。

实验一光控开关和报警电路一.目的1.了解光控(热控)开关电路的一般组成形式。

2.熟悉光敏电阻的性能和作用。

3.熟悉三极管的开关特性。

4.了解音乐集成电路的使用方法。

二.内容与说明在自动控制系统中,经常使用光传感器(如光敏电阻、硅光电阻、光电耦合器件)或热传感器(热敏电阻、PN结、热电偶)等将光强度或温度的变化转换成电信号,并与某一限度比较,当高于或低于这个限度时,产生一个开关信号,去控制一个系统的工作状态。

以光敏电阻和热敏电阻为例,常见的电路形式有:光(热)敏电阻是电阻性传感器,在所受到的光(热)强度发生变化时,其电阻值相应变化。

当光(热)敏电阻与电阻器串联或组成电桥时,就能把电阻的变化转换为电压信号。

热敏电阻有正、负温度系数两种类型,基本知识请参见有关资料。

图1-1为基本光-电、热-电转换电路,把电路的输出引至三极管构成的开关电路,就能实现光(暗)动、热(冷)动开关控制或报警,如图1-2(a)所示。

实验报告

实习报告二——数字钟制作一、实习目的:1. 熟悉电子焊接技术。

2. 了解ZX2042型数码显示电子钟的原理。

3. 通过数字钟的制作进一步的了解各种在制作中用到的中小规模集成电路的作用及实用方法。

4. 学会制作数字钟。

二、实习时间:2010-9-8——2010-9-9三、实习内容:焊接一个ZX2042型数码显示电子钟。

自行装配调试,并能发现问题和解决问题。

写出制作的全过程,编写实习报告。

四、实习步骤:1.数字钟工作原理电路原理图如下图。

LM8560(IC1)是50/60HZ的时基24小时专用数字钟集成电路,有28只管脚,1-14脚是显示笔划输出,15脚为电源端,20脚为负电源端,27脚是内部振荡器RC输入端,16脚为报警输出。

T1为降压变压器,经桥式整流(VD6-VD9)及滤波(C3、C4)后得到直流电,供主电路和显示屏工作。

当交流电源停电时,备用电池通过VD5向电路供电。

IC2(CD4060)、JT、R2、C2构成50HZ的时基电路,CD4060内部包含14位二分频器和一个振荡器,电路简洁,30720HZ的信号经分频后,得到50HZ的信号送到LM8560的25脚,并做秒信号经VT2、VT3驱动显示屏内的冒号闪动。

当调好定时时间后,并按下开关K1,显示屏右下方有绿点指示,到定时时间有驱动信号经R3使VT1工作,即可定时报警输出。

2.焊接步骤A、先焊接在电路板较低的元件,如:电阻、二极管、集成电路、跳线。

B、其次焊接在在电路板上排列稍微高一点的元件,如:LED、插针、电源座。

C、最后将电容、三极管等较高的元件焊上。

3.安装工艺要求在动手焊接前先用表将各元件测量一下,做到心中有数,安装时先装低矮和耐热的元件(如电阻),然后再装大一点的元件,最后装怕热的元件(如三极管、集成电路等)。

电阻的安装:将电阻的阻值选择好后,根据两孔德距离可采用立式紧贴电路板安装。

电解电容器、二极管、三极管安装时注意极性,电解电容器C4紧贴电路板卧式安装,C3紧贴电路板立式安装;二极管紧贴电路板立式安装;三极管安装时注意型号。

全桥DC-DC变换电路实验指导书

全桥DC/DC变换电路实验一.实验目的1.掌握可逆直流脉宽调速系统主电路的组成、原理及各主要单元部件的工作原理。

2.熟悉直流PWM专用集成电路SG3525的组成、功能与工作原理。

3.熟悉H型PWM变换器的各种控制方式的原理与特点。

二.实验内容1.PWM控制器SG3525性能测试。

2.H型PWM变换器DC/DC主电路性能测试。

三.实验系统的组成和工作原理全桥DC/DC变换脉宽调速系统的原理框图如图6—10所示。

图中可逆PWM变换器主电路系采用MOSFET所构成的H型结构形式,UPW为脉宽调制器,DLD为逻辑延时环节,GD为MOS管的栅极驱动电路,FA为瞬时动作的过流保护。

全桥DC/DC变换脉宽调制器控制器UPW采用美国硅通用公司(Silicon General)的第二代产品SG3525,这是一种性能优良,功能全、通用性强的单片集成PWM控制器。

由于它简单、可靠及使用方便灵活,大大简化了脉宽调制器的设计及调试,故获得广泛使用。

四.实验设备及仪器1.教学实验台主控制屏2.NMCL—31组件3.NMCL—22组件4.可调电阻负载5.双踪示波器(自备)五.实验方法1.UPW模块的SG3525性能测试(1)用示波器观察UPW模块的“1”端的电压波形,记录波形的周期。

(2)用示波器观察“2”端的电压波形,调节RP2电位器,使方波的占空比为50%。

(3)用导线将给定模块“G”(15V直流可调电源位于NMCL-31)的“1”和“UPW”的“3”相连,分别调节正负给定,记录“2”端输出波形的最大占空比和最小占空比。

2.控制电路的测试(1)逻辑延时时间的测试在上述实验的基础上,分别将正、负给定均调到零,用示波器观察“DLD”的“1”和“2”端的输出波形,并记录延时时间t d=(2)同一桥臂上下管子驱动信号列区时间测试分别将“隔离驱动”的G和主回路的G相连,用双踪示波器分别测量V VT1.GS和V VT2.GS以及V VT3.GS和V VT4.GS的列区时间:t dVT1.VT2= t dVT3.VT4=3.DC/DC波形观察按图6—11a接线。

数电实验讲义 (2)

数字电子技术实验讲义万用表及实验箱使用一、万用表使用重点讲解:1、电压和电阻测量2、“HOLD”数据保持按钮3、自动关闭功能4、用完后关闭电源二、示波器的使用由学生阅读示波器使用手册完成1、校准和选择探头(P)2、观察输入信号并调出稳定波形3、精确测量输入信号的幅度、周期和频率三、实验箱的构成1、电源开关2、电源输出:要求测量数据3、数据开关:可输出高低电平。

要求测量数据。

4、逻辑开关:可输出单次脉冲。

要求测量数据。

5、元件区:介绍集成块引脚识别、判断集成块是否插好。

6、电平指示:7、数码显示8、拨码开关:9、导线:要求判断通断四、使用注意事项1、导线插拨方法2、接线和更改线路一定要关闭电源3、注意观察电源指示灯,如接通电源时指示灯变暗,说明接线有短路,应关闭电源实验课的目的是培养学生的电子电路实验研究能力,培养学生理论联系实际的能力。

使学生能根据实验结果,利用所学理论,通过分析找出内在联系。

从而对电路参数进行调整,使之符合性能要求。

在实验中培养1.正确使用常用电子仪器。

2.3.4.5.6.7.能独立写出严谨的、有理论分析的、实事求是的、文理通顺、字迹端正的实验报为了顺利完成实验任务,确保人身、设备安全,培养严谨、踏实、实事求是的科学作风和爱护国家财产的优秀品质,特制1.1.1 认真阅读实验指导书,分析、掌握实验电路的工作原理,并进行必要的估算。

1.21.31.42.使用仪器、设备前必须了解其性能、操作方法及注意事项,在使用时应严格遵守。

3.实验时接线要认真,相互仔细检查,确信无误才能接通电源。

初学或没有把握时应经指导教师审查同意后才能接通电源。

4.实验时应注意观察,若发现有破坏性异常现象(例如有元件冒烟、发烫或有异味),应立即关断电源,保持现场,报告指导教师。

找出原因、排除故障并经指导教师同意才能再继续实验。

如果发生事故(例如元件或设备损坏)应主动填写实验事故报告单,服从实验室和指导教师对事故的处理决定(包括经济赔偿)5.6.实验过程中应仔细观察实验现象,认真记录实验结果(数据、波形及其现象)。

微波实验二微带传输线

实验二微带传输线实验一实验目的1.了解微带传输线的基本理论和特性。

2.掌握用网络分析仪测量微带传输线接不同负载时工作参量的值。

3.通过测量认知1/4波长传输线阻抗变换特性。

二实验原理1.微带传输线的基本原理微带线目前是混合微波集成电路和单片微波集成电路使用最多的一种平面型传输线。

它可用作光刻程序制作,且容易与其它无源微波电路和有源微波电路器件集成,实现微波部件和系统的集成化。

微带线可以看作是由双导线传输线演变而成的,如图2—1所示。

在两根导线之间插入极薄的理想导体平板,它并不影响原来的场分布,而去掉板下的一根导线,并将留下的另一根导线“压扁”,即构成了微带传输线。

实际的微带线结构如图2-1所示。

导体带(其宽度为的厚度为力和接地板均由导电良好的金属材料(如银,铜,金)构成,导体带与接地板之间填充以介质基片,导体带与接地板的间距为h o有时为了能使导体带,接地板与介质基片牢固地结合在一起,还要使用一些黏附性较好的铭,铝等材料。

介质基片应采用损耗小,黏附性,均匀性和热传导性较好的材料,并要求其介电常数随频率和温度的变化也较小。

图2—1双导线演变成微带线图2—2微带线的结构及其场分布2.微带线的技术参数2.1特性阻抗若微带线是被一种相对介电常数为名的均匀介质所完全包围着,并把准TEM模当作纯TEM模看待,并设£和C分别为微带线单位长度上的电感和电容,则特性阻抗为相速以为_1_Vovp"√Zc-X但实际上的微带线是含有介质和空气的混合介质系统,因此不能直接套用上面的公式求特性阻抗。

为了求出实际的微带线的特性阻抗Zc和相速度),而引入了等效相对介电常数的概念。

如果微带线的结构现状和尺寸不变,当它被单一的空气介质所包围着时,其分布电容为C。

实际微带线是由空气和相对介电常数为益的介质所填充,它的电容为G,那么,等效相对介电常数册的定义为这样,实际微带线的特性阻抗即可表示为Z :为在同样形状和结构尺寸的情况下,填充介质全部是空气时微带线的特性阻抗我们假定已成形的导体的厚度t 与基片厚度h 相比可以忽略h(t/h<0.005)0这种情况下,我们能够利用只与线路尺寸(w 和h)和介电常数名有关的经验公式。

基于Cadence的模拟集成电路设计

作为流行的EDA工具之一,Cadence一直以来以其强大的功能受到广大EDA工程师的青睐。Cadence可以完成整个IC设计流程的各个方面,如电路图输入(Schematic Input)、电路仿真(Analog Simulation)、版图设计(Layout Design)、版图验证(Layout Verification)、寄生参数提取(Layout Parasitic Extraction)以及后仿真(Post Simulation)。如图1.1所示,我们给出了一个简单的模拟集成电路设计流程,以及对应的Cadence工具。

2

2.1

Cadence初次启动之前需要如下一些配置文件:

.cshrc文件:有关一些Cadence必需的环境变量,如Cadence软件的路径及license。

.cdsenv文件:包含Cadence各种工具的一些初始设置。

.cds.lib文件:用户库的管理文件,在第一次运行Cadence时自动生成。

.cdsinit文件图3.11最终的电路图

3.6

设计完成的电路和图需要经过检查方能进行仿真。单击菜单栏->Check and Save或者键入快捷键大写的X(shift+x),可以对电路进行检查并存储。

检查后如果有错会在CIW窗口上显示示错误或警告信息。如果没错,则如图3.12所示,检查无误后可以关闭Composer了。

如果不做版图设计的话,就不需要tf文件。这里我们选择第三项Don’t need a techfile,单击OK确定。

现在,本教程需要的库就设置好了。

3

本章将通过画一个CMOS反相器来简单的介结电路图设计流程。Cadence用于原理图设计的工具称为Composer。

3.1

集成功率放大电路实验报告

集成功率放大电路实验报告班级:10级电子信息学号:02姓名:梁彩云日期:2011-7-1一、实训目的1)熟悉万用表、示波器等仪器的利用。

2)了解功率放大电路的组成,加深对功率放大电路的感性熟悉。

3)掌握电路元器件的选择及检测方式。

4)熟悉了解TDA2030A集成功率放大器的型号、参数及其应用。

5)熟悉功率放大电路的主要特点、性能指标、主要类型及电路特征。

6)制作音量可调,具有高音、低音提升电路,双声道输入、输出,整个系统采用双12V变压器供电的音频功率放大器。

二、实训器材双踪示波器;万用表;电烙铁;电路板制作工具、电路板及其元件等。

三、实训任务①了解电路图绘制软件的相关常识及其特点;②熟悉电路图绘制软件的利用方式;③会用Protel99SE软件绘制电路原理图;④会在Protel99SE软件环境中自概念库元件;⑤掌握电路板布局布线规则的设置方式;⑥会利用Protel99SE软件生成实用的电路板图;⑦制作出电子产品,并学会调试、检修;⑧作好实训笔记,对自己所发现的疑难问题及时请教解决;⑨联系自己专业知识,体会本次实训的具体进程,总结自己的心得体会;10参考相关的书籍、资料,认真完成实训报告。

○这次实训为两大部份:第一部份是画电路图、制造PCB板。

第二部份是在印制版上焊接安装电路。

四、实训进程1、电路原理图图01二、分析电路工作原理集成功率放大电路如上图所示。

三极管C1815组成前置放大级,主如果补偿其后音调电路的信号衰减,两个100kΩ的电位器及其附属元件组成衰减式高低音调节电路(均衡电路),经调节后的音频信号送入集成功率放大电路TDA2030A,进行功率放大,推动多媒体音箱发声。

电路由50W,次级电压20V的变压器经整流滤波后提供。

若是采用集成功率放大电路LM1872,其输出功率将更大。

3、实验电路原理分析本实验的内容是设计和制备一个可以供多媒体音箱利用的音频功率放大电路,整体功能框图如图1 所示,可以分为音频放大和直流电源两大部份。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

实验2 导线特性

1 实验目的

了解导线的RC特性和建模方法。

2 实验内容

设某层金属阻值为0.086欧姆/方。

金属层导线长度为1300um,宽度为0.13um;其集总电容为0.1pf。

设信号源为1.2V,内阻1K欧姆。

利用Elmore延时公式计算、并使用下列模型仿真此导线的延时(50%至50%)以及上升和下降时间(10%至90%)。

(1)一个电阻、一个电容的集总模型;

(2) 3型RC模型;

(3)T3型RC模型。

下面是当时编写的,自己都记不清了,问号是保存为记事本txt有问题。

(a)

INVa

.options list node post

.model m1 pmos level=2

.model m2 nmos level=2

m1 out in vdd vdd?m1 L=0.250u?W=1.125u

m2 out in 0? 0? m1 L=0.250u?W=0.375u

cl out 0 1pf

vdd vdd 0 dc 2.5

vin in 0 dc 2.5

.op

.dc vin 0 2.5 0.5

.print dc v(in) v(out)

.probe dc v(in) v(out)

.END

(b)

INVb

.options list node post

.model m1 pmos level=2

.model m2 nmos level=2

m1 out in vdd vdd?m1 L=0.250u?W=2.750u m2 out in 0? 0? m1 L=0.250u?W=0.375u cl out 0 1pf

vdd vdd 0 dc 2.5

vin in 0 dc 2.5

.op

.dc vin 0 2.5 0.5

.print dc v(in) v(out)

.probe dc v(in) v(out)

.END

(c)

INVc

.options list node post

.model m1 pmos level=2

.model m2 nmos level=2

m1 out in vdd vdd?m1 L=0.250u?W=1.125u m2 out in 0? 0? m1 L=0.250u?W=0.375u cl out 0 1pf

vdd vdd 0 dc 2.5

vin in 0 dc vd

.data vd_table

1

1.5

2.5

.enddata

.op

.tran 100p 100n

.print tran v(in) v(out)

.probe tran v(in) v(out)

.END

(d)

INVc

.options list node post

.model m1 pmos level=2

.model m2 nmos level=2

m1 out in vdd vdd?m1 L=0.250u?W=0.750u m2 out in 0? 0? m1 L=0.250u?W=0.375u cl out 0 1pf

vdd vdd 0 dc 2.5

vin in 0 dc 2.5

.op

.tran 100p 100n

.print tran v(in) v(out) .probe tran v(in) v(out) .END。