16位通用移位寄存器设计报告

移位寄存器实验报告

移位寄存器实验报告实验题目:移位寄存器一、实验目的了解移位寄存器的原理,掌握移位寄存器的应用。

二、实验原理移位寄存器是一种存储器件,用于将二进制数据以位为单位进行移位操作。

移位寄存器由若干个D触发器组成,每个D触发器的输出接入下一个D触发器的输入,以此类推,形成了一个环形移位结构。

移位寄存器有三种基本工作模式:串行输入并行输出(SIPO),并行输入串行输出(PISO)和并行输入并行输出(PIPO)。

在SIPO模式下,输入数据串行输入到移位寄存器的最高位,然后逐个向低位移位,最终输出到最低位。

在PISO模式下,输入数据并行输入到移位寄存器的每个位,然后逐个向高位移位,最终输出到最高位。

在PIPO模式下,输入数据并行输入到移位寄存器的每个位,然后逐个向低位移位,最终输出到每个输出端口。

移位寄存器的应用很广泛,其中最常见的是时序信号的处理。

移位寄存器可以用于数字频率合成、序列生成、编码器和解码器等方面。

三、实验设备1. 计算机2. Xilinx ISE14.6软件3. BASYS2开发板4. USB下载器四、实验步骤1. 设计移位寄存器的电路原理图并进行仿真。

2. 在Xilinx ISE14.6软件中创建工程并添加源、约束和测试文件。

3. 将电路原理图转换成Verilog HDL代码。

4. 将Verilog HDL代码综合为综合网表,并进行时序分析。

5. 将综合网表映射到BASYS2开发板上并进行状态机调试。

6. 使用USB下载器将设计好的逻辑文件下载到FPGA上。

7. 连接开发板的输入输出端口,验证移位寄存器的正确性,并观察输出端口结果。

五、实验结果与分析通过移位寄存器的实验,我们学会了如何使用Verilog HDL设计并实现移位寄存器,并对移位寄存器进行了详细的仿真、综合、映射和下载调试。

在实验过程中,我们还学会了串行输入并行输出(SIPO),并行输入串行输出(PISO)和并行输入并行输出(PIPO)三种基本工作模式,掌握了移位寄存器在数字频率合成、序列生成、编码器和解码器等领域中的使用方法。

移位寄存器及其应用实验报告

移位寄存器及其应用实验报告1. 背景在数字电路中,移位寄存器是一种常见的基本电路元件。

它可以将输入数据按照一定规则进行移位操作,并输出处理后的数据。

移位寄存器通常由触发器构成,分为串行移位寄存器和并行移位寄存器。

在实际应用中,移位寄存器常用于数据存储、数据传输、脉冲发生器等方面。

本实验旨在通过设计移位寄存器电路及其应用电路的实验,加深对移位寄存器工作原理的理解,掌握其应用。

2. 实验目的1.了解移位寄存器的基本原理;2.学会设计移位寄存器电路及其应用电路;3.掌握移位寄存器的应用方法。

3. 实验原理与方法3.1 移位寄存器原理移位寄存器将输入数据按照一定规则进行移位操作,并输出处理后的数据。

常见的移位规则包括:左移、右移、循环左移、循环右移等。

移位寄存器通常由触发器构成,触发器的状态决定了寄存器中存储的数据。

本实验主要探究两种常用的移位寄存器:串行移位寄存器和并行移位寄存器。

3.1.1 串行移位寄存器串行移位寄存器中,数据是按照位的顺序逐个进行移位的。

串行移位寄存器可以通过级联多个D触发器实现,每个D触发器的输出与下一个D触发器的输入相连。

3.1.2 并行移位寄存器并行移位寄存器中,数据的位同时进行移位。

并行移位寄存器可以通过级联多个D 触发器实现,每个D触发器的输入都与移位数据的对应位相连。

3.2 实验所用材料与方法3.2.1 材料•移位寄存器芯片•发光二极管(LED)•电路连接线3.2.2 方法1.实验预备:准备实验所需的移位寄存器芯片、LED和电路连接线。

2.按照移位寄存器原理,设计移位寄存器电路并进行布线连接。

3.使用示波器检查电路的正确性。

4.进行实验验证,观察移位寄存器的运行情况,并记录实验结果。

4. 实验结果与分析本实验设计了一个4位串行移位寄存器电路,并进行了验证实验。

首先,按照原理部分的描述,我们选择了一个基于D触发器的4位串行移位寄存器芯片。

通过连接四个D触发器,将其串联起来,即可构成一个4位的串行移位寄存器。

计算机组成原理课程设计报告16位模型机的设计

石家庄经济学院华信学院计算机组成原理课程设计报告计算数据块中所有数据的累加和并存储到内存单元中题目16位模型机的设计姓名学号4114170801班号一班指导老师成绩2014年1月目录一、引言 (3)1.1设计目的 (3)1.2设计任务 (3)二、详细设计及实现 (4)2.1 拟定指令系统 (4)2.2指令格式 (5)2.3寻址方式 (5)三、16位CPU的模型 (7)3.1 各功能部件的VHDL设计 (9)3.2 16位模型机的设计与实现 (22)四、总结 (27)五、参考文献: (27)六、代码 (28)一、引言1.1设计目的为掌握并巩固本学期所学习的计算机组成原理知识,设计本次试验。

运用整合所学的相关知识,一步步设计构造一台基本的模型计算机,明确计算机的控制原理与控制过程,巩固和灵活应用所学的理论知识,掌握计算机组成的一般设计方法,提高学生设计能力和实践操作技能,为从事计算机研制与设计打下基础。

1.2设计任务本机功能:计算数据块中所有数据的累加和并存储到内存单元中。

汇编代码如下:START:MOV SI, OFFSET SRC1 ;源操作数地址送SIMOV DI,OFFSET DXT ;目的操作数地址送DIMOV BX,OFFSET SRC2 ;结束地址送BXMOV BL 0 ;设置BL中初值为0NEXT:MOV AL,[SI] ;取数ADD BL , AL ; 数据相加MOV [DI],AL ;存数CMP SI, BX ;JE START ;如果SI=BX,则转向STARTINC SI ;修改源地址JMP NEXT ;转向NEXT二、详细设计及实现2.1 拟定指令系统分析:1)依据汇编语言程序得出部件间的数据流的方向为●立即数→寄存器●寄存器↔内存内存操作数采用寄存器间址寻址方式●源与目的寄存器内容比较,如果源等于目的转移,转向地址在指令中提供●寄存器加1指令●无条件转移指令,转向地址在指令中提供。

16位通用移位电路

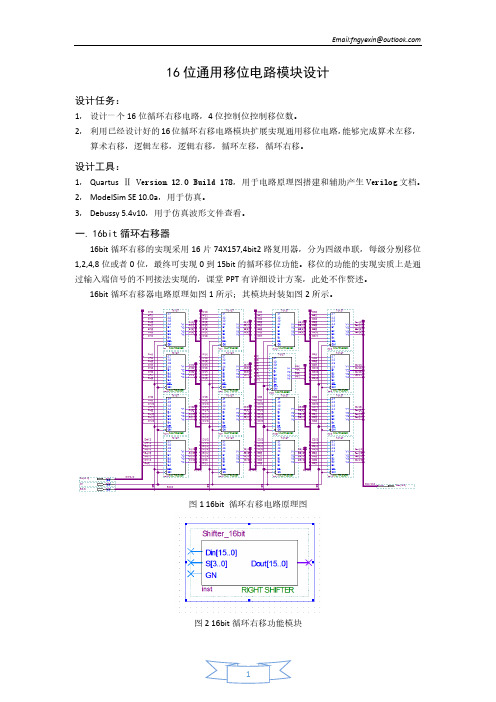

图1 循环右移1位模块图3 循环右移1到16位模块图根据老师上课讲的知识,可以知道此模块节省器件,延迟稍大。

图4 循环右移一位symbol图6 8-n减法器图7 8-n减法器symbol将移位数据选择端S0,S1,S2,S3连接到8-n数据口d0,d1,d2,d3,其中减法器中sel端口是用来选择数据8-n和数据n(S3S2S1S0),即可以用来选择循环左移和右移;将减法器输出数据端口连接到循环右移电路的移位数据选择端实现循环左右移电路。

图8 数据转换电路上图中,输入数据n(IN4 IN3 IN2 IN1),则输出16位数据,其中低n位全为0,高n位数据全为1,例如,输入0010,则输出1111 1111 1111 1100,这个电路可以用来实现逻辑移位和算术移位时的数据转换。

9 数据转换电路symbol逻辑右移数据转换电路算术右移数据转换电路在上图中,首先通过扩展后的16位数据选择器选择转换后的逻辑右移数据和转换后的算术右移数据,sel1控制数据选择,sel1=0时选择逻辑右移数据,sel1=1选择逻辑算术右移数据,输出的16位数据连接到下一个16位数据选择器b端口,a端口接转换后的逻辑/算术左移数据,sel0控制数据选择,sel0=0时选择逻辑/算术左移移数据,sel0=1选择上一级数据选择器输出数据,接着输出后的16位数据再次接到下一级数据选择器的a端口,b端口接原始的16位移位数据A15~A0,sel2控制数据选择。

下面是功能选择的命令控制:sel0 sel1 sel2循环左移 0 任意 1循环右移 1 任意 1逻辑(算术)左移0 任意0逻辑右移 1 0 0算术右移 1 1 0仿真激励设计方案及电路仿真结构2.算术右移sel2 sel1 sel0 S3S2S1S0 A15~A0 Y15~Y00 1 1 0100 1000100101100010 11111000100101104.循环右移sel2 sel1 sel0 S3S2S1S0 A15~A0 Y15~Y01 0 1 1001 1000100101100010 1011000101000100循环左移sel2 sel1 sel0 S3S2S1S0 A15~A0 Y15~Y01 0 0 1100 1000100101100010 0010100010010110从上图中可以看出,电路延迟时间大概为1ns左右,速度较快。

移位寄存器实验报告

移位寄存器实验报告姓名:陈素学号:3120100621 专业:软件工程课程名称:逻辑与计算机设计基础实验同组学生姓名:张闻实验时间:y yyy-mm-dd 实验地点:紫金港东4-509 指导老师:一、实验目的和要求掌握移位寄存器的工作原理及设计方法掌握串、并数据转换的概念与方法了解序列信号在CPU控制器设计中的应用二、实验内容和原理2.1 实验原理带并行置入的移位寄存器移位寄存器:每来一个时钟脉冲,寄存器中的数据按顺序向左或向右移动一位必须采用主从触发器或边沿触发器不能采用电平触发器数据移动方式:左移、右移数据输入输出方式串行输入,串行输出串行输入,并行输出并行输入,串行输出串行输入的移位寄存器使用D触发器,可构成串行输入的移位寄存器2.2 标题<正文>带并行输入的右移移位寄存器数据输入移位寄存器的方式:串行输入、并行输入带并行输入的8位右移移位寄存器module shift_reg(clk, S, s_in, p_in, Q); input wire clk, S, s_in; input wire [7:0] p_in; output wire [7:0] Q; wire [7:0] D; wire nS;FD FDQ0(.C(clk), .D(D[0]), .Q(Q[0])), FDQ1(.C(clk), .D(D[1]), .Q(Q[1])), FDQ2(.C(clk), .D(D[2]), .Q(Q[2])), FDQ3(.C(clk), .D(D[3]), .Q(Q[3])), FDQ4(.C(clk), .D(D[4]), .Q(Q[4])), FDQ5(.C(clk), .D(D[5]), .Q(Q[5])), FDQ6(.C(clk), .D(D[6]), .Q(Q[6])), FDQ7(.C(clk), .D(D[7]), .Q(Q[7]));OR2 D0_L(.I0(L_0), .I1(R_0), .O(D[0])), D1_L(.I0(L_1), .I1(R_1), .O(D[1])), D2_L(.I0(L_2), .I1(R_2), .O(D[2])), D3_L(.I0(L_3), .I1(R_3), .O(D[3])), D4_L(.I0(L_4), .I1(R_4), .O(D[4])),串行输入SD5_L(.I0(L_5), .I1(R_5), .O(D[5])), D6_L(.I0(L_6), .I1(R_6), .O(D[6])), D7_L(.I0(L_7), .I1(R_7), .O(D[7]));并行-串行转换器 没有启动命令时并行-串行转换器ser_out并行输入par_in 移位输入7位并行-串行转换器ser_out并行输入par_in 移位输入7位并行-串行转换器2.1 实验内容用Verilog HDL语言,采用结构化描述方法设计一个8位带并行输入的右移移位寄存器。

计算机组成原理实验报告-寄存器实验

千里之行,始于足下。

计算机组成原理实验报告-寄存器实验计算机组成原理实验报告-寄存器实验》一、实验目的本次实验旨在通过设计和实现一个基本的寄存器,加深对计算机组成原理中寄存器的理解,并掌握寄存器在计算机中的应用。

二、实验设备及软件1. 实验设备:计算机2. 实验软件:模拟器软件Mars3. 实验材料:电路图、线缆、元器件三、实验原理寄存器是计算机的一种重要组成部分,用于存储数据和指令。

一个基本的寄存器通常由一组触发器组成,可以存储多个位的信息。

本实验中,我们需要设计一个16位的寄存器。

四、实验步骤1. 确定寄存器的结构和位数:根据实验要求,我们需要设计一个16位的寄存器。

根据设计要求,选择合适的触发器和其他元器件。

2. 组装寄存器电路:根据电路图,将选择好的元器件按照电路图连接起来。

3. 连接电路与计算机:使用线缆将寄存器电路连接到计算机的相应接口上。

4. 编写程序:打开Mars模拟器软件,编写程序来测试寄存器的功能。

可以编写一段简单的程序,将数据写入寄存器并读取出来,以验证寄存器的正确性。

5. 运行程序并测试:将编写好的程序加载到Mars模拟器中,并运行程序,观察寄存器的输出和模拟器的运行结果。

第1页/共3页锲而不舍,金石可镂。

五、实验结果在本次实验中,我们成功设计和实现了一个16位的寄存器,并进行了相关测试。

经过多次测试,寄存器的功能和性能良好,能够准确地存储和读取数据。

六、实验心得通过本次实验,我对寄存器的结构和工作原理有了更深入的了解。

寄存器作为计算机的一种重要组成部分,起着存储和传输数据的作用。

通过实际操作和测试,我更加清楚了寄存器在计算机中的应用和重要性。

在实验过程中,我遇到了一些问题,如电路连接不稳定、程序错误等,但通过仔细检查和调试,最终解决了这些问题。

这次实验也让我深刻体会到了学习计算机组成原理的重要性,只有深入理解原理并通过实践运用,才能真正掌握计算机的工作原理和能力。

通过这个实验,我有了更深入的认识和理解,对计算机组成原理的学习也更加系统和完整。

EDA创新性实验项目——16位CPU设计

EDA创新性实验项目——16位CPU设计一、项目背景随着计算机科学和技术的不断发展,人们对计算机处理速度和性能的需求也在不断增加。

在这种背景下,为了满足人们对计算速度和性能的需求,研究者们开始将目光投向了新型的CPU设计。

传统的CPU设计多为32位或64位,但这种设计可能会带来一些不必要的复杂性和成本。

因此,设计一种16位CPU成为了当前研究的热点之一二、项目目标本实验项目旨在设计一款16位CPU,以满足轻量级计算需求,并保证其性能和效率。

通过设计一款16位CPU,可以降低处理器的成本和复杂度,提高计算性能,并且更好地满足轻量级计算需求。

三、项目内容1.CPU指令设计:设计新的16位CPU指令集,包括运算指令、数据传输指令、分支跳转指令等,以实现更加高效的计算功能。

2.CPU架构设计:设计16位CPU的整体架构,包括寄存器文件、数据通路、控制单元等,确保CPU的稳定性和高效性。

3.性能优化:对设计的CPU进行性能优化,提高其计算速度和响应速度,确保其在轻量级计算中的高效性。

4.性能评估:通过仿真和实验对设计的16位CPU进行性能评估,检验其计算速度和稳定性,以保证其满足设计需求。

四、项目实施步骤1.设计CPU指令集:根据实际需求设计新的16位CPU指令集,包括指令的格式、操作码和功能,保证其具有高效的计算能力。

2.设计CPU架构:设计16位CPU的整体架构,包括寄存器文件、数据通路和控制单元,确保其能够稳定运行和高效计算。

3.性能优化:对设计的CPU进行性能优化,优化数据通路和控制单元的设计,提高CPU的计算速度和响应速度。

4.实验仿真:通过基于EDA工具进行CPU的设计仿真,检验设计的CPU在不同场景下的计算性能和稳定性。

5.性能评估:对设计的CPU进行性能评估,比较其与传统32位CPU 的性能差异,确保16位CPU在轻量级计算中的优越性。

五、项目成果通过本实验项目的实施,设计一款16位CPU并进行性能评估1.设计一款高效、稳定的16位CPU,满足轻量级计算需求。

移位寄存器实验报告

移位寄存器实验报告移位寄存器实验报告引言移位寄存器是数字电路中常用的模块,它能够将输入的数据按照一定的规则进行移位操作。

本次实验旨在通过实际搭建移位寄存器电路,并通过观察输出结果来验证其功能和性能。

实验目的1. 掌握移位寄存器的工作原理和基本结构;2. 了解不同类型的移位寄存器,并能够根据需求选择合适的类型;3. 熟悉移位寄存器的应用场景和使用方法。

实验器材1. 移位寄存器芯片;2. 电路连接线;3. 示波器;4. 信号发生器。

实验步骤1. 将移位寄存器芯片连接到电路板上,并根据实验要求进行电路连接;2. 使用信号发生器产生输入信号,并将其输入到移位寄存器中;3. 通过示波器观察移位寄存器的输出信号,并记录下观察结果;4. 根据实验要求调整输入信号的频率和幅度,并观察移位寄存器的响应情况;5. 分析实验结果,总结移位寄存器的特性和应用。

实验结果在本次实验中,我们使用了一个4位移位寄存器芯片,并将其连接到电路板上。

通过信号发生器产生的输入信号,我们观察到移位寄存器的输出信号按照一定的规则进行了移位操作。

当输入信号的频率较低时,移位寄存器的输出信号可以清晰地观察到每一位的变化;而当输入信号的频率较高时,移位寄存器的输出信号则呈现出连续的变化。

通过实验结果的观察和分析,我们可以得出以下结论:1. 移位寄存器的工作原理是将输入信号按照一定的规则进行移位操作;2. 移位寄存器的输出信号与输入信号的频率和幅度有关;3. 移位寄存器可以用于数据的平移、扩展、压缩等操作;4. 不同类型的移位寄存器具有不同的特性和应用场景。

讨论与总结移位寄存器作为数字电路中的重要模块,在各种电子设备中都有广泛的应用。

它不仅可以用于数据的移位操作,还可以用于数据的存储、传输和处理。

在计算机系统中,移位寄存器常常用于数据的输入和输出,以及数据的处理和控制。

本次实验通过实际搭建移位寄存器电路,并观察其输出结果,使我们更加深入地了解了移位寄存器的工作原理和应用。

16位通用移位电路设计

wire [15:0] LK; LK_gen i1 ( .A(Var[0]), .B(Var[1]), .C(Var[2]), .D(Var[3]), .LK(LK)); Initial begin $fsdbDumpfile("./wave/wave.fsdb"); $fsdbDumpvars; end initial begin Var=3'b0; #1000 $finish; end always @(Var) begin #10 Var<=Var+1'd1; end endmodule

2

Email:fngyexin@

Drct=1 时右移,右移 k 位时对低 k 位数据进行选择输入。Mode=00 时循环移位,低 k 位

保持不变;Mode=01 时算术移位,低 k 位赋值为 MSB;Mode=10 时逻辑移位,低 k 位赋值 为 1; Mode=11 时暂时不定义。 可以看出,对 16 个数据中的每个数据,都是这四个数据的复用:0,1,原值,最高位。 四路复用可用 2 个控制信号进行控制,设为 x,y。定义如下表: 表 1 循环右移器数据输入端的选择输入 xy out description 00 01 10 11 根据表 1 提供的真值表数据,其所表示的电路如图 4 所示。 A B 0 1 原值 最高位 0 1

表 2 译码电路功能表 Mode[1:0] S[3:0] 00 01 10 00 01 10 K K K K K K

xy

低 K 位 00,其余 00 低 K 位 01,其余 00 低 K 位 11,其余 00 高 K 位 00,其余 00 高 K 位 10,其余 00 高 K 位 10,其余 00

图 1 16bit 循环右移电路原理图

基于FPGA的16位寄存器设计.

商洛学院学位论文

第一章 绪论

随着社会的发展,科学技术也在不断的进步。特别是计算机产业,可以说是 日新月异,寄存器作为计算机的一个重要部件,移位寄存器更是如此,从先前的 只能做简单的左移或右移功能的寄存器到现在广泛应用的具有寄存代码、实现数 据的串行--并行转换、数据运算和数据处理功能的移位寄存器。移位寄存器正在 向着功能强,体积小,重量轻等方向不断发展,本设计主要介绍的是一个基于超 高速硬件描述语言VHDL对移位寄存器进行编程实现[6]。

1.2 课题的内容

本毕业设计主要是关于移位寄存器的设计,它不仅描述了设计所需要多种技 术的介绍,例如EDA、FPGA、VHDL语言、Quartus II软件环境等,并且对移位 寄存器的三种设计进行了时序仿真,包括左移、右移、串行输入及仿真等功能。 本设计根据移位寄存器功能的不同,设计了三种移位寄存器。

1.1 课题目的

在计算机中常要求寄存器有移位功能。如在进行乘法时,要求将部分积右移; 在将并行传送的数转换成串行数时也需要移位。因此,移位寄存器的设计是必要 的。

本次设计的目的就是利用计算机组成原理中移位寄存器的相关知识,通过课 程设计更加深入的了解移位寄存器的功能。了解EDA技术,并掌握VHDL硬件描 述语言的设计方法和思想,通过学习的VHDL语言结合计算机组成原理中的相关 知识理论联系实际,掌握所学的课程知识。通过对移位寄存器的设计,巩固和综 合运用所学知识,提高对计算机组成原理的理解。

近年来,集成电路和计算机应用得到了高速发展,现代电子设计技术已迈入 一个崭新的阶段,具体表现在:(1)电子器件及其技术的发展将更多地趋向于为 EDA服务;(2)硬件电路与软件设计过程已高度渗透;(3)电子设计技术将归 结为更加标准、规范的EDA工具和硬件描述语言HDL的运用;(4)数字系统的 芯片化实现手段已成主流。因此利用计算机和大规模复杂可编程逻辑器件进行现 代电子系统设计已成为电子工程类技术人员必不可少的基本技能之一。

16位微处理器的设计

16位微处理器的设计成员:学号:姓名:学号:姓名:学号:姓名:2012年5月8日Final report 1.硬件结构:数据寄存器组:AX:累加器,BX:基址寄存器,CX:计数器指示寄存器和变址寄存器组SI:源变址器, DI:目的变址器,SP:堆栈指示器,BP:基础指示器段寄存器CS:代码段寄存器,DS:数据段寄存器,SS:堆栈段寄存器程序计数器:IP标志寄存器:IF2.指令集3.示例程序(1)数组排序汇编语言:DATA SEGMENTSHUZU DB 43H,21H,42H,16H,57H,83H,24HCOUNT EQU $-SHUZUDATA ENDSCODE SEGMENTASSUME CS:CODE,DS:DATASTART:MOV AX,DATAMOV DS,AXMOV CX,COUNT-1MOV BX,0LOP1:MOV DX,CXMOV SI,1LOP2:MOV AL,SHUZU[BX]CMP AL,SHUZU[BX+SI]JNA L1MOV AH,SHUZU[BX+SI]MOV SHUZU[BX+SI],ALMOV AL,AHMOV SHUZU[BX],ALL1:ADD SI,1LOOP LOP2ADD BX,1MOV CX,DXLOOP LOP1MOV AH,4CHINT 21HCODE ENDSEND START●C语言:#include<stdio.h>main(){int a[]={43,21,42,16,57,83,24};inti,j,b;printf("排序前:");for(i=0;i<6;i++)printf("%d ",a[i]);for(i=0;i<5;i++)for(j=i+1;j<6;j++){if(a[i]>a[j]){b=a[i];a[i]=a[j];a[j]=b;}}printf("排序后:");for(i=0;i<6;i++)printf("%d ",a[i]);printf("\n");}(2)计算阶乘●汇编语言:DATA SEGMENTA DW 0RESULT DW ?DATA ENDSCODE SEGMENTASSUME CS:CODE,DS:DATA START: MOV AX,DATAMOV DS,AXXOR AX,AXMOV AX,ACMP AX,0JNE LOOPMOV AX,1LOOP: CALL FACTMOV RESULT,AXMOV AH,4CHINT 21HFACT PROC NEARPUSH AXSUB AX,1JNZ F_CONTPOP AXJMP RETURNF_CONT:CALL FACTPOP CXMUL CLRETURN:RETFACT ENDPCODE ENDSEND START●C语言:#include<stdio.h>main(){longa,i,sum;sum=1;printf("功能:计算阶乘\n");printf("请输入所要计算的数:");scanf("%d",&a);for(i=1;i<=a;i++)sum=sum*i;printf("%ld\n",sum);}(3)求sinx●汇编语言DATA SEGMENTX DB 02HN DB 07HM DB 0DHRESULT DW 0000HDATA ENDSCODE SEGMENTASSUME CS:CODE,DS:DATA START: MOV AX, DATAMOV DS, AXLOP: MOV AX, 01HMOV BX, MMOV CX, NLOOP1: MUL XSUB BX,01HJNZ LOOP1MUL 64H ;计算100*X^MLOOP2: MOV BX, MDIV MSUB BX,01HJNZ LOOP2 ; 计算X^M/M!LOOP3 MOV CX, NMUL 0FEHSUB CX,01HJNZ LOOP3 ;计算(-1)^N*X^M/M!ADD RELULT AX ;计算各项和SUB M, 02HSUB N, 01HJNZ LOPMOV AH, 4CHINT 21HCODE ENDSEND STARTC语言include<stdio.h>main(){int x;int n;int m;int a;x=0x1;n=0x7;m=0xd;long result;long result1;result=1;result1=0;for(n=0x7,n>0,n--){for(m=2n-1,m>0,n--){result=result*x;}result=result*0x64h;for(m=2n-1,m>0,m--){result=result/m ;}for(a=n,a>0,a--){result=result*(-1);}result1=result1+result;}printf("result=%d,result1");}4.分工组员:sin,报告整理。

16位循环移位寄存器的设计并扩展循环移位、逻辑移位、算术移位_-vlsi超大规模集成电路设计

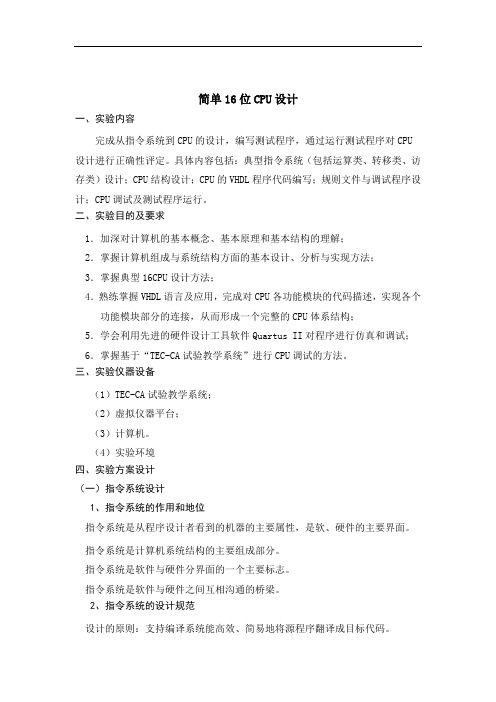

通过S0控制16位多路复用器移位

74x157

A4~A0

B4~B0

G S

Y4~Y0

YO[3:0]

YO[7:4]

YO[11:8]

YO[15:12] DI[3:0]

DI[7:4]

DI[11:8]

DI[15:12]

DI[2:0,15]

DI[6:3]

DI[10:7]

DI[14:11]

S0

DI[15:0]YO[15:0]

A4~A0

B4~B0

G S

Y4~Y0

A4~A0

B4~B0

G S

Y4~Y0

A4~A0

B4~B0

G S

Y4~Y0

循环右移多位的设计:

DI[15:0]

74x157 74x157 74x157 74x157 S074x157

74x157

74x157

74x157

S1

74x157

74x157

74x157

74x157

S2

74x157

74x157

74x157

74x157

S3

DO[15:0]

S[3:0]

Si=1:移动1位移动2位移动4位移动8位

Si=0:不移动

节省器件,延迟大

原理如上图,类似循环右移一位的设计可以设计出循环右移2位、4位、8位的电路。

将这几种移位给以串联即可实现1到15位的任意位数的循环右移。

S[3:0]来控制位数,该电路还有节省器件的优点但延迟较大。

循环左移的实现:

在每个右移模块中加入左右选择电路,即可实现左移与右移输出,其中sel控制左移与右移,具体实现电路如下:。

十六位CPU实验设计报告

简单16位CPU设计一、实验内容完成从指令系统到CPU的设计,编写测试程序,通过运行测试程序对CPU 设计进行正确性评定。

具体内容包括:典型指令系统(包括运算类、转移类、访存类)设计;CPU结构设计;CPU的VHDL程序代码编写;规则文件与调试程序设计;CPU调试及测试程序运行。

二、实验目的及要求1.加深对计算机的基本概念、基本原理和基本结构的理解;2.掌握计算机组成与系统结构方面的基本设计、分析与实现方法;3.掌握典型16CPU设计方法;4.熟练掌握VHDL语言及应用,完成对CPU各功能模块的代码描述,实现各个功能模块部分的连接,从而形成一个完整的CPU体系结构;5.学会利用先进的硬件设计工具软件Quartus II对程序进行仿真和调试;6.掌握基于“TEC-CA试验教学系统”进行CPU调试的方法。

三、实验仪器设备(1)TEC-CA试验教学系统;(2)虚拟仪器平台;(3)计算机。

(4)实验环境四、实验方案设计(一)指令系统设计1、指令系统的作用和地位指令系统是从程序设计者看到的机器的主要属性,是软、硬件的主要界面。

指令系统是计算机系统结构的主要组成部分。

指令系统是软件与硬件分界面的一个主要标志。

指令系统是软件与硬件之间互相沟通的桥梁。

2、指令系统的设计规范设计的原则:支持编译系统能高效、简易地将源程序翻译成目标代码。

正交性:指令字段编码相互独立。

规整性:相似操作有相同的规定。

可扩充性:操作码冗余。

对称性:A-B=》A ;A-B=》B ,便于编译。

3、CPU 中操作数的存储方法CPU 中操作数的存储方法是各种指令集结构之间最主要的区别所在,其影响运算器的组织。

CPU 中用来存储操作数的存储单元主要有: (1)堆栈; (2)累加器; (3)一组寄存器;通用寄存器型指令集结构的主要优点: (1)使编译器有效地使用寄存器;(2)在表达式求值方面,比其它类型指令集结构,具有更大的灵活性; (3)寄存器可以用来存放变量;a.减少存储器的访问量,加快程序的执行速度。

16位桶形(循环)移位寄存器Verlog程序

16位桶形(循环)移位寄存器Verlog程序综合过程要在速度与面积之间进行折中考虑。

“资源共享”是面积的优化技术。

在设计中牺牲一些硅片的面积,往往会增加速度。

下面是一个16位的桶形移位寄存器,(1)是优化前的代码(2)是优化后的代码优化代码使用了两级复用器,其速度得到提高。

复用器共2级个4选一复用器。

对第一级,对输入数据进行0,1,2或3位循环移位;第二级,对输入进行0,4,8,12位的循环移位。

(1)优化前的桶形移位寄存器module barrel_org(S,A_P,B_P);input[3:0]S;input[15:0]A_P;input{15:0]B_P;reg[15:0]B_P;always@(A_P or S)begincase(S)4'b0000:beginB_P<=A_P;end4'b0001:beginB_P[15]<=A_P[0];B_P[14:0]<=A_P[15:1];end4'b0010:beginB_P[15:14]<=A_P[1:0]; B_P[13:0]<=A_P[15:2]; end4'b0011:beginB_P[15:13]<=A_P[2:0]; B_P[12:0]<=A_P[15:3]; end 4'b0100:beginB_P[15:12]<=A_P[3:0]; B_P[11:0]<=A_P[15:4]; end 4'b0101:beginB_P[15:11]<=A_P[4:0]; B_P[10:0]<=A_P[15:5]; end 4'b0110:beginB_P[15:10]<=A_P[5:0]; B_P[9:0]<=A_P[15:6]; end 4'b0111:beginB_P[15:9]<=A_P[6:0]; B_P[8:0]<=A_P[15:7]; end 4'b1000:beginB_P[15:8]<=A_P[7:0]; B_P[7:0]<=A_P[15:8]; end 4'b1001:beginB_P[15:7]<=A_P[8:0]; B_P[6:0]<=A_P[15:9]; end 4'b1010:beginB_P[15:6]<=A_P[9:0]; B_P[5:0]<=A_P[15:10]; end 4'b1011:beginB_P[15:5]<=A_P[10:0]; B_P[4:0]<=A_P[15:11]; end4'b1100:beginB_P[15:4]<=A_P[11:0]; B_P[3:0]<=A_P[15:12]; end 4'b1101:beginB_P[15:3]<=A_P[12:0]; B_P[2:0]<=A_P[15:13]; end 4'b1110:beginB_P[15:2]<=A_P[13:0]; B_P[1:0]<=A_P[15:14]; end 4'b1111:beginB_P[15:1]<=A_P[14:0]; B_P[0]<=A_P[15];enddefault:B_P]<=A_P;endcaseendmodule(2)优化后的桶形移位寄存器module barrel_org(S,A_P,B_P); input[3:0]S;input[15:0]A_P;input{15:0]B_P;reg[15:0]B_P;wire[1:0]SEL1,SEL2;reg[15:0]C;assign SEL1=S[1:0];assign SEL2=S[3:2];always@(A_P or SEL1)begincase(SEL1)2'b00:beginC<=A_P;2'b01:beginC[15]<=A_P[0];C[14:0]<=A_P[15:1];endbeginC[15:14]<=A_P[1:0]; C[13:0]<=A_P[15:2]; end 2'b11:beginC[15:13]<=A_P[2:0]; C[12:0]<=A_P[15:3]; end default:C<<=A_P;endcaseendalways@(A_P or SEL2)begincase(SEL2)2'b00:beginB_P<=C;end2'b01:beginB_P[15:12]<=C[3:0];B_P[11:0]<=C[15:4]; end2'b10:beginB_P[15:8]<=C[7:0]; B_P[7:0]<=C[15:8]; end 2'b11:B_P[15:4]<=C[11:0]; B_P[3:0]<=C[15:12]; end default:B_P<=C;endcaseendendmoudle。

简单16位CPU的设计

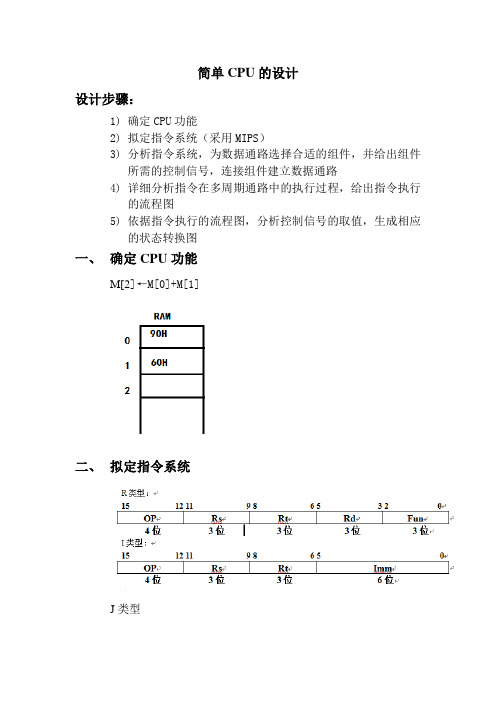

简单CPU的设计设计步骤:1)确定CPU功能2)拟定指令系统(采用MIPS)3)分析指令系统,为数据通路选择合适的组件,并给出组件所需的控制信号,连接组件建立数据通路4)详细分析指令在多周期通路中的执行过程,给出指令执行的流程图5)依据指令执行的流程图,分析控制信号的取值,生成相应的状态转换图一、确定CPU功能M[2]←M[0]+M[1]二、拟定指令系统J类型4位12位指令格式中的op(opcode)是指令操作码。

rs(register source)是源操作数的寄存器号。

rd(register destination)是目的寄存器号。

rt(register target)即可作为源寄存器号,又可作为目的寄存器号,有具体的指令决定。

func(function)可被认为是扩展的操作码,Target表示一下个地址开始注:操作码4位,寄存器字段rs,rt,rd各三位,Fun功能字段3位,Imm立即值字段6位;一共8个寄存器,R0只读不可写,恒为0。

R类型的指令ADD Rd,Rs,RtSUB Rd,Rs,RtAND Rd,Rs,RtOR Rd,Rs,RtXOR Rd,Rs,RtI类型的指令LW Rt, Rs,imm6SW Rt, Rs,imm6存放在ROM中的汇编指令,完成M[2]←M[0]+ M[1]LW R1,0(R0);R1←M[R[0]+0],由于R(0)内容为0,即R1←M[0] LW R2,1(R0);R1←M[R[0]+1],由于R(0)内容为0,即R1←M[1] ADD R3,R1,R2 ; R3←R1+R2SW R3,2(R0) ; M[R[0]+2]←R3下面地址对应着rom模块里面12 NOT R3, R1 0000 001 001 011 11013 SUB R4, R1,R2 0000 001 010 100 01014 BEQ R1 R2 0110 001 010 000 00115 SW R3,7(R0) 0010 000 011 00011116 SW R4,8(R0) 0010 000 100 00100017 LW R1,2(R0)0001 000 001 00001018 LW R2,3(R0)0001 000 010 00001119 J (2) 0011 000 000 000001LW表示读取数据,SW表示存储数据,BEQ表示相等就跳转,J表示直接跳转到某个地址三、根据指令的需求,连接组件,形成多周期的数据通路irwr,pcwr,regwr,aluoutregwr,memwr,lmdwr:相应组件的写使能控制信号,为1时,有效Regdst: 为1时选择RD;为0时选择RT.Signex:为1时扩展器进行符号扩展;为0时扩展器进行零扩展。

16位DSP处理器的移位器的研究

邮局订阅号:82-946360元/年技术创新DSP开发与应用《PLC技术应用200例》您的论文得到两院院士关注16位DSP处理器的移位器的研究Studyofthe16-bitDSPs'Shifter(赣南师范学院)曾瑞淮钟冬庆ZENGRUIHUAIZHONGDONGQING摘要:本文从移位器的功能描述、结构分析入手,并详细阐述了一款16位DSP处理器的高频率低功耗移位器的三个模块的设计。

关键词:移位器;DSPs;设计中图分类号:TP273文献标识码:AAbstract:Thearticlestartedforfunction_describingandstructure_analyzingoftheshifter,anddetaileddescribeddesignofthreemod-uleofthe16-bitDSPs'shifterthatitishighfrequencyandlowpower。

Keywords:Shifter,DSPs,Design文章编号:1008-0570(2006)11-2-0183-03在一般的微处理器中,没有单独设计的移位器,移位功能在算术逻辑单元中实现。

但由于DSP处理器对运算速度要求较高,通过ALU来实现一些移位功能无法满足其要求,所以在DSP中一般设有专门的移位器。

移位器不仅可以提高一般移位功能的速度,还可以更加高速地实现与2的n次幂的乘法运算。

因此对DSP处理器的移位器(Shifter)的研究很有必要的。

移位器是是执行单元的重要组成部分,所有算法的实现都是由执行单元的基本功能组合而成,所有的其他单元例如控制、数据通路都是为执行单元服务的,控制执行部件的具体动作,为执行部件提供充分的数据。

嵌入式定点16位DSP的执行单元结构如图1所示。

DSP执行单元包含3个子单元:16位(结果为40位)移位单元(SHIFT)、16位算术逻辑单元(ALU)和16位(结果为40位)乘法累加单元(MAC)。

移位寄存器实验报告doc

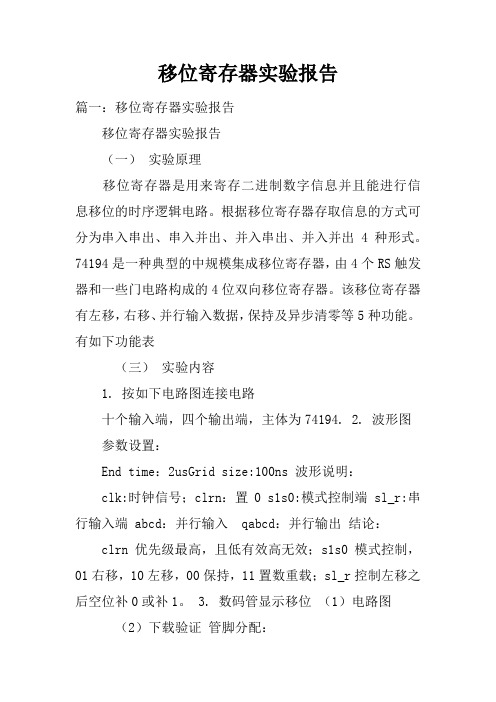

移位寄存器实验报告篇一:移位寄存器实验报告移位寄存器实验报告(一)实验原理移位寄存器是用来寄存二进制数字信息并且能进行信息移位的时序逻辑电路。

根据移位寄存器存取信息的方式可分为串入串出、串入并出、并入串出、并入并出4种形式。

74194是一种典型的中规模集成移位寄存器,由4个RS触发器和一些门电路构成的4位双向移位寄存器。

该移位寄存器有左移,右移、并行输入数据,保持及异步清零等5种功能。

有如下功能表(三)实验内容1. 按如下电路图连接电路十个输入端,四个输出端,主体为74194. 2. 波形图参数设置:End time:2usGrid size:100ns 波形说明:clk:时钟信号;clrn:置0 s1s0:模式控制端 sl_r:串行输入端 abcd:并行输入 qabcd:并行输出结论:clrn优先级最高,且低有效高无效;s1s0模式控制,01右移,10左移,00保持,11置数重载;sl_r控制左移之后空位补0或补1。

3. 数码管显示移位(1)电路图(2)下载验证管脚分配:a,b,c,d:86,87,88,89 bsg[3..0]:99,100,101,102 clk:122 clk0:125 clrn:95 q[6..0]:51,49,48,47,46,44,43 s0,s1:73,72 sl_r:82,83 结论:下载结果与仿真结果一致,下载正确。

一、实验日志1.移位寄存器的实验真的挺纠结的,本来想用7449的,但是下载结果出现了错误,想到它在这个电路图中的功能比较单一,就自己写了一个my7449,终于对了。

五、思考题(1)简单说明移位寄存器的概念及应用情况?概念:移位寄存器是用来寄存二进制数字信息且能进行信息移动的时序逻辑电路。

根据移位寄存器存取信息的方式不同可以分为串入串出,串入并出,并入串出,并入并处4种形式。

应用:移位寄存器可以构成计数器,顺序脉冲发生器,串行累加器,串并转换,并串转换等。

一个16位RISC CPU设计

首先给出了系统的总体结构图如图1:图1.16位RISCCPU结构简图图1中,与外围器件相连的线均为粗体表示。

同时按照要求,设计了MEM用于存放数据和指令,按照便于程序执行的原则,外围设计及连接示意如图2所示:在设计的部件中,针对不同功能的实现,采取了比较繁琐的射击方式。

在MEMORY之外存在几大设计部件。

主要部件设计如下:一.状态控制机:这是最关键的部件,而且,在选定8个状态为一个运行周期的格局以后,对所有指令包括HALT 全部在用统一的指令周期。

这不可避免的导致了单元和面积的增加。

此处存在较大的改进余地。

指令分为五部分:取指,译码,执行,存储器访问,结果写回。

最后一部分很有可能进行第二次寄存器读写。

指令运行周期:(八个时钟周期) 第一周期:取指令 第二周期:指令译码 第三周期:空第四周期:地址线跳转,需要运算的数据送到数据线。

第五周期:ALU 时钟信号,ALU 运算。

第六周期:根据情况,对不同指令,分别进行数据的寄存器读写。

第七周期:对于需要再次读写寄存器的操作,如跳转指令中的地址写回rd Load_ir Into_pc Load_pc Load_reg aux2 Inc_pc aux1 Counter_ena Data_enahalt wrcontr_enaZero clk1Op_code[4:0]寄存器,完成存储。

第八周期:FETCH信号,指令跳转到下面要运行得指令地址,包括正常PC+1和指令跳转地址,为下条指令取指做准备。

控制信号说明:输入信号:Op_code[4:0]:操作数,输入现在是什么指令。

Clk1:时钟信号,大多数的控制信号需要时钟信号的上跳沿触发。

Contro_ena:由控制机产生的信号,控制机复位。

Zero:由ALU送来,用于条件转移指令BZ,BNZ)的辅助信号。

输出信号:(十二个控制信号)Halt:为“1”停机信号。

Wr:为“1”写存储器。

Load_ir:为“1”指令寄存器取指。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

1 1 0 0 0 0 0 0 0 0 0 0 0 0 0 0

1 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

再设循环左右移位电路的 16 位输出分别为 Y15Y14Y13Y12Y11Y10Y9Y8Y7Y6Y5Y4Y3Y2Y1Y0,

可以得到如下逻辑: (1) 循环移位\算术\逻辑左移时有 Pout[n]=Yn Dn A`(其中 A`是对 A 求反, 通过移位方式控制端 A、B 控制自定义 4—16 译码电路使得当 AB=00 时 4—16 自定义译码电 路的输入全为 00,这样输出 Dn=1,也即相当于译码电路不起作用;当 AB=01 时,4—16 自 定义译码电路根据移位位数控制输入端进行产生相应的移位调整序列); (2)算术右移时有 Pout[n]=(Y15 Dn+ Yn Dn`)AB`; (3)逻辑右移时有 Pout[n]=(Yn Dn`)AB。 最后,对电路进行修正,使得当控制输入端输入信号 A B LorR=010、101、111 时电路输 出全为 0。 仿真激励设计方案及电路仿真结果 在对设计好的电路进行仿真时, 考虑到该电路的实际应用中不可能工作在频率极高的环 境中,这样的话在仿真时为了能够清楚地分辨结果,可以视 16 位的并行输入为一个固定的输 入。对于移位位数控制输入端,可以用时间间隔为 100ns 的信号进行仿真,这样可以由仿真 结果得出电路的延迟以及竞争冒险的时间。 (1)A B LorR=000,电路功能实现循环右移,仿真结果如下图 4:

(1)在考虑 16 位循环右移电路的设计时,我选择用 74151“8 选 1 数据选择器”配合门电 路进行搭建桶形移位电路, 对于每个输出断对应需要用两片 74151 对 16 位并行输入数据进行 选择,用移位数控制端 S(S3S2S1S0)中的 S3 实现两片 74151 的片选进而将两片 74151 组成 “16 选 1 数据选择器” ,结构如图 1。用 16 个如图 1 的结构这可以构成 16 位输出的循环右移 电路结构框图,如图 2。

0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1

1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1

1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 0

1 1 1 1 1 1 1 1 1 1 1 1 1 1 0 0

1 1 1 1 1 1 1 1 1 1 1 1 1 0 0 0

(图 4) (2)A B LorR=001,电路功能实现循环左移,仿真结果如下图 5:

(图 5)

(3)A B LorR=011,电路功能实现算术\逻辑左移,仿真结果如下图 6:

(图 6) (4)A B LorR=100,电路功能实现算术右移,仿真结果如下图 7:

(图 7)

(5)A B LorR=110,电路功能实现逻辑右移,仿真结果如下图 8:

S3 S2 S1 S0 D15 D14 D13 D12 D11 D10 D9 D8 D7 D6 D5 D4 D3 D2 D1 D0

0 0 0 0 0 0 0 0 1 1 1 1 1 1 1 1

0 0 0 0 1 1 1 1 0 0 0 0 1 1 1 1

0 0 1 1 0 0 1 1 0 0 1 1 0 0 1 1

(图 2)

(3) 以 16 位循环右移电路(结构图如上图 2)为核心进行构建多功能移位通用电路(结构 图如下图 3) :

16 位并行输入 Pin

16 位 循 环 右 移 4 位全 加器 74283 位 电 路

移位数控制端 S 移位方式控制端 A、B、LorR

16 位 循 环移位并 行输出

16 位循环左移电路

EMAIL:coollover@

设计题目要求

(1) 设计一个 16 位循环右移电路,S 是移位数,A 是移位前的并 行输入,Y 是移位后的并行输出(在本设计中,我用 Pin 表示 移位前的并行输入, Pout 表示移位后的并行输入, S 表示移位 数) ,要求估算电路占用的资源大小及电路的速度; (2) 以上面设计好的 16 位循环右移电路为核心,扩展设计一个能 进行循环右移、循环左移、算术右移、算术左移、逻辑右移、 逻辑左移的通用移位电路。 设计原理及结构方案

移位数控制端 S

4 位全 加器 74283

自 B、LorR

16 位 译 码序列

循 移 输 信 处 产 最 的 望 出 号

环 位 出 号 理 生 终 期 输 信

16 位自定义 移位并行输 出

根据移位方式产生 所需要的译码序列 (图 3)

电路设计描述 (1)16 位循环右移电路设计: 选择用 2 片 74151“8 选 1 数据选择器”对 16 位并行输入数据根据移位数和所在输出位 置进行选择,作为 Pout[n],例如 Pout[0]对应的第一片 74151 的 D7D6D5D4D3D2D1D0 分别 对应 Pin[7]---Pin[0], 第二片 74151 的 D7D6D5D4D3D2D1D0 分别对应 Pin[15]---Pin[8];再如 Pout[6]对应的第一片 74151 的 D7D6D5D4D3D2D1D0 分别对应 Pin[13]---Pin[6], 第二片 74151 的 D7D6D5D4D3D2D1D0 分别对应 Pin[5]---Pin[0]Pin[15]Pin[14], 按照这样的方式不同的输出 位对应的不同的接线方法就可以根据 S(S3S2S1S0)选择相应的输入数据作为输出 Pout[n]。 (2)扩展为 16 位的循环右移电路: 对于循环移位而言,循环左移 N 位即相当于右移 16-N 位,根据这个原理,在左移 N 位 时就可以将控制端 S(S3S2S1S0)各位分别求反然后加 1 既得 16-N,然后用新产生的移位位 数作为 16 位循环右移电路的移位位数控制端,这样输出就是右移 16-N 位,也即左移 N 位。 (3)将循环左右移位电路扩展为算术左右移位、逻辑左右移位通用电路: 首先,我们知道算术左移是低位移向高位,最低位补“0” ,算术右移是高位移向低位, 最高位保持不变;逻辑左移是低位移向高位,最低位补“0” ,逻辑右移是高位移向低位,最 高位移入“1” 。通过观察我们发现,算术左移和逻辑左移是相同的移位操作,因此扩展时实 际上是扩展为三类:算术\逻辑左移、算术右移、逻辑右移。 其次,对各个扩展移位功能分配移位方式控制信号:A B LorR=000 时进行循环右移;A B LorR=001 时进行循环左移;A B LorR=011 时进行算术\逻辑左移;A B LorR=100 时进行算 术右移;A B LorR=100 时进行逻辑右移。 然后,通过观察发现算术、逻辑移位实际是对循环移位进行相应位的变化而得到。在这 里我们首先设计一个自定义的 4—16 译码器,要求译码器的真值表如下:

1 1 1 1 1 1 1 0 0 0 0 0 0 0 0 0

1 1 1 1 1 1 0 0 0 0 0 0 0 0 0 0

1 1 1 1 1 0 0 0 0 0 0 0 0 0 0 0

1 1 1 1 0 0 0 0 0 0 0 0 0 0 0 0

1 1 1 0 0 0 0 0 0 0 0 0 0 0 0 0

16 位并行输入 Pin

74151 16 位并行输出的其中一端 Pout[n]

移位数控制端 S

74151

(图 1)

16 位并行输入 Pin

74151 74151

16 位并行输出端 Pout[0]

移位数控制端 S

16 位并行输入 Pin

74151 16 位并行输出端 Pout[15] 74151

移位数控制端 S

1 1 1 1 1 1 1 1 1 1 1 1 0 0 0 0

1 1 1 1 1 1 1 1 1 1 1 0 0 0 0 0

1 1 1 1 1 1 1 1 1 1 0 0 0 0 0 0

1 1 1 1 1 1 1 1 1 0 0 0 0 0 0 0

1 1 1 1 1 1 1 1 0 0 0 0 0 0 0 0

(图 8) (6)A B LorR=010、101、111,此三种输入控制信号为违法信号,输出结果应全为 0,仿真 结果如下图 9:

(图 9)

设计总结

在本设计中,采用桶形移位电路,大大降低了电路整体的延迟时间,使的竞争冒险的时 间不大于 10ns,符合工程应用的条件,这是本设计的突出优势。但是,由于采用了桶形移位 电路设计, 所以整体电路用到了 32 片 74151 “8 选 1 数据选择器” 和两片 74283 “4 位全加器” , 使用了将近 300 个不同种类的“门” ,整个电路消耗的硬件资源较多,这是本电路的需要继续 改进的地方。 通过该课程设计,进一步理解了集成电路的设计程序、方法技巧,但是由于大规模集成 电路内部较为复杂,排线极容易出错而且不容易排查出错误所在,由于设计完成的电路需要 对可能的输入结果进行逐一验证,然后对验证不符的情况对电路进行修改,这也是本设计后 期过程中最耗费时间的地方。