EDA大作业

EDA技术大作业(一)——4路抢答器的设计

EDA技术大作业(一)4路抢答器的设计1.设计要求利用基本逻辑门电路、组合逻辑电路和触发器,设计一个四人抢答器。

要求:1)四个参加者编号为A、B、C和D,对应组号为1~4,每个参加者控制一个按键,用其发出抢答信号。

2)主持人有一个控制按键,用于将系统清零,即数码显示管灯灭,并控制抢答开始。

3)参加者按抢答按钮,蜂鸣器响铃,对应的指示灯亮,同时数码管上显示最先抢答者的组号。

4)电路具有互锁功能,有人优先抢答后系统能自动关闭其他路的输入信号。

2.设计报告要求1)给出设计方案,画出设计电路框图,并对各个功能模块进行简单的描述。

2)在multiSIM 2001下绘制仿真电路图,并进行仿真验证。

提示:采用CMOS器件设计抢答器(也可以采用74LSXXX系列芯片)数码显示抢答器采用CMOS电路制作,由触发器、编译码电路、数码管、LED指示灯和蜂鸣器等组成,数码管用于显示抢答者的组号,电路框图如下图所示。

(1)数码显示抢答器框图(2)参考电路(仅供参考,请自己设计)这里采用CMOS器件4511、4013、4069、4072设计4路抢答器,图中J1~J4为抢答按钮,J5为复位按钮,4013为D触发器,4069为反相器,4072为4输入或门,4511为4线-七段锁存/译码/驱动器。

(3)仿真分析依次按下A、B、C、D键观察数码管显示状态和蜂鸣器的输出状态。

按下复位键R,观察数码管显示状态和蜂鸣器的输出状态。

南京航空航天大学金城学院本科生实验报告课程名称:EDA技术设计题名:4路抢答器的设计学生姓名:XXX班级学号:XXXXX2010年X月X日一、实验题目和要求二、设计框图三、设计电路图要求对电路图进行简单的功能描述四、仿真结果和分析五、对本课程的几点建议附:个人联系方式手机:E-mail:。

eda大作业

e d a大作业本页仅作为文档页封面,使用时可以删除This document is for reference only-rar21year.March班级 021291学号 02129057EDA实验报告学院电子工程学院专业电子信息工程学生姓名 02129057导师姓名纠博交通控制器一.设计目标设计一个十字路口交通控制系统,其东西,南北两个方向除了有红、黄、绿灯指示是否允许通行外,还设有时钟,以倒计时方式显示每一路允许通行的时间,绿灯,黄灯,红灯的持续时间分别是70、5和75秒。

当东西或南北两路中任一道上出现特殊情况,例如有消防车,警车要去执行任务,此时交通控制系统应可由交警手动控制立即进入特殊运行状态,即两条道上的所有车辆皆停止通行,红灯全亮,时钟停止计时,且其数字在闪烁。

当特殊运行状态结束后,管理系统恢复原来的状态,继续正常运行。

二.设计思路与实施方案1.设计目标思路整理①在十字路口的两个方向上各设一组红、绿、黄灯,显示顺序为其中一方向(东西方向)是绿灯、黄灯、红灯;另一方向(南北方向)是红灯、绿灯、黄灯。

②设置一组数码管,以倒计时的方式显示允许通行或禁止通行的时间,其中绿灯、黄灯、红灯的持续时间分别是70s、5s和75s。

③当各条路上任意一条上出现特殊情况时,如当消防车、救护车或其他需要优先放行的车辆通过时,各方向上均是红灯亮,倒计时停止,且显示数字在闪烁。

当特殊运行状态结束后,控制器恢复原来状态,继续正常运行。

2.原理分析本系统主要由分频器,计数器,控制器,倒计时显示器等电路组成。

分频器将晶振送来的50MHZ信号变为1HZ时钟信号;计数器实现总共150秒的计数,它也是交通控制系统的一个大循环;控制器控制系统的状态转移和红黄绿灯的信号输出;倒计时显示电路实现75秒,70秒及5秒的倒计时和显示功能。

整个系统的工作时序受控制器控制,是系统的核心。

基于此,做出交通控制系统的转移图如下:其中,s0:A方向绿灯亮,B方向红灯亮,此状态持续70秒;S1:A方向黄灯亮,B方向红灯亮,此状态持续5秒;S2:A方向红灯亮,B方向绿灯亮,此状态持续70秒;S3:A方向红灯亮,B方向黄灯亮,此状态持续5秒;S4:紧急制动状态,A方向红灯亮,B方向红灯亮,当hold=‘0‘时进入这种状态。

EDA实验课程大作业报告:设计制作一个用于十字路口的交通灯控制器

交通灯控制器设计一.系统功能设计要求设计制作一个用于十字路口的交通灯控制器,要求如下:(1)南北和东西方向各有一组红、绿、黄灯来指挥交通,持续时间分别为25S,20S,和5S。

(2)当有特殊情况(如消防车、救护车等)时,两个方向均为红灯亮,计时停止。

(3)当特殊情况结束后,控制器恢复原来状态,继续正常运行。

(4)用两组数码管,以倒计时方式显示两个方向允许通行或禁止通行的时间。

二.设计原理1.交通灯控制器的状态转换根据题目要求将将红绿灯的状态转换列成如下表:2.设计方案1)由于交通灯需要使用2位7段LED数码管指示通行剩余时间,故采用LED动态扫描方式显示当前时间。

频率设定CLK1k对应的频率为50MHZ。

2)控制模块是交通灯的核心,主要控制交通灯按工作顺序自动变换,同时控制倒计时模块工作,每当倒计时回零时,控制模块接收到一个计时信号,从而控制交通灯进入下一个工作状态。

3)每个方向有一组2位倒计时器模块,用以显示该方向交通灯剩余的点亮时间。

4)显示模块由两部分组成,一是由七段数码管组成的倒计时显示器,每个方向两个七段数码管;二是由发光二极管代替的交通灯,每个方向3个发光二极管。

三.变量符号说明其中,CLK1K为系统时钟信号输入端,SN为禁止通行信号输入通行信号输入端,light0为东西红灯信号输出端,light1为东西黄灯信号输出端,light2为东西绿灯信号输出端,light3为南北红灯信号输出端,light4为南北黄灯信号输出端,light5为南北绿灯信号输出端,led1、led2、led3、led4为数码管地址选择信号输出端。

四.代码说明library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity Hongld ISport (clk1k,SN:in std_logic; --SN紧急情况led1, led2, led3, led4 :out std_logic_vector (6 downto 0);--显示管显示时间用light:out std_logic_vector (5 downto 0)); --红绿黄灯end Hongld;architecture traffic1 of Hongld ISsignal S:std_logic_vector (1 downto 0); --状态signal DXT:std_logic_vector(7 downto 0):=X"01"; --东西方向时间signal NBX:std_logic_vector(7 downto 0):=X"01"; --南北方向时间signal ART,AGT,AYT,BRT,BGT,BYT: std_logic_vector(7 downto 0); --红绿黄灯信号signal temp: integer range 0 to 49999999; --产生1s计数器时计数signal clk: std_logic;beginART<="00100101";AGT<="00100000";AYT<="00000100";BRT<="00100101";BGT<="00100000";BYT<="00000100";process(clk1k) -- 选频率为50MHZ beginif (clk1k'event and clk1k='1') thenif temp=49999999 thentemp<=0;clk<='1';elsetemp<=temp+1;clk<='0';end if;end if;end process;process(clk,DXT,NBX) --状态转换进程beginif clk'event and clk ='1' thenif(DXT ="00000001")OR (NBX = "00000001") then S<=S+1;else S<=S;end if; --状态转换结束end if;end process;process (clk,SN,S) --倒计时模块beginif SN = '1' then DXT<=DXT; NBX<=NBX;elseif clk'event and clk='1' thenif (DXT="0000000") OR (NBX="00000000") thencase S ISwhen "00"=>DXT<=ART; NBX<=BGT; --南北红灯、东西绿灯when "01"=>NBX<=BYT; --南北红灯、东西黄灯when "10"=>DXT<=AGT; NBX<=BRT; --南北绿灯、东西红灯when "11"=>DXT<=AYT; --南北黄灯、东西红灯when others=>NULL;end case;end if;if DXT/="00000000" thenif DXT(3 downto 0)= "0000" thenDXT(3 downto 0)<="1001";DXT(7 downto 4)<=DXT(7 downto 4)-1;else DXT(3 downto 0)<=DXT(3 downto 0)-1;DXT(7 downto 4)<=DXT(7 downto 4);end if;end if;if NBX/="00000000" thenif NBX(3 downto 0)="0000" thenNBX(3 downto 0)<="1001";NBX(7 downto 4)<=NBX(7 downto 4)-1;else NBX(3 downto 0)<=NBX(3 downto 0)-1;NBX(7 downto 4)<=NBX(7 downto 4);end if;end if;end if;end if;end process; --倒计时模块结束process(DXT,NBX,S,SN) --显示模块begincase NBX(3 downto 0) iswhen "0000"=>led1<="1000000";when "0010"=>led1<="0100100"; when "0011"=>led1<="0110000"; when "0100"=>led1<="0011001"; when "0101"=>led1<="0010010"; when "0110"=>led1<="0000010"; when "0111"=>led1<="1111000"; when "1000"=>led1<="0000000"; when "1001"=>led1<="0010000"; when others=>led1<="1111111"; end case;case NBX(7 downto 4) iswhen "0000"=>led2<="1000000"; when "0001"=>led2<="1111001"; when "0010"=>led2<="0100100"; when "0011"=>led2<="0110000"; when "0100"=>led2<="0011001"; when "0101"=>led2<="0010010"; when "0110"=>led2<="0000010"; when "0111"=>led2<="1111000"; when "1000"=>led2<="0000000"; when "1001"=>led2<="0010000"; when others=>led2<="1111111"; end case;case DXT(3 downto 0) iswhen "0000"=>led3<="1000000"; when "0001"=>led3<="1111001"; when "0010"=>led3<="0100100"; when "0011"=>led3<="0110000"; when "0100"=>led3<="0011001"; when "0101"=>led3<="0010010"; when "0110"=>led3<="0000010"; when "0111"=>led3<="1111000"; when "1000"=>led3<="0000000"; when "1001"=>led3<="0010000"; when others=>led3<="1111111"; end case;case DXT(7 downto 4) iswhen "0000"=>led4<="1000000"; when "0001"=>led4<="1111001"; when "0010"=>led4<="0100100";when "0100"=>led4<="0011001";when "0101"=>led4<="0010010";when "0110"=>led4<="0000010";when "0111"=>led4<="1111000";when "1000"=>led4<="0000000";when "1001"=>led4<="0010000";when others=>led4<="1111111";end case;if SN ='1' then light<="001001";elsecase S ISwhen "00"=>light<="010001";when "01"=> light <="100001";when "10"=> light <="001010";when "11"=> light <="001100";when others=>NULL;end case;end if;end process;end traffic1;五.仿真波形图仿真时序波形图。

EDA大作业

EDA大作业信号发生器的设计要求:(1) 产生方波、三角波、锯齿波、正弦波(2)产生波形的模式可选(3)频率为10KHz设计方案:1.总体设计思路1.1 设计步骤此设计将按模块式实现,据设计要求,设计总共分四大步份完成:(1)产生波形(四种波形:方波、三角波、矩形波和锯齿波)信号;(3)频率为10KHZ幅度固定;1.2设计思想利用VHDL编程,依据基本数字电路模块原理进行整合。

系统各部分所需工作时钟信号由输入系统时钟信号得到。

总体设计框图如下图1所示:波形输出2. 方案论证2.1方案采用VHDL语言来编程,然后下载文件到FPGA来实现。

VHDL语言是电子设计领域的主流硬件描述语言,具有很强的电路描述和建模能力,能从多个层次对数字系统进行建模和描述,从而大大降低了硬件设计任务,提高了设计效率和可靠性,要比模拟电路快得多。

该方案是利用FPGA具有的静态可重复编程和动态在系统重构的特性,使得硬件的功能可以像软件一样通过编程来修改,极大地提高了电子系统设计的灵活性和通用性,设计图如图2。

图2 FPGA总体设计图(需要修改) 通过FPGA软件扫描方式将波形数据读出传输给DAC0832(为8分辨率的D/A转换集成芯片)产生波形输出。

这种方法在软、硬件电路设计上都简单,且与我们的设计思路紧密结合。

㈠3硬件选择4软件设计4.1.1 波形产生模块本设计用VHDL语言根据傅立叶函数采集点进行扫描,分别产生正弦波、三角波和矩形波。

以下介绍各种常用周期信号的傅立叶函数展开式。

4.1.3正弦波(1)设计思想正弦波发生分为两个步骤,即正弦波幅值采样存储和正弦波波形的还原输出。

幅值采样是将一个周期正弦波进行64等分,如图3所示,将64个采样点进行量化处理,量化值=255*sin360/64(V),将64点量化值存入存储器ROM。

正弦波形的产生是通过循环反复将存储器中的64点采样值通过DAC0832进行还原输出,得到幅值正比于64点采样值的正弦波。

EDA大作业2 设计一个循环显示电路

EDA大作业2 设计一个循环显示电路

一、目的

学习使用硬件描述语言设计数字电路方法。

二、任务

在FPGA实验箱上设计一个循环显示电路。

要求:在四位数码管上左移循环显示1, 9, 3, 5, 1, 9, ……;按下复位键后输出显示为0000;按下暂停键后循环停止;使用实验箱上50MHz晶振作为时钟源。

三、内容及步骤

1. 学习用硬件描述语言设计并完成分频功能,建议将50MHz分到5Hz;

2. 学习用状态机设计并完成循环显示功能;

3. 复习用波形仿真检查电路功能是否正确;

4. 使用State Machine Viewer功能观看状态转换图,检查编写的状态机是否正确;(自学,不检查)。

5. 下载到实验箱上验证功能。

四、验收步骤

整个project下载实现全部功能后,才能开始验收。

请同学们首先按以下步骤自查,做的过程中可以答疑,但每人只有一次验收机会。

1. 电路仿真及功能实现;

2. 循环显示电路下载及功能演示;

3. 验收后,上传全部设计文档

StateNumbers:S0:9351 s1:3519 s2:5193 s3:1935 Input : Reset pause clk

Output:Y11~Y0。

(完整word版)EDA计算器设计大作业

计算器设计专业:电子信息工程设计者:本文介绍了一个简单的计算器的设计,该设计采用了现场可编程逻辑器件FPGA设计,并基于VHDL 语言实现加减乘除功能,并用十进制显示在数码管上.系统由计算部分、输入部分、选择部分、输出部分组成,计算部分为加法器、减法器、乘法器和除法器组成.使用Altera公司的QuartusII开发软件进行功能仿真并给出仿真波形,并下载到试验箱,用实验箱上的按键开关模拟输入,用数码管显示十进制计算结果.通过外部按键可以完成四位二进制数的加、减、乘、除四种运算功能,其结果简单,易于实现.关键字:VHDL,计算器,QuartusII一.实验目的 (4)二、流程图 (5)三.顶层原理图 (5)四、各个模块 (7)(1)加法器模块 (7)1、封装元件 (7)2、加法器程序 (7)3、仿真结果 (8)(2)减法器模块 (9)1、封装元件 (9)2、减法器程序 (10)3、仿真结果 (11)4、硬件运行结果 (11)(3)乘法器模块 (12)1、封装元件 (12)2、乘法器的设计思想 (13)3、乘法器程序 (14)4、仿真结果 (14)5、硬件运行结果 (15)(4)除法器模块 (16)1、封装元件 (16)2、除法器设计思想 (16)3、除法器程序 (16)4、仿真结果 (17)5、硬件运行结果 (17)(5)8位除法器 (18)1、封装元件 (18)2、8位除法器设计思想 (19)3、8位除法器程序 (19)4、仿真结果 (22)(6)数码管七段译码电路 (22)1、封装元件 (22)2、共阴极七段显示码十六进制转换表 (23)3、七段译码器程序 (23)4、仿真结果 (24)(7)选择模块 (24)1、封装元件 (24)2、程序 (25)五、管脚锁定 (26)六、小结与收获 (26)一.实验目的1、熟悉QuartusII软件的相关操作,掌握数字电路设计的基本流程.2、介绍QuartusII 的软件,掌握基本的设计思路,软件环境参数配置,仿真,管脚分配,下载等基本操作。

EDA大作业实验程序

实验1--一位全加器的设计======--程序1:或门逻辑描述LIBRARY IEEE ;USE IEEE.STD_LOGIC_1164.ALL; ENTITY or2a ISPORT (a, b :IN STD_LOGIC;c : OUT STD_LOGIC ); END ENTITY or2a;ARCHITECTURE one OF or2a ISBEGINc <= a OR b ;END ARCHITECTURE one;--程序2:半加器描述LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL; ENTITY h_adder ISPORT (a, b : IN STD_LOGIC;co, so : OUT STD_LOGIC);END ENTITY h_adder; ARCHITECTURE fh1 OF h_adder is BEGINso <= NOT(a XOR (NOT b)) ;co <= a AND b ;END ARCHITECTURE fh1;--程序3:1位二进制全加器顶层设计描述LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL; ENTITY f_adder ISPORT (ain,bin,cin : IN STD_LOGIC;cout,sum : OUT STD_LOGIC ); END ENTITY f_adder; ARCHITECTURE fd1 OF f_adder ISCOMPONENT h_adderPORT ( a,b : IN STD_LOGIC;co,so : OUT STD_LOGIC);END COMPONENT ;COMPONENT or2aPORT (a,b : IN STD_LOGIC;c : OUT STD_LOGIC);END COMPONENT;SIGNAL d,e,f : STD_LOGIC;BEGINu1 : h_adder PORT MAP(a=>ain,b=>bin,co=>d,so=>e);u2 : h_adder PORT MAP(a=>e, b=>cin,co=>f,so=>sum);u3 : or2a PORT MAP(a=>d, b=>f,c=>cout); END ARCHITECTURE fd1 ;实验2--原理图输入法设计8位全加器半加器一位的全加器八位的全加器实验3--含异步清0和同步时钟使能的4位加法计数器library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity adder isport(reset:in std_logic;clkin:in std_logic;coutge:out std_logic_vector(3 downto 0);coutshi:out std_logic_vector(3 downto 0)); end adder;architecture shiyan3 of adder issignal temp:std_logic_vector(3 downto 0);signal temp1:std_logic_vector(3 downto 0);beginprocess(clkin,reset)beginif(reset='1') then temp<=(others=>'0');temp1<=(others=>'0');elsif rising_edge(clkin) thenif(temp1>="1001")then temp<=(others=>'0');temp1<=(others=>'0');elsif temp>="1001" thentemp<=(others=>'0');temp1<=temp1+1;elsetemp<=temp+1;end if;end if;coutge<=temp;coutshi<=temp1;end process;end shiyan3;=========LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY CNT10 ISPORT (CLK,RST,EN : IN STD_LOGIC;CQ : OUT STD_LOGIC_VECTOR(3 DOWNTO 0);COUT : OUT STD_LOGIC );END CNT10;ARCHITECTURE behav OF CNT10 ISBEGINPROCESS(CLK, RST, EN)VARIABLE CQI : STD_LOGIC_VECTOR(3 DOWNTO 0);BEGINIF RST = '1' THEN CQI := (OTHERS =>'0') ; --计数器复位ELSIF CLK'EVENT AND CLK='1' THEN --检测时钟上升沿IF EN = '1' THEN --检测是否允许计数IF CQI < "1001" THEN CQI := CQI + 1; --允许计数ELSE CQI := (OTHERS =>'0');--大于9,计数值清零END IF;END IF;END IF;IF CQI = "1001" THEN COUT <= '1'; --计数大于9,输出进位信号ELSE COUT <= '0';END IF;CQ <= CQI; --将计数值向端口输出END PROCESS;END behav;实验4==数控分频器===========LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY PULSE ISPORT(CLK:IN STD_LOGIC;D:IN STD_LOGIC_VECTOR(7 DOWNTO 0);FOUT:OUT STD_LOGIC);END PULSE;ARCHITECTURE one OF PULSE ISSIGNAL FULL :STD_LOGIC;BEGINP_REG:PROCESS(CLK)VARIABLE CNT8:STD_LOGIC_VECTOR(7 DOWNTO 0); BEGINIF CLK'EVENT AND CLK='1'THENIF CNT8="11111111"THENCNT8:=D;FULL<='1';ELSE CNT8:=CNT8+1;FULL<='0';END IF;END IF;END PROCESS P_REG;P_DIV:PROCESS(FULL)VARIABLE CNT2:STD_LOGIC;BEGINIF FULL 'EVENT AND FULL='1'THENCNT2:=NOT CNT2;IF CNT2='1'THEN FOUT<='1';ELSE FOUT <='0';END IF;END IF;END PROCESS P_DIV;END;实验5--用状态机实现序列检测器的设计LIBRARY IEEE ;USE IEEE.STD_LOGIC_1164.ALL;ENTITY SCHK ISPORT( DIN,CLK,CLR : IN STD_LOGIC ; --串行输入数据位/工作时钟/复位信号AB : OUT STD_LOGIC_VECTOR(3 DOWNTO 0)); --检测结果输出END SCHK;ARCHITECTURE behav OF SCHK ISSIGNAL Q : INTEGER RANGE 0 TO 8 ;SIGNAL D : STD_LOGIC_VECTOR(7 DOWNTO 0); --8位待检测预置数BEGIND <="11100101" ; --8位待检测预置数PROCESS( CLK, CLR )BEGINIF CLR = '1' THEN Q <= 0 ;ELSIF CLK'EVENT AND CLK='1' THEN --时钟到来时,判断并处理当前输入的位CASE Q ISWHEN 0=> IF DIN = D(7) THEN Q <= 1 ; ELSE Q <= 0 ; END IF ;WHEN 1=> IF DIN = D(6) THEN Q <= 2 ; ELSE Q <= 0 ; END IF ;WHEN 2=> IF DIN = D(5) THEN Q <= 3 ; ELSE Q <= 0 ; END IF ;WHEN 3=> IF DIN = D(4) THEN Q <= 4 ; ELSE Q <= 0 ; END IF ;WHEN 4=> IF DIN = D(3) THEN Q <= 5 ; ELSE Q <= 0 ; END IF ;WHEN 5=> IF DIN = D(2) THEN Q <= 6 ; ELSE Q <= 0 ; END IF ;WHEN 6=> IF DIN = D(1) THEN Q <= 7 ; ELSE Q <= 0 ; END IF ;WHEN 7=> IF DIN = D(0) THEN Q <= 8 ; ELSE Q <= 0 ; END IF ;WHEN OTHERS => Q <= 0 ;END CASE ;END IF ;END PROCESS ;PROCESS( Q ) --检测结果判断输出BEGINIF Q = 8 THEN AB <= "1010" ; --序列数检测正确,输出"A"ELSE AB <= "1011" ; --序列数检测错误,输出"B"END IF ;END PROCESS ;END behav ;实验6 --用状态机对ADC0809的采样控制电路实现LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY ADCINT ISPORT ( D : IN STD_LOGIC_VECTOR(7 DOWNTO 0); --0809的8位转换数据输出CLK ,EOC : IN STD_LOGIC; --CLK是转换工作时钟LOCK1, ALE, START, OE, ADDA : OUT STD_LOGIC;Q : OUT STD_LOGIC_VECTOR(7 DOWNTO 0) );END ADCINT;ARCHITECTURE behav OF ADCINT ISTYPE states IS (st0, st1, st2, st3,st4,st5,st6) ; --定义各状态子类型SIGNAL current_state, next_state: states :=st0 ;SIGNAL REGL : STD_LOGIC_VECTOR(7 DOWNTO 0);SIGNAL LOCK : STD_LOGIC; -- 转换后数据输出锁存时钟信号BEGINADDA <= '1'; LOCK1 <=LOCK;PRO: PROCESS(current_state,EOC) BEGIN --规定各状态转换方式CASE current_state ISWHEN st0 => ALE<='0';START<='0';OE<='0';LOCK<='0' ;next_state <= st1;WHEN st1 => ALE<='1';START<='0';OE<='0';LOCK<='0' ;next_state <= st2;WHEN st2 => ALE<='0';START<='1';OE<='0';LOCK<='0' ;next_state <= st3;WHEN st3 => ALE<='0';START<='0';OE<='0';LOCK<='0';IF (EOC='1') THEN next_state <= st3; --测试EOC的下降沿ELSE next_state <= st4;END IF ;WHEN st4=> ALE<='0';START<='0';OE<='0';LOCK<='0';IF (EOC='0') THEN next_state <= st4; --测试EOC的上升沿,=1表明转换结束ELSE next_state <= st5; --继续等待END IF ;WHEN st5=> ALE<='0';START<='0';OE<='1';LOCK<='0';next_state <= st6;WHEN st6=> ALE<='0';START<='0';OE<='1';LOCK<='1';next_state <= st0;WHEN OTHERS => ALE<='0';START<='0';OE<='0';LOCK<='0';next_state <= st0;END CASE ;END PROCESS PRO ;PROCESS (CLK)BEGINIF ( CLK'EVENT AND CLK='1') THENcurrent_state <= next_state; -- 在时钟上升沿,转换至下一状态END IF;END PROCESS; -- 由信号current_state将当前状态值带出此进程,进入进程PRO PROCESS (LOCK) -- 此进程中,在LOCK的上升沿,将转换好的数据锁入BEGINIF LOCK='1' AND LOCK'EVENT THEN REGL <= D ;END IF;END PROCESS ;Q <= REGL;END behav;实验7原理图输入设计含LPM的电路实验8 ===循环冗余LIBRARY ieee;USE ieee.std_logic_1164.ALL;USE ieee.std_logic_unsigned.ALL;USE ieee.std_logic_arith.ALL;ENTITY crcm ISPORT (clk : IN std_logic;sdata : IN std_logic_vector(11 DOWNTO 0);datald : IN std_logic;datacrco : OUT std_logic_vector(16 DOWNTO 0);datacrci : IN std_logic_vector(16 DOWNTO 0);rdata : OUT std_logic_vector(11 DOWNTO 0);datafini : OUT std_logic;ERROR0,hsend : OUT std_logic;hrecv : IN std_logic);END crcm;ARCHITECTURE comm OF crcm ISCONSTANT multi_coef : std_logic_vector(5 DOWNTO 0) := "110101";-- 多项式系数, MSB一定为'1'SIGNAL cnt : std_logic_vector(4 DOWNTO 0);SIGNAL dtemp : std_logic_vector(11 DOWNTO 0);SIGNAL sdatam : std_logic_vector(11 DOWNTO 0);SIGNAL rdtemp : std_logic_vector(11 DOWNTO 0);SIGNAL rdatacrc: std_logic_vector(16 DOWNTO 0);SIGNAL rcnt : std_logic_vector(4 DOWNTO 0);SIGNAL st : std_logic;SIGNAL rt : std_logic;BEGINPROCESS(clk)V ARIABLE crcvar : std_logic_vector(5 DOWNTO 0);BEGINIF(clk'event AND clk = '1') THENIF(st = '0' AND datald = '1') THENdtemp <= sdata; sdatam <= sdata;cnt <= (OTHERS => '0');hsend <= '0'; st <= '1';ELSIF(st = '1' AND cnt < 7) THENcnt <= cnt + 1;IF(dtemp(11) = '1') THENcrcvar := dtemp(11 DOWNTO 6) XOR multi_coef;dtemp <= crcvar(4 DOWNTO 0) & dtemp(5 DOWNTO 0) & '0';ELSE dtemp <= dtemp(10 DOWNTO 0) & '0';END IF;ELSIF(st='1' AND cnt =7 ) THENdatacrco <= sdatam & dtemp(11 DOWNTO 7);hsend <= '1'; cnt <= cnt + 1;ELSIF(st = '1' AND cnt = 8) THENhsend <= '0'; st <= '0';END IF;END IF;END PROCESS;PROCESS(hrecv,clk)V ARIABLE rcrcvar : std_logic_vector(5 DOWNTO 0);BEGINIF(clk'event AND clk = '1') THENIF(rt = '0' AND hrecv = '1') THENrdtemp <= datacrci(16 DOWNTO 5);rdatacrc <= datacrci; rcnt <= (OTHERS => '0');ERROR0 <= '0'; rt <= '1';ELSIF(rt= '1' AND rcnt < 7) THENdatafini <= '0'; rcnt <= rcnt + 1;rcrcvar := rdtemp(11 DOWNTO 6) XOR multi_coef;IF(rdtemp(11) = '1') THENrdtemp <= rcrcvar(4 DOWNTO 0) & rdtemp(5 DOWNTO 0) & '0';ELSE rdtemp <= rdtemp(10 DOWNTO 0) & '0';END IF;ELSIF(rt = '1' AND rcnt = 7) THENdatafini <= '1';rdata <= rdatacrc(16 DOWNTO 5);rt <= '0';IF(rdatacrc(4 DOWNTO 0) /= rdtemp(11 DOWNTO 7)) THENERROR0 <= '1';END IF;END IF;END IF;END PROCESS;END comm;下面是根据上面思想写的三分频程序,1/3和50%占空比的程序.library IEEE;use IEEE.STD_LOGIC_1164.ALL;use IEEE.STD_LOGIC_ARITH.ALL;use IEEE.STD_LOGIC_UNSIGNED.ALL;-- Uncomment the following lines to use the declarations that are -- provided for instantiating Xilinx primitive components.--library UNISIM;--use UNISIM.VComponents.all;entity division3 isport (clk: in std_logic;out1: out std_logic);end division3;architecture Behavioral of division3 issignal division2,division4 :std_logic:='0';signal temp1,temp2:integer range 0 to 10;beginp1:process(clk)beginif rising_edge(clk) thentemp1<=temp1+1;if temp1=1 thendivision2<='1';elsif temp1=2 thendivision2<='0';temp1<=0;end if;end if;end process p1;p2:process(clk)beginif clk'event and clk='0' thentemp2<=temp2+1;if temp2=1 thendivision4<='1';elsif temp2=2 thendivision4<='0';temp2<=0;end if;end if;end process p2;p3:process(division2,division4)beginout1<=division2 or division4;end process p3;end Behavioral; (50%)第一章1,什么是EDA 技术?EDA 的英文全称是什么? 答:EDA 技术有狭义和广义之分,狭义EDA 技术就是以大规模可编程逻辑器件为设计载体, 以硬件描述语言为系统逻辑描述的主要表达方式, 以计算机, 大规模可编程逻辑器件的开发软件及实验开发系统为设计工具, 通过有关的开发软件, 自动完成用软件的方式设计的电子系统到硬件系统的逻辑编译,逻辑化简,逻辑分割,逻辑综合及优化,逻辑布局布线,逻辑仿真,直至完成对于特定目标芯片的适配编译,逻辑映射,编程下载等工作,最终形成集成电子系统或专用集成芯片的一门新技术,或称为IES/ASIC 自动设计技术. 2,利用EDA 技术进行电子系统的设计有什么特点? 答: 用软件的方式设计硬件; 用软件方式设计的系统到硬件系统的转换是由有关的开①②发软件自动完成的;③设计过程中可用有关软件进行各种仿真;④系统可现场编程,在线升级;⑤整个系统可集成在一个芯片上,体积小,功耗低,可靠性高. 3,从使用的角度讲,EDA 技术主要包括几个方面的内容? 答:EDA 技术的学习主要应掌握四个方面的内容:①大规模可编程逻辑器件;②硬件描述语言;③软件开发工具;④实验开发系统.其中,硬件描述语言是重点. 4,硬件描述语言VHDL 的特点是什么? 5,什么是综合?有哪些类型?综合在电子设计自己动化地位是什么? 6, 什么是VHDL 语言的自顶向下的设计方法?它与传统的数字逻辑系统设计方法有何不同? 1, 对于目标器件为FPGA/CPLD 的VHDL 设计, 其工程设计包括几个主要步骤?每步的作用是什么?每步的结果是什么? 答:第一:需要进行"源程序的编辑和编译"—用一定的逻辑表达手段将设计表达出来; 第二:要进行"逻辑综合"---将用一定的逻辑表达手段将表达出来的设计经过一系列的操作,分解成一系列的逻辑电路及对应的关系(电路分解); 第三:要进行目标器件的"布线/适配"---在选用的目标器件中建立这些基本逻辑电路的对应关系(逻辑实现) 第四:目标器件的编程下载---将前面的软件设计经过编程变成具体的设计系统(物理实现);最后要进行硬件仿真/硬件测试---验证所设计的系统是否符合要求.同时,在设计过程中要进行有关"仿真"---模拟有关设计结果与设计构想是否相符.设计基本流程如图所示. 2,IP 是什么?IP 与EDA 技术的关系是什么? 第二章1,什么叫可编程逻辑器件(简称PLD) ? FPGA 和CPLD 的中文含意分别是什么?国际上生产FPGA/CPLD 的主流公司,并且在国内占有较大市场份额的主要有哪几家? 目前主要用的产品系列有哪些? 其可用逻辑门/等效门数大约在什么范围? 答:可编程逻辑器件(简称PLD)是一种由用户编程以实现某种逻辑功能的新型逻辑器件. FPGA 和CPLD 分别是现场可编程门阵列和复杂可编程逻辑器件的简称. 国际上生产FPGA/CPLD 的主流公司,并且在国内占有市场份额较大的主要是Xilinx, Altera,Lattice 三家公司. Xilinx 公司的FPGA 器件有XC2000,XC3000,XC4000,XC4000E,XC4000XLA,XC5200 系列等, 可用门数为1200~18 000; Altera 公司的CPLD 器件有FLEX6000, FLEX8000, FLEX10K, FLEX10KE 系列等,提供门数为5000~25 000;Lattice 公司的ISP-PLD 器件有ispLSI1000, ispLSI2000,ispLSI3000,ispLSI6000 系列等,集成度可多达25 000 个PLD 等效门. 2,FPGA 和CPLD 各包括几个基本组成部分? 答:FPGA 在结构上主要分为三个部分,即可编程逻辑单元,可编程输入/输出单元和可编程连线三个部分.CPLD 在结构上主要包括三个部分,即可编程逻辑宏单元,可编程输入/输出单元和可编程内部连线. 第三章1,VHDL 中最基本的结构是什么?其作用各是什么? 答:(1)实体,结构体(2)作用:实体描述电路器件的外部情况几信号端口的基本性质;结构体描述电路器件的内部逻辑功能或电路结构. 2,说明端口模式INOUT 和BUFFER 有何异同点. 答:INOUT 是双向信号,既可输入又可输出.BUFFER 也是实体的输出信号,但作输入用时, 信号不是由外部驱动,而是从反馈得到. 3,表达式C<=A+B 中,A,B 和C 的数据类型都是STD_LOGIC_VECTOR,是否能直接进行加法运算?说明原因和解决办法. 4,VHDL 中有哪三种数据对象?详细说明它们的功能特点及使用方法. 答:在VHDL 中,数据对象(Data Objects)类似于一种容器,它接受不同数据类型的赋值.数据对象有三种,即常量(CONSTANT),变量(VARIABLE)和信号(SIGNAL).前两种可以从传统的计算机高级语言中找到对应的数据类型,其语言行为与高级语言中的变量和常量十分相似. 但信号是具有更多的硬件特征的特殊数据对象,是VHDL 中最有特色的语言要素之一. 1)常量(CONSTANT) 常量代表数字电路中的电源,地,恒定逻辑值等常数;常量的定义和设置主要是为了使设计实体中的常数更容易阅读和修改.例如,将位矢的宽度定义为一个常量,只要修改这个常量就能很容易地改变宽度,从而改变硬件结构.在程序中,常量是一个恒定不变的值,一旦作了数据类型的赋值定义后,在程序中不能再改变,因而具有全局意义. 2)变量(VARIABLE) 变量代表暂存某些值的载体,变量常用在实现某种算法的赋值语句中;在VHDL 语法规则中,变量是一个局部量,只能在进程和子程序中使用.变量不能将信息带出对它作出定义的当前设计单元.变量的赋值是一种理想化的数据传输,是立即发生,不存在任何延时的行为. 3)信号(SIGNAL) 信号代表物理设计中的某一条硬件连接线,包括输入,输出端口.是描述硬件系统的基本数据对象.信号可以作为设计实体中并行语句模块间的信息交流通道.在VHDL 中,信号及其相关的信号赋值语句,决断函数,延时语句等很好地描述了硬件系统的许多基本特征. 如硬件系统运行的并行性;信号传输过程中的惯性延时特性;多驱动源的总线行为等.时序电路中触发器的记忆特性. 信号作为一种数值容器,不但可以容纳当前值,也可以保持历史值.这一属性与触发器的记忆功能有很好的对应关系. 5,常用的VHDL 数据对象有哪些?VHDL 的端口模式包括哪些? 答:常用的VHDL 数据对象有:常数,变量,信号. 端口模式:"IN"" OUT""INOUT""BUFFER". 6,信号与变量的区别有哪些?信号可以用来描述哪些硬件特性? 答:变量赋值与信号赋值的区别在于,变量具有局部特征,它的有效只局限于所定义的一个进程中,或一个子程序中,它是一个局部的,暂时性数据对象(在某些情况下).对于它的赋值是立即发生的(假设进程已启动),即是一种时间延迟为零的赋值行为. 信号则不同, 信号具有全局性特征, 它不但可以作为一个设计实体内部各单元之间数据传送的载体, 而且可通过信号与其他的实体进行通信(端口本质上也是一种信号). 信号的赋值并不是立即发生的,它发生在一个进程结束时.赋值过程总是有某种延时的,它反映了硬件系统并不是立即发生的,它发生在一个进程结束时.赋值过程总是有某些延时的,它反映了硬件系统的重要特性,综合后可以找到与信号对应的硬件结构,如一根传输导线,一个输入/ 输出端口或一个 D 触发器等. 7,名词解释:VHDL,.实体说明,.结构体,类属表,数据对象,并行语句,程序包. 答:1)VHDL(Very high speed intergated circuit Hardware Description Language): 非常高速集成电路的硬件描述语言. 2)实体说明:用来描述电路器件的外部情况及各信号端口的基本性质. 3)结构体:通过若干并行语句来描述设计实体的逻辑功能(行为描述)或内部电路结构(结构描述) ,从而建立设计实体输出与输入之间的关系. 4)类属表:用来确定设计实体中定义的局部常数,用以将信息参数传递到实体,用类属表指明器件的一些特征.最常用的是上升沿和下降沿之类的延迟时间,负载电容,驱动能力和功耗等. 5)数据对象:数据对象是数据类型的载体,共有三种形式的对象:Constant(常量) , Variable(变量) ,Signal(信号) . 6)并行语句:并行语句有五种类型,可以把它们看成结构体的五种子结构.这五种语句结构本身是并行语句,但内部可能含有并行运行的逻辑描述语句或顺序运行的逻辑描述语句,如进程内部包含的即为顺序语句.五种语句结构分别为块语句,进程语句,信号赋值语句,子程序调用语句和元件例化语句. 7)程序包:程序包可定义一些公用的子程序,常量以及自定义数据类型等.各种VHDL 编译系统都含有多个标准程序包, Std-Logic-1164 和Standard 程序包. 如用户也可已自行设计程序包.程序包由两个独立的单元组成:程序包声明单元和程序包体单元构成. 8,元件例化语句的作用是什么? 答:元件例化语句作用:把已经设计好的设计实体称为一个元件或一个模块,它可以被高层次的设计引用.是使VHDL 设计构成自上而下层次设计的重要途径. 9,信号与变量的区别有哪些?信号可以用来描述哪些硬件特性? 答:变量赋值与信号赋值的区别在于,变量具有局部特征,它的有效只局限于所定义的一个进程中,或一个子程序中,它是一个局部的,暂时性数据对象(在某些情况下).对于它的赋值是立即发生的(假设进程已启动),即是一种时间延迟为零的赋值行为. 信号则不同, 信号具有全局性特征, 它不但可以作为一个设计实体内部各单元之间数据传送的载体, 而且可通过信号与其他的实体进行通信(端口本质上也是一种信号). 信号的赋值并不是立即发生的,它发生在一个进程结束时.赋值过程总是有某种延时的,它反映了硬件系统并不是立即发生的,它发生在一个进程结束时.赋值过程总是有某些延时的,它反映了硬件系统的重要特性,综合后可以找到与信号对应的硬件结构,如一根传输导线,一个输入/ 输出端口或一个D 触发器等. 10,什么是并行语句?什么是顺序语句? 答:并行语句主要用来描述模块之间的连接关系,顺序语句一般用来实现模块算法部分. 11,进程语句的特点是什么? 答:进程(PROCESS)语句是最具VHDL 语言特色的语句.因为它提供了一种用算法(顺序语句)描述硬件行为的方法.进程实际上是用顺序语句描述的一种进行过程,也就是说进程用于描述顺序事件. 主要特点有:进程与进程或其它并发语句之间的并发性;进程内部的顺序性;进程的启动于挂起(由敏感信号的变化来启动),并不是任何时候都处于启动状态.:进程与进程或其它并发语句之间的通信. 12,什么是重载运算符?VHDL 的IEEE 库中的哪个程序包预定义了该操作符? 答: 为不同数据类型间的运算带来极大的方便, 通过重新定义运算符的方式, 允许被重载的运算符能够对新的数据类型进行操作, 或者允许不同的数据类型之间用此运算符进行运算.这就是重载运算符.VHDL 的IEEE 库中的STD_LOGIC_UNSIGNED 程序包预定义了该操作符. 13,并行信号赋值语句有哪三种形式?条件信号赋值语句又分别与什么语句等效? 答:简单信号赋值语句,条件信号赋值语句和选择信号赋值语句. 条件信号赋值语句与进程中的多选择IF 语句等价. 14,Case 语句有什么特点?其分支条件使用时有哪些注意事项? 答:CASE 语句根据满足的条件直接选择多项顺序语句中的一项执行.用来描述总线或编码,译码行为.可读性比IF 语句强. 使用CASE 语句需注意以下几点: (1) 条件句中的选择值必须在表达式的取值范围内. (2) 除非所有条件句中的选择值能完整覆盖CASE 语句中表达式的取值,否则最末一个条件句中的选择必须用"OTHERS"表示.它代表已给的所有条件句中未能列出的其他可能的取值,这样可以避免综合器插入不必要的寄存器.这一点对于定义为STD_LOGIC 和STD_LOGIC_VECTOR 数据类型的值尤为重要,因为这些数据对象的取值除了 1 和0 以外,还可能有其他的取值,如高阻态Z,不定态X 等.(3) CASE 语句中每一条件句的选择只能出现一次,不能有相同选择值的条件语句出现.(4) CASE 语句执行中必须选中,且只能选中所列条件语句中的一条.这表明CASE 语句中至少要包含一个条件语句. 15, 元件例化语句的作用是什么?如何进行元件例化?元件例化时端口映射有哪两种方式? 有什么注意事项? 答:把低层次元件安装(调用)到当前层次设计实体内部的过程.包括类属参数传递, 元件端口映射. 例化名称:例化元件名称[GENERIC MAP(类属名称=>表达式{,类属名称=>表达式})] [端口名称=>]表达式--元件端口的映射--类属参数的映射的对应关系{,[端口名称=>]表达式}); 元件例化时端口映射有两种方式: 名称关联方式:低层次端口名=>当前层次端口名,信号名; 位置关联方式:(当前层次端口名,当前层次端口名,…); 第四章1,简述Quartus II 的设计流程. 答:Quartus II 的设计过程包括设计项目的建立与设计的输入,设计编译,设计校验(仿真和定时分析) ,器件编程四个步骤. 设计输入:可以采用原理图输入,HDL 语言描述,及波形输入等几种方式. 设计编译:先根据设计要求设定编译参数和编译策略,如器件的选择,逻辑综合方式的选择等.然后根据设定的参数和策略对设计项目进行网表提取,逻辑综合和器件适配,并产生报告文件,延时信息文件及编程文件,供分析仿真和编程使用. 设计校验(项目仿真) :包括功能仿真,时序仿真和定时分析,可以利用软件的仿真功能来验证设计项目的逻辑功能是否正确. 器件编程与验证:用经过仿真确认后的编程文件通过编程器(Programmer)将设计下载到实际芯片中,最后测试芯片在系统中的实际运行性能. 在设计过程中,如果出现错误,则需重新回到设计输入阶段,改正错误或调整电路后重复上述过程. 或者: 步骤1:建立工作库文件夹; 步骤2:编辑设计文件; 步骤3:存盘,注意实体名与文本取名一致; 步骤4:创建工程; 步骤5:选择目标器件; 步骤6:启动编译; 步骤7:建仿真波形文件; 步骤8:仿真测试和波形分析; 步骤9:引脚锁定并编译; 步骤10:编程下载/配置; 步骤11:硬件测试. 2,设计项目的验证有哪几种方法? 答:包括功能仿真,时序仿真和定时分析. 功能仿真又称前仿真, 是在不考虑器件延时的理想情况下的一种项目验证方法, 通过功能仿真来验证一个项目的逻辑功能是否正确. 时序仿真又称模拟仿真或后仿真, 是在考虑设计项目具体适配器件的各种延时的情况下的一种项目验证方法. 时序仿真不仅测试逻辑功能, 还测试目标器件最差情况下的时间关系. 定时分析可以分析各个信号到输出端的时间延迟,可以给出延迟矩阵和最高工作频率, 还可分析信号的建立,保持时间. 3,什么叫功能仿真?什么叫模拟仿真?两者有什么区别? 答:功能仿真又称前仿真,是在不考虑器件延时的理想情况下的一种项目验证方法,通过功能仿真来验证一个项目的逻辑功能是否正确. 时序仿真又称模拟仿真或后仿真, 是在考虑设计项目具体适配器件的各种延时的情况下的一种项目验证方法. 时序仿真不仅测试逻辑功能,还测试目标器件最差情况下的时间关系. 4,简述层次结构设计的优点. 答:层次化设计是一种模块化的设计方法,设计人员对设计的描述由上至下逐步展开,符合常规的思维习惯; 由于顶层设计与具体的器件和工艺无关, 因此易于在各种可编程逻辑器件中间进行移植. 层次化的设计方法可以使多个设计人员同时进行操作. 有利于对设计任务进行合理的分配并用系统工程的方法对设计进行管理. 5,在数字系统设计中锁定引脚的作用是什么? 答:将设计文件中的输入,输出信号定位到所选器件的具体物理管脚上. 第五章名词解释FPGA EDA SOC FPGA LUT EDA 现场可编程门阵列电子设计自动化单芯片系统现场可编程门阵列查找表电子设计自动化CPLD IP 复杂可编程逻辑器件知识产权核Synthesis 综合LPM VHDL RTL SOPC EAB ASIC RTL 参数可定制宏模块库超高速集成电路硬件描述语言寄存器传输级可编程片上系统嵌入式阵列块专用集成电路寄存器传输级UART 串口(通用异步收发器) ISP IEEE LAB 在系统编程电子电气工程师协会逻辑阵列块。

eda大作业题目 - 副本

参考题目

1、四位数字频率计(结果用四位数码管显示)。

2、字符液晶屏驱动电路(在液晶屏上显示自己的姓名,学号等)。

3、VGA显示器驱动电路(在VGA显示器上显示字符或汉子)。

4、Rs232串行收发电路。

(可与pc机通讯)。

5、简易电子琴。

6、乐曲演奏电路。

7、PS/2键盘按键识别电路。

8、周期测量电路。

9、视频采集电路。

10、I2C通讯电路。

11、8位硬件乘法器。

12、8位硬件除法器。

13、8位有符号数乘法器。

14、ASK调制与解调电路。

15、FSk调制与解调电路。

16、VGA图形显示驱动电路。

17、VGA逻辑分析仪。

18、FPGA中嵌入8051驱动液晶屏电路。

19、NES游戏移植。

20、俄罗斯方块游戏。

注:1以上题目仅供参考,可自行选题,若选择以上题目,每班只能

同时两人选择相同题目,但内容不能相同。

2 报告中应包含以下内容:(1)总体设计说明(2)各模块的设计实现(3)各模块的仿真结果(4)整个设计的仿真或实际结果。

3 设计若包含FPGA以外的电路,应在报告中体现。

4 严禁班与班之间抄袭,所有雷同者均不及格。

5 大作业封面每班要统一格式。

(姓名学号班级不能缺少)。

6 仿真用quartus,或modelsim。

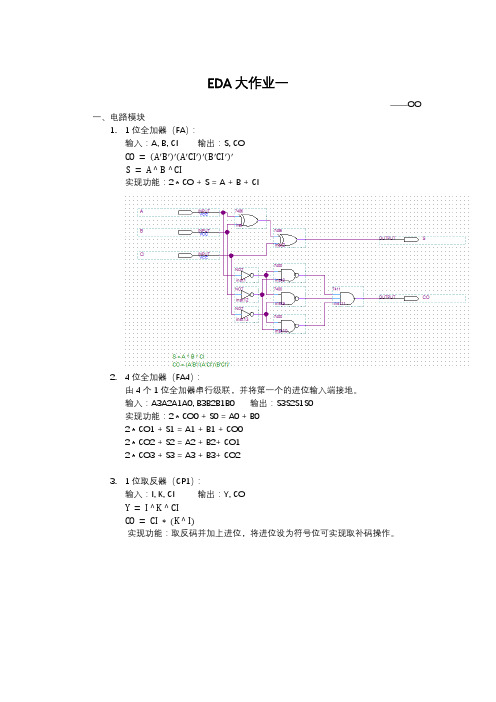

EDA大作业 简易计算器

EDA大作业简易计算器目录EDA大作业简易计算器 (1)目的 (2)任务 (2)内容及步骤 (3)实验设计及实现过程 (3)设计一个1位全加器 (3)设计四位全加器 (4)(1)设计四位加法器 (5)(2)设计可进行加减运算的四位全加器 (6)(3)实现四位全加器的原码输出 (7)设计四位乘法器 (10)(1)设计八位加法器 (10)(2)设计四位乘法器 (11)(3)将乘积结果转化为十进制数 (13)构成简易计算器 (15)下载到实验箱上验证功能 (17)小结与收获 (18)目的1、学习面向可编程器件的FPGA的简单数字系统的设计流程;2、掌握EDA软件Quartus II的原理图输入方式,以及硬件描述语言描述方式;3、熟悉实验装置——实验箱。

任务在可编程逻辑器件上实现一个简易计算器,可以进行4位二进制数的加法和乘法运算,其中被加(乘)数取值范围0~15,加(乘)数取值范围-15~15。

要求用原理图的输入方式及硬件描述语言的结构描述方式完成。

用实验箱上的按键开关模拟输入,用数码管显示十进制计算结果。

内容及步骤1、设计一个1位全加器。

运用波形仿真检查功能正确后,将其封装成1位全加器模块。

2、以1中已封装的1位全加器模块为基础设计一个4位全加器并将其封装成模块,要求:(1) 加数为正时,实现两个4位二进制数与来自低位进位的加法运算,输出显示和及高位进位。

(2) 加数为负时,实现两个4位二进制数的减法运算,输出显示差的原码和正负数标志。

3、以全加器为基础设计一个4位乘法器并封装成乘法器模块,输出显示乘积和正负数标志。

4、以2、3中生成的器件模块为基础构成一个简易计算器,实现如下图功能。

根据S的输入,分别完成Y=A+B或Y=A×B。

5、下载到实验箱上验证功能。

实验设计及实现过程设计一个1位全加器电路图如下:其中A1、B1分别为两个加数,C1为来自低位的进位,S为输出的全加和,C01为向高位的进位。

西电eda大作业

EDA实验报告班级:021211班指导老师:杨明磊实验一:QUARTUS II软件使用及组合电路设计仿真一、实验目的:学习QUARTUS II软件的使用,掌握软件工程的建立、VHDL源文件的设计和波形仿真等基本内容;二、实验内容:1.四选一多路选择器的设计首先利用QuartusⅡ完成4选1多路选择器的文本编辑输入(mux41a.vhd)和仿真测试等步骤,给出仿真波形。

(1)、功能及原理原理:数据选择器又称为多路转换器或多路开关,它是数字系统中常用的一种典型电路。

其主要功能是从多路数据中选择其中一路信号发送出去。

所以它是一个多输入、单输出的组合逻辑电路。

功能:当选择控制端s10=00时,输出ay=;s10=01时,输出by=;s10=10时,输出cy=;s10=11时,输出dy=。

(2)、逻辑器件符号(3)、VHDL语言(4)、波形仿真(5)、仿真分析由波形可知:当s10=00时,y的波形与a相同;当s10=01时,y的波形与b相同;当s10=10时,y的波形与c相同;当s10=11时,y的波形与d相同;与所要实现的功能相符,源程序正确。

2、七段译码器程序设计仿真(1)、功能及原理7段数码是纯组合电路,通常的小规模专用IC,如74或4000系列的器件只能作十进制BCD码译码,然而数字系统中的数据处理和运算都是2进制的,所以输出表达都是16进制的,为了满足16进制数的译码显示,最方便的方法就是利用VHDL译码程序在FPGA或CPLD中实现。

实验中的数码管为共阳极,接有低电平的段发亮。

例如当LED7S输出为 "0010010" 时,数码管的7个段:g、f、e、d、c、b、a分别接0、0、1、0、0、1、0,于是数码管显示“5”。

(2)、逻辑器件符号(3)、VHDL语言(4)、波形仿真(5)、仿真分析由仿真波形可以直观看到,当A=“0000”时,led7s=1000000,数码管显示为0;A=“0001”时,led7s=1111001,数码管显示为1;....依此可验证波形仿真结果完全符合预期,源程序正确。

电子钟设计(EDA大作业)

课程设计(论文)任务书信息工程学院学院通信工程专业2011.1,2,3,4 班一、课程设计(论文)题目电子钟设计二、课程设计(论文)工作自2014 年1月 5 日起至2014年 1月11日止。

三、课程设计(论文) 地点: 华东交通大学4-410,图书馆四、课程设计(论文)内容要求:1.本课程设计的目的(1)掌握EDA技术及CPLD/FPGA的开发流程;(2)掌握自顶向下的设计思想;(3)掌握电子钟的工作原理;(4)掌握系统设计的分析方法;(5)提高学生的科技论文写作能力。

2.课程设计的任务及要求1)基本要求:(1)用HDL设计一个多功能数字钟,包含以下主要功能:精确计时,时间可以24小时制或12小时制显示;(2)日历:显示年月日星期;(3)能用QuartusII软件仿真;(4)把设计文件进行仿真并下载到实验箱实现功能验证。

2)创新要求:在基本要求达到后,可进行创新设计,如增加报时等、秒表功能模块。

3)课程设计论文编写要求(1)要按照书稿的规格打印誊写论文(2)论文包括目录、绪论、正文、小结、参考文献、谢辞、附录等(3)论文装订按学校的统一要求完成4)答辩与评分标准:(1)完成系统分析:30分;(2)完成设计过程:30分;(3)完成仿真:10分;(4)完成下载:10分;(5)回答问题:20分。

5)参考文献:(1)潘松,黄继业编著 .《EDA技术实用教程》,2005 ,科学出版社(2)徐志军,徐光辉编著.《CPLD/FPGA的开发与应用》,电子工业出版社,2001.1(3)/html/85/t-113885.html6)课程设计进度安排内容天数地点构思及收集资料1图书馆设计与调试3实验室撰写论文2图书馆、实验室学生签名:2014 年1 月11 日课程设计(论文)评审意见(1)设计程序(40分):优()、良()、中()、一般()、差();(2)仿真结果(10分):优()、良()、中()、一般()、差();(3)下载结果(10分):优()、良()、中()、一般()、差();(4)回答问题(10分):优()、良()、中()、一般()、差();(5)报告成绩(30分):优()、良()、中()、一般()、差();(6)格式规范性及考勤是否降等级:是()、否()评阅人:朱路职称:副教授2014 年1 月12 日o目录目录 (3)绪论 (4)第一章总体设计 (5)一、功能概述 (5)二、引脚功能 (5)1、时钟输入 (5)2、时分秒或年月日输入 (5)3、清零输入 (5)4、整点报时闹铃开关输入 (5)5、时间显示模式开关输入 (5)6、上午下午状态输出 (6)7、时分秒、年月日、秒表显示输出 (6)8、整点报时、闹铃声音输出 (6)第二章模块分析 (4)一、时间显示及时间修改模块 (4)1、TIME子模块介绍(实现功能程序代码见附录I) (6)2、调秒功能实现分析 (6)二、日历显示及日历设置模块 (7)三、秒表模块 (9)四、闹铃设置模块 (10)五、整点报时及闹铃使能模块 (11)六、功能切换及显示切换模块 (12)1、显示切换模块 (12)2、功能切换模块 (13)七、各模块的整合 (14)第三章硬件测试结果 (15)小结 (16)谢辞 (16)参考文献 (16)附录 (17)绪论本次课程设计主要介绍VHDL电子时钟的设计方法,采用的软件是MAX PLUS II。

EDA技术课程大作业

2。

篇幅在3000-4000字

3.系统中要求有硬件框图、软件框图、EDA片内框图

题目A:2005年全国大学生电子设计竞赛试题A题。

要求产生的信号源用DDS方式使用FPGA芯片来产生。

题目B:基于FPGA的步进电机细分控制器的设计

要求使用FPGA芯片来产生步进电机细分控制器所需要的PWM信号;步进电机(6相,每相的电流为4A,工作电压为50V)的驱动电路;总的系统硬件图。

题目C:视频信号采集系统的设计

1.视频信号的规格为VCD像素数为352X288 ( PAL 制

式)

2.视频信号的采样精度为8bit,采样深度50帧。

题目D:高速公路车辆超速监测系统的设计

1.汽车的速度上限为120/小时。

2.采用FPGA芯片作为主控器件来测速。

简易无线供电系统

数字式电参数测量仪。

数电EDA大作业一报告

将3个CP1串行级联,并将第一个的进位输入端接符号位。

实现功能:求补码

5.简易3-1选择器(3_1selector):

输入:选择端S2S1S0,数位I2I1I0输出:Y

约束条件:

实现功能:选通一个输入端。

6.简易2-4译码器(2_4decoder):

实现功能:通过拨码开关或者接入两列方波序列让加数和结果分别显示在数码管上。

二、设计思路

1.注意到两个带符号位的四位二进制数时,需要先把二进制数的补数相加再取补数,所以做三个补码器和一个全加器组合,进而完成运算器。

2.对于带符号位的三位二进制数,可以扩展成四位,即把M, N扩展成A3A2A1A0形式,其中,A3为符号位,A2补0,A1A0与原M、N的最后两位相同。

2.全加器和运算器的设计基本没有遇到设计上的问题,因为电子技术实验三组合电路有设计过类似电路。

3.设计分频器时,遇到的问题是在quartus ii中不能直接添加时钟,最后查看FPGA使用说明才知道用晶振产生时钟信号。

4.分频器接入电路后出现错位重影的问题,分析是竞争冒险的问题,所以继续分频,直到能准确显示为止(31.25Hz)。

8.同步十进制加法器(SDAC):

实现功能:产生占空比为1/10的方波。

9.降200k分频器(FD200k):

用5个SDAC串联,最后接上一个T触发器,并使T为1或T与CLK相接。

实现功能:将频率降低200k,如将50MHz降为250Hz。

10.扫描显示电路(show):

用2-4译码器、3-1选择器、运算器、7447译码器等组合成扫描显示电路。

A模块:

分别输出31.25Hz和5Hz的时钟信号。

EDA大作业

EDA技术课程大作业设计题目:移位相加8位硬件乘法器的设计学生姓名:曲毅学号:0990*******专业班级:通信1101移位相加8位硬件乘法器电路设计1. 设计背景和设计方案1.1设计背景纯组合逻辑构成的乘法器虽然工作速度比较快,但过于占用硬件资源,难以实现多位乘法器,基于PLD器件外接ROM九九表的乘法器则无法构成单片系统,也不实用。

这里介绍由八位加法器构成的以时序逻辑方式设计的八位乘法器,具有一定的实用价值,而且由FPGA构成实验系统后,可以很容易的用ASIC大型集成芯片来完成,性价比高,可操作性强。

1.2设计方案此设计是由八位加法器构成的以时序逻辑方式设计的八位乘法器,它的核心器件是八加法器。

所以关键是设计好八位加法器方案一八位直接宽位加法器,它的速度较快,但十分耗费硬件资源,对于工业化设计是不合理的方案二:由两个四位加法器组合八位加法器,其中四位加法器是四位二进制并行加法器它的原理简单,资源利用率和进位速度方面都比较好。

综合各方面的考虑,决定采用方案二。

由8位加法器构成的以时序逻辑方式设计的8位乘法器乘法通过逐向移位加原理来实现,从被乘数的最低位开始,若为1,则乘数左移与上一次和相加;若为0,左移后以全零相加,直至被乘数的最高位。

本乘法器结构框图如下:图1 基本结构框图本乘法器原理图如图2所示:由五个模块组成。

其中ARICTL是乘法运算控制电路,它的START信号上的上跳沿与高电平有2个功能,即16位寄存器清零和被乘数A[7..0]]向移位寄存器SREG8B加载;它的低电平则作为乘法使能信号,乘法时钟信号从ARICTL的CLK 输入。

当被乘数被加载于8位右移寄存器SREG8B后,随着每一时钟节拍,最低位在前,由低位至高位逐位移出。

当为1时:一位乘法器ANDARITH打开,8位乘数B[7..0]在同一节拍进入8位加法器,与上一次锁存在16位锁存器REG16B中的高8位进行相加,其和在下一时钟节拍的上升沿被锁进此锁存器。

EDA大作业~~~~彩灯设计,《彩灯控制器》济南大学 EDA

电子设计自动化大作业题目彩灯控制器学院班级 xxxxxxx姓名 xxxxxx学号 xxxxxxxxxxx二O一二年十月三十一日题目:彩灯控制器一、设计要求:设计能让一排彩灯(8只)自动改变显示花样的控制系统,发光二极管可作为彩灯用。

控制器应有两种控制方式:(1)规则变化。

变化节拍有0.5秒和0.x秒两种,交替出现,每种节拍可有4种花样,各执行一或二个周期后轮换。

(2)随机变化。

无规律任意变化。

二、总体设计:1、总体结构图前端控制(外部端口示意图、总体结构图)2、各模块功能三、单元模块设计每个模块含有以下内容:1、模块名(1)模块功能1.分频器a.功能:实现4096分频且占空比为50%b.功能:当clkd为1时实现512分频,clkd为0时输出为0。

c.功能:当clkd为0时实现256分频,clkd为1时输出为0。

2.前端控制功能:当k为0时总输出clk,k为1时总输出为序列码11010110。

3.模8计数器功能:当clr为0时输出为“000”,当clr为1时为模8计数器输出三位二进制数。

(2)VHDL源程序VHDL代码:library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity deng isport(clk: in std_logic;clr: in std_logic;choose: in std_logic_vector(2 downto 0);led: out std_logic_vector(7 downto 0));end deng;architecture control of deng issignal cnt1:std_logic_vector(1 downto 0); signal cnt2:std_logic_vector(1 downto 0); signal cnt3:std_logic_vector(1 downto 0); signal cnt4:std_logic_vector(1 downto 0); signal cnt5:std_logic_vector(1 downto 0); signal cnt6:std_logic_vector(1 downto 0); signal cnt7:std_logic_vector(1 downto 0); signal cnt8:std_logic_vector(1 downto 0);beginprocess(clk,clr)beginif clr='0'thenled<="00000000";elseif choose="000" thenif clk'event and clk='0' thencnt1<=cnt1+1;end if;case cnt1 iswhen "00"=>led<="10000000";when "01"=>led<="01000000";when "10"=>led<="00100000";when "11"=>led<="00010000";end case;elsif choose="001" thenif clk'event and clk='1' thencnt2<=cnt2+1;end if;case cnt2 iswhen "00"=>led<="00000001";when "01"=>led<="00000010";when "10"=>led<="00000100";when "11"=>led<="00001000"; end case;elsif choose="010" thenif clk'event and clk='1' then cnt3<=cnt3+1;end if;case cnt3 iswhen "00"=>led<="10000000";when "01"=>led<="00100000";when "10"=>led<="00001000";when "11"=>led<="00000010";end case;elsif choose="011" thenif clk'event and clk='1' thencnt4<=cnt4+1;end if;case cnt4 iswhen "00"=>led<="00000001";when "01"=>led<="00000100";when "10"=>led<="00010000";when "11"=>led<="01000000"; end case;elsif choose="100" thenif clk'event and clk='0' thencnt5<=cnt5+1;end if;case cnt5 iswhen "00"=>led<="10000001";when "01"=>led<="11000011";when "10"=>led<="11100111";when "11"=>led<="11111111"; end case;elsif choose="101" thenif clk'event and clk='1' thencnt6<=cnt6+1;end if;case cnt6 iswhen "00"=>led<="01111110";when "01"=>led<="00111100";when "10"=>led<="00011000";when "11"=>led<="00000000"; end case;elsif choose="110" thenif clk'event and clk='1' thencnt7<=cnt7+1;end if;case cnt7 iswhen "00"=>led<="11000000";when "01"=>led<="00110000";when "10"=>led<="00001100";when "11"=>led<="00000011"; end case;elsif choose="111" thenif clk'event and clk='1' thencnt8<=cnt8+1;end if;case cnt8 iswhen "00"=>led<="10000001";when "01"=>led<="01000010";when "10"=>led<="00100100";when "11"=>led<="00011000";end case;end if;end if;end process;end architecture control;输入choose为“000”时的仿真波形:结果分析:设置choose为“000”,当clr=1时led7~led4每过一个时钟变为高电平其余时间为低电平,led3~led0为低电平,当clr=0时输出全部为0。

EDA大作业要求

《EDA技术》课程大作业要求项目一、自选一模拟电路(如功放电路),画出仿真电路图(包含虚拟仪器),并对该电路作仿真分析。

要求:1. 仿真电路图、仿真分析过程和结果以截图的形式表达。

2. 六种仿真分析方法中,选三种(必包含参数扫描分析)对电路分析。

3. 仿真结果中包含利用虚拟仪器检测的结果。

4. 对理论分析结果与仿真分析结果要作比较分析。

项目二、设计一8S循环的交通灯控制器(以74LS160D为核心,能读秒)。

要求:1.有简单的设计思路分析。

2.设计步骤明确并得到电原理图,并作仿真分析及说明。

3.用逻辑分析仪输出波形。

4.进阶任务:设计一60S循环的交通灯控制器(本任务可选择30s或60s)大作业文本打印格式要求:1.打印文稿用A4格式排版。

2.行距、字距以美观大方为宜。

3.一级标题用4号宋体、加粗,二级标题用5号宋体、加粗,正文用5号宋体。

4.图、表要有标注、编号(小5号宋体)。

5.封面格式见附页。

上交材料:1.项目设计报告一份(纸质)2.项目设计报告电子稿3.项目设计成果电子档注:电子文档存于以姓名学号为名的文件夹统一上交。

《EDA技术》课程大作业项目名称:实用电路仿真分析设计专业班级:学号:姓名:连云港职业技术学院信息工程学院年月日内容安排参考项目一:项目名称:xxxxxxxxxxxxxxxxx项目要求:1. xxxxxxxxxxxxx2. xxxxxxxxxxxxx项目设计准备分析:1. 2. 3.-------- 项目设计步骤:1. 2. 3.--------项目仿真结果及分析:xxxxxxxxxxxx------------项目二:(最后)课程学习心得()。

EDA应用大作业《串行通信》

四川工程职业技术学院电子信息工程09-1班《EDA应用》大作业串行通信第3组:杨国勋、李开宏、彭国明2011.10目录一、设计任务 (1)二、硬件设计 (1)1、硬件电路图 (1)2、整体模块 (2)三、软件设计 (2)1、主程序模块 (2)2、发送模块 (5)3、接收模块 (7)四、实验结果 (9)五、开发工具 (10)1、硬件 (10)2、软件 (10)六、项目总结 (10)1、遇到的问题 (10)2、解决的办法 (10)七、参考文献 (10)一、设计任务综合运用所学基本知识,通过在FPGA开发板子完成与计算机进行RS232串口通信,计算机上的软件可以使用串口通信调试软件进行数据发送或接收数据。

根据设计要求,应把系统分成4个模块来完成,这四个模块分别是:时钟模块(向系统各部分提供各种频率的时钟信号)收发模块(进行串行通信的发送和接收)显示模块(显示通信的数据格式)控制模块(控制系统的工作)二、硬件设计1、硬件电路图2、整体模块三、软件设计1、主程序模块module uart_test(clock,key,rdata,wen,sdata,seg,dig);input clock; //系统时钟(48MHz) input[2:0] key; //按键输入(KEY1~KEY3) input[7:0]rdata; //接收到的数据output wen; //发送数据使能output[7:0]sdata; //要发送的数据output[7:0]seg; //数码管段码输出output[7:0]dig; //数码管位码输出//I/O寄存器reg[7:0]sdata;reg[7:0]seg;reg[7:0]dig;//内部寄存器reg[16:0]count; //时钟分频计数器reg[2:0]dout1,dout2,dout3,buff; //消抖寄存器reg[1:0] cnt; //数码管扫描计数器reg[3:0]disp_dat; //数码管扫描显存reg div_clk; //分频时钟wire[2:0]key_edge; //按键消抖输出//时钟分频部分always @(posedge clock)beginif (count < 17'd120000)begincount <= count + 1'b1;div_clk <= 1'b0;endelsebegincount <= 17'd0;div_clk <= 1'b1;endend//按键消抖部分always @(posedge clock)beginif(div_clk)begindout1 <= key;dout2 <= dout1;dout3 <= dout2;endend//按键边沿检测部分always @(posedge clock)beginbuff <= dout1 | dout2 | dout3;endassign key_edge = ~(dout1 | dout2 | dout3) & buff;//2位16进制数输出部分always @(posedge clock) //按键1 beginif(key_edge[0])sdata[7:4] <= sdata[7:4] + 1'b1;endalways @(posedge clock) //按键2beginif(key_edge[1])sdata[3:0] <= sdata[3:0] + 1'b1;endassign wen = key_edge[2]; //按键3//数码管扫描显示部分always @(posedge clock) //定义上升沿触发进程beginif(div_clk)cnt <= cnt + 1'b1;endalways @(posedge clock)beginif(div_clk)begincase(cnt) //选择扫描显示数据2'd0:disp_dat = sdata[7:4]; //第一个数码管2'd1:disp_dat = sdata[3:0]; //第二个数码管2'd2:disp_dat = rdata[7:4]; //第七个数码管2'd3:disp_dat = rdata[3:0]; //第八个数码管endcasecase(cnt) //选择数码管显示位2'd0:dig = 8'b01111111; //选择第一个数码管显示2'd1:dig = 8'b10111111; //选择第二个数码管显示2'd2:dig = 8'b11111101; //选择第七个数码管显示2'd3:dig = 8'b11111110; //选择第八个数码管显示endcaseendendalways @(disp_dat)begincase(disp_dat) //七段译码4'h0:seg = 8'hc0; //显示04'h1:seg = 8'hf9; //显示14'h2:seg = 8'ha4; //显示24'h3:seg = 8'hb0; //显示34'h4:seg = 8'h99; //显示44'h5:seg = 8'h92; //显示54'h6:seg = 8'h82; //显示64'h7:seg = 8'hf8; //显示74'h8:seg = 8'h80; //显示84'h9:seg = 8'h90; //显示94'ha:seg = 8'h88; //显示a4'hb:seg = 8'h83; //显示b4'hc:seg = 8'hc6; //显示c4'hd:seg = 8'ha1; //显示d4'he:seg = 8'h86; //显示e4'hf:seg = 8'h8e; //显示f endcaseendendmodule2、发送模块module send(clk,clkout,Datain,TXD,TI,WR);input WR;input [7:0]Datain; //发送的一字节数据input clk;output clkout;output TXD,TI; //串行数据,发送中断reg[9:0]Datainbuf,Datainbuf2; //发送数据缓存reg WR_ctr,TI,txd_reg;reg [3:0]bincnt; //发送数据计数器reg [15:0] cnt;wire clk_equ;parameter cout = 5000;/*************波特率发生进程****************************/ always@(posedge clk)beginif(clk_equ)cnt = 16'd0;elsecnt=cnt+1'b1;endassign clk_equ = (cnt == cout);assign clkout = clk_equ;/*************读数据到缓存进程****************************/ always@(posedge clk)beginif(WR)beginDatainbuf={1'b1,Datain[7:0],1'b0};//读入数据,并把缓存组成一帧数据,10位WR_ctr = 1'b1; //置开始标志位endelse if(TI==0)WR_ctr = 1'b0;end/*************主程序进程****************************/ always@(posedge clk)beginif(clk_equ)beginif(WR_ctr==1||bincnt<4'd10) //发送条件判断,保证发送数据的完整性beginif(bincnt<4'd10)begintxd_reg = Datainbuf2[0]; //从最低位开始发送Datainbuf2 = Datainbuf>>bincnt; //移位输出bincnt = bincnt+4'd1; //发送数据位计数TI = 1'b0;endelsebincnt = 4'd0;endelsebegin //发送完毕或者处于等待状态时TXD和TI为高txd_reg = 1'b1;TI = 1'b1;endendendassign TXD = txd_reg; //TXD连续输出endmodule3、接收模块module rec(clk,clkout,Dataout,RXD,RI);input clk,RXD;output clkout,RI;output [7:0] Dataout; //并行数据输出reg StartF,RI;reg [9:0] UartBuff; //接收缓存区reg [3:0]count,count_bit;reg [15:0] cnt;reg [2:0]bit_collect; //采集数据缓存区wire clk_equ,bit1,bit2,bit3,bit;parameter cout = 312;//时钟是48M所以16*9600的分频数为312.5,这里取整数/*************波特率发生进程****************************/ always@(posedge clk)beginif(clk_equ)cnt = 16'd0;elsecnt=cnt+1'b1;endassign clk_equ = (cnt == cout);assign clkout = clk_equ;assign bit1 = bit_collect[0]&bit_collect[1]; assign bit2 = bit_collect[1]&bit_collect[2]; assign bit3 = bit_collect[0]&bit_collect[2]; assign bit = bit1|bit2|bit3;always@(posedge clk)beginif(clk_equ)beginif(!StartF) //是否处于接收状态beginif(!RXD)begincount = 4'b0; //复位计数器count_bit = 4'b0;RI = 1'b0;StartF = 1'b1;endelse RI = 1'b1;endelsebegincount = count+1'b1; //位接收状态加1if(count==4'd6)bit_collect[0] = RXD; //数据采集if(count==4'd7)bit_collect[1] = RXD; //数据采集if(count==4'd8)beginbit_collect[2] = RXD; //数据采集UartBuff[count_bit] = bit;count_bit = count_bit+1'b1;//位计数器加1if((count_bit==4'd1)&&(UartBuff[0]==1'b1))//判断开始位是否为0beginStartF = 1'b0; //标志开始接收endRI = 1'b0; //中断标志位低endif(count_bit>4'd9) //检测是否接收结束beginRI = 1'b1; //中断标志为高标志转换结束StartF = 1'b0;endendendendassign Dataout = UartBuff[8:1]; //取出数据位endmodule四、实验结果(1) 在工作状态下,若用户按下K1按键,则数码管1上的数字加 1(0~F循环);(2) 在工作状态下,若用户按下K2按键,则数码管2上的数字加 1(0~F循环);(3) 在工作状态下,若用户按下K3按键,则把数码管1和2上的数字通过串口发送到串口调试软件的接收窗口;(4) 在工作状态下,若用户通过串口调试软件在发送窗口发送数字,则在数码管7和8上显示相应的数字。

eda大作业

班级021039学号02103121EDA报告题目VHDL 设计初步 ________________ 学院_________________ 电子工程学院___________________ 专业_________________ 信息对抗技术___________________ 学生姓名 ___________________________________________ 导师姓名目录第一章实验部分(秒表) (2)1、...................................................................... 程序设计: 22、....................................................................... 程序代码23、....................................................................... 程序调试4第二章习题部分 (8)习题一 (8)习题二 (8)习题三 (10)习题四 (11)习题五 (12)习题六 (14)习题七 (17)第一章实验部分(秒表)1、程序设计:秒表显示共有6位,两位显示分,两位显示秒,十分秒和百分秒各一位。

设计时使用一个计数器,随着时钟上升沿的到来循环计数,每计数一次,百分秒位加一,通过百分秒位满十进位来控制十分位的计数,十分位满十进位,依次类推,实现秒表计数。

为实现秒位的计时精确,百秒位必须以0.01秒的时间间隔计数,即时钟的频率是100Hz为此,本设计采用3MHz的时钟频率通过分频得到100Hz的时钟频率,再送给控制时钟以得到比较精确的CLK信号。

其中,时钟信号CLK为3MHz 的时钟频率,分频后得到的时钟为CLK2输出引脚CLK2和输入引脚CLK2在外部相连,实现将分频后的时钟送入。

EDA技术课程大作业

E D A技术课程大作业-标准化文件发布号:(9456-EUATWK-MWUB-WUNN-INNUL-DDQTY-KII安阳工学院电子信息与电气工程学院课程大作业:EDA技术题目:组数:第 11 组班级:(电子信息工程10-1)教师成绩由以下评分标准累计得出1、电路设计和仿真结果正确清晰合理‘ 25%2、设计和仿真结果分析正确合理。

25%3、大作业报告重点突出、阐述清晰。

25%4、小组能很好的组织、合作,过程顺利,按时完成大作业。

15%5、陈述清晰正确、有说服力,能够正确回答问题。

10%总分学生自评分值大作业总成绩总成绩=J*60%+(J+J*(X-25%))*40% J 为教师成绩,X 为学生自评分值数字时钟1. 设计任务和设计方案1.1设计任务1、依据预先设定的数字数字时钟的功能,完成对数字钟的设计。

2、通过数字时钟的设计,学习Quartus II 中基于VHDL 设计的流程。

3、通过这次的设计,掌握简单时序逻辑电路的设计方法与功能仿真技巧。

1.2 设计方案在方案中要实现的功能是:(1)设置复位、清零等功能(2)有时、分、秒计数显示功能,小时为24进制,分钟和秒为60进制以24小时循环计时(3)有校时功能,可以分别对时及分进行单独校时,使其校正到标准时间 (4)时钟通过数码管显示且时钟计数显示时有LED 灯显示; 总体方框图2. 方案实施根据系统设计要求,系统由时钟分频部分、计时部分、按键部分调时部分和显示部分五个部分组成。

这些模块都放在一个顶层文件中。

1)时钟计数:思路:时计时器为一个24进制计数器,分、秒计时器均为60进制计数器。

当秒计时器接受到一个秒脉冲时,秒计数器开始从1计数到60,此时秒显示器将显示00、01、02、...、59、00;每当秒计数器数到00时,就会产生一个脉冲输出送至分计时器,此时分计数器数值在原有基础上加1,其显示器将显示00、01、02、 (59)00;每当分计数器数到00时,就会产生一个脉冲输出送至时计时器,此时时计数器数值在原有基础上加1,其显示器将显示00、01、02、...、23、00。

EDA大作业

EDA技术课程大作业目录1. 设计背景2. 设计方案2.1 计时模块功能2.2 计时模块系统组成框图2.3 设计思路3. 数字秒表计时模块的VHDL源程序3.1 十进制计数器的VHDL源程序(CDU10.VHD)3.2 六进制计数器的VHDL源程序(CDU6.VHD)3.3 计时器的VHDL源程序(COUNT.VHD)4. 源程序总体描述5. 波形仿真图6. 总结1、设计背景在当今社会,数字电路产品的应用在我们的实际生活中显得越来越重要,与我们的生活联系愈加紧密,例如计算机、仪表、电子钟等等,使我们的生活工作较以前的方式更加方便、完善,带来了很多的益处。

在此次EDA课程,我的设计课题是数字秒表——计时模块,根据要求使用平时所学VHDL语言进行编程完成。

报告书主要由设计背景、设计方案、模块介绍、设计源程序、仿真波形图和管脚锁定及硬件连线四部分组成。

设计方案主要介绍了我对于设计课题的大致设计思路,之后各个部分将会详细介绍设计组成及程序。

数字电路主要是基于两个信号,用数字信号完成对数字量进行算术运算和逻辑运算的电路我们称之为数字电路,它具有逻辑运算和逻辑处理等功能,数字电路可分为组合逻辑电路和时序逻辑电路。

EDA技术,就是以大规模可编程逻辑器件为设计载体,以硬件描述语言为系统逻辑描述的主要表达方式,以计算机、大规模可编程逻辑器件的开发软件及实验开发系统为设计工具,通过有关的开发软件,自动完成用软件的方式设计的电子系统到硬件系统的逻辑编译、逻辑化简、逻辑分割、逻辑综合及优化、逻辑布局布线、逻辑仿真,直至完成对于特定目标芯片的适配编译、逻辑映射、编程下载等工作,最终形成集成电子系统或专用集成芯片的一门新技术。

2、设计方案数字秒表的计时模块,其总体功能如下:数字秒表的计时范围是0秒到59分59.59秒,显示的最长时间为59分59。

数字秒表的计时精度是10ms。

复位开关可以在任何情况下使用,即便在计时过程中,只要按一下复位开关,计时器就清零,并做好下次计时的准备。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

信号发生器的设计要求:(1) 产生方波、三角波、锯齿波、正弦波(2)产生波形的模式可选(3)频率为10KHz设计方案:1.总体设计思路1.1 设计步骤此设计将按模块式实现,据设计要求,设计总共分四大步份完成:(1)产生波形(四种波形:方波、三角波、矩形波和锯齿波)信号;(3)频率为10KHZ 幅度固定;1.2设计思想利用VHDL编程,依据基本数字电路模块原理进行整合。

系统各部分所需工作时钟信号由输入系统时钟信号得到。

总体设计框图如下图1所示:波形输出2. 方案论证2.1方案采用VHDL 语言来编程,然后下载文件到FPGA 来实现。

VHDL 语言是电子设计领域的主流硬件描述语言,具有很强的电路描述和建模能力,能从多个层次对数字系统进行建模和描述,从而大大降低了硬件设计任务,提高了设计效率和可靠性,要比模拟电路快得多。

该方案是利用FPGA 具有的静态可重复编程和动态在系统重构的特性,使得硬件的功能可以像软件一样通过编程来修改,极大地提高了电子系统设计的灵活性和通用性,设计图如图2。

图2 FPGA 总体设计图 (需要修改)通过FPGA 软件扫描方式将波形数据读出传输给DAC0832(为8分辨率的D/A 转换集成芯片㈠)产生波形输出。

这种方法在软、硬件电路设计上都简单,且与我们的设计思路紧密结合。

3硬件选择4软件设计4.1.1 波形产生模块本设计用VHDL 语言根据傅立叶函数采集点进行扫描,分别产生正弦波、三角波和矩形波。

以下介绍各种常用周期信号的傅立叶函数展开式。

4.1.3正弦波(1)设计思想正弦波发生分为两个步骤,即正弦波幅值采样存储和正弦波波形的还原输出。

幅值采样是将一个周期正弦波进行64等分,如图3所示,将64个采样点进行量化处理,量化值=255*sin360o/64(V ),将64点量化值存入存储器ROM 。

正弦波形的产生是通过循环反复将存储器中的64点采样值通过DAC0832进行还原输出,得到幅值正比于64点采样值的正弦波。

t(2)VHDL 实现1.正弦信号波形数据文件建立正弦波波形数据由64个点构成,此数据经DAC0832,可在示波器上观察到正弦波形。

源程序见附录: 4.1.2 矩形波1设计思路矩形波的实现较之正弦波发生简单,由于矩形波是两个电平值间的交替变换,因此波形采样值的预存只要有两个不同的数值就行了,为了使矩形波发生的频率灵活可调,采用60个采样值扫描输出来实现,每半个矩形波周期采用三十个采样值,循环反复将存储器中的60点采样值通过DAC0832进行还原输出,得到幅值正比于点采样值的矩形波。

采样图如图4所示。

2 VHDL 实现 源程序见附录。

4.1.3 三角波1设计思路由于三角波是线性的,比较简单就可以产生,如果最低电压设为15V ,最高是255V ,那么根据它的公式255/15=17,每个点的电压只要依次加17就可以得到,一个波形所以采用简单的加减算法就可实现,如图5所示三角波的采样图:图5 三角波采样图2 VHDL实现具体源程序见附录。

4.1.4 基波通过VHDL编程产生的正弦波、方波、三角波三种周期性波形即为基波。

4.1.5谐波的产生采用与基波产生的同样原理,编程产生三种波形的谐波,所不同的是一个波形的周期采样的点数不同,如果基波采样点为63个,谐波采样点数则为21个,其每点的电压值为255*(sin360/60+sin360/20)(V),在对其进行循环扫描即可实现基波与谐波的线性叠加。

4.1.6 波形模块图最终波形的设计模块图如图6所示,L1是三角波,L2是方波,L3是正弦波,L4是谐波。

4.2 频率控制模块本课题要求频率控制是在10KHZ。

在本题设计中只需借助FPGA便可完成。

如下图7所示:4.3 选择波形模块这一部分主要是通过一个按键对波形进行循环选择,按下确认按钮后进行波形的调用。

设计流程图如下图7所示图6 波形模块图图7 选择波形电路设计流程图【实验9】波形发生与扫频信号发生器电路设计1、实验目的:学习用VHDL设计波形发生器和扫频信号发生器,掌握FPGA对D/A的接口和控制技术,学会LPM_ROM在波形发生器设计中的实用方法。

2、实验原理:如实验图5所示,完整的波形发生器由4部分组成:∙ FPGA中的波形发生器控制电路,它通过外来控制信号和高速时钟信号,向波形数据ROM发出地址信号,输出波形的频率由发出的地址信号的速度决定;当以固定频率扫描输出地址时,模拟输出波形是固定频率,而当以周期性时变方式扫描输出地址时,则模拟输出波形为扫频信号。

∙波形数据ROM中存有发生器的波形数据,如正弦波或三角波数据。

当接受来自FPGA 的地址信号后,将从数据线输出相应的波形数据,地址变化得越快,则输出数据的速度越快,从而使D/A输出的模拟信号的变化速度越快。

波形数据ROM可以由多种方式实现,如在FPGA 外面外接普通ROM;由逻辑方式在FPGA中实现(如例6);或由FPGA中的EAB模块担当,如利用LPM_ROM实现。

相比之下,第1种方式的容量最大,但速度最慢;,第2种方式容量最小,但速度最最快;第3种方式则兼顾了两方面的因素;∙D/A转换器负责将ROM输出的数据转换成模拟信号,经滤波电路后输出。

输出波形的频率上限与D/A器件的转换速度有重要关系,本例采用DAC0832器件。

DAC0832是8位D/A转换器,转换周期为1µs,其引脚信号以及与FPGA目标器件典型的接口方式如附图2-7所示。

其参考电压与+5V工作电压相接(实用电路应接精密基准电压)。

DAC0832的引脚功能简述如下:∙ILE(PIN 19):数据锁存允许信号,高电平有效,系统板上已直接连在+5V上。

∙WR1、WR2(PIN 2、18):写信号1、2,低电平有效。

∙XFER(PIN 17):数据传送控制信号,低电平有效。

∙VREF(PIN 8):基准电压,可正可负,-10V~+10V。

∙RFB(PIN 9):反馈电阻端。

∙IOUT1/ IOUT2(PIN 11、12):电流输出1和2 。

D/A转换量是以电流形式输出的,所以必须如实验结构图NO.5所示的连接方式将电流信号变为电压信号。

∙AGND/DGND(PIN 3、10):模拟地与数字地。

在高速情况下,此二地的连接线必须尽可能短,且系统的单点接地点须接在此连线的某一点上。

例6中的正弦波波型数据由64个点构成,此数据经DAC0832,并经滤波器后,可在示波器上观察到光滑的正弦波(若接精密基准电压,可得到更为清晰的正弦波形)。

3、实验内容1:根据示例例6,及以上的设计原理,完成波形发生器和扫频信号源的设计,仿真测试及实验系统上的硬件测试。

硬件实验中注意DAC0832及滤波电路须接+/-12V 电压。

然后将实验系统左下角选择插针处用短路帽短路“D/A直通”,而“滤波1”,“滤波0”处通过短路或不接短路帽达到不同的滤波方式。

将示波器的地与EDA实验系统的地相接,信号端与“AOUT”信号输出端相接;建议CLK接clock0,由此50MHz频率,此频率扫描波形数据;CLK1接clock5,由此接“1024Hz”,此频率决定扫频速度;选电路模式1;KK接键8,当为高电平时,正弦波点频输出,11位输入数据DATA由键3、键2和键1控制,信号源的输出频率由此3键输入的12位二进制数决定,数值越大,输出频率越高;“FD0”时为最高频率;键8低电平时,正弦波扫频输出,扫频速度由clock5的频率决定。

输向0832的8位数据由DD输出。

实验图5 波形发生器电路系统结构图4、实验内容2:在例6中插如一个LPM_ROM,将原例中的波形数据放在内部ROM中。

必要时增加波形点数,以利低频输出时,仍保持良好波形。

波形数据可由其它方式自动生成,然后重复以上的测试和硬件实验。

5、实验思考题:如果CLK的输入频率是50MHz,ROM中一个周期的正弦波数据是128个,要求输出的正弦波频率不低于150KHz,DAC0832是否能适应此项工作?为什么?RAM/ROM 使能拨码开关滤波1A /D 使能转换结束比较器D S 8使能D S 6使能5t h 使能R O M 使能ON87654321拨码8:DAC0832输出滤波使能拨码7:ADC0809使能,默认关闭,见左图拨码6:ADC0809转换结束使能,见左图拨码5:应用LM311使能,见下图拨码4:8数码管显示开关,默认打开拨码3:6数码管显示开关,默认关闭拨码2:默认关闭 向上拨,由厂家通知升级拨码1:两个ROM/RAM 使能,即它们的CS1接地VCCHS (PIO43)VS (PIO44)B (PIO42)G (PIO41)R (PIO40)1054876321 视频接口VGA J6R78 200R77 200R76 2001413GNDPIO45PIO46513PS/2接口J74A I N 1VCC10K VR1拨码7拨码6A I N 0P I O 8(23)(24)1216272610C L O C K 750K H Z A 021+5V r e f (-)r e f (+)I N -1I N -06922257171415818192021E U 1A D C 0809P I O 16P I O 17P I O 18P I O 19P I O 20P I O 21P I O 22P I O 23P I O 32P I O 33P I O 35P I O 34m s b 2-12-22-32-42-52-62-7l s b 2-8E O C A D D -A A D D -B A D D -C A L E E N A B L E S T A R T(拨码1:“ROM 使能 ON”即将CS1接地)P29->A14)27010(PIN30->VCC,PIN3->A15,PIN29->A14)27020(PIN30->A17,PIN3->A15,PIN3->A15,PIN29->A14)27040(PIN31->A18,PIN30->A17,PIN30->A17,PIN3->A15,PIN29->A14)29C040(PIN31->WE,PIN1->A18,628128(PIN30->VCC,PIN3->A14,PIN29->WE)(拨码8:“滤波1 ON”即连接滤波电容)滤波1103连接PIO37与COMP )(拨码5:“比较器ON”即7.2K PIO31PIO29PIO30PIO28PIO27PIO26PIO25PIO24131415164D7D6D5D4D35D26D1D07PIO37+551pFC27COMPLM311VCC10K -12+124823TL082/1AIN0AOUT5.1KR72765TL082/2841+12-12COMMEU2DAC0832118171032WR1FB93211IOUT1IOUT212/CSWR2XFERA GNDD GND VREF8VCC20VCCD1PIO8D2D3D4D5D6D7D8PIO9PIO10PIO11PIO12PIO15PIO14PIO13实验电路结构图NO.5S P E A K E R扬声器FPGA/CPLD 目标芯片12345678D16D15D14D13D12D11D10D9PIO47-PIO44PIO43-PIO40PIO39-PIO36PIO35-PIO32PIO31-PIO28PIO27-PIO24PIO23-PIO20PIO19-PIO16译码器译码器译码器译码器译码器译码器译码器译码器PIO15-PIO8PIO0PIO1PIO2PIO3PIO4PIO5PIO6PIO7键1键2键3键4键5键6键7键8右侧的RAM/ROM 是PIO8左侧的RAM/ROM 是PIO62GNDVCC PIO62/PIO8PIO49RAM/ROMA18/A19A18/A15/WE PIO26PIO25PIO24PIO32PIO33PIO34PIO35PIO36PIO37PIO38PIO39PIO14PIO47PIO10PIO48PIO9PIO46PIO45PIO11PIO12PIO13PIO15PIO31PIO30PIO29PIO28PIO273231302928272625242322212019181716151413121110987654321VCC GND2708027040270202701027512272562764628128622566264VCCA17/VCC WR/A14A13A8A9A11OE A10CS1D7D6D5D4D3GNDD2D1D0A0A1A2A3A4A5A6A7A12A14(A15)A16。