DSP期末试题与答案要点

dsp试卷及答案

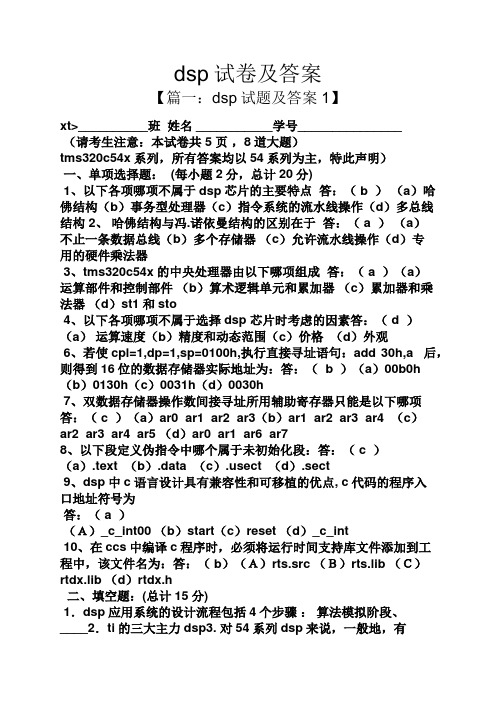

dsp试卷及答案【篇一:dsp试题及答案1】xt>__________班姓名 ___________学号_______________(请考生注意:本试卷共 5 页,8道大题)tms320c54x系列,所有答案均以54系列为主,特此声明)一、单项选择题: (每小题2分,总计20分)1、以下各项哪项不属于dsp芯片的主要特点答:( b )(a)哈佛结构(b)事务型处理器(c)指令系统的流水线操作(d)多总线结构 2、哈佛结构与冯.诺依曼结构的区别在于答:( a )(a)不止一条数据总线(b)多个存储器(c)允许流水线操作(d)专用的硬件乘法器3、tms320c54x的中央处理器由以下哪项组成答:( a )(a)运算部件和控制部件(b)算术逻辑单元和累加器(c)累加器和乘法器(d)st1和sto4、以下各项哪项不属于选择dsp 芯片时考虑的因素答:( d )(a)运算速度(b)精度和动态范围(c)价格(d)外观6、若使cpl=1,dp=1,sp=0100h,执行直接寻址语句:add 30h,a 后,则得到16位的数据存储器实际地址为:答:( b )(a)00b0h (b)0130h(c)0031h(d)0030h7、双数据存储器操作数间接寻址所用辅助寄存器只能是以下哪项答:( c )(a)ar0 ar1 ar2 ar3(b)ar1 ar2 ar3 ar4 (c)ar2 ar3 ar4 ar5 (d)ar0 ar1 ar6 ar78、以下段定义伪指令中哪个属于未初始化段:答:( c )(a).text (b).data (c).usect (d).sect9、dsp中c语言设计具有兼容性和可移植的优点, c代码的程序入口地址符号为答:( a )(A)_c_int00 (b)start(c)reset (d)_c_int10、在ccs中编译c程序时,必须将运行时间支持库文件添加到工程中,该文件名为:答:( b)(A)rts.src (B)rts.lib (C)rtdx.lib (d)rtdx.h二、填空题:(总计15分)1.dsp应用系统的设计流程包括4个步骤:算法模拟阶段、____2.ti的三大主力dsp3. 对54系列dsp来说,一般地,有192k字可寻址存储空间,其中包括:4.用重复指令将程序存储区从地址单元0100h到0180h区间段的内容复制到数据存储区间从1000h开始的地址单元中。

dsp期末考试试题及答案

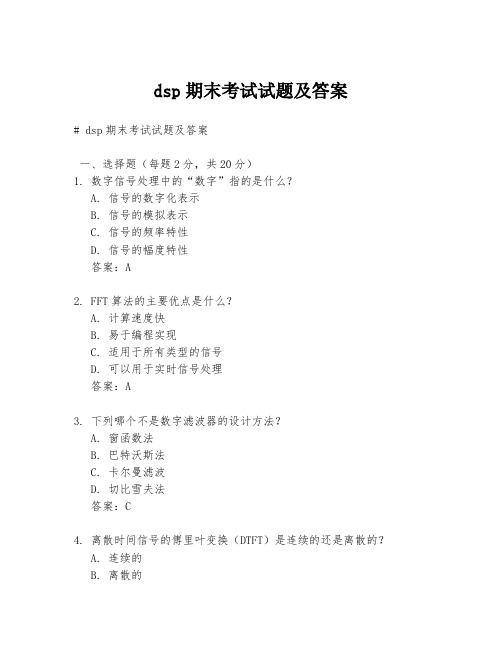

dsp期末考试试题及答案# dsp期末考试试题及答案一、选择题(每题2分,共20分)1. 数字信号处理中的“数字”指的是什么?A. 信号的数字化表示B. 信号的模拟表示C. 信号的频率特性D. 信号的幅度特性答案:A2. FFT算法的主要优点是什么?A. 计算速度快B. 易于编程实现C. 适用于所有类型的信号D. 可以用于实时信号处理答案:A3. 下列哪个不是数字滤波器的设计方法?A. 窗函数法B. 巴特沃斯法C. 卡尔曼滤波D. 切比雪夫法答案:C4. 离散时间信号的傅里叶变换(DTFT)是连续的还是离散的?A. 连续的B. 离散的C. 既连续又离散D. 都不是答案:A5. 采样定理指出,采样频率至少应该是信号最高频率的多少倍?A. 1倍B. 2倍C. 3倍D. 4倍答案:B...(此处省略其他选择题,共10题)二、简答题(每题10分,共20分)1. 解释什么是离散傅里叶变换(DFT)以及它与连续傅里叶变换(FT)的区别。

答案:离散傅里叶变换(DFT)是一种将离散时间信号转换为频域表示的方法。

它是一种离散的变换,意味着输入和输出都是离散的。

DFT通常用于数字信号处理中,可以计算出信号在各个频率上的幅度和相位。

与DFT不同,连续傅里叶变换(FT)是将连续时间信号转换为连续的频域表示,它适用于模拟信号处理。

2. 简述数字滤波器的基本概念及其分类。

答案:数字滤波器是一种对数字信号进行处理的系统,它允许某些频率的信号通过,同时抑制或减少其他频率的信号。

数字滤波器可以根据它们的频率响应特性进行分类,主要分为低通滤波器、高通滤波器、带通滤波器和带阻滤波器。

每种类型的滤波器都设计用于处理特定频率范围内的信号。

三、计算题(每题15分,共30分)1. 给定一个离散时间信号 x[n] = {1, 2, 3, 4},计算其DFT X[k]。

答案:X[k] = DFT{x[n]} = Σ_{n=0}^{N-1} x[n] * e^(-j * 2π * k * n / N)其中,N=4,计算得到 X[k] 的值。

DSP期末试题与答案,推荐文档

在节电模式下,使之更适合于手机。

(7)在片仿真接口,片上的JTAG接口符合IEEE149.1边界扫描逻辑接口标准,可与主机连接,用于芯片的仿真和测试。

9.定时器由哪些寄存器组成,他们是如何工作的?答:定时器主要由3个寄存器所组成,包括定时寄存器TIM 、定时周期寄存器 PRD 、定时控制寄存器TCR。

定时寄存器TIM是一个减1计数器,提供定时器目前的计数值;周期定时器PRD用来存取定时时间常数;定时控制寄存器TCR中包含定时器的控制位和状态位,可以使能和屏蔽定时器,决定定时器的工作模式,用来控制定时器的操作。

二、指令解释1、MAC *AR3+,*AR4+,A,B;B=A-*AR3+*AR4;AR3=AR3+1;AR4=AR4+12、SUB #12345,8,A,B;B=A-12345<<83、ADD *AR2+,*AR2-,A;A=*(AR2)+*(AR2+1)4、RPT #99NOP;重复NOP100次5、MVDD *AR3+,*AR5+;数据存储器内部传送数据AR3→AR5,且指令结束后AR3与AR5加16、ABDST *AR3+,*AR4+;B=(*AR3-*AR4)<<167、CALA A;按累加器规定的地址调用子程序8、ST T,*AR7- *AR7=T,AR7=AR7-19、DST B,*AR1+ AR1=B,AR1=AR1+110、STA, *AR4+||LD *AR4-,A AR4=A,AR4=AR4+1|| A=AR4,AR4-111、LD #0032H,4,A;立即数0032H先左移4位后,再加载累加器A12、STM #1000H,*AR2;立即数1000H存储到AR2指向的地址单元13、MAC #345,A,B;立即数345与T寄存器内值相乘后与累加器A相加,结果加载累加器B14、MVDD *AR3-,100H;AR3指向的地址单元的值传送给地址100H,AR3中地址减一15、LDM *AR1,A;AR1指向的地址单元的值加载到累加器A16、LD #80H, A 把立即数80H装入累加器17、WRITA SMEM 把Smem所指定的数据存储单元中的一个数传送到累加器A所指定的成序存储单元18、PORTR FIFO,*AR5 把一个数从端口为FIFO的I/O口复制到AR5寄存器所指向的数据存储单元中19、LDM MMR ,A ;将MMR 装入累加器A 中20、MVKD SAMPLE,*AR521、ADD *AR3+,14,A ;将AR3左移14加上A →AAR3=AR3+122、MPYA TEMP2;B<=A.Temp2.T=Temp223、STA , *AR4+||LD *AR4-,A24、DST B ,*AR1-; B 存到长字单元 AR1中,且AR 减125、MACD *AR2-,COEFFS,A26、STL A ,@quot;将 累加器A 的低16位字存放在quot 的存储单元中27、ADD #4568H ,8,A ,B;将4568H 左移8位与A 相加,赋给B28、LDM AR1,A;存储器映像寄存器寻址方式,将映像寄存器加载累加器AR1 → A 的低位,其余位置为029、MVDD *AR3+,*AR5+;数据存储器内部传送数据AR3→AR5,且指令结束后AR3与AR5加130、MPYA TEMP2;B<=A.Temp2.T=Temp2四、编程1.用汇编语言编制计算的程序。

dsp试卷及答案

dsp试卷及答案dsp试卷及答案【篇一:dsp试题及答案1】xt>__________班姓名 ___________学号_______________(请考生注意:本试卷共 5 页,8道大题)tms320c54x系列,所有答案均以54系列为主,特此声明)一、单项选择题: (每小题2分,总计20分)1、以下各项哪项不属于dsp芯片的主要特点答:( b )(a)哈佛结构(b)事务型处理器(c)指令系统的流水线操作(d)多总线结构2、哈佛结构与冯.诺依曼结构的区别在于答:( a )(a)不止一条数据总线(b)多个存储器(c)允许流水线操作(d)专用的硬件乘法器3、tms320c54x的中央处理器由以下哪项组成答:( a )(a)运算部件和控制部件(b)算术逻辑单元和累加器(c)累加器和乘法器(d)st1和sto4、以下各项哪项不属于选择dsp 芯片时考虑的因素答:(d )(a)运算速度(b)精度和动态范围(c)价格(d)外观6、若使cpl=1,dp=1,sp=0100h,执行直接寻址语句:add 30h,a 后,则得到16位的数据存储器实际地址为:答:(b )(a)00b0h (b)0130h(c)0031h(d)0030h7、双数据存储器操作数间接寻址所用辅助寄存器只能是以下哪项答:( c )(a)ar0 ar1 ar2 ar3(b)ar1 ar2 ar3 ar4 (c)ar2 ar3 ar4 ar5 (d)ar0 ar1 ar6 ar78、以下段定义伪指令中哪个属于未初始化段:答:( c )(a).text (b).data (c).usect (d).sect9、dsp中c语言设计具有兼容性和可移植的优点, c代码的程序入口地址符号为答:( a )(A)_c_int00 (b)start(c)reset (d)_c_int10、在ccs中编译c程序时,必须将运行时间支持库文件添加到工程中,该文件名为:答:(b)(A)rts.src (B)rts.lib (C)rtdx.lib (d)rtdx.h二、填空题:(总计15分)1.dsp应用系统的设计流程包括4个步骤:算法模拟阶段、____2.ti的三大主力dsp3. 对54系列dsp来说,一般地,有192k字可寻址存储空间,其中包括:4.用重复指令将程序存储区从地址单元0100h到0180h区间段的内容复制到数据存储区间从1000h开始的地址单元中。

DSP原理期末试卷和答案

DSP原理期末试卷和答案1、下面对一些常用的伪指令说法正确的是:( D )A、.def所定义的符号;是在当前模块中使用;在别的模块中定义的符号;B、.ref 所定义的符号;是当前模块中定义;并可在别的模块中使用的符号;C、.sect命令定义的段是未初始化的段;D、.usect命令定义的段是未初始化的段。

2、要使DSP能够响应某个可屏蔽中断;下面的说法正确的是( B)A、需要把状态寄存器ST1的INTM位置1;且中断屏蔽寄存器IMR相应位置0B、需要把状态寄存器ST1的INTM位置1;且中断屏蔽寄存器IMR相应位置1C、需要把状态寄存器ST1的INTM位置0;且中断屏蔽寄存器IMR相应位置0D、需要把状态寄存器ST1的INTM位置0;且中断屏蔽寄存器IMR相应位置13、对于TMS320C54x系列DSP芯片;下列说法正确的是………… ( C )A、 8位DSPB、32位DSPC、定点型DSPD、浮点型DSP4、若链接器命令文件的MEMORY部分如下所示:MEMORY{PAGE 0: PROG: origin=C00h, length=1000hPAGE 1: DA TA: origin=80h, length=200h}则下面说法不正确的是()A、程序存储器配置为4K字大小B、程序存储器配置为8K字大小C、数据存储器配置为512字大小D、数据存储器取名为DATA5、在串行口工作于移位寄存器方式时;其接收由()来启动。

A、RENB、RIC、REN和RID、TR6、执行指令PSHM AR5之前SP=03FEH;则指令执行后SP=( A )A、03FDHB、03FFHC、03FCHD、0400H7、TMS320C54X DSP采用改进的哈佛结构;围绕____A__组_______位总线建立。

A、8;16B、16;8C、8;8D、16;168、TMS320C54X DSP汇编指令的操作数域中; A 前缀表示的操作数为间接寻址的地址。

DSP试题及答案1

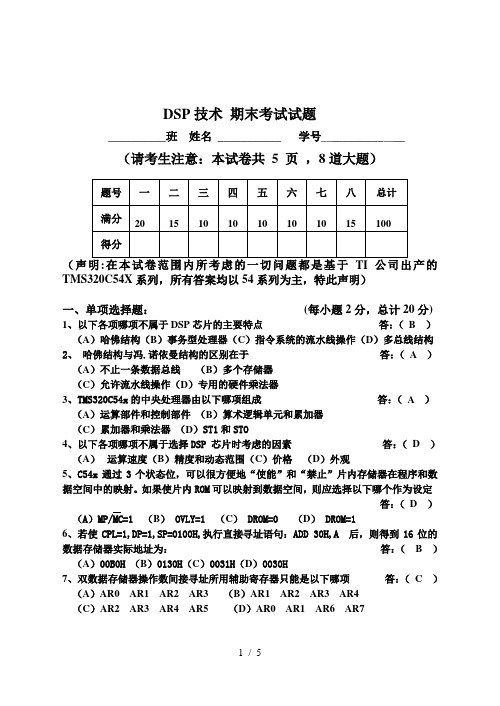

DSP技术期末考试试题__________班姓名___________ 学号_______________(请考生注意:本试卷共 5 页,8道大题)TMS320C54X系列,所有答案均以54系列为主,特此声明)一、单项选择题:(每小题2分,总计20分)1、以下各项哪项不属于DSP芯片的主要特点答:(B )(A)哈佛结构(B)事务型处理器(C)指令系统的流水线操作(D)多总线结构2、哈佛结构与冯.诺依曼结构的区别在于答:(A )(A)不止一条数据总线(B)多个存储器(C)允许流水线操作(D)专用的硬件乘法器3、TMS320C54x的中央处理器由以下哪项组成答:(A )(A)运算部件和控制部件(B)算术逻辑单元和累加器(C)累加器和乘法器(D)ST1和STO4、以下各项哪项不属于选择DSP 芯片时考虑的因素答:(D )(A)运算速度(B)精度和动态范围(C)价格(D)外观5、C54x通过3个状态位,可以很方便地“使能”和“禁止”片内存储器在程序和数据空间中的映射。

如果使片内ROM可以映射到数据空间,则应选择以下哪个作为设定答:(D )(A)MP/MC=1 (B) OVLY=1 (C) DROM=0 (D) DROM=16、若使CPL=1,DP=1,SP=0100H,执行直接寻址语句:ADD 30H,A 后,则得到16位的数据存储器实际地址为:答:( B )(A)00B0H(B)0130H(C)0031H(D)0030H7、双数据存储器操作数间接寻址所用辅助寄存器只能是以下哪项答:(C )(A)AR0 AR1 AR2 AR3 (B)AR1 AR2 AR3 AR4(C)AR2 AR3 AR4 AR5 (D)AR0 AR1 AR6 AR78、以下段定义伪指令中哪个属于未初始化段:答:(C )(A).text (B).data(C).usect(D).sect9、DSP中C语言设计具有兼容性和可移植的优点, C代码的程序入口地址符号为答:(A )(A)_c_int00 (B)start(C)reset (D)_c_int10、在CCS中编译C程序时,必须将运行时间支持库文件添加到工程中,该文件名为:答:(B )(A)rts.src (B)rts.lib(C)rtdx.lib (D)rtdx.h二、填空题:(总计15分) 1.DSP应用系统的设计流程包括4个步骤:算法模拟阶段、____器件选型_______、_____ 软硬件设计____、____调试________.2.TI的三大主力DSP产品系列为: TMS320C2000 、 TMS320C5000 、 TMS320C6000。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

一、填空题:1. DSP芯片的结构特点主要有改进的哈佛结构、低功耗设计、高度并行性、多处理单元、特殊的DSP指令等。

2.C54x DSP具有两个 40 位累加器。

累加器A的 AG或32-39 位是保护位。

3.软件中断都是由 INTR K 、 TRAP K 和 RESET 产生。

4.TMS320C54X片内有8条16位主总线,它们是1条程序总线、 3条数据总线、4条地址总线。

5.MEMROY的作用是用于描述系统实际的硬件资源,用来定义用户设计的系统中所包含的各种形式的存储器,以及它们占据的地址范围,SECTIONS的作用是用于描述输入段怎样被组合到输出段内,在可执行程序内定义输出段,规定存储器内何处存放置输出段,允许重命名输出段。

6. 执行复位操作后,下列寄存器的初始值分别为:ASM= 0 、DP= 0 。

7.TMS320C54x有三种类型的串行口:标准同步串行口(SPI)、缓冲串行口(BSP)、和时分多路复用串行接口(TDM)。

8.桶形移位器能把输入的数据进行 0-31位的左移和 0-15 位的右移。

9.即寻址方式中的立即数有两种数值形式,数值的位数为 3、5、8、9 位时为短立即数;数值的位数为 16 位时是长立即数。

10.DSP片内寄存器在C语言中一般采用指针方式来访问,常常采用的方法是将DSP寄存器地址的列表定义在头文件中(reg.h)。

11. 所有TMS320C54X芯片内部都包含程序存储器和数据存储器。

12.直接寻址就是在指令中包含有数据存储器地址的低7位用作偏移地址,并与基地地址组成16位的数据存储器地址。

13.定时器主要由3个寄存器所组成,包括定时寄存器TIM 、定时周期寄存器PRD 、定时控制寄存器TCR 。

14.链接器对段的处理主要通过 MEMORY 和 SECTIONS 两个命令完成。

15.OVLY= 0 ,则片内RAM只安排到数据存储空间。

DROM= 1 ,则部分片内ROM安排到数据空间。

16.C54X的工作方式状态寄存器PMST提供了三个控制位,包括 MP/非MC 、 OVLY 、DROM 。

17. DSP芯片的结构特点主要有改进的哈佛结构、流水线操作、专用的硬件乘法器、快速的指令周期、特殊的DSP指令等。

18.ST1的CPL= 1 表示选用堆栈指针(SP)的直接寻址方式。

19.TMS320C54X有3个16位寄存器作为状态和控制寄存器,它们是状态寄存器ST0 、状态寄存器ST1 、处理器工作方式状态寄存器PMST 。

20.ST1的C16= 0 表示ALU工作在双精度算术运算方式。

21.时钟发生器包括一个内部振荡器和一个锁相环(PLL)电路。

22.所有的COFF文件都包含三种形式的段,分别是 .text 文本段、 .data 数据段、和 .bss 保留空间段。

23.状态寄存器ST1中CPL=0表示使用DP ,CPL=1表示选择的是使用SP 。

24.累加器寻址的两条指令分别是 READA Smem 、 WRITA Smem 。

二、简答题1.简述TMS320C54x的7种基本的数据寻址方式。

答:1、立即寻址 2、绝对寻址 3、直接寻址 4、间接寻址 5、累加器寻址 6、存储器映射寄存器寻址 7、堆栈寻址2.段的作用是什么?COFF目标文件包含哪些段?答:所谓段,是指连续地占有存储空间的一个代码段或数据段,是COFF文件中最重要的概念。

一个目标文件中的每一段都是分开的和各不相同的。

COFF目标文件文件包含:(1)text段:可执行代码段(2)data段:已初始化数据段(3)bss段:未初始化数据的保留空间段3.简述线性缓冲区法实现FIR滤波器延时一个采样周期运算Z-1。

4.什么是COFF和段?COFF目标文件包含哪些段?答:所谓段,是指连续地占有存储空间的一个代码段或数据段,是COFF文件中最重要的概念。

一个目标文件中的每一段都是分开的和各不相同的。

.text 文本段 .data 数据段 .bss保留空间段5.简述McBSP接口的特点。

答:(1)全双工通信;(2)拥有两级缓冲发送和三级缓冲接收数据寄存器,允许连续数据流传输;(3)为数据发送和接收提供独立的帧同步脉冲和时钟信号;(4)能够与工业标准的解码器、模拟接口芯片(AICs)和其他串行A/D和D/A设备直接连接;5)支持外部移位时钟或内部频率可编程移位时钟。

6)128个通道用于接收传送。

(7)支持A-bis(8)接口直接连接工业标准的多媒体数字信号编解码器,A/D、D/A和模拟芯片。

6.HPI8接口有几个寄存器?他们的作用是什么?答:(1)HPI存储器:用于TMS320C54X与主机间传送数据。

地址从1000H到17FFH,空间容量为2K字(2)HPI地址寄存器:由主机对其直接访问,存放当前寻址HPI存储单元的地址(3)HPI数据锁存器:由主机对其直接访问,存放当前进行读/写的数据(4)HPI控制寄存器:TMS320C54X与主机都能对其直接访问,用于主处理与DSP相互握手,实现相互中断请求(5)HPI控制逻辑:用于处理HPI与主机之间的接口信号7.一个典型的DSP系统通常由哪些部分组成?画出原理框图。

答:DSP 芯片及DSP 基本系统、程序和数据存储器、数/模和模/数转换器、模拟控制与处理电路、各种控制口和通信口、电源处理电路和同步电路等。

8.简述C54X芯片的主要特点。

答:(1)CPU利用其专用的硬件逻辑和高度并行性提高芯片的处理性能。

(2)存储器具有192K字可寻址存储空间(包括64K字程序存储空间、64K字数据存储空间、64K字I/O空间)(3)高度专业化的指令集能够快速地实现算法并用于高级语言编程优化(4)片内外设和专用电路采用模块化的结构设计,可以快速地推出新的系列产品(5)TMS320C54X执行单周期定点指令时间为25/20/15/12.5/10ns,每秒指令数为40/66/100MIPS。

(6)TMS320C54XD电源由IDLE1、IDLE2、IDLE3功耗下降指令控制功能,以便DSP工作在节电模式下,使之更适合于手机。

(7)在片仿真接口,片上的JTAG接口符合IEEE149.1边界扫描逻辑接口标准,可与主机连接,用于芯片的仿真和测试。

9.定时器由哪些寄存器组成,他们是如何工作的?答:定时器主要由3个寄存器所组成,包括定时寄存器TIM 、定时周期寄存器 PRD 、定时控制寄存器TCR。

定时寄存器TIM是一个减1计数器,提供定时器目前的计数值;周期定时器PRD用来存取定时时间常数;定时控制寄存器TCR中包含定时器的控制位和状态位,可以使能和屏蔽定时器,决定定时器的工作模式,用来控制定时器的操作。

二、指令解释1、MAC *AR3+,*AR4+,A,B;B=A-*AR3+*AR4;AR3=AR3+1;AR4=AR4+12、SUB #12345,8,A,B;B=A-12345<<83、ADD *AR2+,*AR2-,A;A=*(AR2)+*(AR2+1)4、RPT #99NOP;重复NOP100次5、MVDD *AR3+,*AR5+;数据存储器内部传送数据AR3→AR5,且指令结束后AR3与AR5加16、ABDST *AR3+,*AR4+;B=(*AR3-*AR4)<<167、CALA A;按累加器规定的地址调用子程序8、ST T,*AR7- *AR7=T,AR7=AR7-19、DST B,*AR1+ AR1=B,AR1=AR1+110、STA, *AR4+||LD *AR4-,A AR4=A,AR4=AR4+1|| A=AR4,AR4-111、LD #0032H,4,A;立即数0032H先左移4位后,再加载累加器A12、STM #1000H,*AR2;立即数1000H存储到AR2指向的地址单元13、MAC #345,A,B;立即数345与T寄存器内值相乘后与累加器A相加,结果加载累加器B14、MVDD *AR3-,100H;AR3指向的地址单元的值传送给地址100H,AR3中地址减一15、LDM *AR1,A;AR1指向的地址单元的值加载到累加器A16、LD #80H, A 把立即数80H装入累加器17、WRITA SMEM 把Smem所指定的数据存储单元中的一个数传送到累加器A所指定的成序存储单元18、PORTR FIFO,*AR5 把一个数从端口为FIFO的I/O口复制到AR5寄存器所指向的数据存储单元中19、LDM MMR,A;将MMR装入累加器A中20、MVKD SAMPLE,*AR521、ADD *AR3+,14,A;将AR3左移14加上A →AAR3=AR3+122、MPYA TEMP2;B<=A.Temp2.T=Temp223、STA , *AR4+||LD *AR4-,A24、DST B ,*AR1-; B 存到长字单元 AR1中,且AR 减125、MACD *AR2-,COEFFS,A26、STL A ,@quot;将 累加器A 的低16位字存放在quot 的存储单元中27、ADD #4568H ,8,A ,B;将4568H 左移8位与A 相加,赋给B28、LDM AR1,A;存储器映像寄存器寻址方式,将映像寄存器加载累加器AR1 → A 的低位,其余位置为029、MVDD *AR3+,*AR5+;数据存储器内部传送数据AR3→AR5,且指令结束后AR3与AR5加130、MPYA TEMP2;B<=A.Temp2.T=Temp2四、编程1.用汇编语言编制计算60i i y x ==∑的程序。

.global start.mmregs .dataTable: .word 1,1,1,1,1,1.textstart: STM #Table,AR1LD #0,ARPT #5 ADDC *AR1+,Aend:b end2. 编一程序,首先实现对DATA 开始的5个单元赋初值0,1,2,3,4,5,然后再对每个单元内容加1。

;chu shi hua x[5]={0,1,2,3,4} bin dui mei ge dan yuan jia 1.title "lian.asm".mmregs.bss x,5stack .usect "stack",10h.datatable: .word 0,1,2,3,4.def start.textstart: STM #x,AR1RPT #4MVPD table,*AR1+LD #1,16,BSTM #4,BRCSTM #x,AR4RPTB #next-1ADD *AR4,16,B,ASTH A,*AR4+next: LD #0,Bend: B end.end3.试编一程序,计算y =x a i i i ∑=51,其中数据均为小数。