安富NF2301蓝牙模组PCB板脚位名称说明图

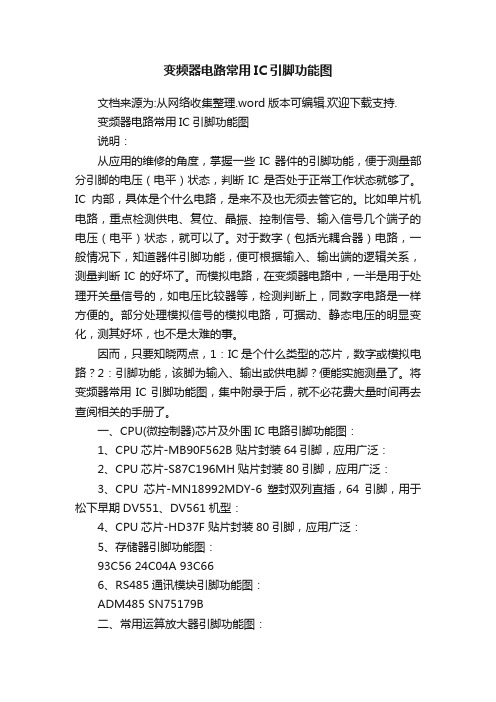

变频器电路常用IC引脚功能图

变频器电路常用IC引脚功能图文档来源为:从网络收集整理.word版本可编辑.欢迎下载支持.变频器电路常用IC引脚功能图说明:从应用的维修的角度,掌握一些IC器件的引脚功能,便于测量部分引脚的电压(电平)状态,判断IC是否处于正常工作状态就够了。

IC内部,具体是个什么电路,是来不及也无须去管它的。

比如单片机电路,重点检测供电、复位、晶振、控制信号、输入信号几个端子的电压(电平)状态,就可以了。

对于数字(包括光耦合器)电路,一般情况下,知道器件引脚功能,便可根据输入、输出端的逻辑关系,测量判断IC的好坏了。

而模拟电路,在变频器电路中,一半是用于处理开关量信号的,如电压比较器等,检测判断上,同数字电路是一样方便的。

部分处理模拟信号的模拟电路,可据动、静态电压的明显变化,测其好坏,也不是太难的事。

因而,只要知晓两点,1:IC是个什么类型的芯片,数字或模拟电路?2:引脚功能,该脚为输入、输出或供电脚?便能实施测量了。

将变频器常用IC引脚功能图,集中附录于后,就不必花费大量时间再去查阅相关的手册了。

一、CPU(微控制器)芯片及外围IC电路引脚功能图:1、CPU芯片-MB90F562B 贴片封装64引脚,应用广泛:2、CPU芯片-S87C196MH贴片封装80引脚,应用广泛:3、CPU芯片-MN18992MDY-6 塑封双列直插,64引脚,用于松下早期DV551、DV561机型:4、CPU芯片-HD37F 贴片封装80引脚,应用广泛:5、存储器引脚功能图:93C56 24C04A 93C666、RS485通讯模块引脚功能图:ADM485 SN75179B二、常用运算放大器引脚功能图:LF347四运放电路 LM324四运放电路 LM339四运放(开路集电极输出)LF353 双运放电路 LM393 双运放(开路集电极输出) TL072四运放电路运算放大器多用于电流、电压检测电路,用于处理模拟信号和将模拟信号转换为开关量信号——报警、停机保护信号。

51单片机引脚介绍

P0口有三个功能:1、外部扩展存储器时,当数据总线。

2、外部扩展存储器时,当地址总线。

3、不扩展时,可做一般的i/o使用,但内部没有上拉电阻,做为输入输出时应在外部接上上拉电阻。

P1口只做I/0口使用,其内部有上拉电阻。

P2口有两个功能:1、扩展外部存储器时,当作地址总线使用。

2、做一般I/O口使用时,其内部有上拉电阻。

P3口也有两个功能:1、除了作为I/O使用外(其内部有上拉电阻),还有一些特殊功能,由特殊寄存器来设置。

2、有内部EPROM的单片机芯片,为写入程序需提供专门的编程脉冲和编程电源,这些信号也是由信号引脚的形式提供的。

RST/VPD:1、复位,当在此引脚加上两个机器周期的高电平时,面实现复位操作。

2、备用电源,当外接电源下降到下限值时,备用电源就会经第二功能的方式由些引脚引入,以保护内部RAM中的信息不会丢失。

ALE/PROG地址锁存控制信号:在系统扩展时,ALE用于控制把P0口的输出低8位地址送锁存器锁存起来,以实现低位地址的数据的隔离。

例如,ALE与74LS373锁存器的G相连接,当CPU对外部进行存取时,用以锁住地址的低位地址,即P0口输出,ALE有可能是高电平也有可能是低电平,当ALE是高电平时,允许地址锁存信号,当请问外部存储器时,ALE负跳变,将P0口上低8位地址信号送入锁存器,当ALE是低电平时,P0口上的内容和锁存器输出一致。

在没有访问外部存储器期间,ALE以1/6振荡周期频率输出,当访问外部存储器以1/12振荡周期输出,从这里我们可以看到,当系统没有进行扩展时ALE会以1/6振荡周期的固定频率输出,因此可以做为外部时钟,或者外部定时脉冲使用。

PROG为编程脉冲的输入端:单片机内部有一个4K或8K的程序存储器ROM。

R OM的作用是用来存放用户需要运行的程序,而PROG就是将这些程序写到ROM中的脉冲输入端。

PSEN外部程序存储器读选通信号:在读外部ROM时PSEN低电平有效,以实现外部ROM单元的读操作,内部ROM读取时,PSEN不动作,外部ROM读取时,在每个机器周期会动作两次。

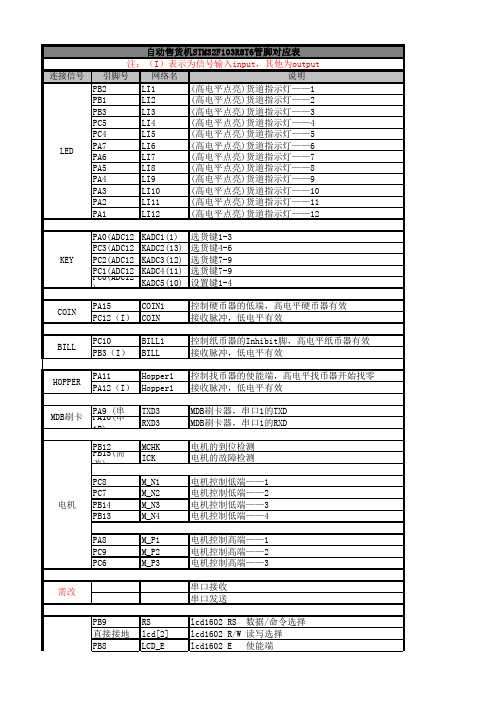

(模板)PCB管脚映射表

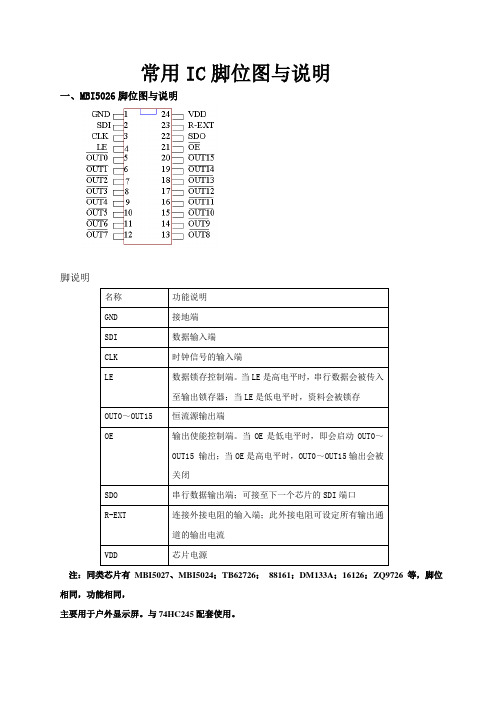

常用IC脚位图与说明

常用IC脚位图与说明

一、MBI5026脚位图与说明

脚说明

注:同类芯片有MBI5027、MBI5024;TB62726;88161;DM133A;16126;ZQ9726等,脚位相同,功能相同,

主要用于户外显示屏。

与74HC245配套使用。

二、74HC595脚位图与说明

注:主要用途是控制列信号。

多于户内点阵单元板,与4953、74HC138,74HC245配套使用。

三、74HC138脚位图说明:

1、A0~A2为地址线输入脚(来源74HC245)。

2、E1~E3为根据电路设计需要决定本身无实际意义。

3、GND 与VCC 为电源脚。

4、Y0~Y8为行信号控制输出到IC4953。

注:同类芯片有74HC139,功能同等,用于行信号控制,多用于户内点阵单元板。

与4953,74HC595,

74HC245配套使用。

四、74HC245脚位图:

说明:1、DIR (VDD)、GND、VCC为直流电源脚(注意区分

正负极)。

2、OE为接地端。

3、A0~A7为信号输入脚.

4、B0~B7为信号输出脚(A0输入对应B0输出,依此类推)。

注:同类IC有74HC244,但脚位不同。

功能同等,

都是用于信号放大。

任何产品都必须使用。

五、4953脚位图

说明:1、S1~S2为行信号输入(来源74HC138)。

2、G1~G2为接电源脚。

3、D1、D2为输出脚。

注:同类产品有4801、4803等。

用于对行信号控制。

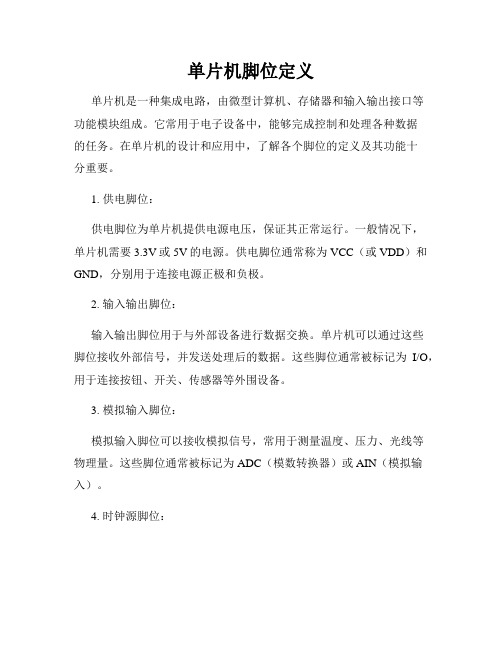

单片机脚位定义

单片机脚位定义单片机是一种集成电路,由微型计算机、存储器和输入输出接口等功能模块组成。

它常用于电子设备中,能够完成控制和处理各种数据的任务。

在单片机的设计和应用中,了解各个脚位的定义及其功能十分重要。

1. 供电脚位:供电脚位为单片机提供电源电压,保证其正常运行。

一般情况下,单片机需要3.3V或5V的电源。

供电脚位通常称为VCC(或VDD)和GND,分别用于连接电源正极和负极。

2. 输入输出脚位:输入输出脚位用于与外部设备进行数据交换。

单片机可以通过这些脚位接收外部信号,并发送处理后的数据。

这些脚位通常被标记为I/O,用于连接按钮、开关、传感器等外围设备。

3. 模拟输入脚位:模拟输入脚位可以接收模拟信号,常用于测量温度、压力、光线等物理量。

这些脚位通常被标记为ADC(模数转换器)或AIN(模拟输入)。

4. 时钟源脚位:时钟源脚位用于提供单片机内部的时钟信号,控制其运行速度。

根据不同的单片机型号,时钟源脚位可以是晶振输入脚位(XTAL)或者外部时钟输入脚位(CLKIN)。

5. 复位脚位:复位脚位用于重启或初始化单片机。

当复位脚位被置高电平时,单片机将重新启动并执行初始化操作。

一般来说,复位脚位被标记为RESET或RST。

6. 中断脚位:中断脚位用于连接外部中断源,如按钮按下、定时器溢出等。

当中断源发生时,单片机可以立即执行中断服务程序,处理相关事件。

不同型号的单片机,其中断脚位的标记可能有所不同。

7. 程序存储器脚位:程序存储器脚位用于连接单片机的存储器芯片,存储程序指令。

这些脚位通常称为ROM或Flash,用于存储程序的读取。

8. 数据存储器脚位:数据存储器脚位用于连接单片机的存储器芯片,用于存储数据。

这些脚位通常称为RAM,用于临时存储运行时的数据。

除了上述常见的脚位定义,不同型号的单片机还可能存在其他功能脚位,如串口通信脚位(UART)、定时器脚位、PWM输出脚位等。

在实际应用中,根据需要选择合适的脚位并正确连接,以满足特定的功能要求。

激光打标机常用主控箱航插脚位实物图

当您在维修设备过程中,看到这种航空插头时,在表面看不出来哪个脚位为1脚,这个资料会给您带来方便。

经常关注我的文档会让您受益非浅。

如何选择电连接器(航空插头)的正确安装方式呢?电连接器的安装方式最只要有三种:压接、SMT、焊接,每一种不同的安装都是根据具体的特点和应用情况的不同而而有所区别。

电连接器的安装方式最只要有三种:压接、SMT、焊接,每一种不同的安装都是根据具体的特点和应用情况的不同而而有所区别。

方式特点:压接一般是小电流,优点是速度快、投资少、能实现自动化生产、效率高;缺点是可靠性低、附加设备多...电流大可以选择SMT,优点是可靠、能实现自动化生产、效率高,缺点是设备投资大电流大也可以选择焊接,优点是可靠性高、设备投资少缺点是不能实现自动化生产、效率低,应用情况:压接, 用在带有电线为主的连接,能够大批量快速生产,同时保证气密连接。

在线对线连接器,线对板连接器的连接上非常实用,很多家电产品和高电流产品都是用这种工艺。

SMT是焊接的一种,将元器件焊接到PCB上,所用的焊盘比较小,连接器的体积也比较小,方便客户缩小产品体积,简化生产工艺,但是一般而言,SMT的结构抗拉力要差一点。

焊接,对于导线与触点之间的焊接,现在已经不是普遍使用了。

因为质量不能很好的保证,有时候会出现虚焊情况,生产工艺效率不高。

另外板对板连接器很多也用压接,生产效率高。

以前已经说过连接器技术创新是连接器行业发展的真正动力,而连接器技术创新的一个要点是要有大胆设想、小心求证的能力和有逆向思维的技巧。

不仅是连接器行业,可以说所有行业都应该从材料和工艺等几个方面进行创新性思维并重在实践和开发。

宇之科表示:连接器是电子行业中品种多、用量大的器件,其生产效率一直是激烈竞争中的一个重要参数,电镀生产效率有时成为连接器制造的一个瓶颈,因此,提高电镀生产效率是连接器电镀中一个重要的课题。

现在一些大型连接器制造厂商已经采用全自动的电镀生产线,目前适用连接器电镀的生产线有振动电镀生产线、带料(线材)生产线和滚镀生产线等。

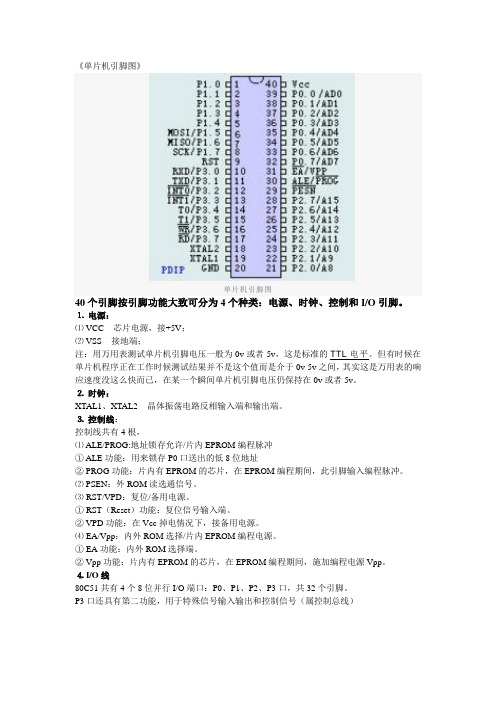

单片机引脚说明-按其引脚功能分为四部分叙述这40条引脚的功能

下面按其引脚功能分为四部分叙述这40条引脚的功能。

1、主电源引脚VCC和VSSVCC——(40脚)接+5V电压;VSS——(20脚)接地。

2、外接晶体引脚XTAL1和XTAL2XTAL1(19脚)接外部晶体的一个引脚。

在单片机部,它是一个反相放大器的输入端,这个放大器构成了片振荡器。

当采用外部振荡器时,对HMOS单片机,此引脚应接地;对CHMOS 单片机,此引脚作为驱动端。

XTAL2(18脚)接外晶体的另一端。

在单片机部,接至上述振荡器的反相放大器的输出端。

采用外部振荡器时,对HMOS单片机,该引脚接外部振荡器的信号,即把外部振荡器的信号直接接到部时钟发生器的输入端;对XHMOS,此引脚应悬浮。

3、控制或与其它电源复用引脚RST/VPD、ALE/PROG、PSEN和EA/VPP①RST/VPD(9脚)当振荡器运行时,在此脚上出现两个机器周期的高电平将使单片机复位。

推荐在此引脚与VSS引脚之间连接一个约8.2k的下拉电阻,与VCC引脚之间连接一个约10μF的电容,以保证可靠地复位。

VCC掉电期间,此引脚可接上备用电源,以保证部RAM的数据不丢失。

当VCC主电源下掉到低于规定的电平,而VPD在其规定的电压围(5±0.5V),VPD就向部RAM提供备用电源。

②ALE/PROG(30脚):当访问外部存贮器时,ALE(允许地址锁存)的输出用于锁存地址的低位字节。

即使不访问外部存储器,ALE端仍以不变的频率周期性地出现正脉冲信号,此频率为振荡器频率的1/6。

因此,它可用作对外输出的时钟,或用于定时目的。

然而要注意的是,每当访问外部数据存储器时,将跳过一个ALE脉冲。

ALE端可以驱动(吸收或输出电流)8个LS型的TTL输入电路。

对于EPROM单片机(如8751),在EPROM编程期间,此引脚用于输入编程脉冲(PROG)。

③PSEN(29脚):此脚的输出是外部程序存储器的读选通信号。

在从外部程序存储器取指令(或常数)期间,每个机器周期两次PSEN有效。

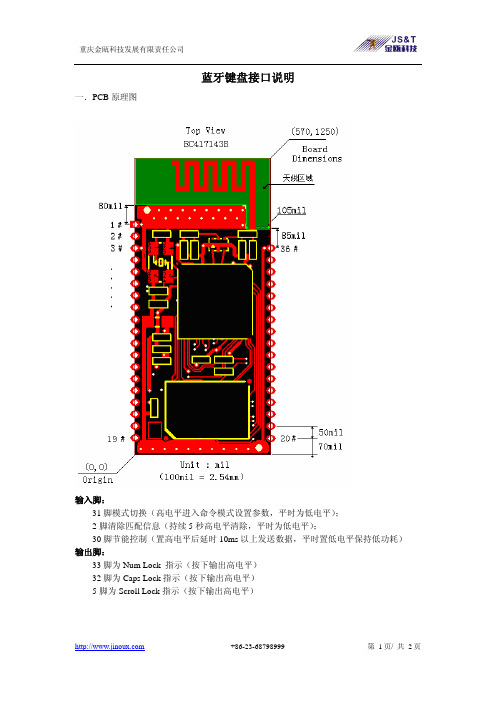

蓝牙键盘软件接口说明_售前

蓝牙键盘接口说明

一.PCB原理图

输入脚:

31脚模式切换(高电平进入命令模式设置参数,平时为低电平);

2脚清除匹配信息(持续5秒高电平清除,平时为低电平);

30脚节能控制(置高电平后延时10ms以上发送数据,平时置低电平保持低功耗)输出脚:

33脚为Num Lock 指示(按下输出高电平)

32脚为Caps Lock指示(按下输出高电平)

5脚为Scroll Lock指示(按下输出高电平)

参数设置AT 指令

AT+BAUD?\r 查询波特率

AT+BAUD=115200\r 设置波特率

AT+NAME?\r 查询本地名称

AT+NAME=xxxxxxxx\r (小于20字节) 设置本地名称

AT+VERSION?\r 查询版本号

AT+DFU\r 进入升级模式

二.时序图

1. 外部处理器置30脚高电平。

2. 置30脚PIO5高电平后至少延时10ms 后,外部处理器开始发送UART 数据。

3. 外部处理器发送完数据后延时10ms ,置30脚低电平。

注:没有数据发送时,一定要将PIO5置低电平,否则会增加蓝牙模组的功耗,从而缩短电池使用寿命。

三.数据包格式 BYTE1

BYTE2

BYTE3

BYTE4

BYTE5

BYTE6

BYTE7

BYTE8

BYTE9

BYTE10

BYTE11

BYTE12。

单片机引脚与指令

《单片机引脚图》单片机引脚图40个引脚按引脚功能大致可分为4个种类:电源、时钟、控制和I/O引脚。

⒈电源:⑴ VCC - 芯片电源,接+5V;⑵ VSS - 接地端;注:用万用表测试单片机引脚电压一般为0v或者5v,这是标准的TTL电平。

但有时候在单片机程序正在工作时候测试结果并不是这个值而是介于0v-5v之间,其实这是万用表的响应速度没这么快而已,在某一个瞬间单片机引脚电压仍保持在0v或者5v。

⒉时钟:XTAL1、XTAL2 - 晶体振荡电路反相输入端和输出端。

⒊控制线:控制线共有4根,⑴ ALE/PROG:地址锁存允许/片内EPROM编程脉冲① ALE功能:用来锁存P0口送出的低8位地址② PROG功能:片内有EPROM的芯片,在EPROM编程期间,此引脚输入编程脉冲。

⑵ PSEN:外ROM读选通信号。

⑶ RST/VPD:复位/备用电源。

① RST(Reset)功能:复位信号输入端。

② VPD功能:在Vcc掉电情况下,接备用电源。

⑷ EA/Vpp:内外ROM选择/片内EPROM编程电源。

① EA功能:内外ROM选择端。

② Vpp功能:片内有EPROM的芯片,在EPROM编程期间,施加编程电源Vpp。

⒋ I/O线80C51共有4个8位并行I/O端口:P0、P1、P2、P3口,共32个引脚。

P3口还具有第二功能,用于特殊信号输入输出和控制信号(属控制总线)5. P3口第二功能P30 RXD 串行输入口P31 TXD 串行输出口P32 INT0 外部中断0(低电平有效)P33 INT1 外部中断1(低电平有效)P34 T0 定时计数器0 P35 T1 定时计数器1P36 WR 外部数据存储器写选通(低电平有效)P37 RD 外部数据存储器读选通(低电平有效)单片机指令功能一览表一、传送操作助记符代码说明MOV A,Rn E8~EF 寄存器AMOV A,direct E5 direct 直接字节送AMOV A,@Ri ER~E7 间接RAM送AMOV A,#data 74 data 立即数送AMOV Rn,A F8~FF A送寄存器MOV Rn,direct A8~AF direct 直接字节送寄存器MOV Rn,#data 78~7F data 立即数送寄存器MOV direct,A F5 direct A送直接字节MOV direct,Rn 88~8F direct 寄存器送直接字节MOV direct1,direct2 85 direct1 direct2 直接字节送直接字节MOV direct,@Ro 86~87 间接RAM送直接字节MOV direct,#data 75 direct data 立即数送直接字节MOV @Ri,A F6~F7 A送间接RAMMOV @Ri,direct 76~77 direct 直接字节送间接RAMMOV @Ri,#data 76~77 data 立即数送间接RAMMOV DPTR,#data16 90 data 15~8 16位常数送数据指针data7~0MOVC A,@A+DPTR 93 由((A)+(DPTR))寻址的程序存贮器字节选A MOVC A,@A+PC 83 由((A)+(PC));寻址的程序存贮器字节送A MOVX A,@Ri E2~E3 送外部数据(8位地址)送AMOVX A,@DPTR E0 送外部数据(16位地址)送AMOVX @Ri,A F2~F3 A送外部数据(8位地址)MOVX @DPTR,A F0 A送外部数据(16位地址)PUSH direct C0 direct 直接字节进栈,SP加1POP direct D0 direct 直接字节退栈,SP减1XCH A,Rn C8~CF 交换A和寄存器XCH A,direct C5 direct 交换A和直接字节XCH A,@Ri C6~C7 交换A和间接RAMXCH A,@Ri D6~D7 交换A和间接RAM的低位SWAP A C4二、算术操作(A的二个半字节交换)ADD A,Rn 28~2F 寄存器加到AADD A,direct 25 direct 直接字节加到AADD A,@Ri 26~27 间接RAM加到AADD A,#data 24data 立即数加到AADD A,Rn 38~3F 寄存器和进位位加到AADD A,direct 35direct 直接字节和进位位加到A ADD A,@Ri 36~37 间接字节和进位位加到AADD A,data 34 data 立即数和进位位加到AADD A,Rn 98~9F A减去寄存器和进位位ADD A,direct 95 direct A减去直接字节和进位位ADD A,@Ri 36~37 间接RAM和进位位加到A ADD A,data 34 data 立即数和进位位加到ASUBB A,Rn 98~9F A减去寄存器和进位位SUBB A,direct 95 direct A减去直接字节和进位位SUBB A,@Ri 96~97 A减去间接RAM和进位位SUBB A,#data 94 data A减去立即数和进位位INC A 04 A加1INC Rn 08~0F 寄存器加1INC direct 05 direct 直接字节加1INC @Ri 06~07 间接RAM加1DEC A 14 A减1DEC Rn 18~1F 寄存器减1DEC direct 15 direct 直接字节减1DEC @Ri 16~17 间接RAM减1INC DPTR A3 数据指针加1MUL AB A4 A乘以BDIV AB 84 A除以BDA A D4 A的十进制加法调整三、逻辑操作ANL A,Rn 58~5F 寄存器“与”到AANL A,direct 55 direct 直接字节“与”到AANL A,@Ri 56~57 间接RAm“与”到AANL A,#data 54 data 立即数“与”到AANL direct A 52 direct A“与”到直接字节ANL direct,#data 53 direct data 立即数“与”到直接字节ORL A,Rn 48~4F 寄存器“或”到AORL A,direct 45 direct 直接字节“或”到AORL A,@Ri 46~47 间接R AM“或”到AORL A,#data 44 data 立即数“或”到AORL direct,A 42 direct A“或”到直接字节ORL direct,#data 43 direct data 立即数“或”到直接字节XRL A,Rn 68~6F 寄存器“异或”到AXRL A,direct 65 direct 直接字节“异或”到AXRL A,@Ri 66~67 间接RAM“异或”到AXRL A,#data 64 data 立即数“异或”到AX RL direct A 62 direct A“异或”到直接字节XRL direct,#data 63 direct data 立即数“异或”到直接字节CLR A E4 清零CPL A F4 A取反RL A 23 A左环移RLC A 33 A通过进位左环移RR A 03 A右环移RRC A 13 A通过进位右环移四、控制程序转移ACALL addr 11 *1 addr(a7~a0) 绝对子程序调用LCALL addr 16 12 addr(15~8) 长子程序调用addr(7~0)RET 22 子程序调用返回RETI addr 11 32 中断调用返回AJMP addr 11 △1 addr(a7~a6) 绝对转移LJMP addr 16 02addr(15~8) 长转移addr(7~0)SJMP rel 80 rel 短转移,相对转移JMP @A+DPTR 73 相对于DPTR间接转移JZ rel 60 rel A为零转移JNZ rel 70 rel A为零转移CJNE A,direct,rel B5 direct rel 直接字节与A比较,不等则转移CJNE A,#data,rel B4 data rel 立即数与A比较,不等则转移CJNE A,Rn,#data,rel B8~BF data rel 立即数与寄存器比较,不等则转移CJNE @Ri,#data,rel B6~B7 data rel 立即数与间接RAM比较,不等则转移DJNZ Rn,rel D8~DF rel 寄存器减1,不为零则转移DJNZ direct,rel B5 direct rel 直接字节减1,不为零则转移NOP 00 空操作*=a10a9a8l△=a10a9a80五、布尔变量操作CLR C C3 清零进位CLR bit C2 清零直接位SETB C D3 置位进位SETB bit D2 置位直接位CPL C B3 进位取反CPL bit B2 直接位取反ANL C,bit 82 dit 直接数“与”到进位ANL C,/bit B0 直接位的反“与”到进位ORL C,bit 72 bit 直接位“或”到进位ORL C,/bit A0 bit 直接位的反“或”到进位MOV C,bit A2 bit 直接位送进位MOV bit,C 92 bit 进位送直接位JC rel 40 rel 进位位为1转移JNC rel 50 rel 进位位为0转移JB bit,rel 20 bit rel 直接位为1相对转移JNB bit,rel 30 bit rel 直接位为0相对转移JBC bit,rel 10 bit rel 直接位为1相对转移,然后清零该位。

CC2530引脚描述

引脚描述引脚名称引脚引脚类型描述AVDD1 28 电源(模拟)2-V–3.6-V 模拟电源连接AVDD2 27 电源(模拟)2-V–3.6-V 模拟电源连接AVDD3 24 电源(模拟)2-V–3.6-V 模拟电源连接AVDD4 29 电源(模拟)2-V–3.6-V 模拟电源连接AVDD5 21 电源(模拟)2-V–3.6-V 模拟电源连接AVDD6 31 电源(模拟)2-V–3.6-V 模拟电源连接DCOUPL 40 电源(数字) 1.8V 数字电源去耦。

不使用外部电路供应。

DVDD1 39 电源(数字)2-V–3.6-V 数字电源连接DVDD2 10 电源(数字)2-V–3.6-V 数字电源连接GND - 接地接地衬垫必须连接到一个坚固的接地面。

GND 1,2,3,4 未使用的引脚连接到GNDP0_0 19 数字I/O 端口0.0P0_1 18 数字I/O 端口0.1P0_2 17 数字I/O 端口0.2P0_3 16 数字I/O 端口0.3P0_4 15 数字I/O 端口0.4P0_5 14 数字I/O 端口0.5P0_6 13 数字I/O 端口0.6P0_7 12 数字I/O 端口0.7P1_0 11 数字I/O 端口1.0-20-mA 驱动能力P1_1 9 数字I/O 端口1.1-20-mA 驱动能力P1_2 8 数字I/O 端口1.2P1_3 7 数字I/O 端口1.3P1_4 6 数字I/O 端口1.4P1_5 5 数字I/O 端口1.5P1_6 38 数字I/O 端口1.6P1_7 37 数字I/O 端口1.7P2_0 36 数字I/O 端口2.0P2_1 35 数字I/O 端口2.1P2_2 34 数字I/O 端口2.2P2_3 33 数字I/O 模拟端口2.3/32.768 kHz XOSCP2_4 32 数字I/O 模拟端口2.4/32.768 kHz XOSCRBIAS 30 模拟I/O 参考电流的外部精密偏置电阻RESET_N 20 数字输入复位,活动到低电平RF_N 26 RF I/O RX 期间负RF 输入信号到LNAc c2530功能引脚图RF_P 25 RF I/O RX 期间正RF 输入信号到LNAXOSC_Q1 22 模拟I/O 32-MHz 晶振引脚1或外部时钟输入XOSC_Q2 23 模拟I/O 32-MHz 晶振引脚23功能介绍·RF/布局–适应2.4-GHz IEEE 802.15.4 的RF 收发器–极高的接收灵敏度和抗干扰性能–可编程的输出功率高达4.5 dBm–只需极少的外接元件–只需一个晶振,即可满足网状网络系统需要–6-mm ×6-mm 的QFN40 封装–适合系统配置符合世界范围的无线电频率法规:ETSI EN 300 328 和EN 300440(欧洲),FCC CFR47 第15 部分(美国)和ARIB STD-T-66(日本)·低功耗–主动模式RX(CPU 空闲):24 mA–主动模式TX 在1dBm(CPU 空闲):29mA–供电模式1(4 μs 唤醒):0.2 mA–供电模式2(睡眠定时器运行):1 μA–供电模式3(外部中断):0.4 μA–宽电源电压范围(2 V–3.6 V)·微控制器–优良的性能和具有代码预取功能的低功耗8051 微控制器内核–32-、64-或128-KB 的系统内可编程闪存–8-KB RAM,具备在各种供电方式下的数据保持能力–支持硬件调试·外设–强大的5 通道DMA–IEEE 802.5.4 MAC 定时器,通用定时器(一个16 位定时器,一个8 位定时器)–IR 发生电路–具有捕获功能的32-kHz 睡眠定时器–硬件支持CSMA/CA–支持精确的数字化RSSI/LQI–电池监视器和温度传感器–具有8 路输入和可配置分辨率的12 位ADC–AES 安全协处理器–2 个支持多种串行通信协议的强大USART–21 个通用I/O 引脚(19×4 mA,2×20 mA)–看门狗定时器4运行条件cc2530在此条件下运行能达到最好的效果。

IC各脚功能

IC各脚功能.txt婚姻是键盘,太多秩序和规则;爱情是鼠标,一点就通。

男人自比主机,内存最重要;女人好似显示器,一切都看得出来。

【1】运放4558D(8脚)1:AMP OUT1 放大信号输出(1)2:IN1- 反相信号输入(1)3:IN1+ 同相信号输入(1)4:GND 接地5:IN2+ 同相信号输入(2)6:IN2- 反相信号输入(2)7:AMP OUT2 放大信号输出(2)8:Vcc 电源【2】功放TDA2822(8脚)1脚3脚左右输出5脚8脚左右反馈2脚4脚正负电源6脚7脚左右输入【3】音频处理SC7313与TM2313,用于车载影音系统(28脚)3路输入4声道输出【4】汽车专用4声道*40W集成运放驱动的OCL功放TDA7388与TDA7386(25脚)注:可用 7381 7382,TB2929HQ……7388和7850等多款IC,(此系列IC仅在于最后一个数字不同,功率不一样,而线路通用)11,12,14,15脚是输入端3,5脚后左7.9脚前左17.19脚前右21.23脚后右22脚:静音(此脚断会通电杂)【5】GPS模块各脚分布(32脚)注:天线处电压:3到3.3V1脚:右声道R2脚:左声道L3脚:地4脚:VB(蓝)5脚:VG(绿)6脚:VR(红)7脚:HS(开路白屏)8至11脚:空12:地13:DET(音频检测)14:空15:RST(复位)16:TXD(触摸)17至20:空21:D122:D223:CLK24:3V325:DEL26:CMD27:D328:D2【21到28是卡座】29至30:地31:ACC记忆32:电源B正(12V)【6】TM2313音频处理【7】BD3702音频处理【8】收音模块4730(24脚)1脚:dout(空,英文nc表示空)2脚: dfs(空)3脚:GPO3/DCLK(晶振脚)4脚:GPO2/INT(地)5脚:GPO1(电源串联1k接过来的电压)6脚至7脚:空8脚: FM天线9脚:RF天线(GND)10脚至11脚:空12脚 :AM天线13脚至14脚:GND15脚:RST(复位脚)16脚:SEN(通常接地)17脚:SCLK18脚:SDIO(DATA)19脚:RCLK(晶振脚)20脚至21脚:电源脚(VCC3.3V)22脚:GND23脚:音频(R)《通常用AR表示,全英文AUDIO即是AR》24脚:音频(L)《通常用AL表示,全英文AUDIO即是AL》【9】视频fms6502【10】SD卡(共9脚)(全名:SecureDigitalCard简称大卡)—安全数码卡1脚:CD DAT3 I/O/PP 卡监测数据位32脚:CMD PP 命令/回复3脚:Vss S 地4脚:Vcc S 供电电压【额定2.7至3.6V,一般机做定在3.3V】5脚:CLK I 时钟6脚:Css2 S 地7脚:DAT0 I/O/PP 数据位08脚:DAT1 I/O/PP 数据位19脚:DAT2 I/O/PP 数据位2注:TF卡(共8脚)(全名:TransFLash简称小卡,引脚定义同SD卡:只少一根地线,其它相同备注:TF卡可经SD卡套转换器后,当SD卡使用。

picf引脚以及功能介绍图文稿

p i c f引脚以及功能介绍 Company number【1089WT-1898YT-1W8CB-9UUT-92108】PIC12F18228引脚8 位闪存单片机产品简介高性能RISC CPU:只需学习49 条指令工作速度:- DC——时钟输入为32 MHz- DC——指令周期为125 ns带自动现场保护的中断功能带可选上溢/ 下溢复位的16 级深硬件堆栈直接、间接和相对寻址模式:- 两个完整的16 位文件选择寄存器(FileSelect Register, FSR)- FSR可读程序和数据寄存器单片机特性:高精度内部振荡器:- 出厂时校准为% (典型值)- 软件可选择频率范围为32 MHz 至31 kHz31kHz低功耗内部振荡器外部振荡器电路,具有:- 4种晶振/ 谐振器模式,频率最高为32 MHz,采用 4x PLL- 3种外部时钟模式,频率最高为32 MHz4倍频锁相环(Phase Locked Loop, PLL)故障保护时钟监视器双速启动节能的休眠模式上电复位(Power-on Reset,POR)上电延时定时器(Power-up Timer, PWRT)振荡器启动定时器(Oscillator Start-Up Timer,OST)带可选择跳变点的欠压复位(Brown-out Reset,BOR)扩展型看门狗定时器(Watchdog Timer, WDT)通过两个引脚进行在线串行编程(In-CircuitSerial ProgrammingTM ,ICSPTM)通过两个引脚进行的在线调试(In-CircuitDebug, ICD)增强型低电压编程(Low-Voltage Programming,LVP)工作电压范围:- 1.8V至3.6V (PIC1XLF182X)- 1.8V至5.5V (PIC1XF182X)可编程代码保护可在软件控制下自编程低功耗特性:待机电流(PIC1XLF182X):- 1.8V时,典型值为30 nA工作电流(PIC1XLF182X):- 1MHz, 1.8V 时,典型值为75 mA 低功耗看狗定时器电流(PIC1XLF182X):- 1.8V时,典型值为500 nA 外设特性:最多17 个I/O 引脚和1 个仅用作输入的引脚:- 高拉/ 灌电流可直接驱动LED- 独立的可编程电平变化中断引脚- 独立的可编程弱上拉Timer0:带8 位可编程预分频器的8 位定时器/ 计数器增强型Timer1:- 带预分频器的16 位定时器/ 计数器- 外部门控输入模式- 专用的低功耗32 kHz 振荡器驱动器3个Timer2 模块(Timer2、4 和6):带8 位周期寄存器、预分频器和后分频器的8 位定时器/ 计数器2个增强型捕捉/ 比较/PWM (EnhancedCapture/Compare/PWM, ECCP)模块:- 可由软件选择的时基- 自动关断和自动重启- PWM转向控制2个捕捉/ 比较/PWM(Capture/Compare/PWM, CCP)模块:- 可由软件选择的时基2个带SPI 和I2CTM 的主同步串行端口(Master Synchronous Serial Port,MSSP),具有:- 7位地址掩码- 兼容SMBus/PMBusTM增强型通用同步异步收发器(EnhancedUniversal Synchronous Asynchronous Receiver Transmitter, EUSART):- 兼容RS-232、RS-485 和LIN- 自动波特率检测- 遇到启动位时自动唤醒SR锁存器(集成555 定时器):- 多个置1/ 复位输入选项模数转换器(Analog-to-Digital Converter,ADC):- 10位分辨率- 12路通道2个比较器:- 轨对轨输入/ 输出- 电压模式控制- 软件可控的滞回电压参考电压模块:- 固定参考电压(Fixed Voltage Reference,FVR),具有1.024V、2.048V 和4.096V 的输出电压- 可选正负参考电压的5 位轨对轨阻式DAC电容触摸振荡器模块:- 12 路通道数据信号调制器:- 从不同的模块输出选择调制器和载波源。

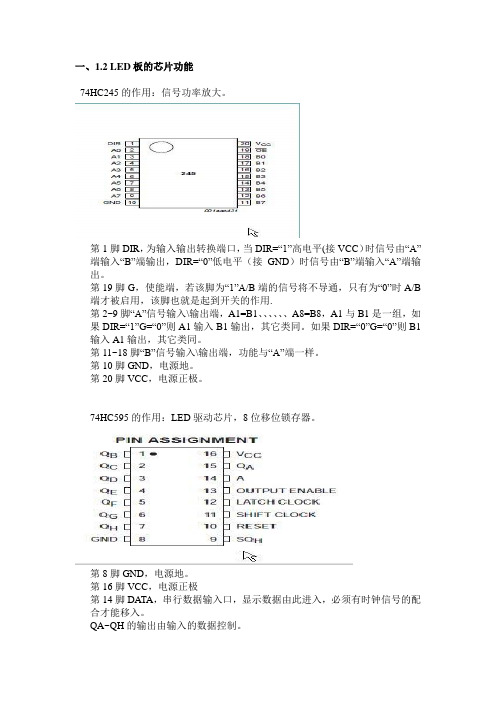

LED显示屏各芯片管脚定义汇总

一、1.2 LED板的芯片功能74HC245的作用:信号功率放大。

第1脚DIR,为输入输出转换端口,当DIR=“1”高电平(接VCC)时信号由“A”端输入“B”端输出,DIR=“0”低电平(接GND)时信号由“B”端输入“A”端输出。

第19脚G,使能端,若该脚为“1”A/B端的信号将不导通,只有为“0”时A/B 端才被启用,该脚也就是起到开关的作用.第2~9脚“A”信号输入\输出端,A1=B1、、、、、、A8=B8,A1与B1是一组,如果DIR=“1”G=“0”则A1输入B1输出,其它类同。

如果DIR=“0”G=“0”则B1输入A1输出,其它类同。

第11~18脚“B”信号输入\输出端,功能与“A”端一样。

第10脚GND,电源地。

第20脚VCC,电源正极。

74HC595的作用:LED驱动芯片,8位移位锁存器。

第8脚GND,电源地。

第16脚VCC,电源正极第14脚DATA,串行数据输入口,显示数据由此进入,必须有时钟信号的配合才能移入。

QA~QH的输出由输入的数据控制。

第12脚STB,锁存端,当输入的数据在传入寄存器后,只有供给一个锁存信号才能将移入的数据送QA~QH口输出。

第11脚CLK,时钟端,每一个时钟信号将移入一位数据到寄存器。

第10脚SCLR,复位端,只要有复位信号,寄存器内移入的数据将清空,显示屏不用该脚,一般接VCC。

第9脚DOUT,串行数据输出端,将数据传到下一个。

第15、1~7脚,并行输出端也就是驱动输出端,驱动LED。

HC16126\TB62726的作用:LED驱动芯片,16位移位锁存器。

备注:HC16126驱动芯片定义和5020,5024,2016等芯片一样第1脚GND,电源地。

第24脚VCC,电源正极第2脚DATA,串行数据输入第3脚CLK,时钟输入第4脚STB,锁存输入第23脚输出电流调整端,接电阻调整第22脚DOUT,串行数据输出第21脚EN,使能输入其它功能与74HC595相似,只是TB62726是16位移位锁存器,并带输出电流调整功能,但在并行输出口上不会出现高电平,只有高阻状态和低电平状态。

管脚分配

时钟CLK 50MHZ PIN_12PIN_14CLK2PIN_62CLK3PIN_64K1PIN_55K2PIN_56K3PIN_57K4PIN_58K1 RESET 12345PIN_55和K1复用6PIN_56和K2复用7PIN_57和K3复用8PIN_58和K4复用D10PIN_73D11PIN_72D12PIN_71D13PIN_70D14PIN_69D15PIN_68D16PIN_67D17PIN_66D2PIN_44D3PIN_5D4PIN_4D5PIN_3D6PIN_2D7PIN_1D8PIN_100D9PIN_99LED0PIN_74LED1PIN_7516个LED发光二极管 变成的时候,LED灯的命名你可以随便写其他的,不影响。

8位动态数码管 LED0代表最右边的一位,LED7代表最左边的一位Dynamic LEDPIN_19PIN_20PIN_21PIN_27深圳市21EDA电子 C-M2FB开发板管脚分配表官方论坛: 官方网站:预留一个时钟焊盘8个拨码开关,5678是分别和K1K2K3K4复用的核心板上面的1个按键底板上面的4个按键,4个按键和4个拨码开5678关复用PIN_44LED3PIN_77LED4PIN_78LED5PIN_81LED6PIN_82LED7PIN_83LED_A PIN_73LED_B PIN_72LED_C PIN_71LED_D PIN_70LED_E PIN_69LED_F PIN_68LED_G PIN_67LED_H PIN_66Dot LedDZ0PIN_73DZ1PIN_72DZ2PIN_71DZ3PIN_70DZ4PIN_69DZ5PIN_68DZ6PIN_67DZ7PIN_66EN0PIN_74EN1PIN_75来定EN2PIN_76EN3PIN_77EN4PIN_78EN5PIN_81EN6PIN_82EN7PIN_83PS/2DATA PIN_55PS/2 CLK PIN_56LCDRS PIN_75LCDWR PIN_76LCDEN PIN_74LCD_D0PIN_66上到下,也可以从下到上扫描,根据自己的情况点阵的段码,这里用户需要注意,应为点阵他是一排一排的,左右对称,段码可以是段码可以是从PIN41到PIN53,也可以PIN53到PIN41根据你自己的程序来定义点阵的行使能端口下面是数码管的段码,段码和8个LED灯复用的。

单片机的引脚原理图及说明

一、P0端口的结构及工作原理P0端口8位中的一位结构图见下图:由上图可见,P0端口由锁存器、输入缓冲器、切换开关、一个与非门、一个与门及场效应管驱动电路构成。

再看图的右边,标号为P0.X引脚的图标,也就是说P0.X引脚可以是P0.0到P0.7的任何一位,即在P0口有8个与上图相同的电路组成。

下面,我们先就组成P0口的每个单元部份跟大家介绍一下:先看输入缓冲器:在P0口中,有两个三态的缓冲器,在学数字电路时,我们已知道,三态门有三个状态,即在其的输出端可以是高电平、低电平,同时还有一种就是高阻状态(或称为禁止状态),大家看上图,上面一个是读锁存器的缓冲器,也就是说,要读取D锁存器输出端Q的数据,那就得使读锁存器的这个缓冲器的三态控制端(上图中标号为‘读锁存器’端)有效。

下面一个是读引脚的缓冲器,要读取P0.X引脚上的数据,也要使标号为‘读引脚’的这个三态缓冲器的控制端有效,引脚上的数据才会传输到我们单片机的内部数据总线上。

D锁存器:构成一个锁存器,通常要用一个时序电路,时序的单元电路在学数字电路时我们已知道,一个触发器可以保存一位的二进制数(即具有保持功能),在51单片机的32根I/O口线中都是用一个D触发器来构成锁存器的。

大家看上图中的D锁存器,D端是数据输入端,CP是控制端(也就是时序控制信号输入端),Q是输出端,Q非是反向输出端。

对于D触发器来讲,当D输入端有一个输入信号,如果这时控制端CP没有信号(也就是时序脉冲没有到来),这时输入端D的数据是无法传输到输出端Q及反向输出端Q非的。

如果时序控制端CP的时序脉冲一旦到了,这时D 端输入的数据就会传输到Q及Q非端。

数据传送过来后,当CP时序控制端的时序信号消失了,这时,输出端还会保持着上次输入端D的数据(即把上次的数据锁存起来了)。

如果下一个时序控制脉冲信号来了,这时D端的数据才再次传送到Q端,从而改变Q端的状态。

多路开关:在51单片机中,当内部的存储器够用(也就是不需要外扩展存储器时,这里讲的存储器包括数据存储器及程序存储器)时,P0口可以作为通用的输入输出端口(即I/O)使用,对于8031(内部没有ROM)的单片机或者编写的程序超过了单片机内部的存储器容量,需要外扩存储器时,P0口就作为‘地址/数据’总线使用。

SMT常见元件方向识别

红圈内铜箔为IC 的方向标识红圈内<为IC 的方向及IC 的红圈内缺口为IC 的方向标识及IC的起始脚。

起始脚。

及IC 的起始脚位置。

蓝圈内三角形为PCB 上IC 方蓝圈内三角形为PCB 上IC 方蓝圈内三角形为PCB 上IC 第向标识。

向标识。

一脚标记。

表示符号晶体发光二极管(LED )铝电解电容钽电容斜角缺口是方向,左红框为负极(K )红框内标记为铝电容的坚条表示钽电容的正极下角为起始第一脚。

蓝框内为PCB 上极性标负极。

注意:钽电容的表示方示;正极(A )表示。

法与二极管相反。

表示符号表示符号圆柱型二极管(DIODE )复合三极管(QA )SOP 封装QFP 封装坚条表示二极管的负极顺着丝印看,元件左下这种封装默认左下角为IC 丝印无特别标记,一角是第一脚。

起始第一脚。

上图圆点般左下方为第一脚。

是起始脚标记。

红圈内的圆点为方向,场效应管(FET/JFET )插座(CONNECT )左下角是起始脚。

字体丝印为方向,贴装倒角缺口表示方向和起方向要与图纸标的字体始脚位置。

方向一致。

SMT常见元件方向识别脚明显较宽,是第一脚。

图纸上第一脚标示第一脚标图纸上对应的第一脚符号TSOP 封装这种封装IC ,默认左上整流桥TQFP 封装晶体角为起始第一脚。

上图整流桥的输出端分正、左上角是起始第一脚。

缺口为晶体方向,晶体丝印▼是表示IC 起始脚负端。

左下角第一脚是起始脚位置。

符号或用或用钽电容钽电容坚条表示钽电容的正极电容有突出尖角的一端二极管(DIODE )圆柱型二极管注意:钽电容的表示方为正极。

坚条丝印表示二极的负坚条丝印表示二极的负法与二极管相反。

极。

极。

TQFP 封装SOP 封装SOP 封装SOIC 封装IC 左下角为方向和第一默认左下角为第一脚。

默认左下角为第一脚。

默认左下角为第一脚。

脚标记。

IC 丝印坚条表示方向,缺口表示IC 方向,缺口顺着丝印看,IC 左下角左下角为起始第一脚。

下方左起为第一脚。

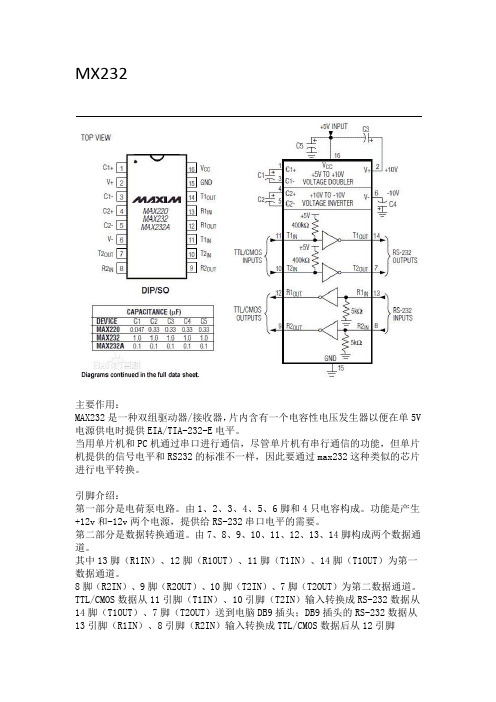

芯片引脚说明

MX232主要作用:MAX232是一种双组驱动器/接收器,片内含有一个电容性电压发生器以便在单5V 电源供电时提供EIA/TIA-232-E电平。

当用单片机和PC机通过串口进行通信,尽管单片机有串行通信的功能,但单片机提供的信号电平和RS232的标准不一样,因此要通过max232这种类似的芯片进行电平转换。

引脚介绍:第一部分是电荷泵电路。

由1、2、3、4、5、6脚和4只电容构成。

功能是产生+12v和-12v两个电源,提供给RS-232串口电平的需要。

第二部分是数据转换通道。

由7、8、9、10、11、12、13、14脚构成两个数据通道。

其中13脚(R1IN)、12脚(R1OUT)、11脚(T1IN)、14脚(T1OUT)为第一数据通道。

8脚(R2IN)、9脚(R2OUT)、10脚(T2IN)、7脚(T2OUT)为第二数据通道。

TTL/CMOS数据从11引脚(T1IN)、10引脚(T2IN)输入转换成RS-232数据从14脚(T1OUT)、7脚(T2OUT)送到电脑DB9插头;DB9插头的RS-232数据从13引脚(R1IN)、8引脚(R2IN)输入转换成TTL/CMOS数据后从12引脚(R1OUT)、9引脚(R2OUT)输出。

第三部分是供电。

15脚GND、16脚VCC(+5v)。

JTAG141,13接电源2,4,6,8,10,14 GND接地3mode 模式选择5mosi主输出从输入7mrst 主复位9sck 同步时钟11miso 主出入从输出Atmegal16VCC 电源正GND 电源地端口A(PA7..PA0) 端口A 做为A/D 转换器的模拟输入端。

端口A 为8 位双向I/O 口,具有可编程的内部上拉电阻。

其输出缓冲器具有对称的驱动特性,可以输出和吸收大电流。

作为输入使用时,若内部上拉电阻使能,端口被外部电路拉低时将输出电流。

在复位过程中,即使系统时钟还未起振,端口A 处于高阻状态。

端口B(PB7..PB0) 端口B 为8 位双向I/O 口,具有可编程的内部上拉电阻。

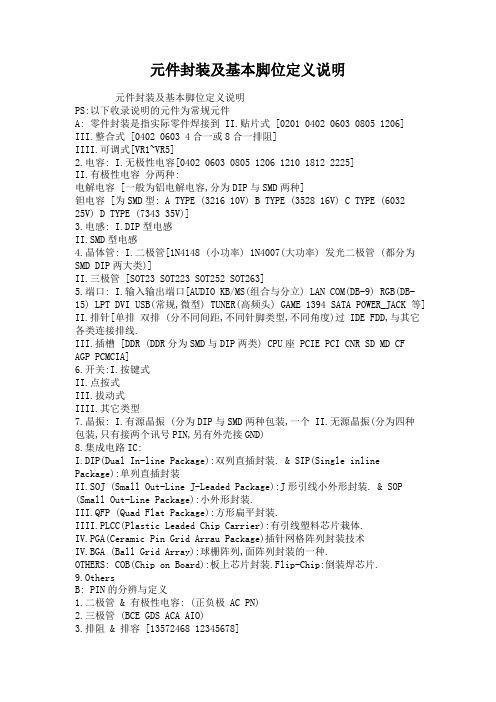

元件封装及基本脚位定义说明.

元件封装及基本脚位定义说明元件封装及基本脚位定义说明PS:以下收录说明的元件为常规元件A: 零件封装是指实际零件焊接到 II.贴片式 [0201 0402 0603 0805 1206]III.整合式 [0402 0603 4合一或8合一排阻]IIII.可调式[VR1~VR5]2.电容: I.无极性电容[0402 0603 0805 1206 1210 1812 2225]II.有极性电容分两种:电解电容 [一般为铝电解电容,分为DIP与SMD两种]钽电容 [为SMD型: A TYPE (3216 10V) B TYPE (3528 16V) C TYPE (603225V) D TYPE (7343 35V)]3.电感: I.DIP型电感II.SMD型电感4.晶体管: I.二极管[1N4148 (小功率) 1N4007(大功率) 发光二极管 (都分为SMD DIP两大类)]II.三极管 [SOT23 SOT223 SOT252 SOT263]5.端口: I.输入输出端口[AUDIO KB/MS(组合与分立) LAN COM(DB-9) RGB(DB-15) LPT DVI USB(常规,微型) TUNER(高频头) GAME 1394 SATA POWER_JACK等] II.排针[单排双排 (分不同间距,不同针脚类型,不同角度)过 IDE FDD,与其它各类连接排线.III.插槽 [DDR (DDR分为SMD与DIP两类) CPU座 PCIE PCI CNR SD MD CF AGP PCMCIA]6.开关:I.按键式II.点按式III.拔动式IIII.其它类型7.晶振: I.有源晶振 (分为DIP与SMD两种包装,一个 II.无源晶振(分为四种包装,只有接两个讯号PIN,另有外売接GND)8.集成电路IC:I.DIP(Dual In-line Package):双列直插封装. & SIP(Single inline Package):单列直插封装II.SOJ (Small Out-Line J-Leaded Package):J形引线小外形封装. & SOP (Small Out-Line Package):小外形封装.III.QFP (Quad Flat Package):方形扁平封装.IIII.PLCC(Plastic Leaded Chip Carrier):有引线塑料芯片栽体.IV.PGA(Ceramic Pin Grid Arrau Package)插针网格阵列封装技术IV.BGA (Ball Grid Array):球栅阵列,面阵列封装的一种.OTHERS: COB(Chip on Board):板上芯片封装.Flip-Chip:倒装焊芯片.9.OthersB: PIN的分辨与定义1.二极管 & 有极性电容: (正负极 AC PN)2.三极管 (BCE GDS ACA AIO)3.排阻 & 排容 [13572468 12345678]4.排针 [主要分两种:1357.... 2468... 12345678...]5.集成电路:集成电路的封装大都是对称式的,如果不在集成电路封装上设立PIN识别标示,则非常容易错接,反接等差错,使产品设计失败.6.OTHERS 一般常见端口PIN定义此项技能考核参考说明:技能要求:B级B项基本熟悉各种元件封装以及基本脚位定义等考题要求:说明十个各不相同元件的名称与特点,由考核者在公司电脑中抓取新建一个线路图,抓取十个有特殊脚位定义封装,更改PIN定义与PIN连接讯号后,请考核者CHECK并改为正确定义.考核标准:按考核题目要求抓取十个各不相同元件,要求全部正确,如对所抓元件有疑问可另行说明,如所抓取元件错误,此项不通过(元件抓取错误但有说明合理原因除外) 按考核题目要求对十个PIN定义错误元件进行更改,如对元件PIN定义有疑问可另行说胆,如更改后PIN定义还是错误,此项不通过(更改后PIN定义错误, 但有说明合理原因除外)说明:抓取正确的元件封装与新建元件同样重要,故不允许出错.如说明原因不容易界定者可安排重考.附1: 集成电路封装说明:DIP封装DIP封装(Dual In-line Package),也叫双列直插式封装技术,指采用双列直插形式封装的集成电路芯片,绝大多数中小规模集成电路均采用这种封装形式,其引脚数一般不超过100.DIP封装的IC芯片有两排引脚,需要插入到具有DIP结构的芯片插座上.当然,也可以直接插在有相同焊孔数和几何排列的电路板上进行焊接.DIP封装的芯片在从芯片插座上插拔时应特别小心,以免损坏管脚.DIP封装结构形式有:多层陶瓷双列直插式DIP,单层陶瓷双列直插式DIP,引线框架式DIP(含玻璃陶瓷封接式,塑料包封结构式,陶瓷低熔玻璃封装式)等.DIP封装具有以下特点:1.适合在PCB(印刷电路板)上穿孔焊接,操作方便.2.芯片面积与封装面积之间的比值较大,故体积也较大QFP封装中文含义叫方型扁平式封装技术(Plastic Quad Flat Pockage),该技术实现的芯片引脚之间距离很小,管脚很细,一般大规模或超大规模集成电路采用这种封装形式,其引脚数一般都在100以上.该技术封装IC时操作方便,可靠性高;而且其封装外形尺寸较小,寄生参数减小,适合高频应用;该技术主要适合用SMT表面安装技术在PCB上安装布线PGA封装中文含义叫插针网格阵列封装技术(Ceramic Pin Grid Arrau Package),由这种技术封装的芯片内外有多个方阵形的插针,每个方阵形插针沿芯片的四周间隔一定距离排列,根据管脚数目的多少,可以围成2~5圈.安装时,将芯片插入专门的PGA插座.该技术一般用于插拔操作比较频繁的场合之下BGA封装BGA技术(Ball Grid Array Package)即球栅阵列封装技术.该技术的出现便成为CPU,主板南,北桥芯片等高密度,高性能,多引脚封装的最佳选择.但BGA封装占用基板的面积比较大.虽然该技术的I/O引脚数增多,但引脚之间的距离远大于QFP,从而提高了组装成品率.而且该技术采用了可控塌陷芯片法焊接,从而可以改善它的电热性能.另外该技术的组装可用共面焊接,从而能大大提高封装的可靠性;并且由该技术实现的封装IC信号传输延迟小,适应频率可以提高很大. BGA封装具有以下特点:1.I/O引脚数虽然增多,但引脚之间的距离远大于QFP封装方式,提高了成品率2.虽然BGA的功耗增加,但由于采用的是可控塌陷芯片法焊接,从而可以改善电热性能3.信号传输延迟小,适应频率大大提高4.组装可用共面焊接,可靠性大大提高附2:元件实物图图表 1 TSSOP图表 2 TSOP图表 3 to-220图表 4 TO263图表 5 TO92图表 6 TO18图表 7 SSOP图表 8 SOT523图表 9 SOT343图表 10 SOT252图表 11 SOT223图表 12 SOT143图表 13 sot89图表 14 sot26图表 15 sot23图表 16 SOT23-5图表 17 SOP图表 18 SOJ图表 19 SOCKET603图表 20 SO图表 21 SIP图表 22 SDIP图表 23 QFP图表 24 PQFP图表 25 PLCC图表 26 PGA图表 27 PGA图表 28 HSOP图表 29 DIP-DIP_TAB图表 30 CNR图表 31 CLCC图表 32 BGA图表 33 BEAD图表 34 168-DIMM。