SOPCNIOSII开发流程(精)

sopc开发流程

实验一一、实验目的1.掌握用 Quartus II 开发 SOPC 的基本流程。

2.掌握用 SOPC Builder 进行 Nios II CPU 开发的基本流程。

3.掌握整个 Nios II 集成开发环境。

二、实验环境1.SOPC-NIOSII SOPC 开发平台一套。

2.USB下载电缆一条。

三、实验原理本实验的目的主要是对 SOPC 有一个基本的认识,了解整个实验过程,并掌握整个 Nios II 集成开发环境的应用。

(1) 在 Quartus II中新建一个工程。

(2) 在 SOPC Builder中根据自己的需要加入各种参数值。

(3) 利用 SOPC Builder 产生 Quartus II 能够识别的文件。

(4) 在(1)中新建的工程中加入(3)中生成的文件。

(5) 加入输入、输出以及双向端口,并根据需要对其命名。

(6) 对(5)中命名的输入、输出核双向端口根据选定的 FPGA 进行引脚分配。

(7) 编译工程。

(8) 下载编辑代码到 FPGA。

(9) 利用 Nios II 新建另一个工程。

(10) 根据(2)中的资源,编写项目需要的代码。

(11) 编译、下载并调试,查看运行结果,直到正确。

(12) 如果需要,将(11)中生成的代码下载到代码 Flash 中。

四、实验内容为了熟悉 SOPC 的基本开发流程,本实验要完成的任务就是设计一个最简单的系统,系统中包括 Nios II CPU、作为标准输入/输出的 JTAG UART 以及存储执行代码SRAM。

通过 SOPC Builder 对系统进行编译,然后通过 Quartus II 对系统进行二次编译,并把产生的 FPGA 配置文件通过 USB 下载电缆下载到实验箱上,这时便完成了本实验中的硬件开发。

接下来的工作是软件协同开发——在Nios II IDE 中编写一个最简单的 C 代码,对其编译后,通过 USB 下载电缆下载到 FPGA 中执行,执行的结果就是在 Nios II 的 Console 窗口打印一条信息——“Hello Nios II!”。

niosII操作图解

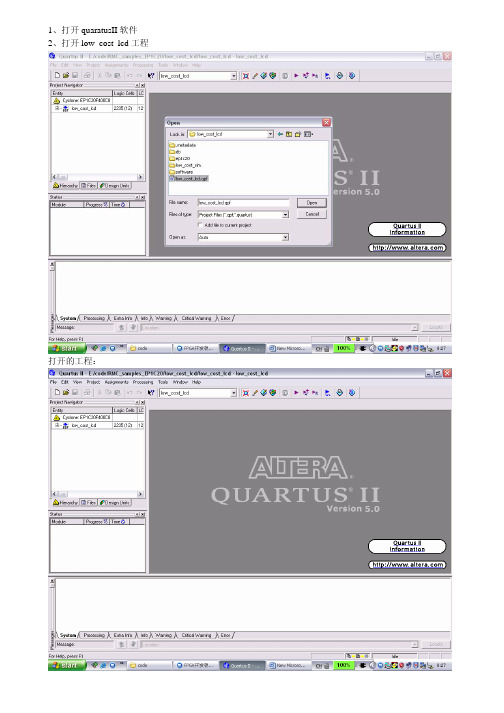

1、打开quaratusII软件2、打开low_cost_lcd工程打开的工程:3、打开sopcbuilder正在打开:Sopc builder中建立的niosII系统4、选择system generationSystem generation界面5、点击run niosII IDE 正在读取中间会提示选择workplace点browse选择在你电脑中的low_cost_lcd文件夹中的software---workspace作为工作空间这是在我电脑中的情况之后等待一会儿,根据电脑的配置不同时间也不同。

可以从上图看到workspace文件夹上面还有一些文件夹。

这些就是存放c/c++例程的地方:这就是存储c文件的地方这个文件夹中就是你所熟悉的c语言程序。

好了言归正传,现在niosII ide 应该已经启动好了,如下显示:6、打开一个你向下载到实验板上的c程序,我以flash_test为例:点击flash_test:7、因为这些文件都是编译过的,就可以不编译了,当然在编译一次也没关系:点project-build project8、先把qaratusII的工程下载到实验板上9、实验板不要断电,下载软件程序注意控制台中显示的内容显示到这一步你的程序就成功了最后讲一下如何建立新的软件工程:1、现在新建一个工程:2、点next选择空白工程3、为你的工程起个名字这时会在旁边出现一个新的工程---flash_test_26、新建一个c/c++文档:出现如下的对话框:7、上面是选择父目录,下面打入文件名8、完成:这时在左侧的工程池中出现了你刚建的文件:9、我先把flash_test.c中的程序复制了,flash_test.c文件的位置上文已经提过了在low_cost_lcd---software---flash_test中。

10、打开文件,然后把刚才复制过的内容粘贴进去,一个新的niosII软件工程就做好了。

编译下载。

NIOS II处理器c程序编写基本流程

NIOS II处理器c程序编写基本流程总结:对NIOS II处理器编写程序主要是用来控制NIOS II外围设备如片上存储器,PIO内核,定时器,SDRAM内核,UART内核,DMA内核以及用户自定义内核等。

其本质是对NIOS II外围设备的相关寄存器进行读写操作。

如下图所示NIOS II处理器即cpu的输入信号主要有时钟,复位信号,中断请求信号,读数据等。

Cpu输出信号主要有地址线,读使能,写使能,写数据,字节选择等。

NIOS II处理器c程序经过编译后产生.elf文件(其内容包括对存储器初始化的.hex文件)下载到FPGA中,其本质主要是将c程序(包括用户自定义的程序和系统自带的库)编译产生的机器代码存储到程序存储器里(一般为rom),为c程序中定义的变量(本质是通过寄存器间接寻址实现)在数据存储器(一般为ram)中分配存储空间。

异常程序的引导程序一般放在ram里以提高异常情况的处理速度。

NIOS II处理器的逻辑模块如下图所示,由此可知NIOS II处理器主要实现读取指令,翻译指令,读写数据,异常控制,中断控制等功能。

步骤一:打开ecplise软件。

步骤二:在QUARTUS II工程文件夹中新建workspace文件夹作为ecplise工作文件夹。

系统会在workspace中自动生成.metadata文件,.metadata文件包含如下图所示的几个文件夹。

步骤三:新建ecplise工程。

选择ecplise工程所需的.sopcinfo文件(之前建立NIOS II处理器系统时产生的文件,此处为mynios.sopcinfo),给ecplise工程命名(此处为mynios_software)。

此时系统自动生成software文件夹,software文件夹中包含以ecplise工程名命名的文件夹(此处为mynios_software)和以ecplise工程名_bsp命名的文件夹(此处为mynios_software_bsp)。

NiosII软件设计与运行流程

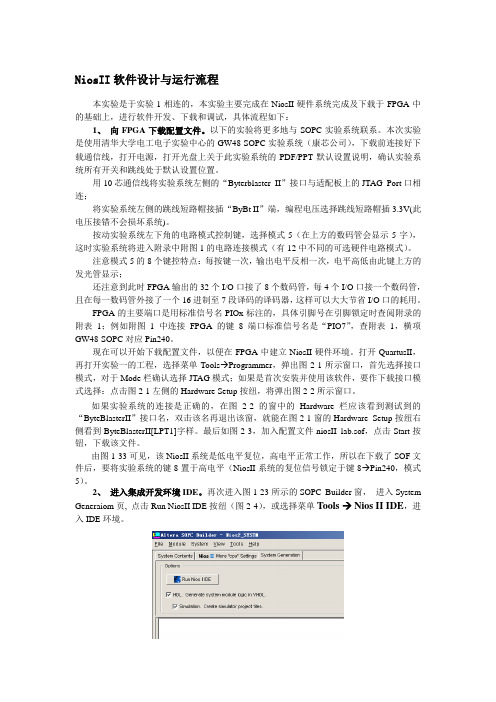

NiosII软件设计与运行流程本实验是于实验1相连的,本实验主要完成在NiosII硬件系统完成及下载于FPGA中的基础上,进行软件开发、下载和调试,具体流程如下:1、向FPGA下载配置文件。

以下的实验将更多地与SOPC实验系统联系。

本次实验是使用清华大学电工电子实验中心的GW48-SOPC实验系统(康芯公司),下载前连接好下载通信线,打开电源,打开光盘上关于此实验系统的PDF/PPT默认设置说明,确认实验系统所有开关和跳线处于默认设置位置。

用10芯通信线将实验系统左侧的“Byterblaster II”接口与适配板上的JTAG Port口相连;将实验系统左侧的跳线短路帽接插“ByBt II”端,编程电压选择跳线短路帽插3.3V(此电压接错不会损坏系统)。

按动实验系统左下角的电路模式控制键,选择模式5(在上方的数码管会显示5字),这时实验系统将进入附录中附图1的电路连接模式(有12中不同的可选硬件电路模式)。

注意模式5的8个键控特点:每按键一次,输出电平反相一次,电平高低由此键上方的发光管显示;还注意到此时FPGA输出的32个I/O口接了8个数码管,每4个I/O口接一个数码管,且在每一数码管外接了一个16进制至7段译码的译码器,这样可以大大节省I/O口的耗用。

FPGA的主要端口是用标准信号名PIOx标注的,具体引脚号在引脚锁定时查阅附录的附表1;例如附图1中连接FPGA的键8端口标准信号名是“PIO7”,查附表1,横项GW48-SOPC对应Pin240。

现在可以开始下载配置文件,以便在FPGA中建立NiosII硬件环境。

打开QuartusII,再打开实验一的工程,选择菜单Tools→Programmer,弹出图2-1所示窗口,首先选择接口模式,对于Mode栏确认选择JTAG模式;如果是首次安装并使用该软件,要作下载接口模式选择:点击图2-1左侧的Hardware Setup按纽,将弹出图2-2所示窗口。

建立能跑uCOSii的Niosii工程

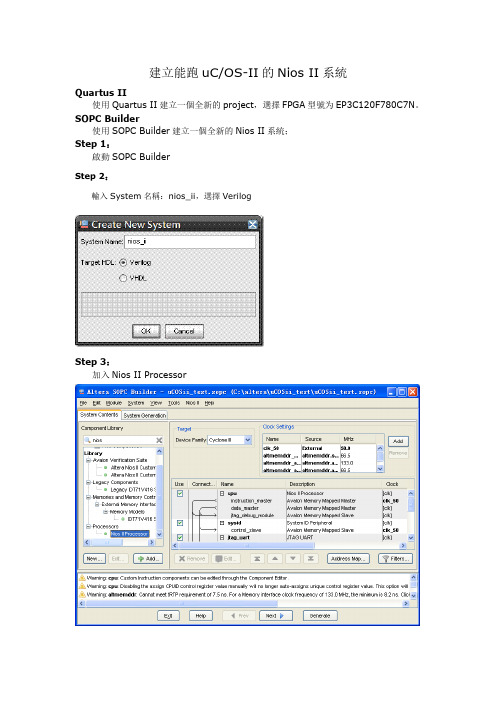

建立能跑uC/OS-II的Nios II系統Quartus II使用Quartus II建立一個全新的project,選擇FPGA型號为EP3C120F780C7N。

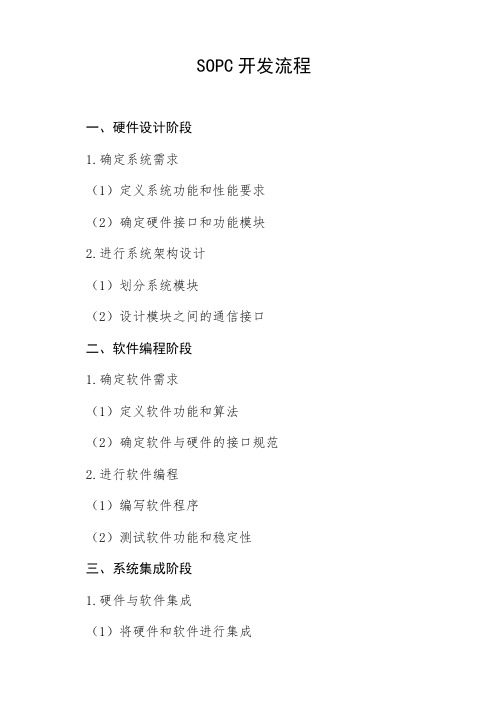

SOPC Builder使用SOPC Builder建立一個全新的Nios II系統;Step 1:啟動SOPC BuilderStep 2:輸入System名稱:nios_ii,選擇VerilogStep 3:加入Nios II Processor使用預設的Nios II/f即可,按FinishStep 4:加入DDR2-SDRAM,选择DDR2 SDRAM Controller With ALTMEMPHY,点“Add”,各参数设置如下图所示,点“Modify parameters…”,将“Memory Burst Length”这项的Value设置为8,完成设置。

点击Finish完成。

在Clock Settings中添加一个125MHz的Clock,名称改为clk_125,把DDR2的时钟改为clk_125,Step 5:由于DDR2与cpu使用的clk不同,要加入Avalon-MM Clock Crossing Bridge来cross,把FIFO depth改为64,点Finish完成。

将Avalon-MM Clock Crossing Bridge的m1的Clock改为DDR2的s1的Clock,并把Avalon-MM Clock Crossing Bridge的m1与DDR2的s1连接起来Step 6:加入Interval Timer,参数设置如图所示:Step 7:加入System ID Peripheral 与JTAG UART ,使用默认设置即可:双击cpu进入设置,将Reset Vector和Exception Vector的Memory都设置为DDR2分配基地址与中断号,最后点击Generate生成sopc系统,完成后点击Exit退出。

NiosIISOPC开发

Nios II/SOPC 的应用领域

01

02

03

04

通信

Nios II/SOPC在通信领域的 应用包括基带处理、调制解调

、协议栈处理等。

工业控制

Nios II/SOPC在工业控制领 域的应用包括运动控制、过程

控制、机器人控制等。

数字信号处理

Nios II/SOPC在数字信号处 理领域的应用包括音频处理、 图像处理、雷达信号处理等。

仿真测试

02

03

调试与优化

使用仿真工具对编译后的文件进 行仿真测试,验证设计的正确性 和可靠性。

在仿真测试过程中,对发现的问 题进行调试和优化,提高设计的 可靠性和性能。

在系统编程与调试

01

02

03

在系统编程

将编译后的文件下载到 Nios II处理器中,实现系 统的实际运行。

在系统调试

在系统运行过程中,使用 调试工具进行实时调试, 解决可能出现的错误和问 题。

Nios II 是一款基于 Altera FPGA 的可定制处理器,具有 高速、低功耗、可编程等优点 ,适用于数字信号处理应用。

数字信号处理算法包括滤波器 设计、频谱分析、信号识别等 ,基于 Nios II 的数字信号处 理系统可以实现这些算法的硬 件加速。

基于 Nios II 的数字信号处理 系统可以应用于音频处理、图 像识别、雷达信号处理等领域 。

应用领域

广泛应用于数字信号处理、通信、控制、图像处理等领域。

Nios II IDE 集成开发环境

概述

Nios II IDE是Altera公司 为Nios II处理器提供的集 成开发环境,支ห้องสมุดไป่ตู้C/C和 汇编语言开发。

Nios II完成最小硬件开发过程

一、实验目的1.学习使用SOPC Builder定制最小NiosII系统的硬件开发过程。

2.学习使用NiosII IDE编写简单应用程序的软件开发过程。

3.学习QuartusII、SOPC Builder、NiosII IDE三种工具的配合使用。

二、实验内容本实验通过使用SOPC Builder定制一个只含“cpu、on_chip_ram、uart”最小NiosII系统,从而完成硬件开发。

然后,使用NiosII IDE编写应用程序,编译完成软件开发。

最后用Quartus II分配管脚,编译、下载完成NiosII最小系统的整个开发过程。

打开超级终端或串口调试助手观察实验结果。

三、所用仪器、材料(设备名称、型号、规格等)计算机、Quarters II软件四、实验步骤及结果截图1、打开Quartus II软件,选择“File| New Preject Wizard”,新建工程“Hello_world”。

点击Next,选择工程的安装路径,输入工程名,如图所示:点击Next,输入要添加到工程中的设计文件,默认不添加。

如图所示:点击Next,选择芯片系列Cyclone II,芯片型号EP2C20F484C8。

如图所示:点击Next,EDA工具设置界面如图所示:点击Next,显示建立新工程所有信息,最后点击Finish,完成新工程向导。

2、打开“Tools| SOPC Builder…”进入SOPC Builder。

(注意:若没有打开工程,“Tools| SOPC Builder…”不可选。

)在“Create New system”对话框中为这个Nios II最小系统命名为“nios_small”(注意该名称不能与工程名重复),默认“Verilog”硬件描述语言,点击“OK”。

如图所示:1)点击“OK”,“Device Family”栏选择“CycloneII”,“clk”栏为“50”MHz。

2)添加片内RAM。

NIOSII SOPC实例1

一.关于SOPC1)SOPC英文全名为:System-On-a-Programmable-Chip,即可编程片上系统。

SOPC 用可编程逻辑技术把整个系统放到一块硅片上,来用于嵌入式系统研究和电子信息处理。

SOPC是一种特殊的嵌入式系统,它是片上系统(System-On-a -Chip,SOC),即由单个芯片完成整个系统的主要逻辑功能但它不是简单的SOC,它也是可编程系统,具有灵活的设计方式,可裁减、可扩充、可升级,并具备软硬件在系统可编程的功能。

SOPC设计包括以32位NIOSII软核处理器为核心的嵌入式系统的硬件配置、硬件设计、硬件仿真、软件设计以及软件调试等。

SOPC系统设计的基本软件工具有:1)QuartusII:用于完成NIOSII系统的综合、硬件优化、适配、编程下载以及硬件系统调试等;2)SOPC Builder:Altera NiosII嵌入式处理器开发软件包,用于实现NiosII 系统的配置、生成,内嵌于QuartusII软件中;3)ModelSim: 用于对SOPC生成的NiosII系统的HDL描述进行系统的功能仿真;4)NiosII IDE:用于进行软件的开发、调试,以及向目标开发板进行Flash下载;二.关于NIOSII处理器NIOSII 是一个可配置的软核处理器。

“可配置”的意思是设计者可以根据性能和成本的要求来增加或删减处理器的功能。

ALTERA公司并不销售NIOSII处理器芯片,而是销售空的FPGA,并提供NIOSII 系统相应的IP核来组成NIOSII系统,然后将这个系统下载到FPGA中实现。

1)关于AVALONAvalon总线是SOPC硬件系统的重要组成部分,Avalon总线规范是为了开发SOPC 环境下外设而设计的。

图1-1 一个SOPC的示例二. SOPC简单实例:软核控制LCD液晶字母显示器1.系统构成规划1)系统功能:在character LCD上显示”Hello LCD from NiosII!”2)本系统中需要的外围器件:(1)L CD:输出显示(2)S RAM存储器:程序运行时将其导入SRAM3)SOPC中建立系统需要添加的模块包括:(1)N ios II 32bit CPU(2)L CD display(3)外部RAM总线(4)外部RAM接口(5)J TAG UART Interface(6)定时器2.硬件系统的建立1)首先打开Quartus II 建立工程文件:将工程文件命名为hello_lcd,顶层文件与工程文件同名。

《NiosIISOPC开发》课件

为了进行NiosIISOPC的开发,你需要先安装好开发环境: Quartus①、SOPC Builder②和NiOS IDE③。

NiosIISOPC的配置文件包括指令集、时钟周期等,通过 SoPc Builder工具进行设置和配置。

NiosIISOPC的服务器设置

通过HMI(人机界面)进行服务器的设置,设定各种

NiosIISOPC在工业自动化中的应用

NiosIISOPC可以应用于各类工业自动化设备,如PLC、机 器人和仪器仪表等,实现设备之间的数据交互和控制。

NiosIISOPC在物联网中的应用

NiosIISOPC能够与云服务进行连接,实现云端数据的处 理、存储和应用,为物联网的开发和应用提供了强有力 的支持。

NiosIISOPC的调试与测试

NiosIISOPC的调试工具介绍

NiosIISOPC提供了一系列调试工具,如调试器和日志监视器,帮助开发者找出问题并解决。

NiosIISOPC的测试方法

NiosIISOPC测试主要包括功能测试和性能测试,其中性能测试会影响到整个系统的稳定性及 响应时间等。

NiosIISOPC的应用实践

NiosIISOPC的应用前景

NiosIISOPC已经得到广泛应用,随着技术的 不断提升和应用场景的丰富,NiosIISOPC的 应用前景必将更加广阔。

结语

1 NiosIISOPC开发的重要性

NiosIISOPC开发对于提高工业自动化水平和实现物联网应用具有重要意义。

2 NiosIISOPC开发的价值与意义

为什么要进行NiosIISOPC开发?

NiosIISOPC开发可以实现工控设备与上位机的通信和控制,提高工业自动化水平及控制效率。

NiosIISOPC基础知识

NiOSIISOPC嵌入式系统基础教程

Altera公司提供的LPM (logic programmable module)宏功能块或用户自己 定制的模块; 5. 在顶层实体中,将NIOS II系统模块、Altera的LPM或用户自定

开发环境:

1. Quartus II 6.0 (8.0) 2. SOPC Builder 6.0 (8.0) 3. Nios II IDE 6.0 (8.0) 4. 基于Cyclone II 的SOPC开发板

Quartus

完成NiosII整个系统的设计、分析、综合、硬件优化和适配 配置文件编程下载、硬件系统测试 SOPC Builder NIOSII 系统硬件开发环境 实现Nios II系统配置和生成 Nios II系统相关的监控和软件调试平台的生成 IDE 完成基于Nios II系统的软件开发和调试 将FPGA配置信息写入Flash或者EPCS

这个两过程类似传统电路设 计中,将所有要使用的芯片 焊接到电路板上,然后通过 PCB上的连线将各个芯片连 接起来,组成电路系统。

集成SOPC生 成的系统到 Quartus II工程

Altera的 LPM模块

硬件抽象层 (HAL)&外设 驱动பைடு நூலகம்序

使用Nios II IDE开发软件

第2章 SOPC硬件开发环境及流程

2.1 SOPC开发流程和开发工具

SOPC设计包括硬件和软件两部分。

1. 硬件设计:基于Quartus II和SOPC Builder 2. 软件设计:基于Nios II IDE 3. 仿真: ModelSim 4. DSP的开发: Matlab和DSP Builder

sopc开发流程

SOPC开发流程

一、硬件设计阶段

1.确定系统需求

(1)定义系统功能和性能要求

(2)确定硬件接口和功能模块

2.进行系统架构设计

(1)划分系统模块

(2)设计模块之间的通信接口

二、软件编程阶段

1.确定软件需求

(1)定义软件功能和算法

(2)确定软件与硬件的接口规范

2.进行软件编程

(1)编写软件程序

(2)测试软件功能和稳定性

三、系统集成阶段

1.硬件与软件集成

(1)将硬件和软件进行集成

(2)确保硬件与软件协同工作正常2.进行系统调试

(1)调试系统功能和性能

(2)优化系统性能和稳定性

四、验证和测试阶段

1.确认系统功能

(1)验证系统功能是否符合需求(2)进行功能性测试

2.进行性能测试

(1)测试系统响应速度和资源利用率(2)确保系统性能达标

五、部署和发布阶段

1.准备部署环境

(1)确定部署硬件平台和软件环境(2)进行部署准备工作

2.系统部署

(1)将系统部署到目标平台

(2)部署后的系统功能测试

六、运行和维护阶段

1.系统运行

(1)系统投入运行

(2)监控系统运行状态

2.系统维护

(1)定期维护系统

(2)处理系统运行中的问题

以上是SOPC开发流程的详细步骤,确保系统开发按照规范进行,达到预期效果。

以最简单的Hello程序为例,NIOSII开发的整个流程

以最简单的Hello程序为例,NIOSII开发的整个流程废话不多说,我们来开始最简单、最基本的NiosII程序,首先打开quartusII 9.1,双击即可,打开如下界面:点击File→New Project Wizard 如下图:出现如图:点击第一个后面的。

将新建的文件放入自己事先建好的文件夹hello内千万记住路径中不能有中文完成后如图:再第二个填入hello中即可,之后点击next,出现如下图:继续next,不要犹豫……在Device family 中选择Cyclone III(由于我们的板子芯片是这个系列的),其他的不用动。

在available devices中选择EP3C10E144C8,完成后点击next,这里我们不做仿真,直接点击next点击finish,完成新建真正的工作马上开始:在这点击File→New都可跳出如下界面:选择Block Diagram/Schematic File,双击,出现如下界面在工具栏()中选择SOPC,单击,出现如下界面其中的System Name 命名为kernal ,Target HDL选为VHDL将时钟改为100M,Name也改为clk(改不改都行)下一步选择CPU,也就是nios的处理器,双击选择完毕后,出现这样的对话框对话框中可看到三种nios核(从e核最简单,占用空间最小,第三个f核是快速的,但是占用空间最大的,中间的S核是介于e与f之间的,性能与占用空间比较平衡的核。

)这里我们选择f核(方便以后开发使用)这里Memory后面可选的部分暂时没有东西,暂且放一边,待我们建立好SDRAM与EPCS 再回来选择即可☺接下来,点击next其中Data cache 选择none(原因在后面介绍☺)点击next点击next 继续next其中有很多级别,这里我们选择level1即可点击完成,出现如下界面其中cpu_0即为我们要使用的核,右键rename改为cpu,下面要做的就是接外设,让cpu工作起来首先加入sdram双击sdram,出现选择Presets:Custom;Data with:16,其他的都不变。

基于NIOS II内核的嵌入式SOPC开发板的实现

基于NIOS II内核的嵌入式SOPC开发板的实现随着大规模集成电路技术的进步和制造工艺水平的提高,嵌入式系统的开发变得日益复杂。

传统的嵌入式系统设计方法已经不能适应当前嵌入式系统设计的需要。

单个芯片容量的增大、功能的增加、体积的减小使得设计变得更加便利,同时也为嵌入式系统设计开发开辟了新的天地即片上系统(System on Chip,SoC)技术。

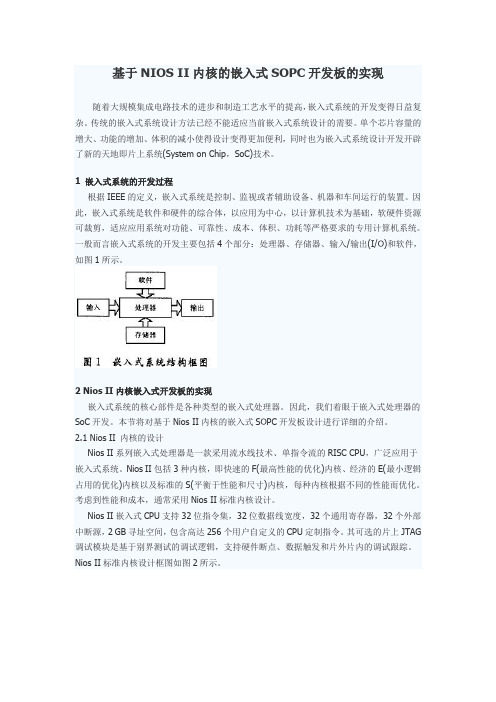

1 嵌入式系统的开发过程根据IEEE的定义,嵌入式系统是控制、监视或者辅助设备、机器和车间运行的装置。

因此,嵌入式系统是软件和硬件的综合体,以应用为中心,以计算机技术为基础,软硬件资源可裁剪,适应应用系统对功能、可靠性、成本、体积、功耗等严格要求的专用计算机系统。

一般而言嵌入式系统的开发主要包括4个部分:处理器、存储器、输入/输出(I/O)和软件,如图1所示。

2 Nios II内核嵌入式开发板的实现嵌入式系统的核心部件是各种类型的嵌入式处理器。

因此,我们着眼于嵌入式处理器的SoC开发。

本节将对基于Nios II内核的嵌入式SOPC开发板设计进行详细的介绍。

2.1 Nios II 内核的设计Nios II系列嵌入式处理器是一款采用流水线技术、单指令流的RISC CPU,广泛应用于嵌入式系统。

Nios II包括3种内核,即快速的F(最高性能的优化)内核、经济的E(最小逻辑占用的优化)内核以及标准的S(平衡于性能和尺寸)内核,每种内核根据不同的性能而优化。

考虑到性能和成本,通常采用Nios II标准内核设计。

Nios II嵌入式CPU支持32位指令集,32位数据线宽度,32个通用寄存器,32个外部中断源,2 GB寻址空间,包含高达256个用户自定义的CPU定制指令。

其可选的片上JTAG 调试模块是基于别界测试的调试逻辑,支持硬件断点、数据触发和片外片内的调试跟踪。

Nios II标准内核设计框图如图2所示。

Nios CPU的所有数据、程序都是通过Avalon总线传输的,系统的FPGA片外PIO(外围IO)包括一个串行口、显示、键盘、存储器,片内PIO采用FIFO实现。

SOPC第五章NiosII应用程序及其外设HAL驱动开发

用户自己创建和管理连接,建议 采用自动连接。 Nios II IDE自动创建和管理连接, 使用前必须指定下面选项。

可执行代码驻留的物理存储器。

只读数据驻留的物理存储器。

可读/写数据驻留的物理存储器。 Heap(堆)驻留的物理存储器。 选S择ta后ck,(栈异)常驻堆留栈的将物驻理存留储在器单。独的物 理存储器中。

(对话框位置:[RUN]→[Debug] →[Nios II Hardware] →Target Connection)

进进行行J连NTAi接oGs在下IJ载IT系A电统G缆下中的载断选电通择缆信。上工 带具J选TA择G。接口器件的选择。

知识回顾3: 调试/运行程序

调试器设置--(Debugger)

(对话框位置:[RUN]→[RUN] /[RUN As])

知识回顾1: Nios II IDE简介

三.调试器

软件调试器(GDB):是强大的、在GNU调试器基础 之上的软件调试器。该调试器提供许多基本调试功能 以及一些在低成本处理器开发套件中不会经常用到的 高级调试功能。

基本调试功能包括:运行控制、调用堆栈查看、软 件断点、反汇编代码查看、调试信息查看、指令集仿 真器。

指定异常堆栈驻留的物理存储器。

指定异常堆栈的最大空间。

知识回顾3: 调试/运行程序

(对话框位置:[RUN]→[Debug] /[Debug As])

选择Debug的目标器件: 1. Nios II硬件 2. Nios II指令仿真器 3. Nios II多处理器集

知识回顾3:调试/运行程序

调试器目标连接设置--(Target Connection)

知识回顾2: 设置工程系统库属性和编译 选项

System Library 设置

NIOSII软件硬件开发流程

make: *** [RUN_ON_HDL_SIMULATOR_ONLY_hello_world_0.elf] Error 1

Build completed in 45.752 seconds

解决办法:

修改编译器的优化级别:

修改工程设置:

`include "div_clk.v"//user

`include "disp_ctl.v"//user

参考博客:/oneseven/archive/2009/08/19/1550190.html

编译成功后控制台显示如下:

程序过大,存储空间过小是导致这种错误的根本原因

7、IDE与modelsim联合仿真。

(1)首次运行时,配置运行参数。

设置modelsim的安装路径,我的是D:\modeltech_10.0c\win32。

然后在modelsim命令窗口中输入run–all。观察输入输出终端

程序输出正确。

修改程序再仿真流程

1在modelsim中暂停仿真,restart仿真;

2在NIOSII IDE中,修改程序,如:

3存储修改后文件,然后buildall;

4、然后在modelsim中run-all,结果如下

UART和PIO应用例:

单击run启动仿真。

(2)Modelsim10.0c自启动后。命令窗口输入s加载文件仿真。

(3)输入h显示操作命令。

(4)打开shell命令窗口。

(5)打开shell命令窗口后,转换当前工作目录到仿真文件夹,

cd/cygdrive/e/NIOSII/SOPC_UART/nios2_sys_sim

建立NIOSII处理器系统基本流程

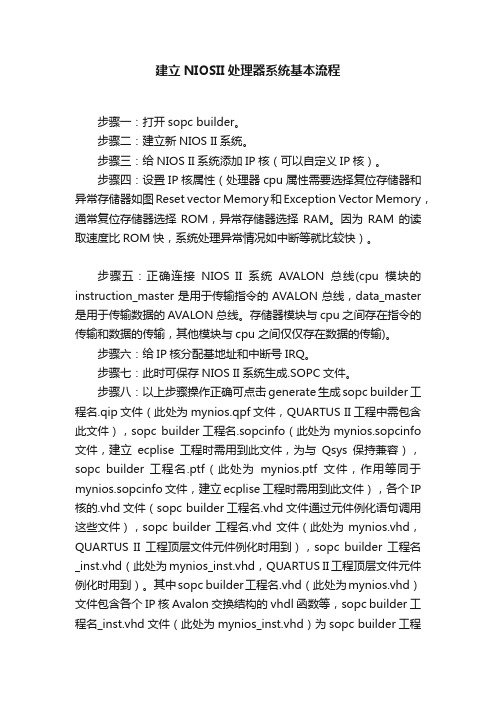

建立NIOSII处理器系统基本流程步骤一:打开sopc builder。

步骤二:建立新NIOS II系统。

步骤三:给NIOS II系统添加IP核(可以自定义IP核)。

步骤四:设置IP核属性(处理器cpu属性需要选择复位存储器和异常存储器如图Reset vector Memory和Exception Vector Memory,通常复位存储器选择ROM,异常存储器选择RAM。

因为RAM的读取速度比ROM快,系统处理异常情况如中断等就比较快)。

步骤五:正确连接NIOS II系统AVALON总线(cpu模块的instruction_master是用于传输指令的AVALON总线,data_master 是用于传输数据的AVALON总线。

存储器模块与cpu之间存在指令的传输和数据的传输,其他模块与cpu之间仅仅存在数据的传输)。

步骤六:给IP核分配基地址和中断号IRQ。

步骤七:此时可保存NIOS II系统生成.SOPC文件。

步骤八:以上步骤操作正确可点击generate生成sopc builder工程名.qip文件(此处为mynios.qpf文件,QUARTUS II工程中需包含此文件),sopc builder工程名.sopcinfo(此处为mynios.sopcinfo 文件,建立ecplise工程时需用到此文件,为与Qsys保持兼容),sopc builder 工程名.ptf(此处为mynios.ptf文件,作用等同于mynios.sopcinfo文件,建立ecplise工程时需用到此文件),各个IP 核的.vhd文件(sopc builder工程名.vhd文件通过元件例化语句调用这些文件),sopc builder工程名.vhd文件(此处为mynios.vhd,QUARTUS II工程顶层文件元件例化时用到),sopc builder工程名_inst.vhd(此处为mynios_inst.vhd,QUARTUS II工程顶层文件元件例化时用到)。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

SOPC/NIOS II 開發流程

硬體開發流程

Quartus II

New Project (.qpf)

SOPC Builder

Add Processor

Add Controllers Component Connect Code Generate (.v) Top Design (.v) Pin Assignment (.qsf) Compile (.sof)

元件 以Address 來 定址所要 Access 的元件

10

SOPC/NIOSII 設計與實作課程

© 2007 Terasic Corporation

SOPC Example

11

SOPC/NIOSII 設計與實作課程

© 2007 Terasic Corporation

SOPC Builder 輸出

– HDL Source File – 硬體描述檔(.PTF)

7

SOPC/NIOSII 設計與實作課程

© 2007 Terasic Corporation

SOPC Builder 介面

元件區

系統建構區

8

SOPC/NIOSII 設計與實作課程

© 2007 Terasic Corporation

SOPC 建構流程

3

SOPC/NIOSII 設計與實作課程

© 2007 Terasic Corporation

NIOS II 版本

• 版本

• 軟體相容性

– Binary Code Compatible (No changes required when CPU version is changed.)

4

SOPC/NIOSII 設計與實作課程

14

SOPC/NIOSII 設計與實作課程

© 2007I IDE(2)

• OS:

– None-OS – MicroC/OS2

• Software Component:

– Standard C Library – TCP/IP Stack – Zip Read-Only File System – Host Based File System

main()

Application Code

17

SOPC/NIOSII 設計與實作課程

© 2007 Terasic Corporation

NIOS II IDE C/C++介面

Debug Run 介面切換

Project Management

Editor

outline

Console

18

SOPC/NIOSII 設計與實作課程

• 目的:

– 將完整的電子系統, 整合在一顆FPGA 內 (All in one!)

• 優點:

– 有彈性, 容易修改與擴充系統

2

SOPC/NIOSII 設計與實作課程

© 2007 Terasic Corporation

NIOS II

• • • • • • • • Altera 第二代Processor Soft-Core 32-bit RISC Royalty-Free 支援Altera 全系列FPGA 依速度, 有三種版本可供選擇 支援Instruction/Data Cache 支援JTAG Debug 可自訂指令

• 以 “系統名稱”來命名HDL Top Source File & 硬體描述檔.PTF

• Example:系統名稱 = “DE2_70_SOPC” – Top: DE2_70_SOPC.v – PTF: DE2_70_SOPC.ptf

12

SOPC/NIOSII 設計與實作課程

© 2007 Terasic Corporation

15

SOPC/NIOSII 設計與實作課程

© 2007 Terasic Corporation

NIOS II System

使用者 產生

NIOS II IDE 產生

SOPC 產生

16

SOPC/NIOSII 設計與實作課程

© 2007 Terasic Corporation

NIOS II System Boot Sequence

Connection

系統建構區

Generate

9

SOPC/NIOSII 設計與實作課程

© 2007 Terasic Corporation

SOPC 系統設定

• MM架構(MemoryMapped) • 設定元件: – Name – Clock – Address – IRQ – 之間的連接關係

System Interconnect Fabric

Breakpoint

Console Window

Disassembly Trace

19

– HAL (Hardware Abstraction Layer).功能: 控制硬體的 Software Library – SYSTEM.h: 定義SOPC 內每個元件的name, base address, IRQ number… 等資訊.

• 執行檔的副檔名為.ELF (Executable and Linkable Format)

SOPC/NIOSII 設計與實作課程

© 2007 Terasic Corporation

SOPC/NIOS II 開發流程

• SOPC/NIOS II • 開發流程 • 開發工具

1

SOPC/NIOSII 設計與實作課程

© 2007 Terasic Corporation

SOPC

• 全名:

– System On a Programmable Chip

© 2007 Terasic Corporation

NIOS II IDE Debug 介面

Debug Trace Control Bar Calling Stack Variable/Register Inspect

C-Level Trace F6: Step Over F5: Step Into

1. 從元件區挑選元件, 一一加入系統建構區 2. 於系統建構區設定: 每個元件的Clock, Address, IRQ, 以及元件間的Connection. 3. 按 “Generate” 產生Source Files

Component Name/Description

Address IRQ

元件區

CRT0.S

RESET

Initialise caches, BSS, stack pointer, global pointer

alt_main

Initialize interrupt system and setup call to main

alt_sys_init

Initialize HAL devices

.PTF 硬體描述檔

軟體開發流程

NIOS II IDE

New Project Project Configure Coding (.c/.cpp) Compile/Linker

DE2_70 Board

HAL & system.h Execute Code (.elf)

5

SOPC/NIOSII 設計與實作課程

© 2007 Terasic Corporation

SOPC/NIOS II 開發工具

• SOPC Builder • NIOS II IDE

6

SOPC/NIOSII 設計與實作課程

© 2007 Terasic Corporation

SOPC Builder

• • • • • Quartus 附屬工具之一 用於快速(幾分鐘!)建立SOPC 內建60個以上的IP, 含Processor 圖形操作介面 自動產生SYSTEM code:

NIOS II IDE 介紹

13

SOPC/NIOSII 設計與實作課程

© 2007 Terasic Corporation

NIOS II IDE(1)

• NIOS II Processor 的C/C++整合開發環境 • 包含Editor, Compile/Link, Download, Debug 功 能 • 依硬體描述檔PTF, 自動產生HAL & SYSTEM.h