引脚对照表

180种CPU引脚功能与机型对照表

33 15 29 33 33 24 55 6 17 9 9 9 33 27 33 33 33 33

6

Байду номын сангаас

CKP1301S 康佳F2109E2 20 CH4001-5B41 长虹C2155 8 CH04001-5553 长虹C2151C 8 CH04001-5C25 长虹C1951K 8 CH0403-5H61 长虹A2928B 7 CH04801-5F43 长虹P2119A 7 CH05001 长虹C2995 41 CTV222S.PRC1 康佳T2516 41 CTV591S.GW3 海尔692-733AM-02 41 CXP80424-146 东芝3429KTP 37 CXP85332-108 东芝 F3SS 机芯 37 LA86C3348A 创维 Y 机芯 7 LC863320A 康佳F2979A 7 LC863324 TCL王牌-2116E 7 LC863328A-5T45 康佳T2188A 7 LC863348A 康佳F2109A 7 LC864012L-5711环宇新宇宙王C5420BZ 8 LC864512V-5D18 海尔HS-2588D 7 MN181768 创维 5N10 机芯 21 MN1874876TSH 松下TC-33GF85 33 TMS73C167 海尔H-2916 10 TMP47C834N-R122 东芝2128KTV 8 TMP87CH36N 厦华XT3868T 34 TMP87CM36N-3649 厦华XT29F8THD 34 TMP87CK36N 康佳T2988P 34 TMP87CX38N 康佳T2166E 20 TMP87CP38N 长虹G2967A 7 TMP87CH38N 厦华XT-3465 7 TMP87PS38N 海信TC2902GD 7 TMP87CK38N TCL王牌2901A 18 TMP87CS38N 飞利蒲29H8 8 ST6368B4/FHO 康佳T2979D1 37 ST6388 创维 5S01 机芯 37 P87C770 飞利蒲29G8 19 P83C266BDR 海信TC2532F 3、41 ONWA KWEC 康佳T2510 8 WH2000C 海尔HP-3408 41 KONKA266 康佳P3486C 14 KS88C8324 长虹G2573 42 Z8933212PSC 北京2163 18 Z90231 康佳F2109C 35 CCU-2070-LDTV-06A 福日HFC2553 28 CH05002 长虹D2963A 41 CHT0406 长虹R2118K 7 CHT0803 长虹43PT18 41 CHT0807 长虹2131FB 7 CHT0808 长虹29SD83 41

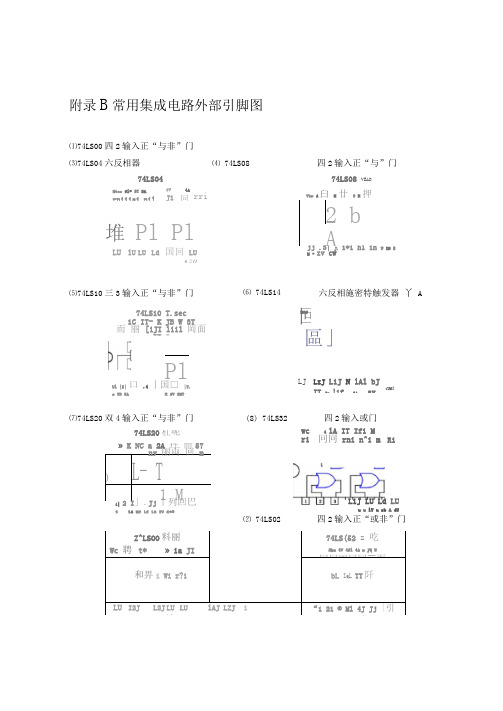

常用集成电路外部引脚图

附录B 常用集成电路外部引脚图Z^LSOO 料丽 Wc 聘 t* » ia JI 而冋网KH 丽R1 m74LS(52 z 吃Xkn 4V 4fl 4A n JQ U冋冋丽冋冋〒面和畀1 Wi r?ibL I Q L TT 阡LU I2J L2J LU LU lAJ LZJ 1 1A -Ifl tV 詁 aflJVI“1 21 ® Ml 4J Jj |引IVIB 2Y lA 2B GhO四2输入正“或非”门⑵ 74LS02⑴74LS00四2输入正“与非”门 ⑶74LS04六反相器⑷ 74LS08 四2输入正“与”门74LS04Mtoc fl* S T SArniiiai nil iVJi4A回 rri堆 Pl Pl2 b 1 ALU lU LU Ld 国回 LUUIf JAivikiY&泌⑸74LS10三3输入正“与非”门⑹ 74LS14六反相施密特触发器 丫 A74LS10 T.sec1C IT- K JB W 3T 而 丽 [iJI liil 岡面IT IMOf回 PlUl |Z|口 .4 丨国□ |T.g IB ZAK 2V SMT⑺74LS20双4输入正“与非”门(8) 74LS3274LS20杠呢 )L- T1 M區」LJ LzJ LiJ N lAl bJIT 2a !1fSAav四2输入或门4 lA IT Ifi M冋冋 rni n^i m <30!R1 74LS08 VEADVbr d臼 M 廿 9 H 押 而河豆同而jj .3| J. 1*1 hl in W IB EM *zv cw» K NC a 2A 丹 而57ny 丽両 回 m2 I 」.Jj 丨列回巴316 MC 1C 1O IV G*®wc ri iiLiJ LU Ld LUu u lY u zb A dU2AB CDE FGH IJFl 帀LL UJ _U [± L£J LJTAIB lY2A3fl7T fiNt(9) 74LS47 BCD 到七段译码器/驱动器(有效低、0C 门、15V )(10) 74LS48 BCD (内有上拉电阻)到七段码译码/驱动器7^LS47 ULr.ljfflWHWc I f 0• c d H1门二3IJGur ;) .忙七V :-..----------- w -----------.F yf r n n Pl ' 1(11) 74LS51 2-3 输入“与或非”门(12) 74LS54与或非门(13) 74LS74 双 D 型触发器(带预置和清除、正沿触(14) 74LS76Vae 2Qfl » ICX Jl*B Xi »[i? 哩 iil 卫呼 IT74LS74 ■h -Jri ?訂 g*B7415716J 匸. 5 1 £1(15) 74LS86四2输入异或门四总线缓冲门Y A(16) 74LS125 (带三态输出、C 高时输出关断,即禁VHD阪74LSe646 4Y R A 砂曲3a u avJig. [VI74LS125 v~AVtc < 4A J* X 3* Jlf冋冋.同而帀瓦風引 ⑺ |叫6 C LT HmSCWII & A <ihDLJ LJ LJ kJ kJ LJ LJ LiJ ci.f HbVHt ml b JI atafiJ JJ H. IN .'I I^J .^J 10( IH lOA ij心K PA XLR双JK 触发器(带预置和清除、负沿触发)1* 1Q 1O GhP » M 203」(17) 74LS138 3 线-8线译码器(多路转换器)(18) 74LS148 8线-3线八进制编码器阿T S7冋T1 TJ M 面洞[i?rfi IQ rftH.J5J■J ij :J.■74LS13e)■1n"1*S l<Jl >. [«.T■T■c OZA ^ZB Gl tT□TOVB eo C5 3 7 \ 0 M叵西I有回匝问74LS14S出a -込.序”q-F ,咅许S0丨引1= Ml ElH At 0X3(19) 74LS151 8 选1数据选择器(多路转换器)(20) 74LS153 4(多路转换器)选1数据选择器(21) 74LS160 同步4位计数器(十进制,直接清除)(22) 74LS161 4位计数器(二进制,直接清除)同步ViJU co OA « oc flO FTJwlFS [171 ;ia [ijl (1? [wlID叵、74LS160/ 卫乍KfhF臨K I 亠Tib, . i 'S rFJf ]LIJ PfOJ? cutLil lU' LU ir LU LtA & c a Efr(23) 74LS194 4 位双向通用移位寄存器(24) CD4060B 二进制计数器和振荡器(分频器,14级进位)oc CD cu< £1 別両冋阪同而冋m«:« QI Qt KSFT er nu fBT冋岡冋向冋冋冋R174LSW4H.理 3 Ltl ⑸ LU 回aR SR A B C 0 a ONO oil QU 414 qe 05 (F CK I»(11VP ■»Y£ U) lA d « V iri IStIf 同同冋同冋rmnnrri(29)七段显示数码管(示意图)(25) NE555多谐振荡器(26)A741运算放大器TED HR mr cn冋m n R]H ; ™ (JtT HL2 Rirn Ri R]NE555TH Uf kJ L JtMl CLI tttLJ U U bJULl 止-祐i(27) ADC0804 八位模/数转换器 (28) DAC0832八位数/模转换器m CLU nm w bu n nn* ns同冋PI 冋岡同冋両IU 回na丽 u pa u pT rnmi T *诣 何同冋丽 网网网 mLJbJkJHkJtdliJkJkJH ?! E Iff cuiiK TH! uiEt IHL tana itnf/a HHLJLiJUJLiJUIIiJLJLLfMl^ 縣 Wi 4ew n K n »He "xm附录C常用门逻辑符号对照表。

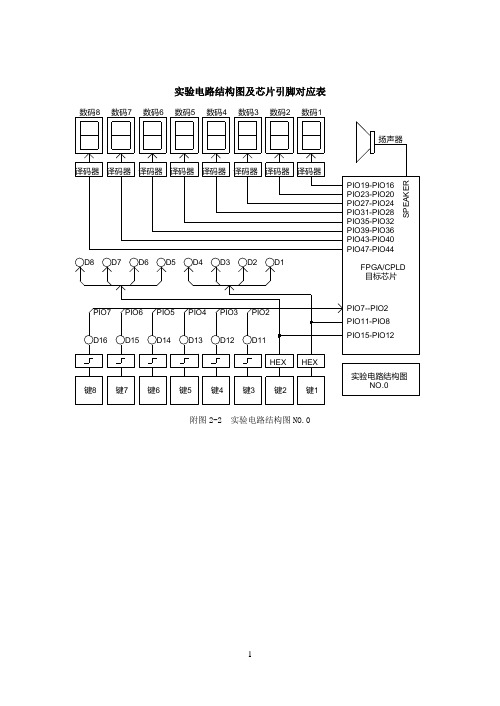

实验电路结构图及芯片引脚对应表

实验电路结构图及芯片引脚对应表NO.0实验电路结构图HEXPIO2PIO3PIO4PIO5PIO7PIO6D1D2D3D4D5D6D7D8D16D15D14D13D12D11数码1数码2数码3数码4数码5数码6数码7数码8S P E A K E R扬声器译码器译码器译码器译码器译码器译码器译码器译码器FPGA/CPLD PIO15-PIO12PIO11-PIO8PIO7--PIO2HEX 键1键2键3键4键5键6键7键8PIO47-PIO44PIO43-PIO40PIO39-PIO36PIO35-PIO32PIO31-PIO28PIO27-PIO24PIO23-PIO20PIO19-PIO16目标芯片附图2-2 实验电路结构图NO.0附图2-3 实验电路结构图NO.1附图2-4 实验电路结构图NO.2ʵÑéµç·½á¹¹Í¼NO.3ÒëÂëÆ÷ÒëÂëÆ÷ÒëÂëÆ÷ÒëÂëÆ÷ÒëÂëÆ÷ÒëÂëÆ÷ÒëÂëÆ÷ÒëÂëÆ÷D9D16D15D14D13D12D11D10D8D7D6D5D4D3D2D1PIO8PIO9PIO10PIO11PIO12PIO13PIO14PIO15S P E A K E RÑïÉùÆ÷12345678Ä¿±êоƬFPGA/CPLD PIO0PIO1PIO2PIO3PIO4PIO5PIO6PIO7¼ü1¼ü2¼ü3¼ü4¼ü5¼ü6¼ü7¼ü8PIO15-PIO8PIO47-PIO44PIO43-PIO40PIO39-PIO36PIO35-PIO32PIO31-PIO28PIO27-PIO24PIO23-PIO20PIO19-PIO16附图2-5 实验电路结构图NO.3附图2-6 实验电路结构图NO.4GNDPIO45PIO46513PS/2接口VCCJ74接PC 机串行通讯接口接口电路单片机接口电路235RS-232B412MHZA键复位P34P33P32X1X2P31P30P35RST GND12345678910VCCPIO11PIO12PIO13PIO14AT89C2051EU3P37P10P11P12P13P14P15P16P17VCC 11121314151617181920PIO15PIO24PIO25PIO26PIO27PIO28PIO29PIO30PIO317.2K P29->A14)27512(PIN30->VCC,PIN3->A15,PIN29->WE)628128(PIN30->VCC,PIN3->A14,RAM/ROMP29->WE)62256(PIN30->VCC,PIN3->A14,6264(PIN30->VCC,PIN29->WR)PIN30->A17,PIN3->A15,PIN29->A14)29C040(PIN31->WE,PIN1->A18,PIN3->A15,PIN29->A14)27040(PIN31->A18,PIN30->A17,PIN29->A14)27020(PIN30->A17,PIN3->A15,P29->A14)27010(PIN30->VCC,PIN3->A15,PIO40PIO41PIO42PIO43PIO44R78 200R77 200R76 20010548761413321 视频接口VGA J6A18/A19A18/A15/WE PIO49VCC SLA17RAM_ENVCC GND SLRAMPIO26PIO25PIO24PIO32PIO33PIO34PIO35PIO36PIO37PIO38PIO39PIO14PIO47PIO10PIO48PIO9PIO46PIO45PIO11PIO12PIO13PIO8PIO15PIO31PIO30PIO29PIO28PIO273231302928272625242322212019181716151413121110987654321VCC GND2708027040270202701027512272562764628128622566264VCC A17/VCC WR/A14A13A8A9A11OE A10CS1D7D6D5D4D3GND D2D1D0A0A1A2A3A4A5A6A7A12A14(A15)A1610K VCCVR1PIO31PIO29PIO30PIO28PIO27PIO26PIO25PIO24131415164D7D6D5D4D35D26D1D07PIO37+5JP251pFC27JP2(COMP)COMP LM311VCC10K -12+124823TL082/1AIN0AOUT1021035.1KR72765TL082/2841+12-12滤波0滤波1FITCOMMEU2DAC0832118171032WR1FB93211IOUT1IOUT212/CS WR2XFER A GND D GNDVREF8VCC 20VCCJP2(1/2,3/4)D1PIO8D2D3D4D5D6D7D8PIO9PIO10PIO11PIO12PIO15PIO14PIO13实验电路结构图NO.5S P E A K E R扬声器FPGA/CPLD 目标芯片12345678D16D15D14D13D12D11D10D9PIO47-PIO44PIO43-PIO40PIO39-PIO36PIO35-PIO32PIO31-PIO28PIO27-PIO24PIO23-PIO20PIO19-PIO16译码器译码器译码器译码器译码器译码器译码器译码器PIO15-PIO8PIO0PIO1PIO2PIO3PIO4PIO5PIO6PIO7键1键2键3键4键5键6键7键8P I O 8J P 2(5/6)P I O 8(23)(24)1216272610C L O C K 750K H Z A F I T102C 30103C 29P I O 37P I O 35C O M MC O M PA D E O C A D E NJ P 22018161412108642191715131197531021+5V A I N 0A I N 1r e f (-)r e f (+)I N -1I N -06922257171415818192021E U 1A D C 0809P I O 16P I O 17P I O 18P I O 19P I O 20P I O 21P I O 22P I O 23P I O 32P I O 33P I O 35P I O 34m s b 2-12-22-32-42-52-62-7l s b 2-8E O C A D D -A A D D -B A D D -C A L E E N A B L E S T A R T附图2-7 实验电路结构图NO.5附图2-8 实验电路结构图NO.6D16D15D14D13D12D11D9D8PIO47D7PIO46D6PIO45D5PIO44D4PIO43D3PIO42D2PIO41PIO40D1NO.7实验电路结构图S P E A K E R扬声器FPGA/CPLD 目标芯片12345678PIO0PIO2PIO3PIO4PIO5PIO6PIO7单脉冲单脉冲单脉冲键1键2键3键4键5键6键7键8PIO47-PIO40PIO39-PIO36PIO35-PIO32PIO31-PIO28PIO27-PIO24PIO23-PIO20PIO19-PIO16译码器译码器译码器译码器译码器译码器附图2-9 实验电路结构图NO.7附图2-10 实验电路结构图NO.8附图2-11 实验电路结构图NO.9附图2-12 实验电路结构图NO.BD22D21D20D19D18D17VCC87654321SDA (PIO79)SCL (PIO78)24C01GNDVCCPIO77PIO766PS/254321GNDVCCD-(PIO76)D+(PIO77)SLAVEUSB GND键12键11键9键1010K X 4PIO75PIO74PIO72PIO73VCCP I O 71P I O 76P I O 77P I O 70P I O 69P I O 68数码14数码13数码12数码11数码10数码9PIO67PIO66PIO65PIO64PIO63PIO62PIO61PIO60hg f e d c b a 888888附图2-13 实验电路结构图COM万能接插口与结构图信号/与芯片引脚对照表附录二:《EDA技术》部分实验参考源程序一、8位硬件加法器设计程序如下:LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY ADDER8 ISPORT ( CIN : IN STD_LOGIC;A, B : IN STD_LOGIC_VECTOR(7 DOWNTO 0);S : OUT STD_LOGIC_VECTOR(7 DOWNTO 0);COUT : OUT STD_LOGIC );END ADDER8;ARCHITECTURE behav OF ADDER8 ISSIGNAL SINT : STD_LOGIC_VECTOR(8 DOWNTO 0);BEGINSINT <= ('0'& A) + B + CIN ;S <= SINT(7 DOWNTO 0); COUT <= SINT(8);END behav;选择实验电路NO.1验证此加法器的功能。

场效应管参数对照表

场效应管参数对照表场效应管(Field Effect Transistor,简称FET),是一种常用的半导体器件,其工作原理基于场效应。

场效应管分为两种基本类型:N-沟道型场效应管(N-channel FET)和P-沟道型场效应管(P-channel FET)。

场效应管有着很多特性参数,下面是场效应管常见参数的对照表。

1. 驱动电压(Vds):场效应管的驱动电压是指在引脚之间的电压差,也成为漏极与源极之间的电压。

该驱动电压决定了场效应管的导通与截止,一般用正参考电压。

2. 阈值电压(Vth):阈值电压是指场效应管悬浮增益区通过导通的初始电压,也就是漏极电流开始出现的电压。

阈值电压决定了FET是否在导通状态,一般用负参考电压。

3.漏极电流(Id):漏极电流是指通过场效应管漏极的电流,当驱动电压大于阈值电压时,场效应管导通,漏极电流会随之增加。

4. 器件尺寸(Size):场效应管的尺寸通常由器件的长度(L)和宽度(W)决定。

尺寸越大,场效应管的漏极电流也越大。

5. 开关速度(Switching Speed):场效应管的开关速度指的是从导通到截止或者从截止到导通的反应时间。

开关速度快的场效应管适用于高频应用。

6. 衰减(Attenuation):场效应管的衰减是指信号经过场效应管后的信号衰减量。

7. 耐压(Vdss):耐压是指场效应管在截止状态下可以承受的最大电压。

一般情况下,Vdss会比驱动电压Vds的值要大。

8. 输入电容(Ciss):输入电容是指场效应管输入端的容量。

输入电容决定了场效应管对输入信号的响应速度。

9. 输出电阻(Rds):输出电阻是指场效应管导通状态下,漏极与源极之间的等效电阻。

输出电阻越小,对负载输出能力越强。

10. 控制源电压(Vgs):控制源电压是指场效应管的栅极电压,通过改变栅极电压,可以控制场效应管的导通与截止。

以上是几个常见的场效应管参数对照表。

不同应用场景的场效应管参数有所不同,使用时需根据具体需求来选择合适的场效应管。

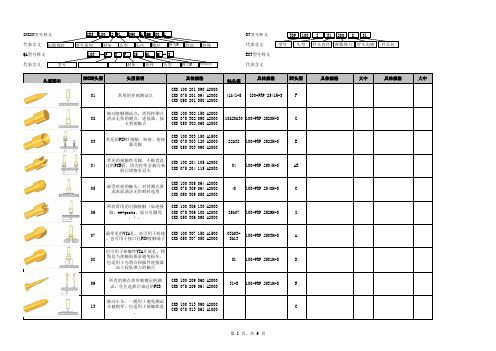

各品牌探针对照表

污染部分引脚。

GKS 075 288 120 A2000

07 100-PRP 2507H-S

89

建议未清洗过的PCB,特殊形状 接触的钢头设计,任何污染颗

粒都能推出接触点

GKS 100 289 050 A2000 GKS 075 289 050 A2000

08&08-S 100-PRP 2508H-S

INGUN型号释义

代表含义 标准探针

QA型号释义

代表含义

型号

GKS 100 2 91 090 A 20 00 L

型号系列 100

材质 头型 头径 镀层 P R P 25 61 H

弹力N 脖高 S

特殊

材质

系列

头型

弹力N

特殊说明

BT型号释义 代表含义 ECT型号释义 代表含义

TOP 100 I 31 200 G S1 型号 头型 针头直径 弹簧弹力 针头电镀

有2个逢场锋利的钢头,比较理 93 想的接触点为清洗过的PCB及其

它一些特殊要求

修改后的标准匕首(91头

GKS 100 297 090 A2000

97

型),也普遍使用,用于上过 GKS 075 297 064 A2000

43 100-PRP 2543H-S

WW

密封漆的VIA孔及测点

GKS 050 297 050 A2000

GKS 100 305 064 A2000 GKS 075 305 064 A2000 GKS 050 305 050 A2000

40 100-PRP 2540H-S

C

所有常用的引脚接触(如连接 GKS 100 306 130 A2000

06

器,ww-posts,部分引脚等 GKS 075 306 100 A2000 29&07 100-PRP 2529H-S

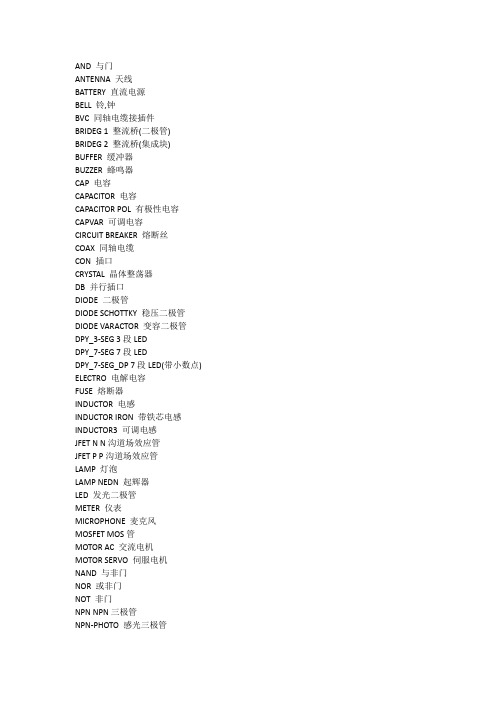

Altium designer元器件对照表和布线笔记

ANTENNA 天线BATTERY 直流电源BELL 铃,钟BVC 同轴电缆接插件BRIDEG 1 整流桥(二极管) BRIDEG 2 整流桥(集成块) BUFFER 缓冲器BUZZER 蜂鸣器CAP 电容CAPACITOR 电容CAPACITOR POL 有极性电容CAPVAR 可调电容CIRCUIT BREAKER 熔断丝COAX 同轴电缆CON 插口CRYSTAL 晶体整荡器DB 并行插口DIODE 二极管DIODE SCHOTTKY 稳压二极管DIODE VARACTOR 变容二极管DPY_3-SEG 3段LEDDPY_7-SEG 7段LEDDPY_7-SEG_DP 7段LED(带小数点) ELECTRO 电解电容FUSE 熔断器INDUCTOR 电感INDUCTOR IRON 带铁芯电感INDUCTOR3 可调电感JFET N N沟道场效应管JFET P P沟道场效应管LAMP 灯泡LAMP NEDN 起辉器LED 发光二极管METER 仪表MICROPHONE 麦克风MOSFET MOS管MOTOR AC 交流电机MOTOR SERVO 伺服电机NAND 与非门NOR 或非门NOT 非门NPN NPN三极管NPN-PHOTO 感光三极管OR 或门PHOTO 感光二极管PNP 三极管NPN DAR NPN三极管PNP DAR PNP三极管POT 滑线变阻器PELAY-DPDT 双刀双掷继电器RES1.2 电阻RES3.4 可变电阻RESISTOR BRIDGE ? 桥式电阻RESPACK ? 电阻SCR 晶闸管PLUG ? 插头PLUG AC FEMALE 三相交流插头SOCKET ? 插座SOURCE CURRENT 电流源SOURCE VOLTAGE 电压源SPEAKER 扬声器SW ? 开关SW-DPDY ? 双刀双掷开关SW-SPST ? 单刀单掷开关SW-PB 按钮THERMISTOR 电热调节器TRANS1 变压器TRANS2 可调变压器TRIAC ? 三端双向可控硅TRIODE ? 三极真空管VARISTOR 变阻器ZENER ? 齐纳二极管DPY_7-SEG_DP 数码管SW-PB 开关74系列:74LS00 TTL 2输入端四与非门74LS01 TTL 集电极开路2输入端四与非门74LS02 TTL 2输入端四或非门74LS03 TTL 集电极开路2输入端四与非门74LS122 TTL 可再触发单稳态多谐振荡器74LS123 TTL 双可再触发单稳态多谐振荡器74LS125 TTL 三态输出高有效四总线缓冲门74LS126 TTL 三态输出低有效四总线缓冲门74LS13 TTL 4输入端双与非施密特触发器74LS132 TTL 2输入端四与非施密特触发器74LS133 TTL 13输入端与非门74LS136 TTL 四异或门74LS138 TTL 3-8线译码器/复工器74LS139 TTL 双2-4线译码器/复工器74LS14 TTL 六反相施密特触发器74LS145 TTL BCD—十进制译码/驱动器74LS15 TTL 开路输出3输入端三与门74LS150 TTL 16选1数据选择/多路开关74LS151 TTL 8选1数据选择器74LS153 TTL 双4选1数据选择器74LS154 TTL 4线—16线译码器74LS155 TTL 图腾柱输出译码器/分配器74LS156 TTL 开路输出译码器/分配器74LS157 TTL 同相输出四2选1数据选择器74LS158 TTL 反相输出四2选1数据选择器74LS16 TTL 开路输出六反相缓冲/驱动器74LS160 TTL 可预置BCD异步清除计数器74LS161 TTL 可予制四位二进制异步清除计数器74LS162 TTL 可预置BCD同步清除计数器74LS163 TTL 可予制四位二进制同步清除计数器74LS164 TTL 八位串行入/并行输出移位寄存器74LS165 TTL 八位并行入/串行输出移位寄存器74LS166 TTL 八位并入/串出移位寄存器74LS169 TTL 二进制四位加/减同步计数器74LS17 TTL 开路输出六同相缓冲/驱动器74LS170 TTL 开路输出4×4寄存器堆74LS173 TTL 三态输出四位D型寄存器74LS174 TTL 带公共时钟和复位六D触发器74LS175 TTL 带公共时钟和复位四D触发器74LS180 TTL 9位奇数/偶数发生器/校验器74LS181 TTL 算术逻辑单元/函数发生器74LS185 TTL 二进制—BCD代码转换器74LS190 TTL BCD同步加/减计数器74LS191 TTL 二进制同步可逆计数器74LS192 TTL 可预置BCD双时钟可逆计数器74LS193 TTL 可预置四位二进制双时钟可逆计数器74LS194 TTL 四位双向通用移位寄存器74LS195 TTL 四位并行通道移位寄存器74LS196 TTL 十进制/二-十进制可预置计数锁存器74LS197 TTL 二进制可预置锁存器/计数器74LS20 TTL 4输入端双与非门74LS21 TTL 4输入端双与门74LS22 TTL 开路输出4输入端双与非门74LS221 TTL 双/单稳态多谐振荡器74LS240 TTL 八反相三态缓冲器/线驱动器74LS241 TTL 八同相三态缓冲器/线驱动器74LS243 TTL 四同相三态总线收发器74LS244 TTL 八同相三态缓冲器/线驱动器74LS245 TTL 八同相三态总线收发器74LS247 TTL BCD—7段15V输出译码/驱动器74LS248 TTL BCD—7段译码/升压输出驱动器74LS249 TTL BCD—7段译码/开路输出驱动器74LS251 TTL 三态输出8选1数据选择器/复工器74LS253 TTL 三态输出双4选1数据选择器/复工器74LS256 TTL 双四位可寻址锁存器74LS257 TTL 三态原码四2选1数据选择器/复工器74LS258 TTL 三态反码四2选1数据选择器/复工器74LS259 TTL 八位可寻址锁存器/3-8线译码器74LS26 TTL 2输入端高压接口四与非门74LS260 TTL 5输入端双或非门74LS266 TTL 2输入端四异或非门74LS27 TTL 3输入端三或非门74LS273 TTL 带公共时钟复位八D触发器74LS279 TTL 四图腾柱输出S-R锁存器74LS28 TTL 2输入端四或非门缓冲器74LS283 TTL 4位二进制全加器74LS290 TTL 二/五分频十进制计数器74LS293 TTL 二/八分频四位二进制计数器74LS295 TTL 四位双向通用移位寄存器74LS298 TTL 四2输入多路带存贮开关74LS299 TTL 三态输出八位通用移位寄存器74LS30 TTL 8输入端与非门74LS32 TTL 2输入端四或门74LS322 TTL 带符号扩展端八位移位寄存器74LS323 TTL 三态输出八位双向移位/存贮寄存器74LS33 TTL 开路输出2输入端四或非缓冲器74LS347 TTL BCD—7段译码器/驱动器74LS352 TTL 双4选1数据选择器/复工器74LS353 TTL 三态输出双4选1数据选择器/复工器74LS365 TTL 门使能输入三态输出六同相线驱动器74LS365 TTL 门使能输入三态输出六同相线驱动器74LS366 TTL 门使能输入三态输出六反相线驱动器74LS367 TTL 4/2线使能输入三态六同相线驱动器74LS368 TTL 4/2线使能输入三态六反相线驱动器74LS37 TTL 开路输出2输入端四与非缓冲器74LS373 TTL 三态同相八D锁存器74LS374 TTL 三态反相八D锁存器74LS375 TTL 4位双稳态锁存器74LS377 TTL 单边输出公共使能八D锁存器74LS378 TTL 单边输出公共使能六D锁存器74LS379 TTL 双边输出公共使能四D锁存器74LS38 TTL 开路输出2输入端四与非缓冲器74LS380 TTL 多功能八进制寄存器74LS39 TTL 开路输出2输入端四与非缓冲器74LS390 TTL 双十进制计数器74LS393 TTL 双四位二进制计数器74LS40 TTL 4输入端双与非缓冲器74LS42 TTL BCD—十进制代码转换器74LS352 TTL 双4选1数据选择器/复工器74LS353 TTL 三态输出双4选1数据选择器/复工器74LS365 TTL 门使能输入三态输出六同相线驱动器74LS366 TTL 门使能输入三态输出六反相线驱动器74LS367 TTL 4/2线使能输入三态六同相线驱动器74LS368 TTL 4/2线使能输入三态六反相线驱动器74LS37 TTL 开路输出2输入端四与非缓冲器74LS373 TTL 三态同相八D锁存器74LS374 TTL 三态反相八D锁存器74LS375 TTL 4位双稳态锁存器74LS377 TTL 单边输出公共使能八D锁存器74LS378 TTL 单边输出公共使能六D锁存器74LS379 TTL 双边输出公共使能四D锁存器74LS38 TTL 开路输出2输入端四与非缓冲器74LS380 TTL 多功能八进制寄存器74LS39 TTL 开路输出2输入端四与非缓冲器74LS390 TTL 双十进制计数器74LS393 TTL 双四位二进制计数器74LS40 TTL 4输入端双与非缓冲器74LS42 TTL BCD—十进制代码转换器74LS447 TTL BCD—7段译码器/驱动器74LS45 TTL BCD—十进制代码转换/驱动器74LS450 TTL 16:1多路转接复用器多工器74LS451 TTL 双8:1多路转接复用器多工器74LS453 TTL 四4:1多路转接复用器多工器74LS46 TTL BCD—7段低有效译码/驱动器74LS460 TTL 十位比较器74LS461 TTL 八进制计数器74LS465 TTL 三态同相2与使能端八总线缓冲器74LS466 TTL 三态反相2与使能八总线缓冲器74LS467 TTL 三态同相2使能端八总线缓冲器74LS468 TTL 三态反相2使能端八总线缓冲器74LS469 TTL 八位双向计数器74LS47 TTL BCD—7段高有效译码/驱动器74LS48 TTL BCD—7段译码器/内部上拉输出驱动74LS490 TTL 双十进制计数器74LS491 TTL 十位计数器74LS498 TTL 八进制移位寄存器74LS50 TTL 2-3/2-2输入端双与或非门74LS502 TTL 八位逐次逼近寄存器74LS503 TTL 八位逐次逼近寄存器74LS51 TTL 2-3/2-2输入端双与或非门74LS533 TTL 三态反相八D锁存器74LS534 TTL 三态反相八D锁存器74LS54 TTL 四路输入与或非门74LS540 TTL 八位三态反相输出总线缓冲器74LS55 TTL 4输入端二路输入与或非门74LS563 TTL 八位三态反相输出触发器74LS564 TTL 八位三态反相输出D触发器74LS573 TTL 八位三态输出触发器74LS574 TTL 八位三态输出D触发器在Altium Designer中,由网络表生成PCB在Altium Designer中,我们可以用DXP设计同步装置把设计资料从一个区域转到另一个区域,它包括比较工具、ECO以及UPDATER。

各品牌探针对照表

22&32 100-PRP 2522H-S

E

04

常见的接触性引脚,不推荐洗 过的PCB板,因为经常会被污染

脏污堵塞皇冠头

GKS 100 204 105 A2000 GKS 075 204 115 A2000

04 100-PRP 2504H-S

AB

05

最受欢迎的触头,对待测点要 求表面清洁无伤痕时选用

GKS 100 313 090 A2000 GKS 075 313 061 A1000

C

大中

第 1 页,共 6 页

最常用的尖端接触引脚。修改 GKS 100 214 050 A2000

14

后的04头型皇冠头设计防止被 GKS 075 214 050 A2000 14&84&44 100-PRP 2584H-S

AB&H BB

改进的03系列头型,接触杯口

19

采用十字槽。最大接触可靠性

是接插件针和线包位置。

24

普遍适用所有的测试点

GKS 100 224 150 A2000 GKS 075 224 130 A2000

07 100-PRP 2507H-S

T

25

普遍适用所有的测试点

GKS 100 225 130 A2000 GKS 075 225 120 A2000

I

。)。

GKS 050 306 090 A2000

07

最常见的VIA孔,亦可用于转接 GKS 100 307 150 A1500 、也可用于接口孔PIN接触端子 GKS 050 307 050 A2000

03&03S&13

100-PRP 2503H-S

A

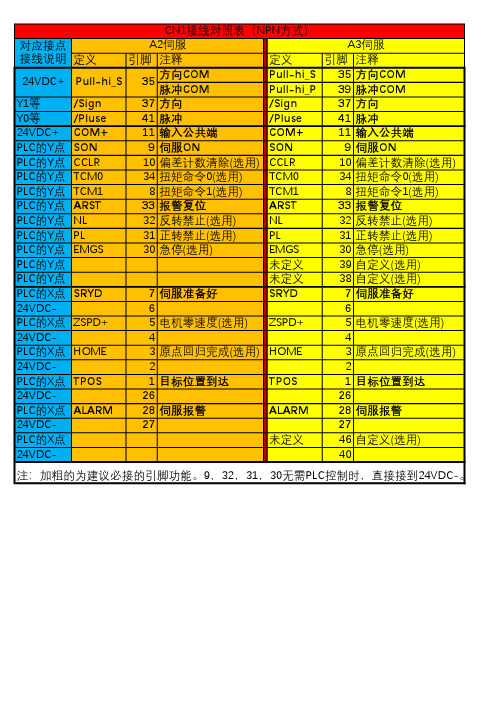

台达A2 A3系列伺服CN1接线对照表

定义引脚注释定义引脚注释方向COM Pull-hi_S 35方向COM 脉冲COM Pull-hi_P 39脉冲COMY1等/Sign 37方向/Sign 37方向Y0等/Pluse 41脉冲/Pluse 41脉冲24VDC+COM+11输入公共端COM+11输入公共端PLC的Y点SON 9伺服ON SON 9伺服ONPLC的Y点CCLR 10偏差计数清除(选用)CCLR 10偏差计数清除(选用)PLC的Y点TCM034扭矩命令0(选用)TCM034扭矩命令0(选用)PLC的Y点TCM18扭矩命令1(选用)TCM18扭矩命令1(选用)PLC的Y点ARST 33报警复位ARST 33报警复位PLC的Y点NL 32反转禁止(选用)NL 32反转禁止(选用)PLC的Y点PL 31正转禁止(选用)PL 31正转禁止(选用)PLC的Y点EMGS 30急停(选用)EMGS 30急停(选用)PLC的Y点未定义39自定义(选用)PLC的Y点未定义38自定义(选用)PLC的X点SRYD 7伺服准备好SRYD 7伺服准备好24VDC-66PLC的X点ZSPD+5电机零速度(选用)ZSPD+5电机零速度(选用)24VDC-44PLC的X点HOME 3原点回归完成(选用)HOME 3原点回归完成(选用)24VDC-22PLC的X点TPOS 1目标位置到达TPOS 1目标位置到达24VDC-2626PLC的X点ALARM 28伺服报警ALARM 28伺服报警24VDC-2727PLC的X点未定义46自定义(选用)24VDC-40注:加粗的为建议必接的引脚功能。

9,32,31,30无需PLC控制时,直接接到24VDC-。

CN1接线对照表(NPN方式)35Pull-hi_S 24VDC+对应接点接线说明A2伺服A3伺服。

集成电路引脚及引脚功能识读、测试

在学习常用集成功放器件之后安排:查一查查阅各种资料,了解功放电路的应用实例,了解集成功放的类型和功用。

做一做集成功率放大器的识别(1)查阅资料,识读表3-3中所列各集成功放的型号,并了解各集成功放的主要技术参数。

(2)查阅资料,识读表3-3中所列各集成功放的引脚,填写表3-3。

表3-3 集成功放的引脚号与引脚功能(3)在图3-18中画出TDA7294和LM3886的引脚排列。

(a)TDA7294 (b)LM3886图3-18 引脚排列示意图在学习常用集成运放器件之后安排:做一做借助资料识别集成运放器件的型号、引脚排列和各引脚的功能表3-6 集成运放的引脚号与引脚功能(1)识读表3-6中所列各集成运放的型号,了解各集成运放的主要技术参数;(2)识读表3-6中所列各集成运放的引脚,填写表3-6;(3)在图3-30中,完成CF353CP和CF224ALJ的引脚排列示意图。

(a)CF353CP引脚排列示意图(b)CF224ALJ引脚排列示意图图3-30 集成运放的引脚排列示意图在学习常用集成编码器件之后安排:做一做【实验设备与器材】数字电路实验箱,74LS147、74LS148、CC40147、CC40148各1只,发光二极管5只,390Ω电阻5只。

1.熟悉74LS147、CC40148的引脚及功能(1)查阅资料,熟悉74LS147、CC40148的引脚排列和引脚功能,在图8-15中标注引脚功能。

图8-15 74LS147、CC40148的引脚及其功能(2)查阅资料,熟悉74LS147、CC40148的功能,并分别与CC40147、74LS148的功能进行比较,找出其异同之处。

2.测试74LS148的逻辑功能【实验步骤】(1)将74LS148插入数字电路实验箱,按图8-16所示,将其各输入端接实验箱上的逻辑开关。

注意输出指示用发光二极管正极接正电源,当输出为0时发光,当输出为1时不发光。

(2)接通电源,按表8-5,拨动逻辑电平开关,使输入端接高电平或低电平,输入控制信号和编码信号,观察输出端的编码输出状态。

FPGA管脚分配图

169

FLAS H_ CS

156

音频 CODEC 模块(大板)

信号名称

对应 FPGA 引脚

SDIN

27

SCLK

33

CS

28

音频 CODEC 模块(小板)

信号名称

对应 FPGA 引脚

SDIN

93

SCLK

94

CS

88

音源模块

RESET

86

DATA

84

BUS Y

153

时钟源模块

信号名称 CLOCK(大板) CLOCK(小板)

216 VGA 接口(大板)

对应 FPGA 引脚

R

58

G

59

B

60

HS

61

VS 信号名称

62 VGA 接口(小板)

对应 FPGA 引脚

R

239

G

238

B

237

HS

235

VS 信号名称

236 PS/2 接口(大板上)

对应 FPGA 引脚

CLOCK

49

DATA 信号名称

82 PS/2 接口(大板下)

对应 FPGA 引脚

98

DB2

95

DB3

143

DB4

141

DB5

140

DB6

139

DB7

138

DB8

136

DB9

135

DB10

134

DB11

133

DB12

132

DB13

131

DB14

128

DB15

127

DB16

116

DB17

电容 贴片 尺寸封装 对照表

电容贴片尺寸封装对照表1. 电容的基本概念和作用电容是一种用来储存电荷的器件,是电子电路中常用的元件之一。

它的作用包括滤波、耦合、隔直、稳压、调谐等。

在不同的电子设备中,会选择不同尺寸和封装的电容来满足各种不同的电路需求。

2. 贴片电容的特点和优势贴片电容是一种表面贴装技术(SMT)元件,具有尺寸小、重量轻、功率损耗小、高频特性好等优点。

在现代电子产品中,贴片电容广泛应用于电子产品的制造,因其在印刷电路板上可以节省很多空间,降低成本,提高生产效率。

3. 电容尺寸封装对照表以下是常见的贴片电容尺寸封装对照表(以毫米为单位):| 封装规格 | 封装尺寸 | 长 | 宽 | 高 | 引脚间距 ||---------|---------|----|----|----|----------|| 0603 | 1.6×0.8 | 1.6| 0.8| 0.8| 0.5 || 0805 | 2.0×1.25| 2.0| 1.25| 0.8| 1.25 || 1206 | 3.2×1.6 | 3.2| 1.6| 0.8 | 2.7 || 1210 | 3.2×2.5 | 3.2| 2.5| 1.2 | 2.7 || 1812 | 4.5×3.5 | 4.5| 3.5| 1.2 | 3.2 || 2220 | 5.7×5.0 | 5.7| 5.0| 1.5 | 5.08 |在实际应用中,根据电路设计的需求,可以选择不同规格的贴片电容来实现相应的功能。

4. 贴片电容的应用场景贴片电容广泛应用于各种电子设备中,包括手机、平板电脑、电视机、数码相机、音响设备等。

它们可以用于电源管理、信号处理、滤波等功能,是现代电子设备中不可或缺的元件。

5. 个人观点和总结贴片电容作为一种重要的电子元件,对于现代电子设备的制造和性能起着至关重要的作用。

通过掌握不同尺寸和封装的贴片电容对照表,可以更好地选择合适的电容来满足电路设计的需求。

引脚介绍

非屏蔽中断( 非屏蔽中断( NMI),上升沿有效。 ) 上升沿有效。 不受中断允许标志IF的控制 , 不受中断允许标志 的控制, 也不能用软件 的控制 进行屏蔽。 进行屏蔽。 可屏蔽中断(INTR和 INTA 中断响应信号) 可屏蔽中断( 和 中断响应信号) 当INTR=1,并且中断允许标志位 ,并且中断允许标志位IF=1时,则CPU 时 在当前指令周期结束后 转入中断响应周期。 指令周期结束后, 在当前指令周期结束后,转入中断响应周期。 中断响应信号: 对中断请求信号INTR 对中断请求信号 INTA 中断响应信号:CPU对中断请求信号 的响应。目的为了获取中断类型码。 的响应。目的为了获取中断类型码。

控制引脚线

8086/8088的引脚信号及工作模式 2.3 8086/8088的引脚信号及工作模式

1. 地址、数据引脚线 AD0~AD15: 分时复用的地址数据引脚线,双向、三态。 T1期间作地址线A15~A0用,输出存储单元低16位地址。 T2~T3期间作数据线D15~D0用,双向。 写操作为T2~T3; 读操作为T3,T2处于悬空状态; CPU响应中断及系统总线处理“保持响应”状态时, AD0~AD15处于悬空状态。

择两种工作模式? 择两种工作模式?

思考:何时传输

地址, 地址,何时传输 数据? 数据?

•

8086/8088的引脚信号及工作模式 2.3 8086/8088的引脚信号及工作模式

2.2.1 8086CPU的引脚及其功能 的引脚及其功能 8086有 40个引脚 , 其中第 有 个引脚 33 (最小 最大模式)脚很 最小/最大模式 最大模式) 关键,它是一条输入线, 关键,它是一条输入线,可 以加高电平, 以加高电平,也可以加低电 平,由该线所加电平的高或 低电平决定24-31引脚的功 低电平决定 引脚的功 能 ( 24-31引脚括号内为最 引脚括号内为最 大模式功能) 大模式功能)其他引脚不受 第 33 引 脚 的 影 响 , 我 们 把 这部分引脚称为一般引脚 一般引脚。 这部分引脚称为一般引脚。

1155 CPU引脚对照表

CPU_VTT

EXP_RXN4

EXP_TXN5

EXP_TXN8

NC NC

GND GND

EXP_RXN10

GND

CPU_VTT

EXP_TXP11

EXP_TXN13

NC NC

GND GND

GND

CPU_VTT

NC NC

GND GND

GND

CPU_VTT

CPU_VTT

DMI_0TXP

DMI_1TXN

GND GND

EXP_RXP2

GND GND

EXP_RXP3

GND GND

EXP_TXP9

VCCSA VCORE VCCSA

VCCSA VCCSA

EXP_RXP0

EXP_RXN1

EXP_TXN3

GND

VCCSA VCCSA VCCSA

GND

CPU_VTT

EXP_RXP4

U_VTT

GND GND

EXP_TXP8

GND

(-DCLKB2)

SBAB0

MAAA6 DDR_15V MAAA4 MAAA3 DDR_15V MAAA9 MAAA7 MAAA8

MAAA12 MAAA15 MAAA11 MAAA14

DDR_15V DDR_15V

GND

CPU_VTT

(-DCLKB1)

GND GND

(-DCLKB3)

GND

DDR_15V

MODT_A1

NC NC

DDR_15V

MODT_A3

CPU_VAXG

CPU_VAXG

CPU_VAXG

CPU_VAXG

CPU_VAXG

AMD CPU型号及接口对照表

以下内容都是在网上收集而得,希望对各位有所帮助~Socket ASocket A接口,也叫Socket 462,是AMD公司Athlon XP和Duron处理器的插座标准。

Socket A接口具有462插孔,可以支持133MHz外频。

如同Socket 370一样,降低了制造成本,简化了结构设计。

在这个接口上,AMD公司推出了多款CPU,从最开始的雷鸟、毒龙,到后来的Athlon XP、新毒龙、部分采用SocketA接口的闪龙。

其产品跨度极大,是AMD公司赶超Intel公司的重要阵地。

现在AMD公司虽然已经不再出产Socket A接口的CPU,但是Socket A接口的CPU在目前使用的PC中仍占有巨大的份额。

Socket 754Socket 754是2003年9月AMD64位桌面平台最初发布时的标准插槽,具有754个CPU针脚插孔,支持200MHz外频和800MHz的HyperTransport总线频率,但不支持双通道内存技术。

目前采用此种插槽的有面向桌面平台的Athlon 64的低端型号和Sempron的高端型号,以及面向移动平台的Mobile Sempron、Mobile Athlon 64以及Turion 64。

随着AMD从2006年开始全面转向支持DDR2内存,今后桌面平台的Socket 754插槽逐渐被具有940根CPU针脚插孔、支持双通道DDR2内存的Socket AM2插槽所取代从而使AMD的桌面处理器接口走向统一,而与此同时移动平台的Socket 754插槽也逐渐被具有638根CPU针脚插孔、支持双通道DDR2内存的Socket S1插槽所取代,在2007年底完成自己的历史使命从而被淘汰。

Socket 939Socket 939是AMD公司2004年6月才发布的64位桌面平台插槽标准,具有939个CPU针脚插孔,支持200MHz外频和1000MHz的HyperTransport总线频率,并且支持双通道内存技术。

引脚介绍

请

进行屏蔽。

求

和

可屏蔽中断(INTR和 INTA中断响应信号)

响 应

当INTR=1,并且中断允许标志位IF=1时,则CPU

操

在当前指令周期结束后,转入中断响应周期。

作

信

INTA 中断响应信号:CPU对中断请求信号INTR

号

的响应。目的为了获取中断类型码。

返回

2.3 8086/8088的引脚信号及工作模式

制 作用:控制8286/8287的数据传送方向。

信

号

DT/R =1时,发送;DT/R=0时,接收。

返回

2.3 8086/8088的引脚信号及工作模式

TEST 测试信号

高电平:CPU继续空转等待;

等

低电平:退出等待,执行下一条指令。

待

检 READY准备就绪信号

测

操

作用:使CPU和低速的存储器或I/O设备之间实

பைடு நூலகம்

外

分时复用。

部 引

8086与8088CPU引脚28信号相反M/IO,IO/M)

脚

引脚34信号,功能与8086稍有不同。

的

区 别

8086有总线高位有效信号,一次可读写8位或16

位数据;而8088读写16位的数据需要两次访问

存储器或端口。

2.3 8086/8088的引脚信号及工作模式

内部结构的区别

8086的总线接口部件BIU中有一个6字节的指令队列。 当 指令队列有2个字节空余时,BIU自动取指令到指令队列。 8088CPU中只有一个4字节的指令队列。当8088指令 队列有1个字节的空余时,BIU自动取指令到指令队列。

M/IO DT/R DEN ALE INTA TEST

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

以"实验二一般计数器的设计"为例

[实验目的]

1、熟悉Quartus II的文本输入方式, 掌握其编辑、编译综合、仿真的操作方法;

2、学习计数器的设计、仿真和硬件测试,进一步熟悉VHDL设计技术。

[实验仪器]

PC机、EDA实验箱一台

Quartus II 6.0软件

[实验内容]

二、实验内容:

按QuartusⅡ的文本输入设计方法与流程完成0-9一般计数器的输入、逻辑综合编译、仿真测试等步骤,得出正确的仿真波形图。

最后进行对目标芯片(EP1K30TC144-3)进行编程下载,并进行硬件测试,验证本项设计的功能。

三、实验步骤:

1、代码编写。

根据计数器的工作原理,在QuartusⅡ6.0开发环境中编写一般计数器的VHDL源程序(建议文件名为cnt10.vhd),具体参考教材中相关章节。

2、波形仿真。

对cnt10.vhd综合编译成功后,建立波形文件进行波形仿真,启动仿真器Simulator,观察输出波形的情况,在软环境下验证设计的正确性。

3、引脚锁定和程序下载。

参选实验电路模式5和附表一中的EP1K30/50144-PIN TQFP 目标芯片,确定输入引脚并在开发环境中进行引脚锁定操作后重新综合编译,成功后进行下载操作。

(建议:键1、键5、键8分别为输入信号clk、en、rst,数码管1作为q[3..0]的输出显示。

)

4、根据代码中的定义,按动实验箱上的相应按键,得到不同的输入信号组合;观察数码管1,检查计数器的设计结果是否正确。

四、实验报告:

1、设计流程图。

2、VHDL代码。

3、仿真波形图。

4、硬件测试数据表。

5、分析实验结果。

6、心得体会。

[实验原理]

1、试验箱电路结构图

[实验步骤]

1、查看目标设备是否选择正确(这个应该在新建工程的时候就已经确定了,如果没有注意,

那么这一步是必须的):Assignments——>Dvice

EP1K30TC144-3

2、编译一次

3、引脚绑定

使用结构图7 :

键5和键8可用作EN和RST输入。

CLK可用键1作手动产生,也可以使用实验内容5里的时钟信号。

四位输出【Q3..Q0】可以使用数码管1、2、4、5、7、8中任一个。

引脚锁定参考后面附表蓝色那列。

如:看电路结构图键5连到目标芯片PIO4,

查表PIO4 为PIN_13

故CLK 锁定PIN_13,其他引脚依此类推。

4、绑定后再编译一次

5、点击Tools——>programmer。

这里两个地方需要修改:

标号1的地方:点击Hardware Setup

再点击Add Hardware 如下图点击OK 再点击Close

标号2的地方mode 里改成Passive Sserial

6、打开试验箱电源开关,选择模式7,然后点击Start下载。

[实验要求]

1、读懂程序

2、硬件演示

附表一是GW48CK/GK/PK系统(万能接插口与结构图信号/与芯片引脚对照表)。