实验电路结构图及芯片引脚对应表

(整理)常用集成电路引脚图

规划编制单位对可能造成不良环境影响并直接涉及公众环境权益的专项规划,应当在规划草案报送审批前,采取调查问卷、座谈会、论证会、听证会等形式,公开征求有关单位、专家和公众对环境影响报告书的意见。

疾病成本法和人力资本法将环境污染引起人体健康的经济损失分为直接经济损失和间接经济损失两部分。直接经济损失有:预防和医疗费用、死亡丧葬费;间接经济损失有:影响劳动工时造成的损失(包括病人和非医务人员护理、陪住费)。这种方法一般通常用在对环境有明显毒害作用的特大型项目。

1.环境影பைடு நூலகம்评价依据的环境标准体系

(6)生态保护措施能否有效预防和控制生态破坏。

常用集成电路引脚图

一、 TTL数字集成电路引脚图

二、CMOS集成电路引脚图

第五章 环境影响评价与安全预评价

2.建设项目环境影响评价文件的报批时限

2.规划环境影响评价的内容

6.提出安全对策措施建议

市场价格在有些情况下(如对市场物品)可以近似地衡量物品的价值,但不能准确度量一个物品的价值。三者的关系为:

EDA实验1lxm二选一数据选择器

实验一二选一数据选择器VHDL设计Quartus II 6.0开发环境与EDA实验箱使用一实验目的1.熟悉在Quartus II 6.0环境下原理图输入方法。

2.熟悉Quartus II 6.0环境下编辑、编译综合、仿真的操作方法。

3、掌握利用EDA软件进行电路设计的详细流程;4、熟悉EDA实验箱的基本使用方法。

学会对实验板上的FPGA/CPLD进行编程下载,硬件验证自己的设计项目。

二实验仪器PC机、Quartus II 6.0软件三实验内容1.详细解读教材117页。

2.在QuartusⅡ上输入该设计的原理图,并进行编辑、编译、综合、适配、仿真。

3.给出其所有信号的时序仿真波形。

四实验原理及步骤1.启动Quartus II 6.0软件在桌面上双击Quartus II 6.0图标或者在开始—>所有程序—>Altera—> Quartus II 6.0,如下图2.建立工作库文件夹及工程任何一次设计都是一项工程(Project),所有此工程相关的所有设计文件都需要放在同一个文件夹里。

不同的设计放在不同的文件夹中。

在E盘下建立一个存放本次设计的工程文件夹,比如“shiyan1”。

注意不要使用中文文件夹,文件夹的存放路径也不要包含中文。

注意本实验室计算机C盘和D盘是重启后复原,不要将任何文件和文件夹放置在桌面或者C、D盘下。

初次打开Quartus II 6.0,会有如图提示:选择是的情况下,首先是新工程向导:介绍下一步下一步下一步,选择目标芯片,首先在Family栏选择ACEX1K系列,然后选择此系列的具体芯片:EP1K30TC144-3。

注意不要选成了EP1K30TC144-3。

下一步就点完成。

3.建立文本程序文件选择File菜单下的New或者直接点击工具栏中的新建图标,选择新建文件类型为VHDL File。

接下来另存文件:保存时需更改文件名与项目名称一样,注意保存在同一个工程文件夹下面。

GW48结构图信号名与芯片引脚对照表

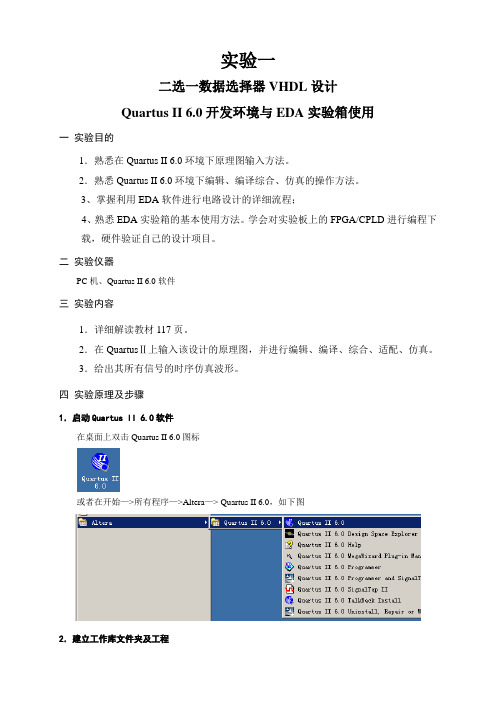

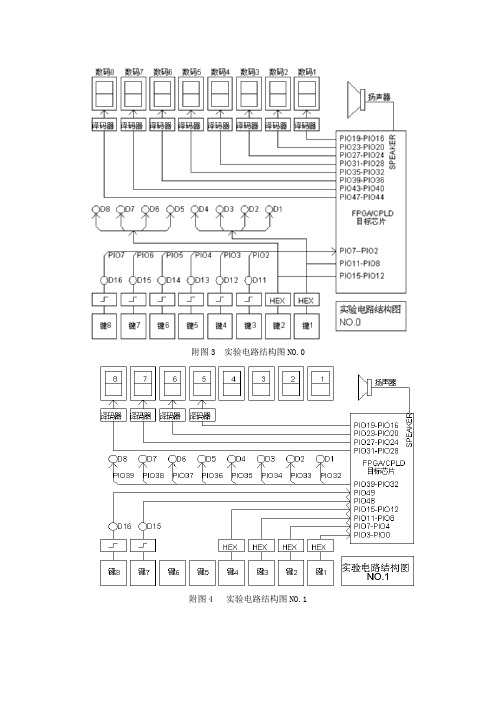

附图3 实验电路结构图NO.0附图4 实验电路结构图NO.1附图5 实验电路结构图NO.2实实实实实实实NO.3实实实实实实实实实实实实实实实实实实实实实实实实D9D16D15D14D13D12D11D10D8D7D6D5D4D3D2D1PIO8PIO9PIO10PIO11PIO12PIO13PIO14PIO15S P E A K E R实实实12345678实实实实FPGA/CPLD PIO0PIO1PIO2PIO3PIO4PIO5PIO6PIO7实1实2实3实4实5实6实7实8PIO15-PIO8PIO47-PIO44PIO43-PIO40PIO39-PIO36PIO35-PIO32PIO31-PIO28PIO27-PIO24PIO23-PIO20PIO19-PIO16附图6 实验电路结构图NO.3附图7 实验电路结构图NO.4D1PIO8D2D3D4D5D6D7D8PIO9PIO10PIO11PIO12PIO15PIO14PIO13实实实实实实实NO.5S P E A K E R实实实FPGA/CPLD 实实实实12345678D16D15D14D13D12D11D10D9PIO47-PIO44PIO43-PIO40PIO39-PIO36PIO35-PIO32PIO31-PIO28PIO27-PIO24PIO23-PIO20PIO19-PIO16实实实实实实实实实实实实实实实实实实实实实实实实PIO15-PIO8PIO0PIO1PIO2PIO3PIO4PIO5PIO6PIO7实1实2实3实4实5实6实7实8附图8 实验电路结构图NO.5附图9 实验电路结构图NO.6D16D15D14D13D12D11D9D8PIO47D7PIO46D6PIO45D5PIO44D4PIO43D3PIO42D2PIO41PIO40D1NO.7实验电路结构图S P E A K E R扬声器FPGA/CPLD 目标芯片12345678PIO0PIO2PIO3PIO4PIO5PIO6PIO7单脉冲单脉冲单脉冲键1键2键3键4键5键6键7键8PIO47-PIO40PIO39-PIO36PIO35-PIO32PIO31-PIO28PIO27-PIO24PIO23-PIO20PIO19-PIO16译码器译码器译码器译码器译码器译码器附图10 实验电路结构图NO.7附图11 实验电路结构图NO.8附图12 实验电路结构图NO.9附图13 实验电路结构图NO.B实验电路结构图 N O .5AD 16D 15D 14D 13D 12D 11D 10D 9D 8D 7D 6D 5D 4D 3D 2D 1P I O 8J P 2(1/2,3/4)J P 2(5/6)P I O 8SPEAKER目标芯片F P G A /C P L D(23)(24)1216272610C L O C K 750K H Z A 750K H Z A F I T102C 30103C 29D A -5--+5D A 0--+5P I O 38P I O 37P I O 35C O M MD A W RC O M P ADE O C A D E N J P 22018161412108642191715131197531021V R 110K V C C +5V A I N 0A I N 1r e f (-)r e f (+)I N -1I N -06922257171415818192021E U 1A D C 0809P I O 16P I O 17P I O 18P I O 19P I O 20P I O 21P I O 22P I O 23P I O 32P I O 33P I O 35P I O 34m s b 2-12-22-32-42-52-62-7l s b 2-8E O C A D D -A A D D -B A D D -C A L E E N A B L E S T A R T扬声器P I O 39-P I O 36P I O 43-P I O 40P I O 47-P I O 4412345678数码数码数码数码数码数码数码数码译码器译码器译码器单脉冲单脉冲单脉冲P I O 0P I O 1P I O 2P I O 3P I O 4P I O 5P I O 6P I O 7P I O 15P I O 14P I O 13P I O 12P I O 11P I O 10P I O 9P I O 8键1键2键3键4键5键6键7键8附图14 实验电路结构图NO.5AD 8D 7D 6D 5D 4D 3D 2D 1译码器译码器译码器D 16D 15D 14D 13D 12D 11D 10D 9实验电路结构图 N O .5BV C C目标芯片F PG A /C P L D串行通讯接口接口电路J 75413P I O 45P I O 46P S /2接口单片机接口电路235接P C 机R S -232B 412M H Z A键复位P I O 11P I O 12P I O 13P I O 14SPEAKERA T 89C 2051E U 3P 34P 33P 32X 1X 2P 31P 30P 35R S TG N D P 37P 10P 11P 12P 13P 14P 15P 16P 17V C C 1234567891011121314151617181920P I O 15P I O 24P I O 25P I O 26P I O 27P I O 28P I O 29P I O 30P I O 31扬声器P I O 39-P I O 36P I O 43-P I O 40P I O 47-P I O 4412345678数码数码数码数码数码数码数码数码单脉冲单脉冲单脉冲P I O 0P I O 1P I O 2P I O 3P I O 4P I O 5P I O 6P I O 7P I O 15P I O 14P I O 13P I O 12P I O 11P I O 10P I O 9P I O 8键1键2键3键4键5键6键7键8附图15 实验电路结构图NO.5BD 16D 15D 14D 13D 12D 11D 10D 9D 1P I O 8D 2P I O 9D 3P I O 10D 4P I O 11D 5P I O 12D 6P I O 13D 7P I O 14D 8P I O 15译码器译码器译码器实验电路结构图 N O .5CF PG A /C P L DJ P 251p F C 27J P 2(C O M P )C O M PP I O 37L M 311V C C 10K-12+124823T L 082/1A I N 0A O U T5.1K102103+510K5.1K5.1KR 72765T L 082/2841+12-12D A 0--+5D A -5--+5滤波0滤波1F I TC O M M E U 2D A C 0832********J P 2(9,10)P I O 38D A W R 2W R 1F B93211I O U T 1I O U T 212/C S W R 2X F E R A G N D D G N D V R E F 8V C C20+5V C CD 0D 1D 2D 3D 4D 5D 6D 7765416151413P I O 24P I O 25P I O 26P I O 27P I O 28P I O 29P I O 30P I O 31P I O 43-P I O 40P I O 35-P I O 32P I O 23-P I O 20P I O 19-P I O 16目标芯片P I O 47-P I O 44译码器译码器P I O 15-P I O 812345678数码数码数码数码数码数码数码数码单脉冲单脉冲单脉冲P I O 0P I O 1P I O 2P I O 3P I O 4P I O 5P I O 6P I O 7键1键2键3键4键5键6键7键8附图16 实验电路结构图NO.5CD A C C1K REFS 1KREFSNO.5DPIO34PIO27SDASCL TEST NC NC NC PIO19PIO17PIO34PIO27GNDNC NC DOUTDIN SK CS 24CXX93CXXVCC87654321VCC GNDVCC 87654321VCC TLC549VCC PIO30PIO2987654321PIO28CSDOUT I/OCK VCC GNDREF-AIN REF+JSL141312111098765PIO26PIO24PIO25PIO31VCCLOADDACD DACC DACB DACA LDAC CLKDATA REFD REFC REFB REFA TLC5620GND VCCREFSS VCC REFSJTLJAVPIO19PIO18TLV1572PIO17SCLKVCC FS DO AINGND VREF PIO34CS 87654321VCC 4321REFSSREFINCLK VCC PIO17PIO34PIO198031VIN-VIN+CS 87654321DOUT GNDADC08031VCC ADCCD1PIO8D2D3D4D5D6D7D8PIO9PIO10PIO11PIO12PIO15PIO14PIO13实实实实实实实S P E A K E R实实实FPGA/CPLD 实实实实12345678D16D15D14D13D12D11D10D9PIO47-PIO44PIO43-PIO40PIO39-PIO36PIO35-PIO32PIO31-PIO28PIO27-PIO24PIO23-PIO20PIO19-PIO16实实实实实实实实实实实实实实实实实实实实实实实实PIO15-PIO8实实实实实实实实实PIO0PIO1PIO2PIO3PIO4PIO5PIO6PIO7实1实2实3实4实5实6实7实8附图17 实验电路结构图NO.5D附录2 GW48结构图信号名与芯片引脚对照表。

常用芯片引脚图

附录三常用芯片引脚图一、 单片机类1、MCS-51芯片介绍:MCS-51系列单片机是美国Intel 公司开发的8位单片机,又可以分为多个子系列。

MCS-51系列单片机共有40条引脚,包括32条I/O 接口引脚、4条控制引脚、2条电源引脚、2条时钟引脚。

引脚说明: P0.0~P0.7:P0口8位口线,第一功能作为通用I/O 接口,第二功能作为存储器扩展时的地址/数据复用口。

P1.0~P1.7:P1口8位口线,通用I/O 接口无第二功能。

P2.0~P2.7:P2口8位口线,第一功能作为通用I/O 接口,第二功能作为存储器扩展时传送高8位地址。

P3.0~P3.7:P3口8位口线,第一功能作为通用I/O 接口,第二功能作为为单片机的控制信号。

ALE/ PROG :地址锁存允许/编程脉冲输入信号线(输出信号)PSEN :片外程序存储器开发信号引脚(输出信号)EA/Vpp :片外程序存储器使用信号引脚/编程电源输入引脚RST/VPD :复位/备用电源引脚2、MCS-96芯片介绍:MCS-96系列单片机是美国Intel 公司继MCS-51系列单片机之后推出的16位单片机系列。

它含有比较丰富的软、硬件资源,适用于要求较高的实时控制场合。

它分为48引脚和68引脚两种,以48引脚居多。

引脚说明:RXD/P2.1 TXD/P2.0:串行数据传出分发送和接受引脚,同时也作为P2口的两条口线HS1.0~HS1.3:高速输入器的输入端HS0.0~HS0.5:高速输出器的输出端(有两个和HS1共用)Vcc :主电源引脚(+5V )Vss :数字电路地引脚(0V )Vpd :内部RAM 备用电源引脚(+5V )V REF :A/D 转换器基准电源引脚(+5V )12345678910111213141516171819204039383736353433323130292827262524232221P1.0P1.1P1.2P1.3P1.4P1.5P1.6P1.7RST RXD/P3.0TXD/P3.1INT0/P3.2INT1/P3.3T0/P3.4T1/P3.5WR/P3.6RD/P3.7XTAL2XTAL1V SS V CC P0.0/AD 0P0.1/AD 1P0.2/AD 2P0.3/AD 3P0.4/AD 4P0.5/AD 5P0.6/AD 6P0.7/AD 7EA/V PP ALE/PROG PSENP2.7/A 15P2.6/A 14P2.5/A 13P2.4/A 12P2.3/A 11P2.2/A 10P2.1/A 9P2.0/A 8803180518751AGND:A/D转换器参考地引脚XTAL1、XTAL2:内部振荡器反相器输入、输出端,常外接晶振。

74LS系列IC管脚图大全

74LS390 双十进制计数器

74LS624 压控振荡器

74LS625 压控振荡器

74LS626 压控振荡器

74LS627 压控振荡器

74LS628 压控振荡器

74LS629 压控振荡器

两片74LS283构成的8位加法器

74LS289 64位随机存取存储器

74LS289 64位随机存取存储器

74LS290异步2—5—10进制计数器

74LS290异步2—5—10进制计数器

74LS292 可编程分频器/数字定时器

74LS293 4位二进制计数器

74LS294 16位可编程模块

74LS374 八D触发器(三态同相)

74381

符号

A0 A1 A2 A3

B0 B1 B2 B3

C -1

S0 S1 S2

引脚排列

A 1 1 20 VCC

F0

B1

A2

F1

A0

B2

F2

B0

F3

S0

A3 B3

7 43 81

S1

C -1

S2

P

P

F0

G

G

F1

F3

GND 1 0 1 1 F 2

74LS381算术逻辑单元

74LS181 算术逻辑单元/功能发生器

74LS181 四位算术逻辑运算器

7 4 18 2

G 1 1 16 V cc

P1

P2

G0

G2

P0

C -1

G3

C0

P3

C1

P

G

G ND 8 9 C 2

74LS182先行进位发生器/超前进位产生器

VCC 2Ai 2Bi 2Ci-1 2Ci 2Si VCC2A 2B 2CIn 2COn+1 2F 74LS183 1COn+1 1A 1B 1CIn 1F GND 1Ai 1Bi 1Ci-1 1Ci 1Si 地

及其他系列芯片引脚图大全

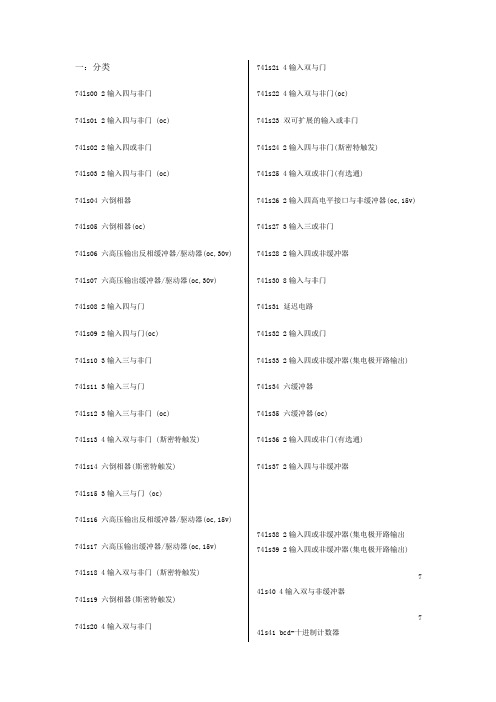

及其他系列芯片引脚图大全Document serial number【KK89K-LLS98YT-SS8CB-SSUT-SST108】一:分类74ls00 2输入四与非门74ls01 2输入四与非门 (oc)74ls02 2输入四或非门74ls03 2输入四与非门 (oc)74ls04 六倒相器74ls05 六倒相器(oc)74ls06 六高压输出反相缓冲器/驱动器(oc,30v) 74ls07 六高压输出缓冲器/驱动器(oc,30v)74ls08 2输入四与门74ls09 2输入四与门(oc)74ls10 3输入三与非门74ls11 3输入三与门74ls12 3输入三与非门 (oc)74ls13 4输入双与非门 (斯密特触发)74ls14 六倒相器(斯密特触发)74ls15 3输入三与门 (oc)74ls16 六高压输出反相缓冲器/驱动器(oc,15v) 74ls17 六高压输出缓冲器/驱动器(oc,15v)74ls18 4输入双与非门 (斯密特触发)74ls19 六倒相器(斯密特触发)74ls20 4输入双与非门74ls21 4输入双与门74ls22 4输入双与非门(oc)74ls23 双可扩展的输入或非门74ls24 2输入四与非门(斯密特触发)74ls25 4输入双或非门(有选通)74ls26 2输入四高电平接口与非缓冲器(oc,15v)74ls27 3输入三或非门74ls28 2输入四或非缓冲器74ls30 8输入与非门74ls31 延迟电路74ls32 2输入四或门74ls33 2输入四或非缓冲器(集电极开路输出)74ls34 六缓冲器74ls35 六缓冲器(oc)74ls36 2输入四或非门(有选通)74ls37 2输入四与非缓冲器74ls38 2输入四或非缓冲器(集电极开路输出74ls39 2输入四或非缓冲器(集电极开路输出)7 4ls40 4输入双与非缓冲器7 4ls41 bcd-十进制计数器4ls42 4线-10线译码器(bcd输入)7 4ls43 4线-10线译码器(余3码输入)7 4ls44 4线-10线译码器(余3葛莱码输入)7 4ls45 bcd-十进制译码器/驱动器7 4ls46 bcd-七段译码器/驱动器7 4ls47 bcd-七段译码器/驱动器7 4ls48 bcd-七段译码器/驱动器7 4ls49 bcd-七段译码器/驱动器(oc)7 4ls50 双二路2-2输入与或非门(一门可扩展)7 4ls51 双二路2-2输入与或非门7 4ls51 二路3-3输入,二路2-2输入与或非门7 4ls52 四路2-3-2-2输入与或门(可扩展)7 4ls53 四路2-2-2-2输入与或非门(可扩展)7 4ls53 四路2-2-3-2输入与或非门(可扩展) 4ls54 四路2-2-2-2输入与或非门7 4ls54 四路2-3-3-2输入与或非门7 4ls54 四路2-2-3-2输入与或非门7 4ls55 二路4-4输入与或非门(可扩展)7 4ls60 双四输入与扩展7 4ls61 三3输入与扩展7 4ls62 四路2-3-3-2输入与或扩展器7 4ls63 六电流读出接口门7 4ls64 四路4-2-3-2输入与或非门7 4ls65 四路4-2-3-2输入与或非门(oc)7 4ls70 与门输入上升沿jk触发器7 4ls71 与输入r-s主从触发器7 4ls72 与门输入主从jk触发器7 4ls73 双j-k触发器(带清除端)4ls74 正沿触发双d型触发器(带预置端和清除端)7 4ls75 4位双稳锁存器7 4ls76 双j-k触发器(带预置端和清除端)7 4ls77 4位双稳态锁存器7 4ls78 双j-k触发器(带预置端,公共清除端和公共时钟端) 4ls80 门控全加器7 4ls81 16位随机存取存储器7 4ls82 2位二进制全加器(快速进位)7 4ls83 4位二进制全加器(快速进位)7 4ls84 16位随机存取存储器74ls85 4位数字比较器7 4ls86 2输入四异或门7 4ls87 四位二进制原码/反码/oi单元7 4ls89 64位读/写存储器7 4ls90 十进制计数器7 4ls91 八位移位寄存器7 4ls92 12分频计数器(2分频和6分频)7 4ls93 4位二进制计数器7 4ls94 4位移位寄存器(异步)7 4ls95 4位移位寄存器(并行io)7 4ls96 5位移位寄存器7 4ls97 六位同步二进制比率乘法器7 4ls100 八位双稳锁存器7 4ls103 负沿触发双j-k主从触发器(带清除端)7 4ls106 负沿触发双j-k主从触发器(带预置,清除,时钟)7 4ls107 双j-k主从触发器(带清除端)4ls108 双j-k主从触发器(带预置,清除,时钟)7 4ls109 双j-k触发器(带置位,清除,正触发)7 4ls110 与门输入j-k主从触发器(带锁定)7 4ls111 双j-k主从触发器(带数据锁定)7 4ls112 负沿触发双j-k触发器(带预置端和清除端)7 4ls113 负沿触发双j-k触发器(带预置端)7 4ls114 双j-k触发器(带预置端,共清除端和时钟端)7 4ls116 双四位锁存器7 4ls120 双脉冲同步器/驱动器7 4ls121 单稳态触发器(施密特触发)7 4ls122 可再触发单稳态多谐振荡器(带清除端)7 4ls123 可再触发双单稳多谐振荡器7 4ls125 四总线缓冲门(三态输出) 4ls126 四总线缓冲门(三态输出)7 4ls128 2输入四或非线驱动器7 4ls131 3-8译码器7 4ls132 2输入四与非门(斯密特触发)7 4ls133 13输入端与非门7 4ls134 12输入端与门(三态输出)7 4ls135 四异或/异或非门7 4ls136 2输入四异或门(oc)7 4ls137 八选1锁存译码器/多路转换器7 4ls138 3-8线译码器/多路转换器7 4ls139 双2-4线译码器/多路转换器7 4ls140 双4输入与非线驱动器7 4ls141 bcd-十进制译码器/驱动器7 4ls142 计数器/锁存器/译码器/驱动器4ls145 4-10译码器/驱动器7 4ls147 10线-4线优先编码器7 4ls148 8线-3线八进制优先编码器7 4ls150 16选1数据选择器(反补输出)7 4ls151 8选1数据选择器(互补输出)7 4ls152 8选1数据选择器多路开关7 4ls153 双4选1数据选择器/多路选择器7 4ls154 4线-16线译码器7 4ls155 双2-4译码器/分配器(图腾柱输出)7 4ls156 双2-4译码器/分配器(集电极开路输出)7 4ls157 四2选1数据选择器/多路选择器7 4ls158 四2选1数据选择器(反相输出)7 4ls160 可预置bcd计数器(异步清除)7 4ls161 可预置四位二进制计数器(并清除异步) 4ls162 可预置bcd计数器(异步清除)7 4ls163 可预置四位二进制计数器(并清除异步)7 4ls164 8位并行输出串行移位寄存器7 4ls165 并行输入8位移位寄存器(补码输出)7 4ls166 8位移位寄存器7 4ls167 同步十进制比率乘法器7 4ls168 4位加/减同步计数器(十进制)7 4ls169 同步二进制可逆计数器7 4ls170 4*4寄存器堆7 4ls171 四d触发器(带清除端)7 4ls172 16位寄存器堆7 4ls173 4位d型寄存器(带清除端)7 4ls174 六d触发器7 4ls175 四d触发器4ls176 十进制可预置计数器7 4ls177 2-8-16进制可预置计数器7 4ls178 四位通用移位寄存器7 4ls179 四位通用移位寄存器7 4ls180 九位奇偶产生/校验器7 4ls181 算术逻辑单元/功能发生器7 4ls182 先行进位发生器7 4ls183 双保留进位全加器7 4ls184 bcd-二进制转换器7 4ls185 二进制-bcd转换器7 4ls190 同步可逆计数器(bcd,二进制)7 4ls191 同步可逆计数器(bcd,二进制)7 4ls192 同步可逆计数器(bcd,二进制)7 4ls193 同步可逆计数器(bcd,二进制) 4ls194 四位双向通用移位寄存器7 4ls195 四位通用移位寄存器7 4ls196 可预置计数器/锁存器7 4ls197 可预置计数器/锁存器(二进制)7 4ls198 八位双向移位寄存器7 4ls199 八位移位寄存器7 4ls210 2-5-10进制计数器7 4ls213 2-n-10可变进制计数器7 4ls221 双单稳触发器7 4ls230 八3态总线驱动器7 4ls231 八3态总线反向驱动器7 4ls240 八缓冲器/线驱动器/线接收器(反码三态输出)7 4ls241 八缓冲器/线驱动器/线接收器(原码三态输出)4ls242 八缓冲器/线驱动器/线接收器7 4ls243 4同相三态总线收发器7 4ls244 八缓冲器/线驱动器/线接收器7 4ls245 八双向总线收发器7 4ls246 4线-七段译码/驱动器(30v)7 4ls247 4线-七段译码/驱动器(15v)7 4ls248 4线-七段译码/驱动器7 4ls249 4线-七段译码/驱动器7 4ls251 8选1数据选择器(三态输出)7 4ls253 双四选1数据选择器(三态输出)7 4ls256 双四位可寻址锁存器7 4ls257 四2选1数据选择器(三态输出)7 4ls258 四2选1数据选择器(反码三态输出)7 4ls259 8为可寻址锁存器4ls260 双5输入或非门7 4ls261 4*2并行二进制乘法器7 4ls265 四互补输出元件7 4ls266 2输入四异或非门(oc)7 4ls270 2048位rom (512位四字节,oc)7 4ls271 2048位rom (256位八字节,oc)7 4ls273 八d触发器7 4ls274 4*4并行二进制乘法器7 4ls275 七位片式华莱士树乘法器7 4ls276 四jk触发器7 4ls278 四位可级联优先寄存器7 4ls279 四s-r锁存器7 4ls280 9位奇数/偶数奇偶发生器/较验器7 4ls2814ls283 4位二进制全加器7 4ls290 十进制计数器7 4ls291 32位可编程模7 4ls293 4位二进制计数器7 4ls294 16位可编程模7 4ls295 四位双向通用移位寄存器7 4ls298 四-2输入多路转换器(带选通)7 4ls299 八位通用移位寄存器(三态输出)7 4ls348 8-3线优先编码器(三态输出)7 4ls352 双四选1数据选择器/多路转换器7 4ls353 双4-1线数据选择器(三态输出)7 4ls354 8输入端多路转换器/数据选择器/寄存器,三态补码输出7 4ls355 8输入端多路转换器/数据选择器/寄存器,三态补码输出4ls356 8输入端多路转换器/数据选择器/寄存器,三态补码输出7 4ls357 8输入端多路转换器/数据选择器/寄存器,三态补码输出7 4ls365 6总线驱动器7 4ls366 六反向三态缓冲器/线驱动器7 4ls367 六同向三态缓冲器/线驱动器7 4ls368 六反向三态缓冲器/线驱动器7 4ls373 八d锁存器7 4ls374 八d触发器(三态同相)7 4ls375 4位双稳态锁存器7 4ls377 带使能的八d触发器7 4ls378 六d触发器7 4ls379 四d触发器7 4ls381 算术逻辑单元/函数发生器7 4ls382 算术逻辑单元/函数发生器7 4ls384 8位*1位补码乘法器7 4ls385 四串行加法器/乘法器7 4ls386 2输入四异或门7 4ls390 双十进制计数器7 4ls391 双四位二进制计数器7 4ls395 4位通用移位寄存器7 4ls396 八位存储寄存器74ls398 四2输入端多路开关(双路输出)74ls399 四-2输入多路转换器(带选通)74ls422 单稳态触发器74ls423 双单稳态触发器74ls440 四3方向总线收发器,集电极开路74ls441 四3方向总线收发器,集电极开路74ls442 四3方向总线收发器,三态输出74ls443 四3方向总线收发器,三态输出74ls444 四3方向总线收发器,三态输出74ls445 bcd-十进制译码器/驱动器,三态输出74ls446 有方向控制的双总线收发器74ls448 四3方向总线收发器,三态输出74ls449 有方向控制的双总线收发器74ls465 八三态线缓冲器74ls466 八三态线反向缓冲器74ls467 八三态线缓冲器74ls468 八三态线反向缓冲器74ls490 双十进制计数器74ls540 八位三态总线缓冲器(反向) 74ls541 八位三态总线缓冲器74ls589 有输入锁存的并入串出移位寄存器74ls590 带输出寄存器的8位二进制计数器74ls591 带输出寄存器的8位二进制计数器74ls592 带输出寄存器的8位二进制计数器74ls593 带输出寄存器的8位二进制计数器74ls594 带输出锁存的8位串入并出移位寄存器74ls595 8位输出锁存移位寄存器74ls596 带输出锁存的8位串入并出移位寄存器74ls597 8位输出锁存移位寄存器74ls598 带输入锁存的并入串出移位寄存器74ls599 带输出锁存的8位串入并出移位寄存器74ls604 双8位锁存器74ls605 双8位锁存器74ls606 双8位锁存器74ls607 双8位锁存器74ls620 8位三态总线发送接收器(反相)74ls621 8位总线收发器74ls622 8位总线收发器74ls623 8位总线收发器74ls640 反相总线收发器(三态输出)74ls641 同相8总线收发器,集电极开路74ls642 同相8总线收发器,集电极开路74ls643 8位三态总线发送接收器74ls644 真值反相8总线收发器,集电极开路74ls645 三态同相8总线收发器74ls646 八位总线收发器,寄存器74ls647 八位总线收发器,寄存器74ls648 八位总线收发器,寄存器74ls649 八位总线收发器,寄存器74ls651 三态反相8总线收发器74ls652 三态反相8总线收发器74ls653 反相8总线收发器,集电极开路74ls654 同相8总线收发器,集电极开路74ls668 4位同步加/减十进制计数器74ls669 带先行进位的4位同步二进制可逆计数器74ls670 4*4寄存器堆(三态)74ls671 带输出寄存的四位并入并出移位寄存器74ls672 带输出寄存的四位并入并出移位寄存器74ls673 16位并行输出存储器,16位串入串出移位寄存器74ls674 16位并行输入串行输出移位寄存器74ls681 4位并行二进制累加器74ls682 8位数值比较器(图腾柱输出)74ls683 8位数值比较器(集电极开路)74ls684 8位数值比较器(图腾柱输出)74ls685 8位数值比较器(集电极开路)74ls686 8位数值比较器(图腾柱输出)74ls687 8位数值比较器(集电极开路)74ls688 8位数字比较器(oc输出)74ls689 8位数字比较器74ls690 同步十进制计数器/寄存器(带数选,三态输出,直接清除)74ls691 计数器/寄存器(带多转换,三态输出) 74ls692 同步十进制计数器(带预置输入,同步清除)74ls693 计数器/寄存器(带多转换,三态输出) 74ls696 同步加/减十进制计数器/寄存器(带数选,三态输出,直接清除)74ls697 计数器/寄存器(带多转换,三态输出) 74ls698 计数器/寄存器(带多转换,三态输出) 74ls699 计数器/寄存器(带多转换,三态输出) 74ls716 可编程模n十进制计数器74ls718 可编程模n十进制计数器LM12瓦运算放大器LM124 LM224 LM324 LM2902 低电压双路运算放大器LM324 低电压双路运算放大器LM129 LM329 精密电压基准芯片LM135 LM235 LM335 精密温度传感器芯片LM1458 LM1558 双运算放大器LM158 LM258 LM358 LM2904 低压双运算放大器LM18293 四通道推拉驱动器LM1868 调幅/调频收音机芯片LM1951 1安培固态开关LM2574 降阶式电压调节器LM1575 LM2575 1A 降阶式电压调节器LM2576 3A 3A 降阶式电压调节器LM1577 LM2577 降阶式电压调节器LM2587 5A 返馈开关式电压调节器LM1893 LM2893 载体电流收发器LM193 LM293 LM393 LM2903 双路低压低漂移比较器LM2907 LM2917 频率电压转换器LM101A LM201A LM301A 运算放大器芯片LM3045 LM3046 LM3086 晶体管阵列LM111 LM211 LM311 电压比较器LM117 LM317 三端可调式稳压器LM118 LM218 LM318 运算放大器LM133 LM333安培可调负电压调节器LM137 LM337 可调式三端负压稳压器LM34 精密华氏温度传感器LM342 三端正压稳压器LM148 LM248 LM348 / LM149 LM349 双LM741运算放大器LM35 精密摄氏温度传感器LM158 LM258 LM358 LM2904 低压双运算放大器LM150 LM350 3安培可调式电压调节器LM380 瓦音频放大器LM386 低压音频功率放大器LM3886 高性能68瓦音频功率放大器/带静音LM555 LM555C 时基发生器电路LM556 LM556C 双时基发生器电路LM565 相位跟随器LM567 音频译码器LM621 无刷电机换向器LM628 LM629精密位移控制器LM675功率运算放大器LM723 电压调节器LM741 运算放大器LM7805 LM78xx 系列稳压器LM7812 LM78xx 系列稳压器LM7815 LM78xx 系列稳压器LM78L00 三端正压调节器LM78L05 三端正压调节器LM78L09三端正压调节器LM78L12 三端正压调节器LM78L15 三端正压调节器LM78L62 三端正压调节器LM78L82 三端正压调节器LM340 LM78Mxx 三端正压稳压器LM7905 三端负压调节器LM7912 三端负压调节器LM7915 三端负压调节器LM79Mxx三端负压调节器LF147 LF347 宽带J型场效应输入运算放大器LF351 宽带J型场效应输入运算放大器LF353 宽带J型场效应输入运算放大器LF444 双低压J型场效应输入运算放大器(1) 74LS00双输入四与非门,管脚图如附图1-27所示。

引脚功能与内部结构图

在生产制造过程中,引脚的设计 和制造工艺必须严格控制,以确 保其具有良好的导电性能、机械

强度和耐腐蚀性。

引脚与电路板或其他连接器的接 触性能也是影响产品性能的重要 因素,因此需要采取有效的措施

来确保良好的接触。

如何保证引脚的质量和可靠性

01 在生产过程中,应采用高精度的制造设备和工艺, 确保引脚的尺寸和形状精度符合要求。

03

内部结构对引脚的热设计有要 求,需要考虑到元件在工作时 的发热情况,合理设计引脚的 散热方式。

如何根据内部结构选择合适的引脚

01

根据电路板上的线路布局和焊接方式选择合适的引 脚,确保元件能够顺利安装和稳定工作。

02

根据元件的型号和参数选择相应的引脚,确保引脚 上印有的信息准确无误。

03

根据元件在工作时的发热情况选择合适的引脚材质 和尺寸,确保元件能够得到良好的散热效果。

模块化设计

通过使用不同规格和类型 的引脚,可以实现模块化 设计,方便组装和维修。

引脚设计

间距与规格

引脚的间距和规格需要根据具体的电路板和元件规格进行设计, 以满足电气性能和机械强度的要求。

材料选择

引脚的材料选择对其电气性能、机械强度和可靠性有着重要影响, 常用的材料有铜、不锈钢等。

长度与形状

引脚的长度和形状需要根据具体的应用场景进行设计,以满足信号 传输和连接稳定性的要求。

自动化生产中,引脚的加工、检测、组装等环节都可以通过自动化设备来完成,大 大提高了生产效率和产品质量。

谢谢观看

02

内部结构图解析

集成电路内部结构

集成电路是将多个电子元件集成在一块衬底上,实现一定的电路或系统功能的微型电子部件。其内部 结构包括输入输出引脚、逻辑门、触发器、存储器等电路元件,以及连接这些元件的导线和互连线。

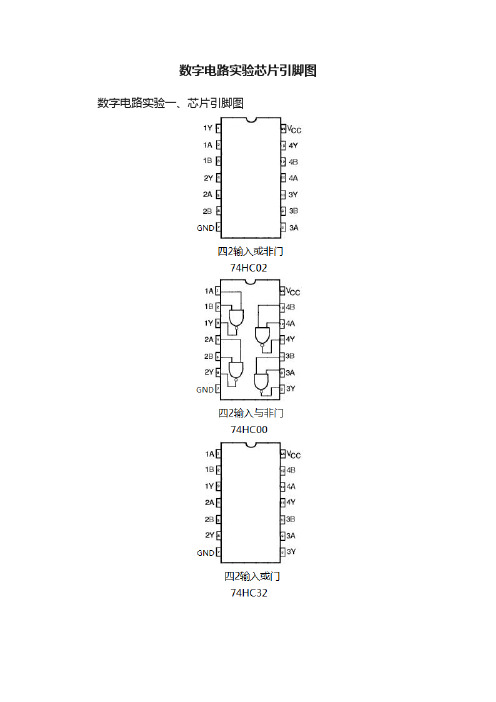

数字电路实验芯片引脚图

数字电路实验芯片引脚图数字电路实验一、芯片引脚图真值表:二、组合逻辑电路实验设计题1.举重比赛有3个裁判,一个主裁判A和两个辅裁判B和C,杠铃完全举上的裁决由每个裁判按下自己的按键来决定。

当3个裁判判为成功或两个裁判(其中一个为主裁判)判为成功则成功绿色指示灯亮,否则红色指示灯亮。

试用74LS151设计此逻辑电路。

2.设输入数据为4位二进制数,当该数据能被3整除时绿色指示灯亮,否则红色指示灯亮。

试用74LS151设计此逻辑电路。

3.设输入数据为4位二进制数,当该数据能被5整除时绿色指示灯亮,否则红色指示灯亮。

试用74LS151设计此逻辑电路。

4.试设计一个四人表决器,当四个人中有3个人或4个人赞成时绿灯亮表示建议被通过,否则红灯亮表示建议被否决。

试用74LS151设计此逻辑电路。

5.设输入数据为4位二进制数,设计由此二进制数决定的偶校验逻辑电路,即当此二进制数中有偶数个1时绿色指示灯亮,否则红色指示灯亮。

试用74LS151设计此逻辑电路。

6.某楼道内住着A、B、C、D 四户人家,楼道顶上有一盏路灯。

请设计一个控制电路,要求A、B、C、D 都能在自己的家中独立地控制这盏路灯。

试用74LS151设计此逻辑电路。

7.用74LS151实现一个函数发生器,其功能是:当S1S0=00时,Y=AB;当S1S0=01时,Y=A+B;当S1S0=10时,Y=A B;当S1S0=11时,Y=。

试用74LS151设计此逻辑电路。

8.试用两片74LS151实现16选1数据选择器。

三、时序逻辑电路实验设计题1.用十进制计数-译码器CC4017设计一个8盏灯的流水灯电路。

2.用74LS161设计一个12进制的加1计数器。

其代码转换图为:0000→0001→0010→…→1011循环。

每循环一次产生一个进位脉冲。

3.用74LS161设计一个12进制的加1计数器。

其代码转换图为:0100→0101→0110→…→1111循环。

及其他系列芯片引脚图大全

一:分类74ls00 2输入四与非门74ls01 2输入四与非门 (oc)74ls02 2输入四或非门74ls03 2输入四与非门 (oc)74ls04 六倒相器74ls05 六倒相器(oc)74ls06 六高压输出反相缓冲器/驱动器(oc,30v) 74ls07 六高压输出缓冲器/驱动器(oc,30v)74ls08 2输入四与门74ls09 2输入四与门(oc)74ls10 3输入三与非门74ls11 3输入三与门74ls12 3输入三与非门 (oc)74ls13 4输入双与非门 (斯密特触发)74ls14 六倒相器(斯密特触发)74ls15 3输入三与门 (oc)74ls16 六高压输出反相缓冲器/驱动器(oc,15v) 74ls17 六高压输出缓冲器/驱动器(oc,15v)74ls18 4输入双与非门 (斯密特触发)74ls19 六倒相器(斯密特触发)74ls20 4输入双与非门74ls21 4输入双与门74ls22 4输入双与非门(oc)74ls23 双可扩展的输入或非门74ls24 2输入四与非门(斯密特触发)74ls25 4输入双或非门(有选通)74ls26 2输入四高电平接口与非缓冲器(oc,15v)74ls27 3输入三或非门74ls28 2输入四或非缓冲器74ls30 8输入与非门74ls31 延迟电路74ls32 2输入四或门74ls33 2输入四或非缓冲器(集电极开路输出)74ls34 六缓冲器74ls35 六缓冲器(oc)74ls36 2输入四或非门(有选通)74ls37 2输入四与非缓冲器74ls38 2输入四或非缓冲器(集电极开路输出74ls39 2输入四或非缓冲器(集电极开路输出)7 4ls40 4输入双与非缓冲器7 4ls41 bcd-十进制计数器4ls42 4线-10线译码器(bcd输入)7 4ls43 4线-10线译码器(余3码输入)7 4ls44 4线-10线译码器(余3葛莱码输入)7 4ls45 bcd-十进制译码器/驱动器7 4ls46 bcd-七段译码器/驱动器7 4ls47 bcd-七段译码器/驱动器7 4ls48 bcd-七段译码器/驱动器7 4ls49 bcd-七段译码器/驱动器(oc)7 4ls50 双二路2-2输入与或非门(一门可扩展)7 4ls51 双二路2-2输入与或非门7 4ls51 二路3-3输入,二路2-2输入与或非门7 4ls52 四路2-3-2-2输入与或门(可扩展)7 4ls53 四路2-2-2-2输入与或非门(可扩展)7 4ls53 四路2-2-3-2输入与或非门(可扩展) 4ls54 四路2-2-2-2输入与或非门7 4ls54 四路2-3-3-2输入与或非门7 4ls54 四路2-2-3-2输入与或非门7 4ls55 二路4-4输入与或非门(可扩展)7 4ls60 双四输入与扩展7 4ls61 三3输入与扩展7 4ls62 四路2-3-3-2输入与或扩展器7 4ls63 六电流读出接口门7 4ls64 四路4-2-3-2输入与或非门7 4ls65 四路4-2-3-2输入与或非门(oc)7 4ls70 与门输入上升沿jk触发器7 4ls71 与输入r-s主从触发器7 4ls72 与门输入主从jk触发器7 4ls73 双j-k触发器(带清除端)4ls74 正沿触发双d型触发器(带预置端和清除端)7 4ls75 4位双稳锁存器7 4ls76 双j-k触发器(带预置端和清除端)7 4ls77 4位双稳态锁存器7 4ls78 双j-k触发器(带预置端,公共清除端和公共时钟端) 4ls80 门控全加器7 4ls81 16位随机存取存储器7 4ls82 2位二进制全加器(快速进位)7 4ls83 4位二进制全加器(快速进位)7 4ls84 16位随机存取存储器7 4ls85 4位数字比较器7 4ls86 2输入四异或门7 4ls87 四位二进制原码/反码/oi单元7 4ls89 64位读/写存储器7 4ls90 十进制计数器7 4ls91 八位移位寄存器7 4ls92 12分频计数器(2分频和6分频)7 4ls93 4位二进制计数器7 4ls94 4位移位寄存器(异步)7 4ls95 4位移位寄存器(并行io)7 4ls96 5位移位寄存器7 4ls97 六位同步二进制比率乘法器7 4ls100 八位双稳锁存器7 4ls103 负沿触发双j-k主从触发器(带清除端)7 4ls106 负沿触发双j-k主从触发器(带预置,清除,时钟)7 4ls107 双j-k主从触发器(带清除端)4ls108 双j-k主从触发器(带预置,清除,时钟)7 4ls109 双j-k触发器(带置位,清除,正触发)7 4ls110 与门输入j-k主从触发器(带锁定)7 4ls111 双j-k主从触发器(带数据锁定)7 4ls112 负沿触发双j-k触发器(带预置端和清除端)7 4ls113 负沿触发双j-k触发器(带预置端)7 4ls114 双j-k触发器(带预置端,共清除端和时钟端)7 4ls116 双四位锁存器7 4ls120 双脉冲同步器/驱动器7 4ls121 单稳态触发器(施密特触发)7 4ls122 可再触发单稳态多谐振荡器(带清除端)7 4ls123 可再触发双单稳多谐振荡器7 4ls125 四总线缓冲门(三态输出) 4ls126 四总线缓冲门(三态输出)7 4ls128 2输入四或非线驱动器7 4ls131 3-8译码器7 4ls132 2输入四与非门(斯密特触发)7 4ls133 13输入端与非门7 4ls134 12输入端与门(三态输出)7 4ls135 四异或/异或非门7 4ls136 2输入四异或门(oc)7 4ls137 八选1锁存译码器/多路转换器7 4ls138 3-8线译码器/多路转换器7 4ls139 双2-4线译码器/多路转换器7 4ls140 双4输入与非线驱动器7 4ls141 bcd-十进制译码器/驱动器7 4ls142 计数器/锁存器/译码器/驱动器4ls145 4-10译码器/驱动器7 4ls147 10线-4线优先编码器7 4ls148 8线-3线八进制优先编码器7 4ls150 16选1数据选择器(反补输出)7 4ls151 8选1数据选择器(互补输出)7 4ls152 8选1数据选择器多路开关7 4ls153 双4选1数据选择器/多路选择器7 4ls154 4线-16线译码器7 4ls155 双2-4译码器/分配器(图腾柱输出)7 4ls156 双2-4译码器/分配器(集电极开路输出)7 4ls157 四2选1数据选择器/多路选择器7 4ls158 四2选1数据选择器(反相输出)7 4ls160 可预置bcd计数器(异步清除)7 4ls161 可预置四位二进制计数器(并清除异步) 4ls162 可预置bcd计数器(异步清除)7 4ls163 可预置四位二进制计数器(并清除异步)7 4ls164 8位并行输出串行移位寄存器7 4ls165 并行输入8位移位寄存器(补码输出)7 4ls166 8位移位寄存器7 4ls167 同步十进制比率乘法器7 4ls168 4位加/减同步计数器(十进制)7 4ls169 同步二进制可逆计数器7 4ls170 4*4寄存器堆7 4ls171 四d触发器(带清除端)7 4ls172 16位寄存器堆7 4ls173 4位d型寄存器(带清除端)7 4ls174 六d触发器7 4ls175 四d触发器4ls176 十进制可预置计数器7 4ls177 2-8-16进制可预置计数器7 4ls178 四位通用移位寄存器7 4ls179 四位通用移位寄存器7 4ls180 九位奇偶产生/校验器7 4ls181 算术逻辑单元/功能发生器7 4ls182 先行进位发生器7 4ls183 双保留进位全加器7 4ls184 bcd-二进制转换器7 4ls185 二进制-bcd转换器7 4ls190 同步可逆计数器(bcd,二进制)7 4ls191 同步可逆计数器(bcd,二进制)7 4ls192 同步可逆计数器(bcd,二进制)7 4ls193 同步可逆计数器(bcd,二进制) 4ls194 四位双向通用移位寄存器7 4ls195 四位通用移位寄存器7 4ls196 可预置计数器/锁存器7 4ls197 可预置计数器/锁存器(二进制)7 4ls198 八位双向移位寄存器7 4ls199 八位移位寄存器7 4ls210 2-5-10进制计数器7 4ls213 2-n-10可变进制计数器7 4ls221 双单稳触发器7 4ls230 八3态总线驱动器7 4ls231 八3态总线反向驱动器7 4ls240 八缓冲器/线驱动器/线接收器(反码三态输出)7 4ls241 八缓冲器/线驱动器/线接收器(原码三态输出)4ls242 八缓冲器/线驱动器/线接收器7 4ls243 4同相三态总线收发器7 4ls244 八缓冲器/线驱动器/线接收器7 4ls245 八双向总线收发器7 4ls246 4线-七段译码/驱动器(30v)7 4ls247 4线-七段译码/驱动器(15v)7 4ls248 4线-七段译码/驱动器7 4ls249 4线-七段译码/驱动器7 4ls251 8选1数据选择器(三态输出)7 4ls253 双四选1数据选择器(三态输出)7 4ls256 双四位可寻址锁存器7 4ls257 四2选1数据选择器(三态输出)7 4ls258 四2选1数据选择器(反码三态输出)7 4ls259 8为可寻址锁存器4ls260 双5输入或非门7 4ls261 4*2并行二进制乘法器7 4ls265 四互补输出元件7 4ls266 2输入四异或非门(oc)7 4ls270 2048位rom (512位四字节,oc)7 4ls271 2048位rom (256位八字节,oc)7 4ls273 八d触发器7 4ls274 4*4并行二进制乘法器7 4ls275 七位片式华莱士树乘法器7 4ls276 四jk触发器7 4ls278 四位可级联优先寄存器7 4ls279 四s-r锁存器7 4ls280 9位奇数/偶数奇偶发生器/较验器7 4ls2814ls283 4位二进制全加器7 4ls290 十进制计数器7 4ls291 32位可编程模7 4ls293 4位二进制计数器7 4ls294 16位可编程模7 4ls295 四位双向通用移位寄存器7 4ls298 四-2输入多路转换器(带选通)7 4ls299 八位通用移位寄存器(三态输出)7 4ls348 8-3线优先编码器(三态输出)7 4ls352 双四选1数据选择器/多路转换器7 4ls353 双4-1线数据选择器(三态输出)7 4ls354 8输入端多路转换器/数据选择器/寄存器,三态补码输出7 4ls355 8输入端多路转换器/数据选择器/寄存器,三态补码输出4ls356 8输入端多路转换器/数据选择器/寄存器,三态补码输出7 4ls357 8输入端多路转换器/数据选择器/寄存器,三态补码输出7 4ls365 6总线驱动器7 4ls366 六反向三态缓冲器/线驱动器7 4ls367 六同向三态缓冲器/线驱动器7 4ls368 六反向三态缓冲器/线驱动器7 4ls373 八d锁存器7 4ls374 八d触发器(三态同相)7 4ls375 4位双稳态锁存器7 4ls377 带使能的八d触发器7 4ls378 六d触发器7 4ls379 四d触发器7 4ls381 算术逻辑单元/函数发生器7 4ls382 算术逻辑单元/函数发生器7 4ls384 8位*1位补码乘法器7 4ls385 四串行加法器/乘法器7 4ls386 2输入四异或门7 4ls390 双十进制计数器7 4ls391 双四位二进制计数器7 4ls395 4位通用移位寄存器7 4ls396 八位存储寄存器74ls398 四2输入端多路开关(双路输出)74ls399 四-2输入多路转换器(带选通)74ls422 单稳态触发器74ls423 双单稳态触发器74ls440 四3方向总线收发器,集电极开路74ls441 四3方向总线收发器,集电极开路74ls442 四3方向总线收发器,三态输出74ls443 四3方向总线收发器,三态输出74ls444 四3方向总线收发器,三态输出74ls445 bcd-十进制译码器/驱动器,三态输出74ls446 有方向控制的双总线收发器74ls448 四3方向总线收发器,三态输出74ls449 有方向控制的双总线收发器74ls465 八三态线缓冲器74ls466 八三态线反向缓冲器74ls467 八三态线缓冲器74ls468 八三态线反向缓冲器74ls490 双十进制计数器74ls540 八位三态总线缓冲器(反向)74ls541 八位三态总线缓冲器74ls589 有输入锁存的并入串出移位寄存器74ls590 带输出寄存器的8位二进制计数器74ls591 带输出寄存器的8位二进制计数器74ls592 带输出寄存器的8位二进制计数器74ls593 带输出寄存器的8位二进制计数器74ls594 带输出锁存的8位串入并出移位寄存器74ls595 8位输出锁存移位寄存器74ls596 带输出锁存的8位串入并出移位寄存器74ls597 8位输出锁存移位寄存器74ls598 带输入锁存的并入串出移位寄存器74ls599 带输出锁存的8位串入并出移位寄存器74ls604 双8位锁存器74ls605 双8位锁存器74ls606 双8位锁存器74ls607 双8位锁存器74ls620 8位三态总线发送接收器(反相)74ls621 8位总线收发器74ls622 8位总线收发器74ls623 8位总线收发器74ls640 反相总线收发器(三态输出)74ls641 同相8总线收发器,集电极开路74ls642 同相8总线收发器,集电极开路74ls643 8位三态总线发送接收器74ls644 真值反相8总线收发器,集电极开路74ls645 三态同相8总线收发器74ls646 八位总线收发器,寄存器74ls647 八位总线收发器,寄存器74ls648 八位总线收发器,寄存器74ls649 八位总线收发器,寄存器74ls651 三态反相8总线收发器74ls652 三态反相8总线收发器74ls653 反相8总线收发器,集电极开路74ls654 同相8总线收发器,集电极开路74ls668 4位同步加/减十进制计数器74ls669 带先行进位的4位同步二进制可逆计数器74ls670 4*4寄存器堆(三态)74ls671 带输出寄存的四位并入并出移位寄存器74ls672 带输出寄存的四位并入并出移位寄存器74ls673 16位并行输出存储器,16位串入串出移位寄存器74ls674 16位并行输入串行输出移位寄存器74ls681 4位并行二进制累加器74ls682 8位数值比较器(图腾柱输出)74ls683 8位数值比较器(集电极开路)74ls684 8位数值比较器(图腾柱输出)74ls685 8位数值比较器(集电极开路)74ls686 8位数值比较器(图腾柱输出)74ls687 8位数值比较器(集电极开路)74ls688 8位数字比较器(oc输出)74ls689 8位数字比较器74ls690 同步十进制计数器/寄存器(带数选,三态输出,直接清除)74ls691 计数器/寄存器(带多转换,三态输出)74ls692 同步十进制计数器(带预置输入,同步清除)74ls693 计数器/寄存器(带多转换,三态输出)74ls696 同步加/减十进制计数器/寄存器(带数选,三态输出,直接清除)74ls697 计数器/寄存器(带多转换,三态输出)74ls698 计数器/寄存器(带多转换,三态输出)74ls699 计数器/寄存器(带多转换,三态输出)74ls716 可编程模n十进制计数器74ls718 可编程模n十进制计数器LM12瓦运算放大器LM124 LM224 LM324 LM2902 低电压双路运算放大器LM324 低电压双路运算放大器LM129 LM329 精密电压基准芯片LM135 LM235 LM335 精密温度传感器芯片LM1458 LM1558 双运算放大器LM158 LM258 LM358 LM2904 低压双运算放大器LM18293 四通道推拉驱动器LM1868 调幅/调频收音机芯片LM1951 1安培固态开关LM2574 降阶式电压调节器LM1575 LM2575 1A 降阶式电压调节器LM2576 3A 3A 降阶式电压调节器LM1577 LM2577 降阶式电压调节器LM2587 5A 返馈开关式电压调节器LM1893 LM2893 载体电流收发器LM193 LM293 LM393 LM2903 双路低压低漂移比较器LM2907 LM2917 频率电压转换器LM101A LM201A LM301A 运算放大器芯片LM3045 LM3046 LM3086 晶体管阵列LM111 LM211 LM311 电压比较器LM117 LM317 三端可调式稳压器LM118 LM218 LM318 运算放大器LM133 LM333安培可调负电压调节器LM137 LM337 可调式三端负压稳压器LM34 精密华氏温度传感器LM342 三端正压稳压器LM148 LM248 LM348 / LM149 LM349 双LM741运算放大器LM35 精密摄氏温度传感器LM158 LM258 LM358 LM2904 低压双运算放大器LM150 LM350 3安培可调式电压调节器LM380 瓦音频放大器LM386 低压音频功率放大器LM3886 高性能68瓦音频功率放大器/带静音LM555 LM555C 时基发生器电路LM556 LM556C 双时基发生器电路LM565 相位跟随器LM567 音频译码器LM621 无刷电机换向器LM628 LM629精密位移控制器LM675功率运算放大器LM723 电压调节器LM741 运算放大器LM7805 LM78xx 系列稳压器LM7812 LM78xx 系列稳压器LM7815 LM78xx 系列稳压器LM78L00 三端正压调节器LM78L05 三端正压调节器LM78L09三端正压调节器LM78L12 三端正压调节器LM78L15 三端正压调节器LM78L62 三端正压调节器LM78L82 三端正压调节器LM340 LM78Mxx 三端正压稳压器LM7905 三端负压调节器LM7912 三端负压调节器LM7915 三端负压调节器LM79Mxx三端负压调节器LF147 LF347 宽带J型场效应输入运算放大器LF351 宽带J型场效应输入运算放大器LF353 宽带J型场效应输入运算放大器LF444 双低压J型场效应输入运算放大器(1) 74LS00双输入四与非门,管脚图如附图1-27所示。

实验二组合逻辑电路分析

本科学生实验报告

云南师范大学教务处编印

实验序号实验名称组合逻辑电路分析实验时间实验室

1.实验元件(元件型号;引脚结构;逻辑功能;引脚名称)

1.SAC-DS4数字逻辑实验箱1个

2.万用表 1块

3.74LS00N 四二输入与非门 3片

74LS00引脚结构及逻辑功能

2.实验目的

1.掌握组合逻辑电路的分析方法

2. 验证半加器、全加器逻辑功能。

3.实验电路原理图及接线方法描述:

(1)两片74LS00N实现半加器的逻辑功能电路图

(2)三片74LS00N实现全加器的逻辑功能电路图

4.实验中各种信号的选取及控制(电源为哪些电路供电;输入信号的分布位置;输出信号的指示类型;总结完成实验条件)

(1)用两片74LS00(引脚见附录)按图4-1接线。

74LS00芯片14脚接+5V,7脚接地。

(2)用三片74LS00按图4-2接好线。

74LS00芯片14脚接 +5v,7脚接地.。

数电实验——精选推荐

实验一 TTL集成逻辑门的参数测试一、实验目的1、了解TTL与非门各参数的意义。

2、掌握TTL集成门电路的逻辑功能和参数测试方法。

二、实验原理、方法和手段TTL集成与非门是数字电路中广泛使用的一种逻辑门,使用时,必须对它的逻辑功能、主要参数和特性曲线进行测试,以确定其性能好坏。

本实验主要是对TTL集成与非门74LS20进行测试,该芯片外形为DIP双列直插式结构。

原理电路、逻辑符号和管脚排列如图1-1(a)、(b)、(c)所示。

图1-1 74LS20芯片原理电路、逻辑符号和封装引脚图1. 与非门的逻辑功能与非门的逻辑功能是:当输入端有一个或一个以上的低电平时,输出端为高电平;只有输入端全部为高电平时,输出端才是低电平。

(即有“0”得“1”,全“1”得“0”。

)对与非门进行测试时,门的输入端接逻辑开关,开关向上为逻辑“1”,向下为逻辑“0”。

门的输出端接电平指示器,发光管亮为逻辑“1”,不亮为逻辑“0”。

与非门的逻辑表达式为:Q ABCD2. TTL与非门的主要参数(1)低电平输出电源电流I CCL与高电平输出电源电流I CCH与非门在不同的工作状态,电源提供的电流是不同的。

I CCL 是指输出端空载,所有输入端全部悬空,(与非门处于导通状态),电源提供器件的电流。

I CCH 是指输出端空载,每个门各有一个以上的输入端接地,其余输入端悬空,(与非门处于截止状态),电源提供器件的电流。

测试电路如图1-2(a)、(b)所示。

通常I CCL >I CCH ,它们的大小标志着与非门在静态情况下的功耗大小。

导通功耗:P CCL =I CCL ×U CC 截止功耗:P CCH =I CCH ×U CC由于I CCL 较大,一般手册中给出的功耗是指P CCL 。

注意:TTL 电路对电源电压要求较严,电源电压V CC 允许在+5±10%的电压范围内工作,超过5.5V 将损坏器件;低于4.5V 器件的逻辑功能将不正常。

74ls系列主要芯片引脚及参数.doc

<74LS00引脚图>74l s00 是常用的2输入四与非门集成电路,他的作用很简单顾名思义就是实现一个与非门。

Vcc 4B 4A 4Y 3B 3A 3Y┌┴—┴—┴—┴—┴—┴—┴┐__ │14 13 12 11 10 9 8│Y = AB )│ 2输入四正与非门 74LS00│ 1 2 3 4 5 6 7│└┬—┬—┬—┬—┬—┬—┬┘1A 1B 1Y 2A 2B 2Y GND74LS00真值表:A=1 B=1 Y=0A=0 B=1 Y=1A=1 B=0 Y=1A=0 B=0 Y=174HC138基本功能74LS138 为3 线-8 线译码器,共有54/74S138和54/74LS138 两种线路结构型式,其74LS138工作原理如下:当一个选通端(G1)为高电平,另两个选通端(/(G2A)和/(G2B))为低电平时,可将地址端(A、B、C)的二进制编码在一个对应的输出端以低电平译出。

74LS138的作用:利用G1、/(G2A)和/(G2B)可级联扩展成24 线译码器;若外接一个反相器还可级联扩展成32 线译码器。

若将选通端中的一个作为数据输入端时,74LS138还可作数据分配器用与非门组成的3线-8线译码器74LS138图74ls138译码器内部电路3线-8线译码器74LS138的功能表备注:这里的输入端的三个A0~1有的原理图中也用A B C表示(如74H138.pdf中所示,试用于普中科技的HC-6800 V2.2单片机开发板)。

<74ls138功能表>74LS138逻辑图无论从逻辑图还是功能表我们都可以看到74LS138的八个输出管脚,任何时刻要么全为高电平1—芯片处于不工作状态,要么只有一个为低电平0,其余7个输出管脚全为高电平1。

如果出现两个输出管脚在同一个时间为0的情况,说明该芯片已经损坏。

当附加控制门的输出为高电平(S=1)时,可由逻辑图写出74ls138逻辑图由上式可以看出,在同一个时间又是这三个变量的全部最小项的译码输出,所以也把这种译码器叫做最小项译码器。

74ls系列主要芯片引脚及参数.doc

74ls系列主要芯⽚引脚及参数.doc<74LS00引脚图>74l s00 是常⽤的2输⼊四与⾮门集成电路,他的作⽤很简单顾名思义就是实现⼀个与⾮门。

Vcc 4B 4A 4Y 3B 3A 3Y┌┴—┴—┴—┴—┴—┴—┴┐__ │14 13 12 11 10 9 8│Y = AB )│ 2输⼊四正与⾮门 74LS00│ 1 2 3 4 5 6 7│└┬—┬—┬—┬—┬—┬—┬┘1A 1B 1Y 2A 2B 2Y GND74LS00真值表:A=1 B=1 Y=0A=0 B=1 Y=1A=1 B=0 Y=1A=0 B=0 Y=174HC138基本功能74LS138 为3 线-8 线译码器,共有54/74S138和54/74LS138 两种线路结构型式,其74LS138⼯作原理如下:当⼀个选通端(G1)为⾼电平,另两个选通端(/(G2A)和/(G2B))为低电平时,可将地址端(A、B、C)的⼆进制编码在⼀个对应的输出端以低电平译出。

74LS138的作⽤:利⽤G1、/(G2A)和/(G2B)可级联扩展成24 线译码器;若外接⼀个反相器还可级联扩展成32 线译码器。

若将选通端中的⼀个作为数据输⼊端时,74LS138还可作数据分配器⽤与⾮门组成的3线-8线译码器74LS138图74ls138译码器内部电路3线-8线译码器74LS138的功能表备注:这⾥的输⼊端的三个A0~1有的原理图中也⽤A B C表⽰(如74H138.pdf中所⽰,试⽤于普中科技的HC-6800 V2.2单⽚机开发板)。

<74ls138功能表>74LS138逻辑图⽆论从逻辑图还是功能表我们都可以看到74LS138的⼋个输出管脚,任何时刻要么全为⾼电平1—芯⽚处于不⼯作状态,要么只有⼀个为低电平0,其余7个输出管脚全为⾼电平1。

如果出现两个输出管脚在同⼀个时间为0的情况,说明该芯⽚已经损坏。

当附加控制门的输出为⾼电平(S=1)时,可由逻辑图写出74ls138逻辑图由上式可以看出,在同⼀个时间⼜是这三个变量的全部最⼩项的译码输出,所以也把这种译码器叫做最⼩项译码器。

555定时器电路结构图与管脚排列图_555定时器功能表_555定时器引脚图 - 电子技术

555定时器电路结构图与管脚排列图_555定时器功能表_555定时器引脚图 - 电子技术555定时器是一种将模拟电路和数字电路集成于一体的集成芯片。

用它可以构成单稳态触发器、多谐振荡器和施密特触发器等多种电路。

555定时器在工业控制、定时、检测、报警等方面有广泛应用。

它由下面四部分组成:1、分压器:由三个5KΩ电阻构成2、比较器:由电压比较器C1和C2构成3、R-S触发器4、放电开关管T555定时器电路结构图与管脚排列图如下图所示。

比较器C1的参考电压为,加在同相输入端;比较器C2的参考电压为,加在反相输入端。

在初学阶段必须掌握的几个管脚的功能如下:2脚:低电平触发端,由此输入触发脉冲。

当此输入端的输入电压大于时,C2的输出为高电平“1”;当输入电压小于时,C2的输出为低电平“0”,使基本RS触发器置“1”。

6脚:高电平触发端,由此输入触发脉冲。

当此输入端的输入电压小于时,C1的输出为高电平“1”;当输入电压大于时,C1的输出为低电平“0”,使基本RS触发器置“0”。

7脚:放电端D,当触发器的=1时,放电晶体管T导通,外接电容元件通过T放电。

3脚:输出端Q,输出电流可以达到200 mA,因此可以直接驱动继电器、发光二极管、扬声器、指示灯等。

输出高电压约低于电源电压1~3 V。

其它管脚的功能如下:8脚:电源端VCC,可以在5~18 V范围内使用。

1脚:接地端。

4脚:复位端,由此输入负脉冲(或使其电位低于0.7 V)使基本RS触发器直接复位(置“0”)。

5脚:电压控制端,在此端可以外加一电压以改变比较器的参考电压。

不用时,经0.01 F的电容接地,以防止干扰信号的引入。

由原理电路结构不难得到555定时器电路的功能,其功能表如下表所示。

在分析后面介绍的555定时器的应用电路时,就依据该表分析。

555定时器功能表。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

实验电路结构图及芯片引脚对应表NO.0实验电路结构图HEXPIO2PIO3PIO4PIO5PIO7PIO6D1D2D3D4D5D6D7D8D16D15D14D13D12D11数码1数码2数码3数码4数码5数码6数码7数码8S P E A K E R扬声器译码器译码器译码器译码器译码器译码器译码器译码器FPGA/CPLD PIO15-PIO12PIO11-PIO8PIO7--PIO2HEX 键1键2键3键4键5键6键7键8PIO47-PIO44PIO43-PIO40PIO39-PIO36PIO35-PIO32PIO31-PIO28PIO27-PIO24PIO23-PIO20PIO19-PIO16目标芯片附图2-2 实验电路结构图NO.0附图2-3 实验电路结构图NO.1附图2-4 实验电路结构图NO.2ʵÑéµç·½á¹¹Í¼NO.3ÒëÂëÆ÷ÒëÂëÆ÷ÒëÂëÆ÷ÒëÂëÆ÷ÒëÂëÆ÷ÒëÂëÆ÷ÒëÂëÆ÷ÒëÂëÆ÷D9D16D15D14D13D12D11D10D8D7D6D5D4D3D2D1PIO8PIO9PIO10PIO11PIO12PIO13PIO14PIO15S P E A K E RÑïÉùÆ÷12345678Ä¿±êоƬFPGA/CPLD PIO0PIO1PIO2PIO3PIO4PIO5PIO6PIO7¼ü1¼ü2¼ü3¼ü4¼ü5¼ü6¼ü7¼ü8PIO15-PIO8PIO47-PIO44PIO43-PIO40PIO39-PIO36PIO35-PIO32PIO31-PIO28PIO27-PIO24PIO23-PIO20PIO19-PIO16附图2-5 实验电路结构图NO.3附图2-6 实验电路结构图NO.4GNDPIO45PIO46513PS/2接口VCCJ74接PC 机串行通讯接口接口电路单片机接口电路235RS-232B412MHZA键复位P34P33P32X1X2P31P30P35RST GND12345678910VCCPIO11PIO12PIO13PIO14AT89C2051EU3P37P10P11P12P13P14P15P16P17VCC 11121314151617181920PIO15PIO24PIO25PIO26PIO27PIO28PIO29PIO30PIO317.2K P29->A14)27512(PIN30->VCC,PIN3->A15,PIN29->WE)628128(PIN30->VCC,PIN3->A14,RAM/ROMP29->WE)62256(PIN30->VCC,PIN3->A14,6264(PIN30->VCC,PIN29->WR)PIN30->A17,PIN3->A15,PIN29->A14)29C040(PIN31->WE,PIN1->A18,PIN3->A15,PIN29->A14)27040(PIN31->A18,PIN30->A17,PIN29->A14)27020(PIN30->A17,PIN3->A15,P29->A14)27010(PIN30->VCC,PIN3->A15,PIO40PIO41PIO42PIO43PIO44R78 200R77 200R76 20010548761413321 视频接口VGA J6A18/A19A18/A15/WE PIO49VCC SLA17RAM_ENVCC GND SLRAMPIO26PIO25PIO24PIO32PIO33PIO34PIO35PIO36PIO37PIO38PIO39PIO14PIO47PIO10PIO48PIO9PIO46PIO45PIO11PIO12PIO13PIO8PIO15PIO31PIO30PIO29PIO28PIO273231302928272625242322212019181716151413121110987654321VCC GND2708027040270202701027512272562764628128622566264VCC A17/VCC WR/A14A13A8A9A11OE A10CS1D7D6D5D4D3GND D2D1D0A0A1A2A3A4A5A6A7A12A14(A15)A1610K VCCVR1PIO31PIO29PIO30PIO28PIO27PIO26PIO25PIO24131415164D7D6D5D4D35D26D1D07PIO37+5JP251pFC27JP2(COMP)COMP LM311VCC10K -12+124823TL082/1AIN0AOUT1021035.1KR72765TL082/2841+12-12滤波0滤波1FITCOMMEU2DAC0832118171032WR1FB93211IOUT1IOUT212/CS WR2XFER A GND D GNDVREF8VCC 20VCCJP2(1/2,3/4)D1PIO8D2D3D4D5D6D7D8PIO9PIO10PIO11PIO12PIO15PIO14PIO13实验电路结构图NO.5S P E A K E R扬声器FPGA/CPLD 目标芯片12345678D16D15D14D13D12D11D10D9PIO47-PIO44PIO43-PIO40PIO39-PIO36PIO35-PIO32PIO31-PIO28PIO27-PIO24PIO23-PIO20PIO19-PIO16译码器译码器译码器译码器译码器译码器译码器译码器PIO15-PIO8PIO0PIO1PIO2PIO3PIO4PIO5PIO6PIO7键1键2键3键4键5键6键7键8P I O 8J P 2(5/6)P I O 8(23)(24)1216272610C L O C K 750K H Z A F I T102C 30103C 29P I O 37P I O 35C O M MC O M PA D E O C A D E NJ P 22018161412108642191715131197531021+5V A I N 0A I N 1r e f (-)r e f (+)I N -1I N -06922257171415818192021E U 1A D C 0809P I O 16P I O 17P I O 18P I O 19P I O 20P I O 21P I O 22P I O 23P I O 32P I O 33P I O 35P I O 34m s b 2-12-22-32-42-52-62-7l s b 2-8E O C A D D -A A D D -B A D D -C A L E E N A B L E S T A R T附图2-7 实验电路结构图NO.5附图2-8 实验电路结构图NO.6D16D15D14D13D12D11D9D8PIO47D7PIO46D6PIO45D5PIO44D4PIO43D3PIO42D2PIO41PIO40D1NO.7实验电路结构图S P E A K E R扬声器FPGA/CPLD 目标芯片12345678PIO0PIO2PIO3PIO4PIO5PIO6PIO7单脉冲单脉冲单脉冲键1键2键3键4键5键6键7键8PIO47-PIO40PIO39-PIO36PIO35-PIO32PIO31-PIO28PIO27-PIO24PIO23-PIO20PIO19-PIO16译码器译码器译码器译码器译码器译码器附图2-9 实验电路结构图NO.7附图2-10 实验电路结构图NO.8附图2-11 实验电路结构图NO.9附图2-12 实验电路结构图NO.BD22D21D20D19D18D17VCC87654321SDA (PIO79)SCL (PIO78)24C01GNDVCCPIO77PIO766PS/254321GNDVCCD-(PIO76)D+(PIO77)SLAVEUSB GND键12键11键9键1010K X 4PIO75PIO74PIO72PIO73VCCP I O 71P I O 76P I O 77P I O 70P I O 69P I O 68数码14数码13数码12数码11数码10数码9PIO67PIO66PIO65PIO64PIO63PIO62PIO61PIO60hg f e d c b a 888888附图2-13 实验电路结构图COM万能接插口与结构图信号/与芯片引脚对照表附录二:《EDA技术》部分实验参考源程序一、8位硬件加法器设计程序如下:LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY ADDER8 ISPORT ( CIN : IN STD_LOGIC;A, B : IN STD_LOGIC_VECTOR(7 DOWNTO 0);S : OUT STD_LOGIC_VECTOR(7 DOWNTO 0);COUT : OUT STD_LOGIC );END ADDER8;ARCHITECTURE behav OF ADDER8 ISSIGNAL SINT : STD_LOGIC_VECTOR(8 DOWNTO 0);BEGINSINT <= ('0'& A) + B + CIN ;S <= SINT(7 DOWNTO 0); COUT <= SINT(8);END behav;选择实验电路NO.1验证此加法器的功能。