共源共栅运算放大器的设计

6折叠式共源共栅运算放大器设计实验之欧阳法创编

6折叠式共源共栅运算放大器设计实验之欧阳法创编欧阳法是一种常用的运算放大器设计方法,它在设计中充分利用了共源共栅结构的优点,既能实现放大器的高增益、高输入阻抗和低输出阻抗,又能保证输出波形的线性度。

在设计6折叠式共源共栅运算放大器之前,首先需要明确一些设计参数,例如设计的输入电压范围、输出电压范围、增益要求等。

接下来,我们按照以下步骤进行设计实验。

第一步:确定输出电流偏置在共源共栅运算放大器中,偏置电流决定了放大器的输入阻抗和输出电压范围。

为了实现输出电压范围的最大化,一般选择输出电流的一半作为偏置电流。

假设输出电流为Iout,则偏置电流为Ibias=0.5*Iout。

第二步:确定放大器的增益根据设计要求确定放大器所需的增益。

对于共源共栅结构,其放大倍数可以通过控制输入电流和输出电流之间的比值来实现。

输出电流为Iout,输入电流为Iin,则放大倍数Av=Iout/Iin。

第三步:确定放大器的工作电压根据设计要求确定放大器的工作电压。

将放大器的工作电压设为VDD/2,这样可以最大程度地利用电源电压范围。

第四步:确定电阻值根据欧阳法的设计准则,可选择如下电阻值:R1=R2=RL=1.2*VDD/(Ibias*Av)R3=R4=2*RL第五步:确定电容值选择合适的电容值可以提高放大器的频率响应。

一般选择的电容值为:Cgs=Cgd=2*Iout/(Av*VDD*fL)Cdb=Cgd/5其中,fL为放大器的最低截止频率。

第六步:确定晶体管尺寸根据电阻和电容的选择,可以反推出晶体管的尺寸。

根据晶体管的工作点,选择适当的W/L比值来满足电流需求。

完成以上步骤后,可以利用电路设计软件进行模拟仿真,并根据仿真结果进行优化调整。

最后,可以进行实验验证,并对实验结果进行分析。

以上是关于6折叠式共源共栅运算放大器设计实验的欧阳法创编的详细步骤。

在实际设计中,还需要注意噪声和功耗等因素,并进行合理的折衷考虑。

希望以上内容能对你的实验展开有所帮助。

共源共栅放大器实验报告材料

实验名称:共源共栅放大器设计实验目的:放大器的根本工作原理与相关优缺点3. 共源共栅放大器设计与仿真实验设备与型号:orcd仿真软件实验原理与实验步骤:实验原理:共栅级的输入信号可以是电流,共源级可以可以将电压信号转换为电流信号。

共源共栅级的级联叫做共源共栅结构。

共源共栅级的输出阻抗很高通过计算Rout可得Rout约=〔gm1+gmb2〕r o2r o1也就是说M2将M1的增益提高至原来的〔gm1+gmb2〕r o2倍其还可以扩展为三个或多个以获得更高的输出电阻但这需要额外的电压余度共源共栅结构不仅可以作为放大器而且可以作为恒定电流源高的输出阻抗接近一个理想电流源本次需要仿真的pmos 共源共栅负载的nmos 共源共栅放大器即是如此。

在某种意义上,共源共栅晶体管结构“屏蔽〞输入器件使它不受输出节点电压变化的影响。

这种共源共栅结构屏蔽特性在许多电路中是非常有用的 实验步骤:由于共源共栅放大器的电路图已给出,所以电路设计省略 2.按所给设计图绘制相应电路图所得电路图如下0.653FREQ = 1kVA MPL = 15mVO FF = 03.根据题目要求先对其进展相应仿真 1〕设置静态工作点和器件参数。

如此处静态输出电压Vout=3v Vcc=6v Vb1=5.13v Vb2=4.88v Vb3= 0.904v 等2):设定静态电流。

①设定长L=2u②调试WL主要是调试W,要使静态电流为100uA,L固定以后,就调节W来达到需要的电流。

此处用快速扫描的方法来调试出所需W的大小待所需各个管的w值扫描出后③bias point 仿真检验电流i是否达到要求。

3)根据题目要求进展相应的交流仿真。

以下是相关的扫描实验数据扫描w的值测得MP1管w的值为205ubias point 仿真检验。

去掉输出端的3v电压后原如此上在每个管子的W定好了之后通过bias point仿真静态输出电压为3V静态电流约为100uA。

折叠式共源共栅运算放大器的设计报告

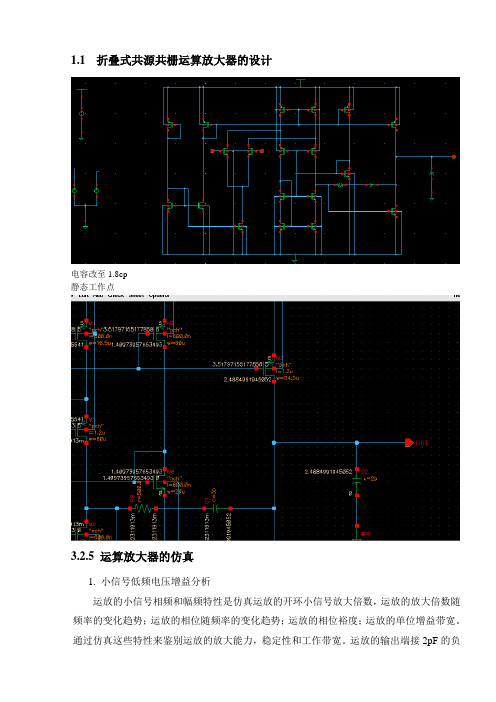

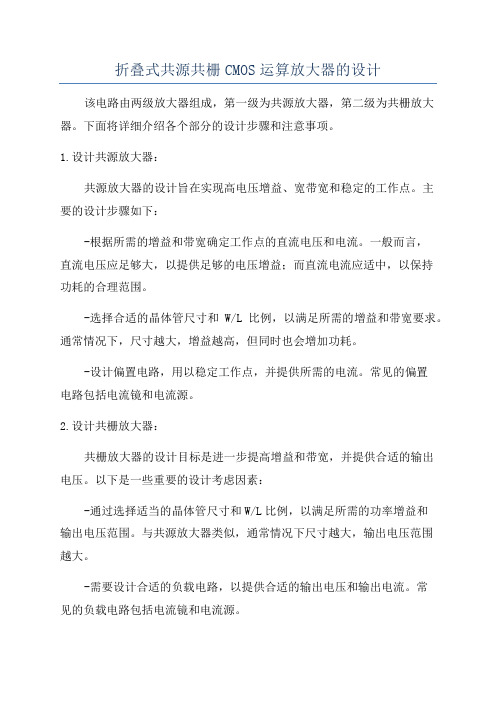

1.1折叠式共源共栅运算放大器的设计电容改至1.8cp静态工作点3.2.5 运算放大器的仿真1. 小信号低频电压增益分析运放的小信号相频和幅频特性是仿真运放的开环小信号放大倍数,运放的放大倍数随频率的变化趋势;运放的相位随频率的变化趋势;运放的相位裕度;运放的单位增益带宽。

通过仿真这些特性来鉴别运放的放大能力,稳定性和工作带宽。

运放的输出端接2pF的负载电容,在电源电压为5V ,共模输入电压为2.5V ,在运放输入端接差分交流信号1V ,两输入端的输入交流信号相位相反的条件下做交流小信号分析,可以得到运放的小信号相频和幅频特性如图(3.4)所示。

电路图连接如图3.3,仿真程序见附录1.12.5VAC.1图3.3 低频小信号特性仿真电路连接图图3.4 低频小信号电压增益分析图该运算放大器的小信号低频电压增益可以看出是112.793dB 。

满足设计指标。

2. 单位增益带宽程序跟测量小信号低频电压增益时相同,仿真波形如图3.5所示。

该运算放大器的单位增益带宽可以看出100.927MHz.满足设计指标。

图3.5 低频小信号单位带宽分析图3. 相位裕度仿真:从图上看出相位裕度为180°-127°=53°,满足设计指标。

程序和测量小信号低频电压增益时相同。

仿真波形如图3.6。

图3.6 相位裕度分析图4. 转换速率(slew rate)运放的转换速率是分析运放在大信号作用下的反映速度。

仿真运放的转换速率可将运放的输出端和反相输入端相连构成单位增益结构。

运放的同相输入端输入2V到3V的阶跃信号,利用仿真软件对该电路做瞬态分析得到的输出波形见图3.8,从仿真波形得到:在输出上升曲线的10%和90%处,其电压分别为2.9V和2.1V;时间分别为10.7ns和3.32ns。

运放的转换速率SR=(2.9V-2.1V)/( 10.7nS—3.32nS)=108.4 V/μs,满足运放的转换速率的指标要求。

折叠式共源共栅运算放大器设计说明

折叠式共源共栅运算放大器设计说明一、设计原理二、设计步骤1.确定规格要求:根据实际应用需求确定输入阻抗、输出阻抗、增益、带宽等参数。

2.选择管子:根据需求选择合适的场效应管。

通常选择具有良好参数的MOS管,如低频用的2N7000,高频用的BF861A等。

3.设计共源级:首先设计共源级,这是整个电路的放大核心。

根据增益要求和输入阻抗要求,确定共源电阻的值,再根据场效应管的参数计算源极电流和电压。

同时,要保证共源级的电流和电压工作在合适的范围内,不引起过大的功耗和失真。

4.设计共栅级:共栅级起到输出驱动的作用,可以提供较低的输出阻抗。

根据输出阻抗和带宽要求,选择合适的共栅电阻值和驱动电路的参数。

同时要注意共栅级的工作点和共源级的匹配,以保证电路的整体性能。

5.接入电源电压:根据电路需求,确定合适的电源电压。

注意电源电压的选择要与场效应管的参数相匹配,避免电压过高或过低导致管子失效或工作不稳定。

6.进行仿真和调试:在完成电路设计后,进行电路仿真和调试,检查电路的增益、带宽等参数是否满足设计要求。

可以使用SPICE电路仿真软件进行仿真,根据仿真结果对电路进行调整和优化。

7.布局和绘制电路板:根据电路设计,进行布局和绘制电路板。

布局过程中要注意相邻元件的干扰和电路的稳定性。

绘制电路板时要保持线路的规整和排布的合理性。

8.组装和测试:完成电路板制作后,进行元件的组装和焊接。

然后进行电路的测试和调试,检查电路的工作状态和各项指标是否满足要求。

三、注意事项1.设计时要考虑到电压的限制,避免电路失效或工作不稳定。

2.选择合适的场效应管,根据具体需求选择低频或高频的管子。

3.设计时要注意电路整体性能,使其在增益、带宽等方面满足要求。

4.在进行仿真时,要根据仿真结果对电路进行调整和优化,确保电路性能达到最佳状态。

5.布局和绘制电路板时要注意干扰和稳定性,保持线路的规整和排布的合理性。

6.组装和测试时要仔细检查,确保电路的工作状态和各项指标达到要求。

折叠式共源共栅运算放大器设计

折叠式共源共栅运算放大器目录一.摘要 (2)二.电路设计指标 (3)三.电路结构 (3)四.手工计算 (7)五.仿真验证 (10)六.结论 (12)七.收获与感悟 (12)八.参考文献 (13)摘要运算放大器在现代科技的各个领域得到了广泛的应用,针对不同的应用领域出现了不同类型的运放。

本文完成了一个由pmos作输入的放大器。

vdd为3.3v,负载电容为1pf,增益Av 大于80dB,带宽GBM大于100MHz的放大器。

输出级采用共源级结构以提高输出摆幅及驱动能力,为达到较宽的带宽,本文详细分析推导了电路所存在的极零点,共源共栅镜像电流源产生Ibias。

选择P沟道晶体管的宽度和长度,使得它们的m g 和ds r 与N沟道晶体管的情况相匹配。

关键字:运算放大器、共源共栅级、极点AbstractOperation amplifiers are widely used in many field s nowadays。

All kinds of differential operation amplifiers appear f6r special application.One basic cell of which is fully differential operation amplifiers is designed in the thesis.Power Supply 3.3v,load capacitor 1pf,Gain>80dB,GBM>100MHz。

The output stage is common source amplifier for getting proper DC operation point,for the purpose of wider bandwidth,we carefully analysis the pole and zero in the circuit ,use common source common gate as current Ibias。

折叠式共源共栅cmos运算放大器的设计与优化

折叠式共源共栅cmos运算放大器的设计与优化下载提示:该文档是本店铺精心编制而成的,希望大家下载后,能够帮助大家解决实际问题。

文档下载后可定制修改,请根据实际需要进行调整和使用,谢谢!本店铺为大家提供各种类型的实用资料,如教育随笔、日记赏析、句子摘抄、古诗大全、经典美文、话题作文、工作总结、词语解析、文案摘录、其他资料等等,想了解不同资料格式和写法,敬请关注!Download tips: This document is carefully compiled by this editor. I hope that after you download it, it can help you solve practical problems. The document can be customized and modified after downloading, please adjust and use it according to actual needs, thank you! In addition, this shop provides you with various types of practical materials, such as educational essays, diary appreciation, sentence excerpts, ancient poems, classic articles, topic composition, work summary, word parsing, copy excerpts, other materials and so on, want to know different data formats and writing methods, please pay attention!折叠式共源共栅CMOS运算放大器的设计与优化1. 引言在集成电路领域,CMOS运算放大器一直是研究的热点之一。

一种折叠共源共栅运算放大器的设计

一种折叠共源共栅运算放大器的设计关键词:运算放大器,ADC, DAC,模拟集成电路,混合信号集成电路,跨导运算放大器,共源共栅1 引言随着集成电路技术的不断发展,高性能运算放大器广泛应用于高速模/数转换器(ADC)、数/模转换器(DAC)、开关电容滤波器、带隙电压基准源和精密比较器等各种电路系统中,成为模拟集成电路和混合信号集成电路设计的核心单元电路,其性能直接影响电路及系统的整体性能,高性能运算放大器的设计一直是模拟集成电路设计研究的热点之一,以折衷满足各种应用领域的需要。

许多现代集成CMOS运算放大器被设计成只驱动电容负载。

有了这样只有电容的负载,对于运放放大器,就没有必要使用电压缓存器来获得低输出阻抗,因此,有可能设计出比那些需要驱动电阻负载的运算放大器具有更高速度和更大的信号幅度的运算放大器。

通过在一个只驱动电容负载的运算放大器输出端只有一个高阻抗节点,可以获得这些提高,这些运算放大器在其他节点看到的导纳与MOS管的跨导在一个量级上,因此他们具有低阻抗。

有了所有相对低阻抗的内部节点,运算放大器的速度得到最大化,这里还应该提到的是:这些低节点阻抗使得所有节点而不是输出节点的电压信号降低,然而,各种晶体管的电流信号可能非常大,对这些运算放大器,应看到补偿通常是由负载电容达到的,这样,当负载电容变大,运算放大器通常变得更稳定也更慢,这些现代晶体管最重要的参数之一是他们的跨导值(即输出电流和输入电流的比)。

因此,一些设计者称这些现代运算放大器为跨导运算放大器或者运算跨导放大器(OTA)。

在各种OTA结构中,折叠共源共栅运放结构的运算放大器可以使设计者优化二阶性能指标,这一点在传统的两极运算放大器中是不可能的,特别是共源共栅技术对提高增益、增加PSRR值和在输出端允许自补偿是有用的。

这种灵活性允许在CMOS工艺中发展高性能无缓冲运算放大器,目前,这样的放大器已被广泛应用无线电通信的集成电路中。

本文介绍的运放是一种采用TSMC 0.18 μm Mixed Signal SALICIDE(1P6M,1.8V/3.3V)CMOS工艺的折叠共源共栅运放,并对其进行了DC,AC及瞬态分析,最后与设计指标进行比较。

折叠共源共栅单级运算放大器设计

折叠共源共栅单级运算放大器设计折叠共源共栅单级运算放大器(FCSG)是一种常用的放大器电路,在电子电路设计和微电子技术中具有广泛的应用。

它是由共源放大器和共栅放大器组成的,可以实现高放大增益、宽带、低噪声和低功耗等特性。

FCSG电路的基本原理是,共源放大器用来实现信号的放大和匹配,而共栅放大器则承担了放大器的输出任务。

在FCSG电路中,信号来源将直接连接到共源极,而输出信号则从共栅极获取。

折叠共源共栅单级运算放大器的设计是一个复杂的过程,需要注意以下几个关键因素:1.电路的电流:FCSG电路的电流是非常重要的参数,因为它决定了电路的增益和功耗。

因此,在设计FCSG电路时,必须考虑到电流大小及其对电路性能的影响。

2.电路的电容:FCSG电路的电容也是关键的因素,它决定了电路的带宽和响应速度。

在FCSG电路设计时,需要合理地规划电容大小和放置位置,以确保电路性能的最佳效果。

3.电路的阻抗匹配:FCSG电路需要从信号源中获取信号,因此必须考虑电路的阻抗匹配问题。

如果电路的输入阻抗和信号源的输出阻抗不匹配,将会影响电路性能。

因此,在FCSG电路设计中,需要使用适当的匹配电路来解决这个问题。

4.电路的噪声:FCSG电路中的噪声也是设计考虑的重要因素之一。

由于FCSG电路通常用于低噪声电路设计,因此需要对电路的噪声进行特殊处理,例如选择低噪声元器件和合理的电路布局等。

总的来说,折叠共源共栅单级运算放大器的设计需要综合考虑电路的电流、电容、阻抗和噪声等因素,以最大程度地实现电路性能的优化。

在实际应用中,还需要结合具体的应用场景和要求,进行合理的电路设计和优化。

折叠式共源共栅运算放大器设计

折叠式共源共栅运算放大器设计1.设计原理折叠式共源共栅运放的设计原理主要基于共源共栅电路,通过级联的方式来增加放大器的增益和带宽。

共源共栅电路是一种结合了共源级和共栅级的运放电路,具有高输入阻抗、低输出阻抗和高增益的特点。

通过将两个共源共栅电路级联,可以得到折叠式共源共栅运放,进一步提高增益和带宽。

2.关键参数在设计折叠式共源共栅运放时,需要考虑以下几个关键参数:-增益:增益是指输入信号与输出信号之间的比例关系,是一个放大器的主要性能指标。

在设计过程中,需要确定所需的增益,并根据电路结构进行调整。

-带宽:带宽是指放大器能够放大信号的频率范围。

在设计折叠式共源共栅运放时,需要选择适当的电容和电阻来提供所需的带宽。

-输入阻抗:输入阻抗是指放大器的输入端对外部信号的电阻。

在折叠式共源共栅运放中,可以通过调整栅极电阻和源极电阻来控制输入阻抗。

-输出阻抗:输出阻抗是指放大器的输出端对外部负载的电阻。

在设计过程中,需要考虑输出阻抗对于负载的影响,并选择适当的电路结构来提供所需的输出阻抗。

3.设计流程-确定设计规格:首先需要明确设计的需求,包括增益、带宽和输入输出阻抗等。

-电路拓扑选择:选择折叠式共源共栅电路作为基本电路拓扑。

-参数计算:根据设计规格和电路拓扑,计算所需的电阻、电容等参数。

-电路模拟:使用电路模拟软件,如SPICE,对电路进行仿真,验证设计参数的正确性,并进行性能分析。

-电路调整:根据仿真结果,对电路进行调整,满足设计规格。

-PCB设计:将电路布局成PCB,进行进一步的测试和优化。

-调试与测试:进行电路的调试和测试,对性能进行评估和调整。

4.实际应用折叠式共源共栅运放可应用于各种通信和成像系统中,例如放大器、滤波器、混频器等。

由于折叠式共源共栅运放具有高增益和宽带宽的优势,可以提高信号的质量和速度,使系统更加稳定和可靠。

同时,折叠式共源共栅运放还可以用于低功耗电路设计中,通过优化电路结构和参数选择,降低功耗并提高电路性能。

一种高电流效率套筒式共源共栅运算放大器的设计

一种高电流效率套筒式共源共栅运算放大器的设计套筒式共源共栅运算放大器是一种常用的电路设计,可以实现高电流效率的放大功能。

在设计这种电路时,需要考虑到放大器的性能指标、工作原理和设计注意事项等方面。

首先,设计一个高电流效率的套筒式共源共栅运算放大器,我们需要明确一些性能指标,如增益、带宽、输入和输出阻抗等。

在实际应用中,增益通常为几十至上百倍,带宽通常在几十kHz至几百kHz之间,输入和输出阻抗也需要具备匹配特性。

接下来,我们可以采取如下的套筒式共源共栅运算放大器电路设计方案:1.工作原理:套筒式共源共栅运放电路是将输入信号通过共源级电路进行放大,然后通过共栅级电路进行输出,两级电路之间共享负载电阻,以提高电流效率。

2.器件选择:可以选择n沟道MOSFET作为工作元件,因为它们具有较高的输入阻抗、低噪声以及低失真等特点。

3.共源级电路设计:共源级电路负责信号的放大,输入信号通过电容耦合方式输入到栅极,并通过与源极串联的电阻实现负反馈,以提高放大器的稳定性和增益。

同时,需要注意源极电极和分压电阻的设计,以确定电流的设置。

4.共栅级电路设计:共栅级电路负责输出信号的放大,在这个级别上需要设计合适数值的电阻和电容,以确定放大器的带宽和阻抗匹配特性。

此外,为了保持共源共栅级电路的偏置电位稳定,可以加入偏置电路。

5.电源电压选择:根据放大器的需求,确定电源电压的选择,通常为几个伏特到几十伏特之间。

6.电路布局:将电路布局设计为紧凑且规整,以提高电路的稳定性和可靠性。

同时,要注意信号线和电源线之间的距离,以减小干扰。

7.仿真和优化:在设计完成后,需要使用相应的电路仿真工具进行仿真和优化,以验证电路的性能指标,例如增益、带宽和失真等,确保放大器能够满足设计要求。

根据仿真结果,可以对电路进行优化和改进。

8.PCB设计:最后,将电路设计转化为PCB布局图,并进行制板和组装。

在电路布局过程中,需要注意信号线和电源线的走线,以及地线设计,以提升电路的抗干扰性能、防止反馈和共模干扰。

一种两级全差分折叠共源共栅运算放大器的设计

Rcc

=

Cc + CL gm12Cc

=

4.75 gm12

(2.10)

2.确定尾电流大小 由图 2.1 可知当输入差分信号很大时,不妨设 M2 管截止,此时通过 Cc2 的充电电流大

小为 ID6-ID10,由此可计算出压摆率为

SR = ID6 − ID10 > 2V / μs Cc

(2.11)

其中 Cc=8pF,故 ID6-ID10=16μA。在设计中为了留有裕量,取 ID6-ID10=25μA。又

载电容较大,为 30pF。可以预计电路的主极点位于第一级放大器的输出端,而非主极点位 于第二级放大器的输出端,且与主极点的值相差不远。频率补偿的目的就是尽可能使这两个 极点分离开,可以采取的方案有密勒补偿。同时,还可以引入左半平面的零点,以补偿非主

2

极点造成的相频恶化,例如给 CMFB 的共模取样电阻并上电容等。 除了考虑电路差模环的频率稳定性外,还应该考虑共模环的稳定性。因为 CMFB 电路

为了达到 60º相位裕度,应满足

(2.6)

PM = 180 + Ph[T ( jGB)] = 60

(2.7)

由

Ph[T ( jω)] = − tan−1( ω ) − tan−1( ω ) + tan−1( ω )

− p1

− p2

−z

(2.8)

代入(2.7)式,并设 z > 10GB,可以求得|p2|=2.2GB,Cc > 0.22CL=6.6pF。在设计中为

(2.13)

式中 VDS6 < VTP 总能成立,所以输入管 M1、M2 工作于饱和区。实际上,输入共模电压最 小可以低于 0V。输入共模电压最大值至少应为 1.2V,有

折叠式共源共栅运算放大器设计实验

折叠式共源共栅运算放大器设计实验一、设计步骤1.确定规格和目标:首先确定设计的规格和目标,例如增益、带宽、输入输出电阻等。

2.选择适当的工作点:根据目标确定合适的工作点。

通常,选择中间状态的电流偏置,例如源极电流和漏极电流各占目标电流的一半。

3.估计W/L比例:根据工作点电流和所用晶体管的尺寸参数,估计晶体管的W/L比例。

可以使用厂商提供的模型参数进行计算。

4.电流源设计:设计适当的电流源,用于提供偏置电流。

电流源可以采用单端(如PMOS、NMOS)或差分结构(如源随器)。

5.阶数计算:根据需求和规格,计算需要的放大器阶数。

6.确定并绘制电路拓扑:根据放大器的阶数,选择合适的电路拓扑。

折叠式共源共栅运放通常由两个共源共栅级联组成。

绘制电路图,包括晶体管、电容、电流源等。

7.进行直流偏置分析:进行直流偏置分析,计算电压、电流等参数。

确保电路能够在合适的工作点工作,并且各个极点和零点在期望的频率范围内。

8.进行交流分析:进行交流分析,计算增益、带宽等参数。

可以使用电路仿真软件进行模拟分析,找到需要优化的部分。

9.优化设计:根据仿真结果,逐步调整电路参数,优化设计。

可以通过改变晶体管的W/L比例、电容的数值等参数,使得仿真结果符合要求。

10.布局设计:进行电路的布局设计,包括电源、接地、电容、晶体管等部分的布局。

注意避开毫米波的射频干扰源,并且尽量减少板间互电容等干扰。

11.进行仿真验证:进行全局电路的仿真验证,确保电路能够满足设计要求。

12.绘制电路原理图和PCB板:根据最终的设计结果,绘制电路原理图和PCB板,进行制作。

二、实验过程1.制作PCB板:根据设计的PCB布局图,制作PCB板。

2.感知电路:将制作好的PCB板安装到实验台上,连接电源和信号源。

3.测量电路参数:使用万用表、示波器等仪器,测量电路参数,例如增益、带宽、输入输出电阻等。

4.分析结果:根据测量结果,分析电路的性能是否满足设计要求。

折叠式共源共栅CMOS运算放大器的设计

折叠式共源共栅CMOS运算放大器的设计该电路由两级放大器组成,第一级为共源放大器,第二级为共栅放大器。

下面将详细介绍各个部分的设计步骤和注意事项。

1.设计共源放大器:共源放大器的设计旨在实现高电压增益、宽带宽和稳定的工作点。

主要的设计步骤如下:-根据所需的增益和带宽确定工作点的直流电压和电流。

一般而言,直流电压应足够大,以提供足够的电压增益;而直流电流应适中,以保持功耗的合理范围。

-选择合适的晶体管尺寸和W/L比例,以满足所需的增益和带宽要求。

通常情况下,尺寸越大,增益越高,但同时也会增加功耗。

-设计偏置电路,用以稳定工作点,并提供所需的电流。

常见的偏置电路包括电流镜和电流源。

2.设计共栅放大器:共栅放大器的设计目标是进一步提高增益和带宽,并提供合适的输出电压。

以下是一些重要的设计考虑因素:-通过选择适当的晶体管尺寸和W/L比例,以满足所需的功率增益和输出电压范围。

与共源放大器类似,通常情况下尺寸越大,输出电压范围越大。

-需要设计合适的负载电路,以提供合适的输出电压和输出电流。

常见的负载电路包括电流镜和电流源。

3.总体电路优化:在设计过程中,需要进行一系列的优化步骤,以满足设计要求。

以下是一些常见的优化技术:-频率补偿:通过选择合适的补偿电容和电阻,提高电路的带宽和稳定性。

-去耦电容:通过添加适当的去耦电容,提高电路的低频响应和直流工作点稳定性。

-噪声优化:通过减小晶体管尺寸、优化偏置电路等措施,减小电路的噪声。

综上所述,折叠式共源共栅CMOS运算放大器的设计需要考虑多个方面,包括增益、带宽、工作点、输出电压范围等。

通过合理选择晶体管尺寸和W/L比例、设计合适的负载电路和偏置电路,以及进行适当的优化,可以实现高性能的运算放大器设计。

最后,需要进行电路的仿真和验证,以确保设计的性能符合预期要求。

一款高性能共源共栅运算放大器设计

一款高性能共源共栅运算放大器设计于M5,M6 的源端,M11,M12 的输入电压大小与M5,M6 相同,设计管子宽长比尺寸一样,M11,M12 维持了M3a,M3b,M4a,M4b 漏电势,帮助改善它们之间的匹配性。

图2 中左边部分为偏置电路,其中Vbp1 为M0 管提供偏置电流,Vbp2 为M7,M8 提供偏置电压。

Vbn2 为M5,M6,M11,M12 提供偏置电压。

I1,I2 为外部引入的基准电流。

在引入I2 后,流过M1,M14,M15,M16 的电流相同,根据电流公式,宽长比与Von(过驱动电压)成反比,调节宽长比使|Von|在120~400 mV 之间,很容易就能得到Vbp1。

计算Vbp1,Vbp2 的方法相同。

在电路进行DC 仿真时,M1 和M13 工作在线性区。

为了证明复用型折叠式共源共栅运算放大器相比文献中折叠式共源共栅运算放大器具有的优越性,在分析电路时,假定所有管子工作在饱和区,饱和区电流公式为:首先分析两种电路的低频增益,低频增益的公式为:Av=GmR0。

在折叠式共源共栅运算放大器运放中:GMFC=gm1;复用型折叠式共源共栅运算放大器中:GMRFC=4gm1a,考虑到M1 的尺寸是M1a 的2 倍,由公式Gm=2I/(VGS-VTH)可知,gm1=2gm1a,在相同的输出电阻情况下,2 倍的输入跨导,大约会给运放带来6 dB 的增益提升。

在两个运放的输出电阻分析中,由运放主电路的右边电路的小信号模型有:ROFC=gm6 rds6(rds2‖rds4)‖gm8rds8 rds10 (2)RORFC=gm6 rds6(rds2a‖rds4a)‖gm8rds8 rds10 (3)假设其他参数相同的条件下,由公式rds=1/(λID)可知,RORFC 比RRFC 大。

因此,复用型比传统型折叠式共源共栅运放在低频增益上有8~10。

折叠式共源共栅运算放大器设计

CMOS课程设计折叠式共源共栅运算放大器设计学院: 机械与电子工程学院专业: 电子科学与技术指导老师: 蔡志民班级: 1221401学号: 201220140125姓名: 姜国理报告时间: 2015-07-05一、设计目的设计共源共栅运算放大器,使其满足V DD=5V,功率P=10mW,输出摆幅为2.35V,增益A V约10dB。

使用st02 0.5um 5V CMOS工艺5V晶体管模型。

学习差动放大器DC扫描、AC、瞬态分析的方法。

参数给定:C OX=(εsiεo)/t ox其中εsi=8.85*10-12,εo=3.9,t ox =9nm;u n=350cm2/v/s,u p=100 cm2/v/s。

二、设计步骤本次实验采用IC615设计整个过程。

启动cadence工具,在terminal中输入virtuoso &启动IC615并后台运行,如图所示:启动后CIW窗口如图所示:启动IC615后,新建library取名201220140125,并关联到st02库,如图所示:在library中新建cell,选择schematic原理图输入,并调用st02器件mn及mp,分别修改参数,最后原理图如图所示:参数的设定:1)电流分配:根据10mw的功率,及电源电压5v,由公式p=ui,算出I总=2mA,由电路对称性平均分配电流M0,M1为1mA,M9流过M8,及M10的电流之和也为1mA,其他的管子电流都为0.5mA。

2)过驱动电压分配:电流确定后,根据摆幅2.35v分配过驱动电压,M0,M1的V on=0.45v,M2,3的V on=0.8v,M4,5,8,10的V on=0.8v,M6,7的V on=0.6v,M9的V on=1v。

3)宽长比确定:通过电流与过驱动电压的关系式确定宽长比,由于所有mos管都必须工作在饱和区,所以使用饱和区的电流-过驱动电压的关系:Nmos管:I DS=1/2u n C OX(W/L)(V GS-V th)2=1/2u n C OX V OD2=>(W/L)=(2 I DS) /( u n C OX V OD2)Pmos管:I DS=1/2u p C OX(W/L)(V GS-V th)2=1/2u p C OX V OD2=>(W/L)= (2 I DS)/(u p C OX V OD2)根据公式可得所有mos管的宽长比,分别为:(w/l)0,1=149.25/0.55, (w/l)2,3=22.62/0.55, (w/l)4,5,8,10=5.87/0.5,(w/l)6,7=10.44/0.5, (w/l)9=7.5/0.54)分配初始偏置电压值:mos管阈值电压的初始值由工艺库中给定,pmos管的阈值电压为V th=-0.8V,nmos管的阈值电压为V th=0.7V,这些值将在仿真过程中修正。

6折叠式共源共栅运算放大器设计实验汇总

6折叠式共源共栅运算放大器设计实验汇总折叠式共源共栅运算放大器是一种常用的电路结构,常用于设计高增益、低功耗的放大器电路。

本文将对这种电路进行实验设计和汇总,总结电路设计过程中的关键问题和解决方法。

首先,我们需要确定设计的目标。

折叠式共源共栅运算放大器的主要性能指标包括增益、带宽、输入电阻、输出电阻、功耗等。

在设计之前,我们要先确定这些性能指标的要求,以便在设计中进行优化。

接下来,我们需要确定电路的工作点。

工作点决定了电路的偏置电流和电压,对放大器的性能起着重要作用。

在折叠式共源共栅运算放大器中,我们可以通过调整源极电流和栅极电压来实现合适的工作点。

一般情况下,我们希望工作点在电压-电流特性曲线的中间位置,以便有足够的线性放大范围。

然后,我们需要选择合适的晶体管。

在折叠式共源共栅运算放大器中,常常选择NMOS晶体管作为放大器管,因为NMOS晶体管具有较好的线性特性和较高的增益。

根据工作点的要求,我们可以在晶体管的数据手册中找到合适的晶体管型号。

接下来,我们需要确定电路的输入阻抗。

由于折叠式共源共栅运算放大器的输入是通过共源极实现的,所以输入阻抗受到源极电流的影响。

为了实现较高的输入阻抗,我们可以选择较大的源极电流。

此外,还可以通过并联电容以降低输入阻抗。

然后,我们需要确定电路的增益和带宽。

增益和带宽是折叠式共源共栅运算放大器的两个主要指标。

增益可以通过选择合适的电阻和电容来调整,通常可以通过负反馈来实现。

带宽则受到晶体管的频率特性限制,可以通过合适的电容和电感来进行补偿。

最后,我们需要进行电路的仿真和测试。

通过电路仿真软件,我们可以验证电路的性能指标是否满足设计要求,并进行一些优化调整。

在测试中,我们可以使用示波器、函数发生器等仪器测量电路的增益、带宽和失调等指标。

综上所述,折叠式共源共栅运算放大器设计的关键问题包括确定设计目标、确定电路的工作点、选择合适的晶体管、确定电路的输入阻抗、确定电路的增益和带宽,以及进行电路的仿真和测试。

6 折叠式共源共栅运算放大器设计实验.

设置DC参量时,首先,要选择Save DC Operating Point项,此项是为了保存静态工作点的;然后在Sweep Variable区域选择Design Variable项,选取变量名称,可以直接输入你所定义的变量名,也可以从下面的Select Design Variable中选择需要扫描的变量,我们这里扫描差动信号的直流分量vdm1。在Sweep Range中选择扫描变量的范围,定义起始点为0V,终止点为3.3V,而且采取线性扫描方式,扫描的步长设为0.01V。

建立的symbol的图形(可以改变图形形状),如下图所示:

5.加入激励

对于已经生成symbol的图形,需要给输入端加入激励之后才能够进行仿真。需要生成一个新的cell view作仿真,此处起名为sim_pucker-SG,易于统一名称。

Cell view的生成同上所述,在cell view的设计过程中加入刚刚设计的折叠式共源共栅放大器作为仿真模型,对其输入端加激励。

从上面的叙述可知,电容的值是一个根据要求而变化的值,所以我们把电容值设为一个参数cap,在仿真过程中再添加其值。这样只是为了方便更改而已,你也可以直接对负载电容赋值,在仿真时,再根据情况更改电容值。

负载电容的值设为参变量cap,在仿真过程中给定值。

注意:在作仿真图形时,还需要有一个用来规定电源电压值的电路,这是为了防止多个电路中有多个电源电压的情况,这样只需设定一个电源电压来规定电源电压的值,而不会发生冲突。

负载电容值的确定:

对于负载电容值的确定是有要求的,因为题目要求单位增益带宽尽可能的大,所以在满足了增益的情况下,需要主极点越大越好,只有主极点越大才能保证单位增益带宽越大。主极点与输出阻抗和负载电容的乘积的倒数有关,而输出阻抗的值影响增益的大小,如果输出阻抗越大,则增益越大,但是主极点越小,从而使单位增益带宽越小,所以只有在增益一定的情况下改变负载电容的值来增加单位增益带宽。

折叠式共源共栅运算放大器设计

折叠式共源共栅运算放大器目录一.摘要 (2)二.电路设计指标 (3)三.电路结构 (3)四.手工计算 (7)五.仿真验证 (10)六.结论 (12)七.收获与感悟 (12)八.参考文献 (13)摘要运算放大器在现代科技的各个领域得到了广泛的应用,针对不同的应用领域出现了不同类型的运放。

本文完成了一个由pmos作输入的放大器。

vdd为3.3v,负载电容为1pf,增益Av 大于80dB,带宽GBM大于100MHz的放大器。

输出级采用共源级结构以提高输出摆幅及驱动能力,为达到较宽的带宽,本文详细分析推导了电路所存在的极零点,共源共栅镜像电流源产生Ibias。

选择P沟道晶体管的宽度和长度,使得它们的m g 和ds r 与N沟道晶体管的情况相匹配。

关键字:运算放大器、共源共栅级、极点AbstractOperation amplifiers are widely used in many field s nowadays。

All kinds of differential operation amplifiers appear f6r special application.One basic cell of which is fully differential operation amplifiers is designed in the thesis.Power Supply 3.3v,load capacitor 1pf,Gain>80dB,GBM>100MHz。

The output stage is common source amplifier for getting proper DC operation point,for the purpose of wider bandwidth,we carefully analysis the pole and zero in the circuit ,use common source common gate as current Ibias。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

共源共栅运算放大器的设计

共源共栅运算放大器,也称为共源共栅放大器或共栅源跟随器,是常用的运算放大器电路结构。

它由共源放大器和共栅放大器组成,可以提供高增益、宽带宽并具有高输入电阻和低输出阻抗的特点。

下面将详细讨论共源共栅运算放大器的设计。

设计目标:

1.高增益:希望放大器具有高增益,以提供较大的放大倍数。

2.宽带宽:希望放大器具有较宽的频带,以传输更高频率的信号。

3.高输入电阻:希望放大器具有较高的输入电阻,以不对被测电路产生影响。

4.低输出阻抗:希望放大器具有较低的输出阻抗,以不对后级电路产生影响。

设计步骤:

1.选择晶体管:

选择性能良好、参数稳定的晶体管作为放大器的关键部件。

常用的晶体管有MOSFET和JFET,选用适合的型号,使其性能满足设计的要求。

2.偏置电路设计:

根据晶体管的工作条件,设计偏置电路以保证放大器的工作稳定性。

通常采用电流源和电阻网络来实现晶体管的偏置。

3.增益极化设计:

确定放大器的增益级数和增益大小,并选择适当的分压比例和电阻值,使得输出电压能够满足要求。

同时考虑增益的稳定性,防止输出波形失真。

4.频率补偿设计:

由于共源共栅放大器的频率响应受到极点和零点的影响,需要设计频

率补偿电路来提高带宽。

常用的频率补偿方法有米勒补偿电容和并联补偿

电容等。

5.输入和输出阻抗设计:

通过选择合适的电路参数和组件数值,使得输入电阻和输出电阻达到

所需的要求。

一般采用反馈电阻网络来实现输入和输出阻抗的调节。

6.功耗和温度设计:

考虑到功耗和温度对放大器性能的影响,需要进行功耗和热量分析,

并选择适当的散热器来保证放大器的长期稳定工作。

7.电源设计:

根据放大器的电源需求,选择适当的电源电压和电源过滤电路,以保

证放大器的工作正常和稳定性。

以上是共源共栅运算放大器的设计步骤。

在设计过程中,需要综合考

虑各种因素,并根据具体的应用场景和要求进行优化。

通过合理的设计和

调试,可以获得性能良好的共源共栅运算放大器。