第5章_课后习题答案

第五章微机原理课后习题参考答案

习题五一. 思考题⒈半导体存储器主要分为哪几类?简述它们的用途和区别。

答:按照存取方式分,半导体存储器主要分为随机存取存储器RAM(包括静态RAM和动态RAM)和只读存储器ROM(包括掩膜只读存储器,可编程只读存储器,可擦除只读存储器和电可擦除只读存储器)。

RAM在程序执行过程中,能够通过指令随机地对其中每个存储单元进行读\写操作。

一般来说,RAM中存储的信息在断电后会丢失,是一种易失性存储器;但目前也有一些RAM 芯片,由于内部带有电池,断电后信息不会丢失,具有非易失性。

RAM的用途主要是用来存放原始数据,中间结果或程序,与CPU或外部设备交换信息。

而ROM在微机系统运行过程中,只能对其进行读操作,不能随机地进行写操作。

断电后ROM中的信息不会消失,具有非易失性。

ROM通常用来存放相对固定不变的程序、汉字字型库、字符及图形符号等。

根据制造工艺的不同,随机读写存储器RAM主要有双极型和MOS型两类。

双极型存储器具有存取速度快、集成度较低、功耗较大、成本较高等特点,适用于对速度要求较高的高速缓冲存储器;MOS型存储器具有集成度高、功耗低、价格便宜等特点,适用于内存储器。

⒉存储芯片结构由哪几部分组成?简述各部分的主要功能。

答:存储芯片通常由存储体、地址寄存器、地址译码器、数据寄存器、读\写驱动电路及控制电路等部分组成。

存储体是存储器芯片的核心,它由多个基本存储单元组成,每个基本存储单元可存储一位二进制信息,具有0和1两种状态。

每个存储单元有一个唯一的地址,供CPU访问。

地址寄存器用来存放CPU访问的存储单元地址,该地址经地址译码器译码后选中芯片内某个指定的存储单元。

通常在微机中,访问地址由地址锁存器提供,存储单元地址由地址锁存器输出后,经地址总线送到存储器芯片内直接进行译码。

地址译码器的作用就是用来接收CPU送来的地址信号并对它进行存储芯片内部的“译码”,选择与此地址相对应的存储单元,以便对该单元进行读\写操作。

计算机网络课后习题答案(第五章)

答:可能,但应用程序中必须额外提供与TCP相同的功能。

5—08为什么说UDP是面向报文的,而TCP是面向字节流的?答:发送方UDP 对应用程序交下来的报文,在添加首部后就向下交付IP 层。

UDP 对应用层交下来的报文,既不合并,也不拆分,而是保存这些报文的边界。

接收方UDP 对IP 层交上来的UDP 用户数据报,在去除首部后就原封不动地交付上层的应用进程,一次交付一个完整的报文。

发送方TCP对应用程序交下来的报文数据块,视为无结构的字节流〔无边界约束,课分拆/合并〕,但维持各字节5—09端口的作用是什么?为什么端口要划分为三种?答:端口的作用是对TCP/IP体系的应用进程进行统一的标志,使运行不同操作系统的计算机的应用进程能够互相通信。

熟知端口,数值一般为0~1023.标记常规的效劳进程;1024~491515—10试说明运输层中伪首部的作用。

答:用于计算运输层数据报校验和。

5—11某个应用进程使用运输层的用户数据报UDP,然而继续向下交给IP层后,又封装成IP 数据报。

既然都是数据报,可否跳过UDP而直接交给IP层?哪些功能UDP提供了但IP没提提供?答:不可跳过UDP而直接交给IP层IP数据报IP报承当主机寻址,提供报头检错;只能找到目的主机而无法找到目的进程。

UDP提供对应用进程的复用和分用功能,以及提供对数据差分的过失检验。

5—12一个应用程序用UDP,到IP层把数据报在划分为4个数据报片发送出去,结果前两个数据报片丧失,后两个到达目的站。

过了一段时间应用程序重传UDP,而IP层仍然划分为4个数据报片来传送。

结果这次前两个到达目的站而后两个丧失。

试问:在目的站能否将这两次传输的4个数据报片组装成完整的数据报?假定目的站第一次收到的后两个数据报片仍然保存在目的站的缓存中。

答:不行重传时,IP数据报的标识字段会有另一个标识符。

仅当标识符相同的IP数据报片才能组装成一个IP数据报。

前两个IP数据报片的标识符与后两个IP数据报片的标识符不同,因此不能组装成一个IP数据报。

大学物理课后答案第5章

第五章 热力学基础5-1 在水面下50.0 m 深的湖底处(温度为4.0℃),有一个体积为1.0×10-5 m 3的空气泡升到湖面上来,若湖面的温度为17.0℃,求气泡到达湖面的体积。

(大气压P 0 = 1.013×105 Pa ) 分析:将气泡看成是一定量的理想气体,它位于湖底和上升至湖面代表两个不同的平衡状态。

利用理想气体物态方程即可求解本题。

位于湖底时,气泡内的压强可用公式gh p p ρ+=0求出,其中ρ为水的密度(常取ρ = 1.0⨯103 kg·m -3)。

解:设气泡在湖底和湖面的状态参量分别为(p 1,V 1,T 1)和(p 2,V 2,T 2)。

由分析知湖底处压强为ghp gh p p ρρ+=+=021。

利用理想气体的物态方程可得空气泡到达湖面的体积为()3510120121212m 1011.6-⨯=+==T p V T gh p T p V T p V ρ5-2 氧气瓶的容积为3.2×10-2 m 3,其中氧气的压强为1.30×107 Pa ,氧气厂规定压强降到1.00×106 Pa 时,就应重新充气,以免经常洗瓶。

某小型吹玻璃车间,平均每天用去0.40 m 3 压强为1.01×105 Pa 的氧气,问一瓶氧气能用多少天?(设使用过程中温度不变) 分析:由于使用条件的限制,瓶中氧气不可能完全被使用。

从氧气质量的角度来分析。

利用理想气体物态方程pV = mRT /M 可以分别计算出每天使用氧气的质量m 3和可供使用的氧气总质量(即原瓶中氧气的总质量m 1和需充气时瓶中剩余氧气的质量m 2之差),从而可求得使用天数321/)(m m m n -=。

解:根据分析有RT V Mp m RT V Mp m RT V Mp m 333122111===;;则一瓶氧气可用天数()()5.933121321=-=-=V p V p p m m m n5-3 一抽气机转速ω=400r ּmin -1,抽气机每分钟能抽出气体20升。

第五章课后习题答案

5.10 假设对指令Cache 的访问占全部访问的75%;而对数据Cache 的访问占全部访问的25%。

Cache 的命中时间为1个时钟周期,失效开销为50 个时钟周期,在混合Cache 中一次load 或store 操作访问Cache 的命中时间都要增加一个时钟周期,32KB 的指令Cache 的失效率为0.39%,32KB 的数据Cache 的失效率为4.82%,64KB 的混合Cache 的失效率为1.35%。

又假设采用写直达策略,且有一个写缓冲器,并且忽略写缓冲器引起的等待。

试问指令Cache 和数据Cache 容量均为32KB 的分离Cache 和容量为64KB 的混合Cache 相比,哪种Cache 的失效率更低?两种情况下平均访存时间各是多少?解:(1)根据题意,约75%的访存为取指令。

因此,分离Cache 的总体失效率为:(75%×0.15%)+(25%×3.77%)=1.055%;容量为128KB 的混合Cache 的失效率略低一些,只有0.95%。

(2)平均访存时间公式可以分为指令访问和数据访问两部分:平均访存时间=指令所占的百分比×(读命中时间+读失效率×失效开销)+ 数据所占的百分比×(数据命中时间+数据失效率×失效开销)所以,两种结构的平均访存时间分别为:分离Cache 的平均访存时间=75%×(1+0.15%×50)+25%×(1+3.77%×50)=(75%×1.075)+(25%×2.885)=1.5275混合Cache 的平均访存时间=75%×(1+0.95%×50)+25%×(1+1+0.95%×50)=(75%×1.475)+(25%×2.475)=1.725因此,尽管分离Cache 的实际失效率比混合Cache 的高,但其平均访存时间反而较低。

第5章-习题参考答案

第五章习题参考答案一、填空题1、MCS-51有5个中断源,2个中断优先级,优先级由软件填写特殊功能寄存器 IP 加以选择。

2、外中断请求标志位是 IE0 和 IE1 。

3、 RETI 指令以及任何访问 IE 和 IP 寄存器的指令执行过后,CPU不能马上响应中断。

4、8051单片机响应中断后,产生长调用指令LCALL,执行该指令的过程包括:首先把 PC的内容压入堆栈,以进行断点保护,然后把长调用指令的16位地址送 PC ,使程序执行转向程序存储器中的中断地址区。

二、选择题:1、在中断服务程序中,至少应有一条( D )。

A、传送指令B、转移指令C、加法指令D、中断返回指令2、要使MCS-51能够响应定时器T1中断,串行接口中断,它的中断允许寄存器IE的内容应是( A )。

A、 98HB、 84HC、 42HD、 22H3、MCS-51响应中断时,下列哪种操作不会发生( A )A、保护现场B、保护PCC、找到中断入口D、保护PC转入中断入口4、MCS-51中断源有( A )A、 5个B、 2个C、 3个D、6个5、计算机在使用中断方式与外界交换信息时,保护现场的工作应该是( C )A、由CPU自动完成B、在中断响应中完成C、应由中断服务程序完成D、在主程序中完成6、MCS-51的中断允许触发器内容为83H,CPU将响应的中断请求是( D )。

A、 INT0,INT1B、 T0,T1C、 T1,串行接口D、 INT0,T07、若MCS-51中断源都编程为同级,当它们同时申请中断时,CPU首先响应( B )。

A、 INT1B、 INT0C、 T1D、T08、当CPU响应串行接口中断时,程序应转到( C )。

A、 0003HB、 0013HC、 0023HD、 0033H9、执行MOV IE,#03H后,MCS-51将响应的中断是( D )。

A、 1个B、 2个C、 3个D、0个10、外部中断1固定对应的中断入口地址为( C )。

第五章 课后习题及答案

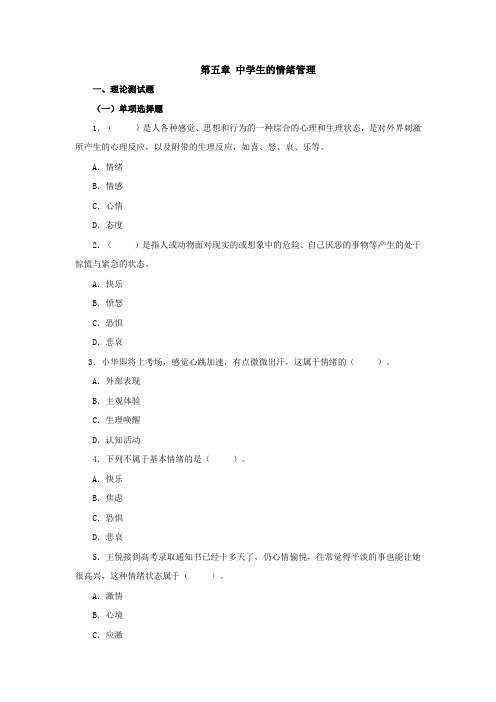

第五章中学生的情绪管理一、理论测试题(一)单项选择题1.()是人各种感觉、思想和行为的一种综合的心理和生理状态,是对外界刺激所产生的心理反应,以及附带的生理反应,如喜、怒、哀、乐等。

A.情绪B.情感C.心情D.态度2.()是指人或动物面对现实的或想象中的危险、自己厌恶的事物等产生的处于惊慌与紧急的状态。

A.快乐B.愤怒C.恐惧D.悲哀3.小华即将上考场,感觉心跳加速,有点微微出汗,这属于情绪的()。

A.外部表现B.主观体验C.生理唤醒D.认知活动4.下列不属于基本情绪的是()。

A.快乐B.焦虑C.恐惧D.悲哀5.王悦接到高考录取通知书已经十多天了,仍心情愉悦,往常觉得平淡的事也能让她很高兴,这种情绪状态属于()。

A.激情B.心境C.应激6.“情急生智”所描述的一种情绪状态是()。

A.心境B.理智C.应激D.激情7.“忧者见之则忧,喜者见之则喜”,这是受一个人的()影响所致。

A.激情B.心境C.应激D.热情8.()是一种猛烈、迅疾和短暂的情绪,类似于平时说的激动。

A.快乐B.应激C.心境D.激情9.狂喜、恐惧的情绪状态属于()。

A.激情B.热情C.应激D.心境10.学生临考的怯场属于()。

A.应激B.心境C.激情D.热情11.车祸、地震、水灾等突如其来的灾难引起的情绪体验是()。

A.心境B.激情C.应激12.晓东在解决了困扰他许久的数学难题后出现的喜悦感属于()。

A.道德感B.理智感C.美感D.效能感13.求知欲属于()。

A.道德感B.理智感C.美感D.应激14.“先天下之忧而忧,后天下之乐而乐”是()。

A.道德感B.理智感C.美感D.热情15.当同学们获悉本班取得学校合唱比赛第一名的成绩时欣喜若狂。

他们的情绪状态属于()。

A.心境B.激情C.应激D.热情16.当人们遇到突然出现的事件或意外发生危险时,为了应付这类瞬息万变的紧急情境,就得果断地采取决定。

这种情况属于()。

A.激情B.应激C.快乐D.心境17.()用因素分析的方法,提出人类具有8~11种基本情绪,它们是兴趣、惊奇、痛苦、厌恶、愉快、愤怒、恐惧、悲伤、害羞、轻蔑、自罪感。

第5章课后习题解答

第5章课后习题解答-情境题

【参考答案三】手环自身一般不具备分析功能,数据分析是 在服务器端完成的。服务器通过使用各种算法和科学缜密的逐 辑运算对采集的数据进行分析,建立健康模型,最终将这些数 据转变成手环可读数字——步数、距离、消耗的卡路里数值等 呈现给终端用户,还可以通过与手环相连的手机端将用户的运 动、睡眠、心率等数据可视化呈现出来并给用户提供健康建议。

【参考答案四】实际上仅依靠手环采集数据做分析是不全面 的,还需结合用户的年龄、体重、身高、性别等个人信息进行 数据分析,因此个人信息填写正确与否直接影响数据分析的准 确性。

【参考答案二】能回答运动时利用的加速度传感器是三轴加 速度传感器,而且是通过捕捉人体三个维度的各项数据,并上传 至服务端进行统计分析。或者增加实例,如利用手环检测心率, 主要是通过光感进行,采用绿色搭配感光光电二极管实时检测流 经手腕血液的流量来获取心率信息。当用户的心脏跳动时,会有 更多的血液流过用户的手腕,绿光的吸收量也会越大;在心脏跳 动间隙,血液流量减少,绿光的吸收也会减少。

B (2)下列可以用于分析数据趋势的是( )。

A. 饼图 B. 折线图 C. 动态热力图 D. 词云图

A (3)数据分析的方法不包括( )。

A. 线性分析 B. 关联分析 C. 聚类分析

D. 数据分类

第5章课后习题解答-思考题

若要求你对本班同学喜欢看的书籍进行分类统计,并对其进行数据分析,你 会如何做?谈谈你的想法。

参考答案一: (项目需求分析)分析书籍分类统计的项目:书名、图书类别、出版时 间、来源(网购、书店购买、图书馆借阅、向他人借阅)、同学姓名, 性别等。 (数据采集)能够选择合适的工具采集和保存信息:可使用文件共享或 选择协同办公软件采集书籍信息记录(逐条统计),能够使用硬盘存储 或云存储方式保存数据。 (数据分析与可视化表达)能够采用词云图、折线图或饼图等方式,按 照图书类别分析出本班同学的图书喜好,能分析出某位同学的兴趣爱好。

高等数学第五章课后习题答案

班级姓名学号1 第五章定积分1.证明定积分性质:òò=b abadxx f kdx x kf )()((k 是常数). 证:òåòå=D =D ==®=®banii ban ii x kf x kf x f k x f k)()(lim )(lim )(1010x x l l 2.估计下列积分值:(1)dxx )sin 1(4542ò+p p解:令x x f 2sin 1)(+=,则02sin cos sin 2)(===x x x x f ‘得驻点:,,221p p==x x 由23)4(,23)4(,1)(,2)2(====p p p pf f f f ,得2)(max ,1)(min ==x f x f 由性质,得pp p p2)(454££òdx x f (2)ò333arctan xdxx 解:令x x x f arctan )(=,01arctan )(2>++=xxx x f ‘,所以)(x f 在]333[,上单调增加,p p33)(max ,36)(min ==\x f x f ,)()(33333arctan 33336333-££-\òp pxdx x ,即pp32a r c t a n 9333££òx d x x班级班级 姓名姓名 学号学号3.比较下列积分值的大小:.比较下列积分值的大小: (1)dx x ò12与dxx ò13解:当10££x 时,有23x x £,且23x x -不恒等于0,0312>-\òdx x x )(,即,即 dxx dxx òò>1212。

(2)ò6pxdx 与ò6sin pxdx解:当60p££x 时,有x x £sin ,且x x sin -不恒等于0,0sin 10>-\òdx x x )(,即,即 dx x dx x òò>1010sin 。

第五章吸收课后习题答案

第五章 吸收课后习题答案一、 填空1.减小;靠近。

2.不变;增加。

3.对数平均推动力法;脱吸因数法。

4.气;液;吸收;液;气;解吸5. 散装填料 二、选择1. B ;2.A ;3.C ;4.D ;5.A . 三、计算题相组成的换算【5-1】在吸收塔中用水吸收混于空气中的氨。

已知入塔混合气中氨含量为5.5%(质量分数,下同),吸收后出塔气体中氨含量为0.17%,试计算进、出塔气体中氨的摩尔比Y 1、Y 2。

解:先计算进、出塔气体中氨的摩尔分数1y 和2y 。

0903.029/945.017/055.017/055.01=+=y0029.029/9983.017/0017.017/0017.02=+=y进、出塔气体中氨的摩尔比1Y 、2Y 为10.09030.099310.0903Y ==-0029.00029.010029.02=-=Y气液相平衡【5-2】 某系统温度为10℃,总压101.3kPa ,试求此条件下在与空气充分接触后的水中,每立方米水溶解了多少克氧气?(已知10℃时,氧气在水中的亨利系数E 为3.31×106kPa 。

)解:由于ssEM Hρ≈,所以34-6A A m /kmol 1057.3181031.327.211000⨯=⨯⨯⨯===*sAs EM p Hp c ρ故 m A =3.57×10-4×32×1000=11.42 g/m 3【5-3】 在温度为40 ℃、压力为101.3 kPa 的条件下,测得溶液上方氨的平衡分压为15.0 kPa 时,氨在水中的溶解度为76.6 g (NH 3)/1 000 g(H 2O)。

试求在此温度和压力下的亨利系数E 、相平衡常数m 及溶解度系数H 。

解:水溶液中氨的摩尔分数为76.6170.07576.610001718x ==+ 由*p Ex =亨利系数为*15.0kPa 200.00.075p E x ===kPa相平衡常数为t 200.0 1.974101.3E m p === 由于氨水的浓度较低,溶液的密度可按纯水的密度计算。

第5章课后习题参考答案

printf("一行字符中字母#和a出现的次数分别是%d,%d\n ",num1,num2);

}

6、从键盘输入一个正整数,统计该数的位数,如输入1234,输出4,输入0,输出1

#include<stdio.h>

void main()

{

int n,m,num=0;

printf("请输入一个正整数n:");

}

ave=sum/num2;

printf("负数个数num1=%d,正数的平均值ave=%.2f\n",num1,ave);

}

2、sum=2+5+8+11+14+…,输入正整数n,求sum的前n项和。

#include<stdio.h>

void main()

{

int i,n,sum=0;

#include<stdio.h>

void main()

{

char ch;

int num1=0,num2=0;

printf("请输入一行字符:\n");

while((ch=getchar())!='\n')

{

if(ch=='#') num1++;

if(ch=='a') num2++;

#include<stdio.h>

void main()

{

int x,y,z,num=0;

for(x=1;x<=9;x++)

第五章旋光异构(有机化学课后习题答案)

内消旋体: Ⅰ Ⅱ

有手性C

五、一个旋光的醇C5H10O(A),催化加氢后得到一个无

旋光的醇C5H12O(B)。试写出(A)和(B)的结构式。

A:

H

CH

OH

CH2

C OH

C2H5

B: CH3CH2CHC2H5

不饱和度= 1

C H C 2H 5

2 . B rC H 2 C H D C H 2 C l

COOH

3.

CHCl COOH

4.

OH

5.

Br

二、用R、S标出下列化合物中手性碳原子的构型式:

c CH 3

1.

H

b

aB r

2 .

H

a COOH c CH3

b

c

CHO 3. CH3

a

b

COOH

Cl

C H 2C H 3

CH2CH=CH2 H

③ (2R,3R)-2,3-二溴丁酸

COOH Br H Br CH3 H Br

*④ (4S,2E)-4-甲基-2-己烯

H

C C

CH3 H H

CH3 C2H5

四.指出下列说法正确与否(正确的用“√”表示,不正确的

用“×”表示)。

(1) 顺式异构体都是Z型的,反式异构体都是E型的。(× )

第五章旋光异构基础知识部分一下列化合物中有无手性c用表示手性cch3chchchch3ch?chc2h51brch2chdch2cl2coohchclcoohohbr3

第五章

旋光异构

基础知识部分 一、下列化合物中有无手性C(用*表示手性C)

1. C H 3C H C H C H ( C H 3 )C H

第5章课后习题参考答案

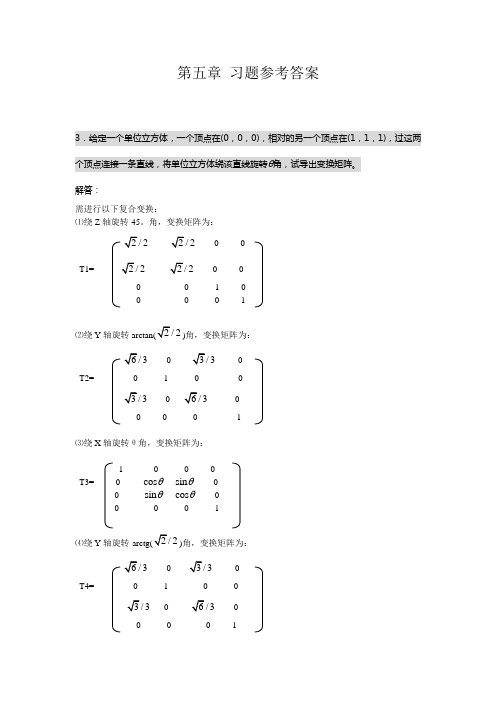

第五章习题参考答案3.给定一个单位立方体,一个顶点在(0,0,0),相对的另一个顶点在(1,1,1),过这两个顶点连接一条直线,将单位立方体绕该直线旋转θ角,试导出变换矩阵。

解答:需进行以下复合变换:⑴绕Z轴旋转-45。

角,变换矩阵为:/220 0T1= 2/20 00 1 00 0 1⑵绕Y轴旋转2)角,变换矩阵为:/30 30T2= 0 1 0 030 300 0 0 1⑶绕X轴旋转θ角,变换矩阵为:1 0 0 0T3= 0 cosθs i nθ00 -sinθc o sθ00 0 0 1⑷绕Y轴旋转2)角,变换矩阵为:/30 30T4= 0 1 0 030 300 0 0 1⑸绕Z 轴旋转45。

角,变换矩阵为:/2/20 0 T5= 2/20 0 0 0 1 00 0 0 1 故最后的变换矩阵为: T=T1T2T3T4T5=1/32/3cos θ+ 1/3/3s i n1/3c o s θθ+- 1/3/3s i n 1/3c o s θθ-- 0 1/33sin 1/3cos θθ-- 1/32/3c o s θ+ 1/3/3s i n1/3c o s θθ+- 01/33sin 1/3cos θθ+- 1/3/3s i n1/3c o s θθ-- 1/32/3c o s θ+ 00 0 0 1 6.编程绘制第5题中三棱锥的正等轴测和正二测图。

同上类似,只是变换矩阵改为T 正等=0.70700.40800.70700.4080000.816001-⎡⎤⎢⎥--⎢⎥⎢⎥⎢⎥⎣⎦和T 正二=⎥⎥⎥⎥⎦⎤⎢⎢⎢⎢⎣⎡---1000943.0000312.00354.00118.00935.07.编程绘制第5题中三棱锥的斜等测和斜二测投影图。

同上类似,变换矩阵改为:T 斜等=⎥⎥⎥⎥⎦⎤⎢⎢⎢⎢⎣⎡-1001000707.00707.00001T斜二=⎥⎥⎥⎥⎦⎤⎢⎢⎢⎢⎣⎡-1001000354.00354.000018.编程绘制第5题中三棱锥的立体一点、二点和三点透视图。

大学物理课后习题答案第五章

第五章机械波5.1 已知一波的波动方程为y = 5×10-2sin(10πt – 0.6x ) (m). (1)求波长、频率、波速及传播方向;(2)说明x = 0时波动方程的意义,并作图表示. [解答](1)与标准波动方程比较得:2π/λ= 0.6, 因此波长为:λ = 10.47(m);圆频率为:ω = 10π, 频率为:v =ω/2π = 5(Hz);波速为:u = λ/T = λv = 52.36(m·s -1).且传播方向为x 轴正方向.(2)当x = 0时波动方程就成为该处质点的振动方程: y = 5×10-2sin10πt = 5×10-2cos(10πt – π/2), 振动曲线如图.5.2 一平面简谐波在媒质中以速度为u = 0.2m·s -1沿x 轴正向传播,已知波线上A 点(x A = 0.05m )的振动方程为(m).试求:(1)简谐波的波动方程;(2)x= -0.05m 处质点P 处的振动方程.[解答](1)简谐波的波动方程为:; 即= 0.03cos[4π(t – 5x ) + π/2]. (2)在x = -0.05m 处质点P 点的振动方程为:y = 0.03cos[4πt + π + π/2]= 0.03cos(4πt - π/2).5.3已知平面波波源的振动表达式为(m).求距波源5m 处质点的振动方程和该质点与波源的位相差.设波速为2m·s -1.[解答]振动方程为:, 位相差为 Δφ = 5π/4(rad).5.4有一沿x 轴正向传播的平面波,其波速为u = 1m·s -1,波长λ = 0.04m ,振幅A = 0.03m .若以坐标原点恰在平衡位置而向负方向运动时作为开始时刻,试求:(1)此平面波的波动方程;(2)与波源相距x = 0.01m 处质点的振动方程,该点初相是多少? [解答](1)设原点的振动方程为:y 0 = A cos(ωt + φ),其中A = 0.03m .由于u = λ/T ,所以质点振动的周期为:T = λ/u = 0.04(s),圆频率为:ω = 2π/T = 50π. 当t = 0时,y 0 = 0,因此cos φ = 0;由于质点速度小于零,所以φ = π/2. 原点的振动方程为:y 0 = 0.03cos(50πt + π/2), 平面波的波动方程为:= 0.03cos[50π(t – x ) + π/2).(2)与波源相距x = 0.01m 处质点的振动方程为:y = 0.03cos50πt . 该点初相φ = 0.5.5一列简谐波沿x 轴正向传播,在t 1 = 0s ,t 2 = 0.25s 时刻的波形如图所示.试求: (1)P 点的振动表达式;2cos()xy A t πωλ=-0.03cos(4)2A y t ππ=-cos[()]Ax x y A t uωϕ-=-+0.050.03cos[4()]0.22x y t ππ-=--20 6.010sin2y t π-=⨯26.010sin()2xy t u π-=⨯-50.06sin()24t ππ=-0.03cos[50()]2x y t u ππ=-+(2)波动方程; (3)画出O 点的振动曲线.[解答](1)设P 点的振动方程为y P = A cos(ωt + φ), 其中A = 0.2m .在Δt = 0.25s 内,波向右传播了Δx = 0.45/3 = 0.15(m),所以波速为u = Δx/Δt = 0.6(m·s -1).波长为:λ = 4Δx = 0.6(m), 周期为:T = λ/u = 1(s), 圆频率为:ω = 2π/T = 2π.当t = 0时,y P = 0,因此cos φ = 0;由于波沿x 轴正向传播,所以P 点在此时向上运动,速度大于零,所以φ = -π/2.P 点的振动表达式为:y P = 0.2cos(2πt - π/2). (2)P 点的位置是x P = 0.3m ,所以波动方程为. (3)在x = 0处的振动方程为y 0 = 0.2cos(2πt + π/2),曲线如图所示.5.6 如图所示为一列沿x 负向传播的平面谐波在t = T /4时的波形图,振幅A 、波长λ以及周期T 均已知.(1)写出该波的波动方程;(2)画出x = λ/2处质点的振动曲线;(3)图中波线上a 和b 两点的位相差φa – φb 为多少?[解答](1)设此波的波动方程为: ,当t = T /4时的波形方程为:. 在x = 0处y = 0,因此得sin φ = 0,解得φ = 0或π.而在x = λ/2处y = -A ,所以φ = 0. 因此波动方程为:. (2)在x = λ/2处质点的振动方程为:, 曲线如图所示.(3)x a = λ/4处的质点的振动方程为; x b = λ处的质点的振动方程为.波线上a 和b 两点的位相差φa – φb = -3π/2.0.2cos[2()]2P x x y t u ππ-=--100.2cos(2)32t x πππ=-+cos[2()]t xy A T πϕλ=++cos(2)2xy A ππϕλ=++sin(2)xA πϕλ=-+cos 2()t x y A T πλ=+cos(2)cos 2t t y A A T Tπππ=+=-cos(2)2a t y A T ππ=+cos(22)b ty A Tππ=+图5.55.7 已知波的波动方程为y = A cosπ(4t – 2x )(SI ).(1)写出t = 4.2s 时各波峰位置的坐标表示式,并计算此时离原点最近的波峰的位置,该波峰何时通过原点?(2)画出t = 4.2s 时的波形曲线.[解答]波的波动方程可化为:y = A cos2π(2t – x ),与标准方程比较,可知:周期为T = 0.5s ,波长λ = 1m .波速为u = λ/T = 2m·s -1. (1)当t = 4.2s 时的波形方程为 y = A cos(2πx – 16.8π)= A cos(2πx – 0.8π). 令y = A ,则cos(2πx – 0.8π) = 1,因此 2πx – 0.8π = 2k π,(k = 0, ±1, ±2,…), 各波峰的位置为x = k + 0.4,(k = 0, ±1, ±2,…).当k = 0时的波峰离原点最近,最近为:x = 0.4(m).通过原点时经过的时间为:Δt = Δx/u = (0 – x )/u = -0.2(s), 即:该波峰0.2s 之前通过了原点.(2)t = 0时刻的波形曲线如实线所示.经过t = 4s 时,也就是经过8个周期,波形曲线是重合的;再经Δt = 0.2s ,波形向右移动Δx = u Δt = 0.4m ,因此t = 4.2s 时的波形曲线如虚线所示.[注意]各波峰的位置也可以由cos(2πx – 16.8π) = 1解得,结果为x = k + 8.4,(k = 0, ±1, ±2,…),取同一整数k 值,波峰的位置不同.当k = -8时的波峰离原点最近,最近为x = 0.4m .5.8一简谐波沿x 轴正向传播,波长λ = 4m ,周期T = 4s ,已知x = 0处的质点的振动曲线如图所示. (1)写出时x = 0处质点的振动方程;(2)写出波的表达式;(3)画出t = 1s 时刻的波形曲线.[解答]波速为u = λ/T = 1(m·s -1).(1)设x = 0处的质点的振动方程为y = A cos(ωt + φ), 其中A = 1m ,ω = 2π/T = π/2.当t = 0时,y = 0.5,因此cos φ = 0.5,φ = ±π/3.在0时刻的曲线上作一切线,可知该时刻的速度小于零,因此φ = π/3.振动方程为:y = cos(πt /2 + π/3).(2)波的表达式为:.(3)t = 1s 时刻的波形方程为,波形曲线如图所示.5.9在波的传播路程上有A 和B 两点,都做简谐振动,B 点的位相比A 点落后π/6,已知A 和B 之间的距离为2.0cm ,振动周期为2.0s .求波速u 和波长λ.cos[2()]t x y A T πϕλ=-+cos[2()]t xy A T πϕλ=-+cos[()]23t x ππ=-+5cos()26y x ππ=-图5.8[解答]设波动方程为:, 那么A 和B 两点的振动方程分别为:, . 两点之间的位相差为:,由于x B – x A = 0.02m ,所以波长为:λ = 0.24(m).波速为:u = λ/T = 0.12(m·s -1). 5.10 一平面波在介质中以速度u = 20m·s -1沿x 轴负方向传播.已知在传播路径上的某点A 的振动方程为y = 3cos4πt .(1)如以A 点为坐标原点,写出波动方程;(2)如以距A 点5m 处的B 点为坐标原点,写出波动方程; (3)写出传播方向上B ,C ,D 点的振动方程. [解答](1)以A 点为坐标原点,波动方程为 .(2)以B 点为坐标原点,波动方程为. (3)以A 点为坐标原点,则x B = -5m 、x C = -13m 、x D = 9m ,各点的振动方程为, ,.[注意]以B 点为坐标原点,求出各点坐标,也能求出各点的振动方程.5.11 一弹性波在媒质中传播的速度u = 1×103m·s -1,振幅A = 1.0×10-4m ,频率ν= 103Hz .若该媒质的密度为800kg·m -3,求:(1)该波的平均能流密度;(2)1分钟内垂直通过面积S = 4×10-4m 2的总能量. [解答](1)质点的圆频率为:ω = 2πv = 6.283×103(rad·s -1), 波的平均能量密度为:= 158(J·m -3), 平均能流密度为:= 1.58×105(W·m -2).(2)1分钟内垂直通过面积S = 4×10-4m 2的总能量为:E = ItS = 3.79×103(J).5.12一平面简谐声波在空气中传播,波速u = 340m·s -1,频率为500Hz .到达人耳时,振幅A = 1×10-4cm ,试求人耳接收到声波的平均能量密度和声强?此时声强相当于多少分贝?已知空气密度ρ = 1.29kg·m -3.[解答]质点的圆频率为:ω = 2πv = 3.142×103(rad·s -1), 声波的平均能量密度为:= 6.37×10-6(J·m -3), cos[2()]t xy A T πϕλ=-+cos[2()]AA x ty A T πϕλ=-+cos[2()]BB x ty A Tπϕλ=-+2(2)6BAx x πππλλ---=-3cos 4()3cos(4)5x x y t t u πππ=+=+3cos 4()Ax x y t u π-=+3cos(4)5x t πππ=+-3cos 4()3cos(4)BB x y t t u πππ=+=-33cos 4()3cos(4)5C C x y t t u πππ=+=-93cos 4()3cos(4)5D D x y t t u πππ=+=+2212w A ρω=I wu =2212w A ρω=图5.10平均能流密度为:= 2.16×10-3(W·m -2), 标准声强为:I 0 = 1×10-12(W·m -2), 此声强的分贝数为:= 93.4(dB).5.13 设空气中声速为330m·s -1.一列火车以30m·s -1的速度行驶,机车上汽笛的频率为600Hz .一静止的观察者在机车的正前方和机车驶过其身后所听到的频率分别是多少?如果观察者以速度10m·s -1与这列火车相向运动,在上述两个位置,他听到的声音频率分别是多少?[解答]取声速的方向为正,多谱勒频率公式可统一表示为, 其中v S 表示声源的频率,u 表示声速,u B 表示观察者的速度,u S 表示声源的速度,v B 表示观察者接收的频率.(1)当观察者静止时,u B = 0,火车驶来时其速度方向与声速方向相同,u S = 30m·s -1,观察者听到的频率为= 660(Hz). 火车驶去时其速度方向与声速方向相反,u S = -30m·s -1,观察者听到的频率为= 550(Hz). (2)当观察者与火车靠近时,观察者的速度方向与声速相反,u B = -10m·s -1;火车速度方向与声速方向相同,u S = 30m·s -1,观察者听到的频率为= 680(Hz). 当观察者与火车远离时,观察者的速度方向与声速相同,u B = 10m·s -1;火车速度方向与声速方向相反,u S = -30m·s -1,观察者听到的频率为= 533(Hz). [注意]这类题目涉及声速、声源的速度和观察者的速度,规定方向之后将公式统一起来,很容易判别速度方向,给计算带来了方便.5.14.一声源的频率为1080Hz ,相对地面以30m·s -1速率向右运动.在其右方有一反射面相对地面以65m·s -1的速率向左运动.设空气中声速为331m·s -1.求:(1)声源在空气中发出的声音的波长; (2)反射回的声音的频率和波长.[解答](1)声音在声源垂直方向的波长为:λ0 = uT 0 = u /ν0 = 331/1080 = 0.306(m); 在声源前方的波长为:λ1 = λ0 - u s T 0 = uT 0 - u s T 0 = (u - u s )/ν0 = (331-30)/1080 = 0.2787(m); 在声源后方的波长为:λ2 = λ0 + u s T 0 = uT 0 + u s T 0 = (u + u s )/ν0= (331+30)/1080 = 0.3343(m).(2)反射面接收到的频率为 = 1421(Hz).将反射面作为波源,其频率为ν1,反射声音的频率为= 1768(Hz).I wu =010lgIL I =BB S Su u u u νν-=-33060033030B S S u u u νν==--33060033030B S S u u u νν==-+3301060033030B B S S u u u u νν-+==--3301060033030B B S S u u u u νν--==-+1033165108033130B Su u u u νν++==⨯--`11331142133165B u u u νν==⨯--反射声音的波长为=0.1872(m).或者= 0.1872(m). [注意]如果用下式计算波长=0.2330(m), 结果就是错误的.当反射面不动时,作为波源发出的波长为u /ν1 = 0.2330m ,而不是入射的波长λ1.5.15S 1与S 2为两相干波源,相距1/4个波长,S 1比S 2的位相超前π/2.问S 1、S 2连线上在S 1外侧各点的合成波的振幅如何?在S 2外侧各点的振幅如何?[解答]如图所示,设S 1在其左侧产生的波的波动方程为,那么S 2在S 1左侧产生的波的波动方程为,由于两波源在任意点x 产生振动反相,所以合振幅为零.S 1在S 2右侧产生的波的波动方程为,那么S 2在其右侧产生的波的波动方程为,由于两波源在任意点x 产生振动同相,所以合振幅为单一振动的两倍.5.16两相干波源S 1与S 2相距5m ,其振幅相等,频率都是100Hz ,位相差为π;波在媒质中的传播速度为400m·s -1,试以S 1S 2连线为坐标轴x ,以S 1S 2连线中点为原点,求S 1S 2间因干涉而静止的各点的坐标.[解答]如图所示,设S 1在其右侧产生的波的波动方程为 ,那么S 2在其左侧产生的波的波动方程为. 两个振动的相差为Δφ = πx + π,当Δφ = (2k + 1)π时,质点由于两波干涉而静止,静止点为x = 2k , k 为整数,但必须使x 的值在-l /2到l /2之间,即-2.5到2.5之间.当k = -1、0和1时,可得静止点的坐标为:x = -2、0和2(m).5.17设入射波的表达式为,`1111331651421BBu u u uλννν--=-==`1`13311768uλν==`111650.27871768Bu λλν=-=-1cos[2()]t xy A T πϕλ=++2/4cos[2()]2t x y A T λππϕλ-=++-cos[2()]t xA T πϕπλ=++-1cos[2()]t xy A T πϕλ=-+2/4cos[2()]2t x y A T λππϕλ-=-+-cos[2()]t xA T πϕλ=-+1/2cos[2()]x l y A t u πνϕ+=-+5cos(2)24A t x πππνϕ=-+-2/2cos[2()]x l y A t u πνϕπ-=+++cos(2)24A t x πππνϕ=++-1cos 2()t xy A T πλ=+S 1 S 2S 12在x = 0处发生反射,反射点为一自由端,求:(1)反射波的表达式; (2)合成驻波的表达式.[解答](1)由于反射点为自由端,所以没有半波损失,反射波的波动方程为.(2)合成波为y = y 1 + y 2,将三角函数展开得,这是驻波的方程.5.18两波在一很长的弦线上传播,设其表达式为:,,用厘米、克、秒(cm,g,s )制单位,求:(1)各波的频率,波长、波速;(2)节点的位置;(3)在哪些位置上,振幅最大?[解答](1)两波可表示为:,, 可知它们的周期都为:T = 0.5(s),频率为:v = 1/T = 2(Hz);波长为:λ = 200(cm);波速为:u = λ/T = 400(cm·s -1).(2)位相差Δφ = πx /50,当Δφ = (2k + 1)π时,可得节点的位置x = 50(2k + 1)(cm),(k = 0,1,2,…).(3)当Δφ = 2k π时,可得波腹的位置x = 100k (cm),(k = 0,1,2,…).2cos 2()t xy A T πλ=-222coscosy A x t Tππλ=1 6.0cos(0.028.0)2y x t π=-2 6.0cos(0.028.0)2y x t π=+1 6.0cos 2()0.5200t x y π=-2 6.0cos 2()0.5200t x y π=+。

结构力学课后答案第五章习题答案

5-1 试回答:用单位荷载法计算结构位移时有何前提条件?单位荷载法是否可用于超静定结构的位移计算?aaaaa NCD NCE NBE NAD NBC NAC DE F F 0, F F F F F A B P P P PR R F F F =========-由对称性分析知道N NP 12()F F 1()2 6.832222()P P P cx P F a l F a F a EA EA EA EA EA ⨯⨯-⨯-⨯∆==⨯+⨯+=↓∑5-4 已知桁架各杆截面相同,横截面面积A =30cm 2,E =20.6×106N/cm 2,F P =98.1kN 。

试求C 点竖向位移yC Δ。

25544P P P P F F F ===NAD NAE NEC NEF 由节点法知:对A 节点 F F 对E 节点 F F115(122516(()4)4 11.46 ()N NP yc P P P F F l F F EA EA cm =∆==⨯⨯⨯+⨯⨯+⨯⨯=↓∑NAD NAE 由节点法知:对A 节点 F F5-5 已知桁架各杆的EA 相同,求AB 、BC 两杆之间的相对转角B Δθ。

杆的内力计算如图所示施加单位力在静定结构上。

其受力如图11(12N NP BF F l EA EAθ∆==-∑5-6 试用积分法计算图示结构的位移:(a )yB Δ;(b )yC Δ;(c )B θ;(d )xB Δ。

(a)211232113421yc 1004142B ()1()26()111 ()()()26111 =()30120p llp q q q x x q l q qM x q x x lM x x q q M x M x dx q x x dx EI EI l q l q l EI -=+-=+=-∴∆=⨯=++⎰⎰以点为原点,向左为正方向建立坐标。

显然,A Bq 2q 1lEI22q l 254q l PM l74l M2224113153251315127()()324244342243416yc ql q l l ql l ql l l l l l ql EI EI ∆=⨯⨯+⨯⨯+⨯⨯+⨯⨯+⨯⨯=↓(c)22201()(sin )12(1cos )2()1111[(sin )12(1cos)]2(8-3)-1.42=()EI EIB M R R M R R Rd EIπϕϕϕϕθϕϕϕπ=⨯-⨯-==⨯⨯-⨯-=⎰逆时针l3l 4ABCql EI=常数OAB1kN/m2kNR =2m4mϕθqds qRd θ=20()sin()(1cos )M qRd R qR ϕϕθϕθϕ=⨯-=-⎰2240()sin 111()()(1cos )sin ()2xBM R M M ds qR R Rd qR EI EI EIπϕϕϕϕϕϕϕ=∆==-=←⎰⎰5-7 试用图乘法计算图示梁和刚架的位移:(a )yC Δ;(b )yD Δ;(c )xC Δ;(d )xE Δ;(e )D θ;(f )yE Δ。

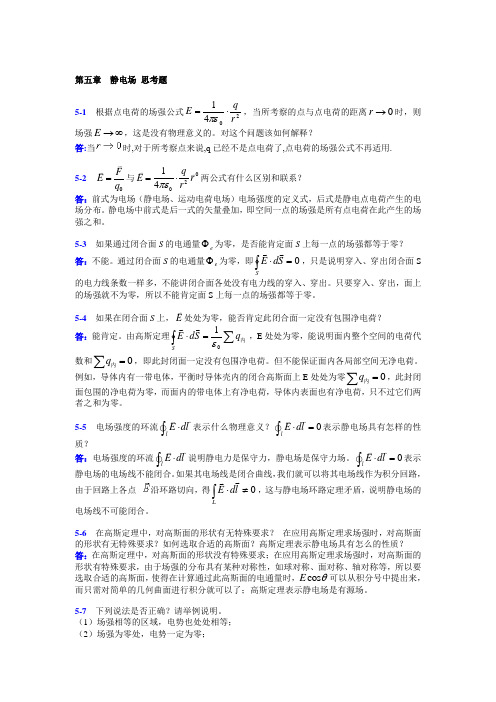

基础物理学第五章(静电场)课后习题答案

第五章 静电场 思考题5-1 根据点电荷的场强公式2041rqE ⋅=πε,当所考察的点与点电荷的距离0→r 时,则场强∞→E ,这是没有物理意义的。

对这个问题该如何解释? 答:当时,对于所考察点来说,q 已经不是点电荷了,点电荷的场强公式不再适用.5-2 0FE q =与02014q E r r πε=⋅两公式有什么区别和联系? 答:前式为电场(静电场、运动电荷电场)电场强度的定义式,后式是静电点电荷产生的电场分布。

静电场中前式是后一式的矢量叠加,即空间一点的场强是所有点电荷在此产生的场强之和。

5-3 如果通过闭合面S 的电通量e Φ为零,是否能肯定面S 上每一点的场强都等于零?答:不能。

通过闭合面S 的电通量e Φ为零,即0=⋅⎰SS d E,只是说明穿入、穿出闭合面S的电力线条数一样多,不能讲闭合面各处没有电力线的穿入、穿出。

只要穿入、穿出,面上的场强就不为零,所以不能肯定面S 上每一点的场强都等于零。

5-4 如果在闭合面S 上,E 处处为零,能否肯定此闭合面一定没有包围净电荷? 答:能肯定。

由高斯定理∑⎰=⋅内qS d E S1ε,E 处处为零,能说明面内整个空间的电荷代数和0=∑内q,即此封闭面一定没有包围净电荷。

但不能保证面内各局部空间无净电荷。

例如,导体内有一带电体,平衡时导体壳内的闭合高斯面上E 处处为零0=∑内q,此封闭面包围的净电荷为零,而面内的带电体上有净电荷,导体内表面也有净电荷,只不过它们两者之和为零。

5-5 电场强度的环流lE dl ⋅⎰表示什么物理意义?0lE dl⋅=⎰表示静电场具有怎样的性质?答:电场强度的环流lE dl ⋅⎰说明静电力是保守力,静电场是保守力场。

0lE dl⋅=⎰表示静电场的电场线不能闭合。

如果其电场线是闭合曲线,我们就可以将其电场线作为积分回路,由于回路上各点沿环路切向,得⎰≠⋅Ll d E 0,这与静电场环路定理矛盾,说明静电场的电场线不可能闭合。

《统计学概论》第五章课后练习题答案

《统计学概论》第五章课后练习题答案一、思考题1.什么叫时间序列,构成时间序列的基本要素有哪些?P1212.序时平均数与一般平均数有何异同?P1273.时间数列与时点数列有哪些区别?P124-1254.环比增长速度与定基增长速度之间有什么关系?P1365.什么是平均发展速度?说说水平法和累计法计算平均发展速度的基本思路,各在什么情况下选用?P1386.测定长期趋势有哪些常用的方法?测定的目的是什么?P1367.实际中如何根据时间序列的发展变化的数列特征来判断合适的趋势方程形式?P1458.影响时间序列指标数值大小的因素有哪些?这些因素共同作用的理论模型有哪些?P140二、判断题1.时间序列也称动态数列,它是变量数列的一种形式。

(×)【解析】时间序列是数列,而变量数列是静态数列。

2.时间数列和时点数列属于总量指标时间序列。

(√)3.所谓序时平均数是指将同一总体的不同时期的平均数按时间先后顺序排列起来。

(×)【解析】序时平均数是将不同时期的发展水平加以平均而得到的平均数。

4.间隔相等的时期数列计算平均发展水平时,应用首末折半法。

(×)【解析】间隔相等的时点数列计算平均发展水平时,应用首末折半法。

5.平均增长速度等于各期环比增长速度连乘积开n次方。

(×)【解析】平均发展速度等于各期环比发展速度连乘积开n次方,平均增长速度=平均发展速度-1(或100%)6.两个相邻时期的定基发展速度之比等于相应的环比发展速度。

(√)7.用移动平均法测定长期趋势时,移动平均项数越多越好。

(×)【解析】移动平均法所取项数的多少,应视资料的特点而定。

8.某一时间序列有25年的数据,若采用五项移动平均,则修匀后的数列缺少4项数据。

(√)9.如果时间序列是年度数据,则不存在季节变动。

(√)10.用相同方法拟合趋势方程时,t的取值不同,则得到的趋势方程也不同,但趋势预测值不变。

(√)三、单项选择题1.时间序列的构成要素是()。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

第5章习题解答

5-1由与非门组成的基本RS触发器的R d,S d之间为什么要有约束?当违反约束条件时,输出端Q、Q会出现什么情况?试举例说明。

解:由与非门组成的基本RS触发器的R d和S d之间的约束条件是:不允许R d和S d同时为0。

当违反约束条件即当R d=S d=0时,Q、Q端将同时为1,作为基本存储单元来说,这既不是0状态,又不是1状态,没有意义。

5-2试列出或非门组成的基本RS触发器的真值表,它的输入端R d和S d之间是否也要有约束?为什么?

解:真值表如右表所示、

Rd、Sd之同也要有约束条件,即不允许Rd=Sd=1,

否则Q、Q端会同时出现低电平。

5-3画出图5-33由与非门组成的基本RS触发器输出端Q、Q的电压波形,输入端R D、S的电压波形如图中所示。

D

图5-33

解:见下图:

5-4画出图5-34由或非门组成的基本RS触发器输出端Q、Q的电压波形,输入端S D、R D的电压波形如图中所示。

图5-34

解:见下图:

5-5图5-35所示为一个防抖动输出的开关电路。

当拨动开关S时,由于开关触点接通瞬间发生振颤,R D、S D的电压波形如图中所示。

试画出Q、Q端对应的电压波形。

图5-35

解:见下图:

5-6在图5-36电路中、若CP、S、R的电压波形如图中所示,试画出Q、Q端与之对

应的电压波形。

假定触发器的初始状态为Q=0。

图5-36

解:见下图:

5-7在图5-37(a)所示的主从RS触发器中,CP、R、S的波形如图5-37(b)所示,试画出相应的Q m、Q m、Q和Q的波形图。

图5-37

解:主从RS触发器的工作过程是:在CP=l期间主触发器接收输入信号,但输出端并不改变状态,只有当CP下降沿到来时从触发器甚才翻转,称为下降沿触发。

根据主从RS 触发器状态转换图可画出波形图如下图所示。

5-8在图5-38(a)所示的主从JK触发器中,CP、J、K的波形如图5-38(b)所示,试画出相应的Q m、Q m、Q和Q的波形图。

图5-38

解:主从JK触发翻的工作过程是上升沿接收,下降沿翻转。

根据状态转换图可画出波形图如下图所示。

5-9TTL主从触发器的输入端J、K、R d、S d及CP的波形图如图5-39所示,试画出

输出端Q的波形图。

图5-39

解:根据输入信号画主从JK触发器的输出端波形时,需考虑如下三点:第一,在CP 信号下降沿到来时状态更新;第二,在CP上升沿及CP=1期间,J、K信号如有变化,应考虑一次变化问题;第三,R和S

d为直接复位端、置位端。

只要有低电平作用,可以直接

将

d

触发器复位或置位,不受CP信号到来与否的限制。

输出端Q波形图如下图所示。

5-10边沿触发型JK触发器及其输入端信号CP、J、K的波形如图5-40所示,设触发器的初始状态为0,试画出Q、Q的波形图.

图5-40

解:见下图:

5-11维持阻塞D触发器及其CP、D输入端的波形图如图5-41所示,设触发器的初始状态为0,试画出Q和Q的波形图。

图5-41

解:见下图:

5-12已知CMOS边沿触发结构JK触发器各输入端的电压波形如图5-42所示。

试画出Q、Q端对应的电压波形。

图5-42

解:见下图:

5-13设图5-43中各触发器的初始状态皆为Q=0,试画出在CP信号连续作用下各触发器输出端的电压波形。

图5-43

解:见下图:

5-14图5-44(a)所示各触发器均为边沿触发器,其CP及A、B、C的波形图如图5-44(b) 所所示,试写出各触发器次态Q n+1的逻辑表达式,设各触发器的初态均为0,要求画出Q

端的工作时序图。

图5-44

解:见下图:

5-15图5-45(a)中FF1、FF2是CMOS边沿触发器,FF3、FF4是TTL边沿触发器。

CP

及其A、B、C输入端的波形用如图5-45(b)所示。

设各触发器的初态均为0。

试画出各触发器输出端Q的波形图。

图5-45

解:见下图:

5-16在图5-46(a)所示的T触发器电路中,已知CP和输入端T的波形如图5-46(b)所示,设初始状态为0,试画Q和Q的波形图。

图5-46

解:见下图:

nQ n

5-17如图5-47(a)所示电路,设初始状态Q120,CP、A端的输入波形如图5-47(b) 所示,试画出Q1和Q2的波形图。

图5-47

解:见下图:

F1:CP1=A,

J=K=1

n

n1

QQ

11

nRQ

2

F2:CP2=CP,

n

JQ,K=1

1

n

n1n

QQQ

212

nQ n

5-18如图5-48(a)所示电路,设初始状态Q121,其输入端D、R d及CP的波形

图如图5-48(b)所示,试分别画出nQ n1

1

Q和的波形图。

12

图5-48

解:见下图:

F1:

n1 QD

1

n

JQ,K=1F2:1

n

n1n

QQQ

212

5-19如图5-49(a)所示电路。

其输入端CP和A的波形图如图5-49(b)所示,设触发nQ n

器的初始状态Q0,试画出电路输出端F1,F2的波形图。

12

图5-49

解:见下图:

n1

QA

1

n1n

QQ

21

n

n

FQQ

112

n

n

FQQ

212

5-20在图5-50(a)所示电路中,CP和J的波形图如图5-50(b)所示,设触发器的初始状态为0,试画出Q和R的波形图。

图5-50

解:见下图:

5-21图5-51所示是用CMOS边沿触发器和异或门组成的脉冲分路电路。

试画出在—系列CP脉冲作用下Q1、Q2和Z端对应的输出电压波形。

设触发器的初始状态皆为Q=0。

图5-51

解:见下图:。