stm32f407数据手册中文

stm32f407数据手册中文

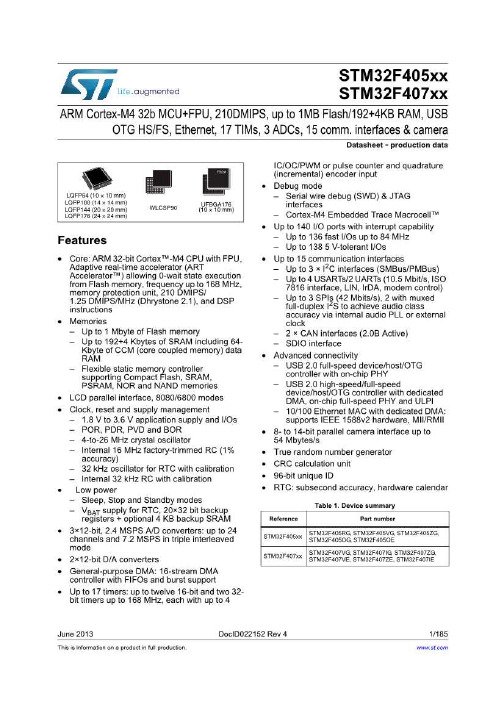

stm32f407数据手册中文STM32F4是由ST(意法半导体)开发的一种高性能微控制器。

其采用了90纳米的NVM工艺和ART(自适应实时存储器加速器,Adaptive Real-Time MemoryAccelerator T,,)o简介:ST(意法半导体)推出了以基于ARM® Cortex™-M4为内核的STM32F4系列高性能微控制器,其采用了90纳米的NVM工艺和ART(自适应实时存储器加速器,Adaptive Real-Time MemoryAccelerator™)oART技术使得程序零等待执行,提升了程序执行的效率,将Cortext-M4的性能发挥到了极致,使得STM32 F4 系列可达到210DMIPS@168MHz o自适应实时加速器能够完全释放Cortex-M4内核的性能;当CPU 工作于所有允许的频率仁168MHz)时,在闪存中运行的程序,可以达到相当于零等待周期的性能。

STM32F4系列微控制器集成了单周期DSP指令和FPU(floating point unit,浮点单元),提升了计算能力,可以进行一些复杂的计算和控制。

STM32 F4系列引脚和软件兼容于当前的STM32 F2系列产品。

优点兼容于STM32F2系列产品,便于ST的用户扩展或升级产品,而保持硬件的兼容能力。

集成了新的DSP和FPU指令,168MHz的高速性能使得数字信号控制器应用和快速的产品开发达到了新的水平。

提升控制算法的执行速度和代码效率。

先进技术和工艺・存储器加速器:自适应实时加速器(ART Accelerator™ )・多重AHB总线矩阵和多通道DMA:支持程序执行和数据传输并行处理,数据传输速率非常快・90nm工艺咼性能・210DMIPS@168MHz・由于采用了ST的ART加速器,程序从FLASH运行相当于0等待更多的存储器・多达1MB FLASH (将来ST计划推出2MB FLASH的STM32F4) ・192Kb SRAM:128KB在总线矩阵上,64KB在专为CPU使用的数据总线上高级外设与STM32F2兼容・USB OTG 高速480Mbit/s・IEEE1588 ,以太网MAC 10/100・PWM高速定时器:168MHz最大频率・加密/哈希硬件处理器:32位随机数发生器(RNG)・带有日历功能的32位RTC:<1 pA的实时时钟,1秒精度更多的提升・低电压:1.8V到3.6V VDD ,在某些封装上,可降低至1.7V ・全双工I2S・ 12 位ADC:0.41us 转换/2.4Msps(7.2Msps 在交替模式)・高速USART ,可达10.5Mbits/s・高速SPI,可达37.5Mbits/s・Camera接口,可达54M字节/s。

stm32f407zgt6中文资料_数据手册_参数

万联芯城-电子元器件采购网,只售原装正品现货库存,提供一站式电 元器件配套服务,为客户解决采购烦恼,节省采购成本,目前,万联芯 城代理销售长电科技,先科ST,顺络电子等国内一线电子元器件品牌产 品,其余产品均来自原厂及代理商渠道,价格优势明显,采购电子元器 件就上万联芯城。点击进入万联芯城。

其中,高速时钟(HSE和HSI)提供给芯片主体的主时钟.低速时钟(LSE和LSI)只是提供给芯片中的RTC(实时时钟)及独立看门狗使用,图中可以看出高速时钟也可以提供给 RTC。内部时钟是在芯片内部RC振荡器产生的,起振较快,所以时钟在芯片刚上电的时候,默认使用内部高速时钟。而外部时钟信号是由外部的晶振输入的,在精度 和稳定性上都有很大优势,所以上电之后我们再通过软件配置,转而采用外部时钟信号. 高速外部时钟(HSE):以外部晶振作时钟源,晶振频率可取范围为4~16MHz,我们一般采用8MHz的晶振。 OSC_OUT和OSC_IN开始,这两个引脚分别接到外部晶振8MHz,第一个分频器PLLXTPRE,遇到开关PLLSRC(PLL entry clock source),我们可以选择其输出,输出为外部 高速时钟(HSE)或是内部高速时钟(HSI)。这里选择输出为HSE,接着遇到锁相环PLL,具有倍频作用,在这里我们可以输入倍频因子PLLMUL,要是想超频,就得在这 个寄存器上做手脚啦。经过PLL的时钟称为PLLCLK。倍频因子我们设定为9倍频,也就是说,经过PLL之后,我们的时钟从原来8MHz的 HSE变为72MHz的 PLLCLK。STM32F407ZGT6紧接着又遇到了一个开关SW,经过这个开关之后就是STM32的系统时钟(SYSCLK)了。STM32F407ZGT6通过这个开关,可以切换SYSCLK的 时钟源,可以选择为HSI、PLLCLK、HSE。我们选择为PLLCLK时钟,所以SYSCLK就为ቤተ መጻሕፍቲ ባይዱ2MHz了。PLLCLK在输入到SW前,还流向了USB预分频器,这个分频器输出为 USB外设的时钟(USBCLK)。回到SYSCLK,SYSCLK经过AHB预分频器,分频后再输入到其它外设。如输出到称为HCLK、FCLK的时钟,还直接输出到SDIO外设的 SDIOCLK时钟、存储器控制器FSMC的FSMCCLK时钟,和作为APB1、APB2的预分频器的输入端。GPIO外设是挂载在APB2总线上的, APB2的时钟是APB2预分频器的 输出,而APB2预分频器的时钟来源是AHB预分频器。因此,把APB2预分频器设置为不分频,那么我们就可以得到GPIO外设的时钟也等于HCLK,为72MHz了。 SYSCLK:系统时钟,STM32大部分器件的时钟来源。主要由AHB预分频器分配到各个部件。 HCLK:由AHB预分频器直接输出得到,它是高速总线AHB的时钟信号,STM32F407ZGT6提供给存储器,DMA及cortex内核,是cortex内核运行的时钟,cpu主频就是这 个信号,它的大小与STM32运算速度,数据存取速度密切相关。 FCLK:同样由AHB预分频器输出得到,是内核的“自由运行时钟”。“自由”表现在它不来自时钟 HCLK,因此在HCLK时钟停止时 FCLK 也继续运 行。STM32F407ZGT6它的存在,可以保证在处理器休眠时,也能够采样和到中断和跟踪休眠事件 ,它与HCLK互相同步。 PCLK1:外设时钟,由APB1预分频器输出得到,大频率为36MHz,提供给挂载在APB1总线上的外设,APB1总线上的外设如下:

STM32固件库使用手册的中文翻译版

因为该固件库是通用的,并且包括了所有外设的功能,所以应用程序代码的大小和执行速度可能不是最优 的。对大多数应用程序来说,用户可以直接使用之,对于那些在代码大小和执行速度方面有严格要求的应 用程序,该固件库驱动程序可以作为如何设置外设的一份参考资料,根据实际需求对其进行调整。

1.3.1 变量 ................................................................................................................................................ 28 1.3.2 布尔型 ............................................................................................................................................ 28 1.3.3 标志位状态类型 ........................................................................................................................... 29 1.3.4 功能状态类型 .............................................................................................................

STM32F407xx芯片手册第1到3章中文翻译

STM32F407xx芯⽚⼿册第1到3章中⽂翻译1⽂档约定寄存器缩写列表下⾯的缩写⽤于描述寄存器Read/Write(rw)软件可读写Read-Only(r)软件只读Write-only(w)软件只写Read/clear(rc_w1)软件可读,写1清除,写0⽆作⽤Read/clear(rc_w0)软件可读,写0清除,写1⽆作⽤Read/clear by read软件可读,读后⾃动清零,写0⽆作⽤Read/set(rs)软件可读,可置位,写0⽆作⽤Read-only writeTrigger(rt_w)软件可读,写0或1翻转此位Toggle(t)写1翻转,写0⽆作⽤Reserved(Res.)保留位,必须保持复位值2存储器和总线架构2.1系统架构主系统包括32位多层互联AHB总线阵列,连接以下部件:Height masters—Cortex TM-M4F内核I-Bus(指令总线),D-bus(数据总线)和S-bus(系统总线)—DMA1存储器总线—DMA2存储器总线—DMA2外设总线—以太⽹DMA总线—USB OTG HS DMA总线Seven slaves—内置Flash存储器指令总线—内置Flash存储器数据总线—主内置SRAM1(112KB)—辅助内置SRAM2(16KB)—AHB1外设,包括AHB到APB的桥以及APB外设—AHB2外设—FSMC接⼝总线矩阵提供从主设备到从设备的访问,即使在有若⼲⾼速外设同时运⾏的情况下也能并⾏访问并⾼效运转。

这个架构如图1所⽰。

注意:64KB的CCM(内核耦合存储器core coupled memory)数据RAM并不是总线矩阵的⼀部分,它只能通过CPU来访问。

图1系统架构2.1.1S0:指令总线这条总线连接Cortex TM-M4F内核的指令总线到总线矩阵,⽤于内核取指。

总线的Target是存储有代码的存储器(包括内置Flash存储器/SRAM以及通过FSMC外扩的外部存储器)。

stm32f407编程手册

stm32f407编程手册

STM32F407编程手册是一本指导开发者如何使用STM32F407微控制器进行编程的指南。

它通常包含以下内容:

1. 概述:介绍STM32F407微控制器的特点、应用领域、主要功能和性能指标。

2. 开发环境:详细介绍开发STM32F407应用程序所需的软件和工具,包括编译器、调试器、仿真器和开发板等。

3. 硬件接口:介绍STM32F407微控制器的各种硬件接口,如GPIO、UART、SPI、I2C、ADC、DAC等,以及如何配置和使用这些接口。

4. 中断和定时器:介绍STM32F407微控制器的中断和定时器系统,包括NVIC、SysTick、PWM、RTC等,以及如何配置和使用它们。

5. 启动和系统配置:介绍STM32F407微控制器的启动过程和系统配置,包括时钟系统、低功耗模式、内存等。

6. 外设驱动程序示例:提供一些常用的外设驱动程序示例,如LED闪烁、按键输入、串口通信等,以便开发者快速上手。

7. 性能优化:介绍如何优化STM32F407微控制器的性能,包括代码优化、功耗优化等。

8. 常见问题解答:汇总开发者在编程过程中可能遇到的问题,并提供解决方案。

需要注意的是,不同的STM32F407编程手册可能包含的内容有所不同,以上内容仅供参考。

在实际使用过程中,建议根据具体的编程手册和需求进行学习。

stm32f407数据手册中文

stm32f407数据手册中文STMICROELECTRONICS STM32F407VGT6 微控制器, 32位, 以太网MAC, 照相机接口, ARM 皮质-M4, 168 MHzSTM32F407 cortex-m4的高端芯片,常用于嵌入式产品中,内含DSPμC/OS II(Micro-Controller Operating System Two)是一个可以基于ROM运行的、可裁剪的、抢占式、实时多任务内核,具有高度可移植性,特别适合于微处理器和控制器,适合很多商业操作系统性能相当的实时操作系统(RTOS)。

为了提供最好的移植性能,μC/OS II最大程度上使用ANSI C语言进行开发,并且已经移植到近40多种处理器体系上,涵盖了从8位到64位各种CPU(包括DSP)。

μC/OS II可以简单的视为一个多任务调度器,在这个任务调度器之上完善并添加了和多任务操作系统相关的系统服务,如信号量、邮箱等。

其主要特点有公开源代码,代码结构清晰、明了,注释详尽,组织有条理,可移植性好,可裁剪,可固化。

内核属于抢占式,最多可以管理60个任务。

从1992年开始,由于高度可靠性、鲁棒性和安全性,μC/OS II已经广泛使用在从照相机到航空电子产品的各种应用中。

μC/OS-II实时多任务操作系统内核。

它被广泛应用于微处理器、微控制器和数字信号处理器。

μC/OS-II 的前身是μC/OS,最早出自于1992 年美国嵌入式系统专家Jean brosse 在《嵌入式系统编程》杂志的5 月和6 月刊上刊登的文章连载,并把μC/OS 的源码发布在该杂志的B B S 上。

μC/OS-II可以大致分成核心、任务处理、时间处理、任务同步与通信,CPU的移植等5个部分。

1) 核心部分(OSCore.c) 是操作系统的处理核心,包括操作系统初始化、操作系统运行、中断进出的前导、时钟节拍、任务调度、事件处理等多部分。

能够维持系统基本工作的部分都在这里。

stm32f407数据手册中文

STMICROELECTRONICS STM32F407VGT6 微控制器, 32位, 以太网MAC, 照相机接口, ARM 皮质-M4, 168 MHz, 1 MB, 196 KB, 100 引脚, LQFPSTM32F407VGT6基于高性能的ARM Cortex-M4 32位RISC内核, 运行频率高达168MHz. Cortex-M4内核具有一个浮点单元(FPU)单精度, 支持所有ARM单精度数据处理指令和数据类型. 它还执行全套的DSP指令, 并包含一个存储器保护单元, 加强应用的安全性. STM32F407VGT6融合了高速内嵌存储器(闪存存储器高达1Mbyte, 高达192K字节SRAM), 高达4K字节备用SRAM, 以及一个加强范围的输入输出, 外部设备连接至两个APB总线, 三个AHB总线和一个32位多AHB总线矩阵..高达1Mbyte闪存.高达192+4 K字节SRAM, 包括64K字节CCM (核心耦合存储器) 数据RAM.灵活的静态存储器控制器支持紧凑型闪存, SRAM, PSRAM, NOR 和NAND存储器.LCD并行接口, 8080/6800模式.时钟, 复位和电源管理.4MHz至26 MHz晶体振荡器.内部16 MHz工厂调整RC (1%精准度) .32kHz振荡器用于实时时钟, 带校准功能.内部32kHz RC, 带校准.睡眠, 停止和待机模式.VBAT供电实时时钟, 20×32位备用电源.3 ×12位, 2.4MSPS 模数转换器.2 ×12位数模转换器.通用DMA控制器, 支持FIFO和爆破. .多达17个计时器.调试模式.多达140个输入输出端口, 带中断能力.多达136个快速输入输出, 高达84MHz .多达138个5V输入输出.高达15个通讯接口STM32F407VGT6 中文资料规格参数参数列表反馈错误技术参数电源电压(DC)1.80 V (min)时钟频率168 MHzRAM大小200704 B位数32封装参数安装方式Surface Mount引脚数100封装LQFPLQFPActive制造应用视频和目视, 嵌入式设计与开发, Industrial, 多媒体, 便携式器材, Clock & Timing, Embedded Design & Development, Imaging, Video & Vision, Industrial, , 时钟与计时, 传感与仪器, 工业, 医用Compliant含铅标准Lead FreeREACH SVHC标准No SVHC海关信息ECCN代码3A991A2。

stm32f407zgt6中文资料

STM32程序设计案例教程:《STM32程序设计案例教程》是2019年电子工业出版社出版的图书,作者是欧启标。

内容简介:本书系统介绍了STM32程序设计的基础知识和实战技巧。

本书案例丰富、结构清晰、实用性强。

本书可作为高职高专院校电类专业学生的教材使用,也可供相关工程技术人员作为参考用书。

目录:项目1 STM32的开发步骤及STM32的GPIO端口的输出功能(1)任务1-1 控制一颗LED发光二极管闪烁(1)1.1 初步认识STM32的GPIO端口的输出功能(10)1.2 寄存器及其地址信息(15)1.3 volatile修饰符的使用及寄存器定义(17)习题1 (18)项目2 认识模块化编程(19)任务2-1 控制一颗LED发光二极管闪烁(19)2.1 模块化编程(24)2.2 其他C语言注意事项(25)2.2.1 用#define和typedef定义类型别名(25)2.2.2 一些常见的运算符问题(25)2.2.3 文件包含(26)2.2.4 关于注释(27)习题2 (28)项目3 认识STM32的存储器结构(29)任务3-1 LED0闪烁控制(29)3.1 存储器基础知识(30)3.2 Cortex-M4内核和STM32的存储器结构(31)3.2.1 Cortex-M4内核的存储器结构(31)3.2.2 STM32的存储器结构(33)3.2.3 位带(Bit Band)及位带别名区(Bit Band Alias)的关系(37)3.3 结构体在STM32中的应用(40)3.4 通用的I/O端口功能设置函数的设计(42)任务3-2 跑马灯的实现(44)习题3 (47)项目4 精确延时的实现—SysTick 定时器的原理及其应用(48)任务4-1 蜂鸣器发声控制(48)4.1 SysTick定时器介绍(52)4.2 嘀嗒定时器的延时应用(55)习题4 (57)项目5 机械按键的识别——初步认识GPIO端口的输入功能(58)任务5-1 识别机械按键的按下与弹起(58)5.1 STM32的GPIO端口的数据输入功能(65)5.1.1 GPIO端口位的数据输入通道(65)5.1.2 GPIO端口位的输入配置及上/下拉电阻使能(66)5.2 按键状态的判断(67)习题5 (68)项目6 深入了解STM32F407的时钟系统(69)6.1 STM32F4的时钟系统简介(69)6.2 STM32F4的时钟系统(69)6.3 STM32F4的系统时钟和各模块时钟(72)6.3.1 系统时钟SYSCLK (72)6.3.2 由SYSCLK模块提供时钟源的时钟(73)6.3.3 RCC模块的相关寄存器及其作用(75)习题6 (77)项目7 认识STM32的串口结构(78)任务7-1 使用STM32的串口向PC端发送字符串(78)7.1 串口基础知识(83)7.2 STM32的串口结构(84)7.3 引脚复用(90)7.4 端口初始化函数的重新组织(93)习题7 (95)项目8 STM32F407的中断管理(96)任务8-1 使用STM32的外部中断(96)8.1 内嵌中断向量控制器NVIC对中断的控制(102)8.1.1 STM32的中断源(102)8.1.2 STM32的中断使能控制(105)8.1.3 STM32的中断优先级(106)8.1.4 中断函数接口及中断函数的实现(112)8.2 外部中断(113)8.2.1 外部中断的中断源(113)8.2.2 外部中断的设置(114)习题8 (116)项目9 认识STM32的定时器(118)任务9-1 使用定时器中断控制LED0的闪烁(118)9.1 STM32的定时器概述(122)9.2 TIM3内部结构及其计数原理(122)9.2.1 TIM3的内部结构(122)9.2.2 STM32定时器的定时原理(124)9.3 定时器中断的实现(127)9.4 应用定时器产生PWM调制信号(128)9.4.1 TIM14的PWM调制原理(130)9.4.2 TIM14产生PWM信号涉及的寄存器(132)9.4.3 TIM14产生PWM信号的实现流程(133)任务9-2 使用TIM14产生周期为500s、占空比为80%的脉冲信号(134)习题9 (136)项目10 认识STM32的独立看门狗(137)任务10-1 认识STM32的独立看门狗的工作原理(137)10.1 看门狗电路概述(140)10.2 STM32F407的看门狗电路(140)10.3 独立看门狗相关的寄存器(141)10.4 独立看门狗的设置、启动及工作流程(142)习题10 (143)项目11 认识STM32F407的实时时钟(144)任务11-1 认识STM32的RTC (144)11.1 RTC实时时钟介绍(149)11.2 STM32的RTC的工作原理(149)11.3 STM32的RTC的操作步骤(153)习题11 (155)项目12 STM32迷你开发板电路设计(156)项目13 认识ARM处理器(161)13.1 架构简介(161)13.2 Cortex-M4的操作状态、工作模式和访问等级(161)13.3 数据长度(162)13.4 存储器大小端(162)13.5 Cortex-M4的寄存器(163)13.6 堆和栈的概念(166)13.7 内存分配(167)习题13 (170)项目14 汇编语言基础和Cortex-M4指令集(172)14.1 汇编语言基础(172)14.2 Cortex-M4的指令集(174)14.3 Cortex-M4的伪操作和伪指令(180)14.3.1 伪操作(180)14.3.2 伪指令(186)习题14 (187)项目15 认识启动文件startup_stm32f40_41xxx.s (188)习题15 (191)附录A STM32F407ZGT6的引脚结构与功能(192)附录B STM32F407ZGT6核心电路设计(203)附录C STM32F407ZGT6外围电路设计(204)附录D 关于编译信息的解释(205)参考文献(207)。

stm32f407数据手册中文

本参考手册涵盖了基于ARM® Cortex®-M3内核的单片机STM32F101xx, STM32F102xx, STM32F103xx, STM32F105xx and STM32F107xx产品线,它为用户使用以上单片机提供了完整的存储器和外设信息。

(STM32F101xx, STM32F102xx, STM32F103xx, STM32F105xx and STM32F107xx advanced ARM-based 32-bit MCUs)

计算机图形学,输入的是对虚拟场景的描述,通常为多边形数组,而每个多边形由三个顶点组成,每个顶点包括三维坐标、贴图坐标、RGB 颜色等。

输出的是图像,即二维像素数组。

计算机视觉,输入的是图像或图像序列,通常来自相机、摄像头或视频文件。

输出的是对于图像序列对应的真实世界的理解,比如检测人脸、识别车牌。

图像处理,输入的是图像,输出的也是图像。

Photoshop中对一副图像应用滤镜就是典型的一种图像处理。

常见操作有模糊、灰度化、增强对比度等。

尽管三者所涉及的都是运用计算机来处理对象,但是长期以来却是属于不同技术领域,近些年来,随着多媒体技术、计算机动画以及三维数据场显示技术等的迅速发展,计算机图形学、图像处理和计算机视觉结合日益紧密,并且相互渗透。

例如,三维游戏为了增加表现力会叠加全屏的后期特效,原理就是数字图像处理,只是将计算量放在了显卡端;计算机视觉对需要识别的照片进行预处理也是运用了数字图像处理技术;最明显的是增强现实(AR),用数字图像处理技术进行预处理,用计算机视觉技术进行跟踪物体的识别与姿态获取,用图形学技术进行虚拟三维物体的叠加和显示。

STM32F407单片机使用攻略:中文手册、实战问答15篇

STM32F407单片机使用攻略:中文手册、实战问答15篇STM32F4系列基于最新的ARM Cortex M4内核,在现有出色的STM32微控制器产品组合中新增了信号处理功能,并提高了运行速度;STM32F405x集成了定时器、3个ADC、2个DAC、串行接口、外存接口、实时时钟、CRC计算单元和模拟真随机数发生器在内的整套先进外设。

STM32F407在STM32F405产品基础上增加了多个先进外设。

STM32&STM8技术社区整理STM32F407中文资料,帮助大家的开发设计。

中文资料篇在STM32F4DISCOVERY上移植EMWIN(图片+源码)EMWIN 是NXP和Segger公司联合开发的图形库,界面比起UCGUI更加漂亮和直观,美中不足的是,在不购买其专利授权情况下,无法获取源码,只有编译好的库使用,目前库版本已经更新到5.20。

现在分享一个4.15D版本的EMWIN在STM32F4DISCOVERY上的移植。

STM32F407学习板全部例程+原理图全部代码都已测试通过,若发现有什么问题请和贴主联系。

因为时间仓促,基本上都是一些硬件测试程序。

记得要把例程和固件库放在同一目录下,全部工程共用一个库的。

至于SD 卡里的文件只是几个测试图片和音频文件,只需要根据程序将文件放置在相应目录下即可STM32F407正交编码器问题所有的定时器都有编码器模式,但是,实际上TIM9~12保留了。

tim2-5是正常的。

不知道是BUG还是确实就是没有,总之是被简介给坑了。

大家注意下。

STM32F407跑ucosii+emwin5.14,欢迎大家围观~工程代码提供在F407上移植了ucOSII和emwin5.14,因为最近在做实验室的项目,在LPC1788上使用了emwin,那个界面绝对不是盖的,相当的漂亮啊~所以就想移植到STM32F407上面来了。

附工程源码分享下刚刚画好的DXP封装__STM32F407效果如图示,原理图源文件在附件里,送几个PCB库,略微检查了下,应该没问题开发问答篇STM32F407在USART时的管脚映射说明STM32F407在跑USART时,USART3对应的是PD8和PD9.其他的USART1、USART2对应的是哪个管脚STM32F407运行usb otg的库函数#define MSC_IN_EP 0x81#define MSC_OUT_EP 0x01端点被更改就不能正常应用了有没有谁尝试更改端点关于stm32f407-discovery开发板DAC的例程问题在stm32f407discovery开发板的例程中对于DAC通道1的DMA配置为通道7流为6 ,DAC通道2的DMA配置为通道7流为5,这跟官方的编程手册中的说明dma流跟通道完全相反了,整个程序是可以跑的,但是不知道问题出在了哪里关于stm32f407 I2s DMA的主发送问题最近用stm32f407做一个sd卡mp3解码后,音频传输的项目,声卡芯片用的VM8978,采取的是SPI3的i2s,用的DMA是DMA1的stream5通道0.用的是主发送模式在dma中断中我用一个led反转看是否进入中断,结果是,中断进入,但i2s 引脚为何没有输出,按道理说应该是有波形输出的啊BCLk脚怎么一直是低电平了?stm32f407 串口不中断有没高手熟悉stm32f407的啊? 小弟在使用时,发现如果打开三个uart发送和接收中断。

stm32f407vet6数据手册_引脚图_参数

This is information on a product in full production. June 2013DocID022152 Rev 41/185STM32F405xxSTM32F407xxDatasheet - production dataFeatures•Core: ARM 32-bit Cortex™-M4 CPU with FPU, Adaptive real-time accelerator (ART Accelerator™) allowing 0-wait state execution from Flash memory, frequency up to 168MHz, memory protection unit, 210DMIPS/1.25DMIPS/MHz (Dhrystone 2.1), and DSP instructions•Memories –Up to 1 Mbyte of Flash memory–Up to 192+4Kbytes of SRAM including 64-Kbyte of CCM (core coupled memory) data RAM–Flexible static memory controller supporting Compact Flash, SRAM, PSRAM, NOR and NAND memories•LCD parallel interface, 8080/6800 modes•Clock, reset and supply management – 1.8 V to 3.6 V application supply and I/Os–POR, PDR, PVD and BOR–4-to-26MHz crystal oscillator–Internal 16 MHz factory-trimmed RC (1% accuracy)–32 kHz oscillator for RTC with calibration–Internal 32 kHz RC with calibration•Low power –Sleep, Stop and Standby modes–V BAT supply for RTC, 20×32 bit backup registers + optional 4 KB backup SRAM•3×12-bit, 2.4MSPS A/D converters: up to 24 channels and 7.2MSPS in triple interleaved mode•2×12-bit D/A converters•General-purpose DMA: 16-stream DMA controller with FIFOs and burst support•Up to 17 timers: up to twelve 16-bit and two 32-bit timers up to 168MHz, each with up to 4 IC/OC/PWM or pulse counter and quadrature (incremental) encoder input •Debug mode –Serial wire debug (SWD) & JTAG interfaces –Cortex-M4 Embedded Trace Macrocell™•Up to 140 I/O ports with interrupt capability –Up to 136 fast I/Os up to 84MHz –Up to 138 5 V-tolerant I/Os •Up to 15 communication interfaces –Up to 3 × I 2C interfaces (SMBus/PMBus)–Up to 4 USARTs/2 UARTs (10.5Mbit/s, ISO 7816 interface, LIN, IrDA, modem control)–Up to 3 SPIs (42Mbits/s), 2 with muxed full-duplex I 2S to achieve audio class accuracy via internal audio PLL or external clock – 2 × CAN interfaces (2.0B Active)–SDIO interface •Advanced connectivity –USB 2.0 full-speed device/host/OTG controller with on-chip PHY –USB 2.0 high-speed/full-speed device/host/OTG controller with dedicated DMA, on-chip full-speed PHY and ULPI –10/100 Ethernet MAC with dedicated DMA: supports IEEE 1588v2 hardware, MII/RMII •8- to 14-bit parallel camera interface up to 54Mbytes/s •True random number generator •CRC calculation unit •96-bit unique ID •RTC: subsecond accuracy, hardware calendarTable 1. Device summary Reference Part number STM32F405xx STM32F405RG, STM32F405VG, STM32F405ZG, STM32F405OG, STM32F405OE STM32F407xxSTM32F407VG, STM32F407IG, STM32F407ZG,STM32F407VE, STM32F407ZE, STM32F407IERevision history STM32F405xx, STM32F407xx 176/185DocID022152 Rev 48 Revision historyTable 98. Document revision historyDateRevision Changes 15-Sep-20111Initial release.24-Jan-20122Added WLCSP90 package on cover page.Renamed USART4 and USART5 into UART4 and UART5,respectively.Updated number of USB OTG HS and FS in Table 2: STM32F405xxand STM32F407xx: features and peripheral counts .Updated Figure 3: Compatible board design betweenSTM32F10xx/STM32F2xx/STM32F4xx for LQFP144 package andFigure 4: Compatible board design between STM32F2xx andSTM32F4xx for LQFP176 and BGA176 packages , and removed note1 and 2.Updated Section 2.2.9: Flexible static memory controller (FSMC).Modified I/Os used to reprogram the Flash memory for CAN2 andUSB OTG FS in Section 2.2.13: Boot modes .Updated note in Section 2.2.14: Power supply schemes .PDR_ON no more available on LQFP100 package. UpdatedSection 2.2.16: Voltage regulator . Updated condition to obtain aminimum supply voltage of 1.7V in the whole document.Renamed USART4/5 to UART4/5 and added LIN and IrDA feature forUART4 and UART5 in Table 5: USART feature comparison .Removed support of I2C for OTG PHY in Section 2.2.30: Universalserial bus on-the-go full-speed (OTG_FS).Added Table 6: Legend/abbreviations used in the pinout table .Table 7: STM32F40x pin and ball definitions : replaced V SS _3, V SS _4,and V SS _8 by V SS ; reformatted Table 7: STM32F40x pin and balldefinitions to better highlight I/O structure, and alternate functionsversus additional functions; signal corresponding to LQFP100 pin 99changed from PDR_ON to V SS ; EVENTOUT added in the list ofalternate functions for all I/Os; ADC3_IN8 added as alternate functionfor PF10; FSMC_CLE and FSMC_ALE added as alternate functionsfor PD11 and PD12, respectively; PH10 alternate functionTIM15_CH1_ETR renamed TIM5_CH1; updated PA4 and PA5 I/Ostructure to TTa.Removed OTG_HS_SCL, OTG_HS_SDA, OTG_FS_INTN in Table 7:STM32F40x pin and ball definitions and Table 9: Alternate functionmapping .Changed TCM data RAM to CCM data RAM in Figure 18: STM32F40xmemory map .Added I VDD and I VSS maximum values in Table 12: Currentcharacteristics .Added Note 1 related to f HCLK , updated Note 2 in Table 14: Generaloperating conditions , and added maximum power dissipation values.Updated Table 15: Limitations depending on the operating powersupply range .STM32F405xx, STM32F407xx Revision history24-Jan-20122(continued)Added V12 in Table19: Embedded reset and power control blockcharacteristics.Updated Table21: Typical and maximum current consumption in Runmode, code with data processing running from Flash memory (ARTaccelerator disabled) and Table20: Typical and maximum currentconsumption in Run mode, code with data processing running fromFlash memory (ART accelerator enabled) or RAM. Added Figure,Figure25, Figure26, and Figure27.Updated Table22: Typical and maximum current consumption in Sleepmode and removed Note 1.Updated Table23: Typical and maximum current consumptions in Stopmode and Table24: Typical and maximum current consumptions inStandby mode, Table25: Typical and maximum current consumptionsin VBAT mode, and Table26: Switching output I/O currentconsumption.Section: On-chip peripheral current consumption: modified conditions,and updated Table27: Peripheral current consumption and Note2.Changed f HSE_ext to 50MHz and t r(HSE)/t f(HSE) maximum value inTable29: High-speed external user clock characteristics.Added C in(LSE) in Table30: Low-speed external user clockcharacteristics.Updated maximum PLL input clock frequency, removed related note,and deleted jitter for MCO for RMII Ethernet typical value in Table35:Main PLL characteristics. Updated maximum PLLI2S input clockfrequency and removed related note in Table36: PLLI2S (audio PLL)characteristics.Updated Section: Flash memory to specify that the devices areshipped to customers with the Flash memory erased. UpdatedTable38: Flash memory characteristics, and added t ME in Table39:Flash memory programming.Updated Table42: EMS characteristics, and Table43: EMIcharacteristics.Updated Table56: I2S dynamic characteristicsUpdated Figure46: ULPI timing diagram and Table62: ULPI timing.Added t COUNTER and t MAX_COUNT in Table51: Characteristics of TIMxconnected to the APB1 domain and Table52: Characteristics of TIMxconnected to the APB2 domain. Updated Table65: Dynamiccharacteristics: Ethernet MAC signals for RMII.Removed USB-IF certification in Section: USB OTG FScharacteristics.Table 98. Document revision history (continued)Date Revision ChangesDocID022152 Rev 4177/185Revision history STM32F405xx, STM32F407xx 178/185DocID022152 Rev 424-Jan-20122(continued)Updated Table 61: USB HS clock timing parameters Updated Table 67: ADC characteristics .Updated Table 68: ADC accuracy at fADC = 30MHz .Updated Note 1 in Table 74: DAC characteristics .Section 5.3.25: FSMC characteristics : updated Table 75 to Table 86, changed C L value to 30pF, and modified FSMC configuration for asynchronous timings and waveforms. Updated Figure 60: Synchronous multiplexed PSRAM write timings .Updated Table 96: Package thermal characteristics .Appendix A.1: USB OTG full speed (FS) interface solutions : modified Figure 86: USB controller configured as peripheral-only and used inFull speed mode added Note 2, updated Figure 87: USB controllerconfigured as host-only and used in full speed mode and addedNote 2, changed Figure 88: USB controller configured in dual modeand used in full speed mode and added Note 3.Appendix A.2: USB OTG high speed (HS) interface solutions : removedfigures USB OTG HS device-only connection in FS mode and USBOTG HS host-only connection in FS mode, and updated Figure 89:USB controller configured as peripheral, host, or dual-mode and usedin high speed mode and added Note 2.Added Appendix A.3: Ethernet interface solutions .Table 98. Document revision history (continued)Date Revision ChangesSTM32F405xx, STM32F407xx Revision history31-May-20123Updated Figure5: STM32F40x block diagram and Figure7: Power supply supervisor interconnection with internal reset OFFAdded SDIO, added notes related to FSMC and SPI/I2S in Table2: STM32F405xx and STM32F407xx: features and peripheral counts. Starting from Silicon revision Z, USB OTG full-speed interface is now available for all STM32F405xx devices.Added full information on WLCSP90 package together with corresponding part numbers.Changed number of AHB buses to 3.Modified available Flash memory sizes in Section2.2.4: Embedded Flash memory.Modified number of maskable interrupt channels in Section2.2.10: Nested vectored interrupt controller (NVIC).Updated case of Regulator ON/internal reset ON, RegulatorON/internal reset OFF, and Regulator OFF/internal reset ON in Section2.2.16: Voltage regulator.Updated standby mode description in Section2.2.19: Low-power modes.Added Note1 below Figure16: STM32F40x UFBGA176 ballout. Added Note1 below Figure17: STM32F40x WLCSP90 ballout. Updated Table7: STM32F40x pin and ball definitions.Added Table8: FSMC pin definition.Removed OTG_HS_INTN alternate function in Table7: STM32F40x pin and ball definitions and Table9: Alternate function mapping. Removed I2S2_WS on PB6/AF5 in Table9: Alternate function mapping.Replaced JTRST by NJTRST, removed ETH_RMII _TX_CLK, and modified I2S3ext_SD on PC11 in Table9: Alternate function mapping. Added Table10: STM32F40x register boundary addresses.Updated Figure18: STM32F40x memory map.Updated V DDA and V REF+ decoupling capacitor in Figure21: Power supply scheme.Added power dissipation maximum value for WLCSP90 in Table14: General operating conditions.Updated V POR/PDR in Table19: Embedded reset and power control block characteristics.Updated notes in Table21: Typical and maximum current consumption in Run mode, code with data processing running from Flash memory (ART accelerator disabled), Table20: Typical and maximum current consumption in Run mode, code with data processing running from Flash memory (ART accelerator enabled) or RAM, and Table22: Typical and maximum current consumption in Sleep mode.Updated maximum current consumption at T A = 25°n Table23: Typical and maximum current consumptions in Stop mode.Table 98. Document revision history (continued)Date Revision ChangesDocID022152 Rev 4179/185Revision history STM32F405xx, STM32F407xx 180/185DocID022152 Rev 431-May-2012 3 (continued)Removed f HSE_ext typical value in Table 29: High-speed external user clock characteristics . Updated Table 31: HSE 4-26 MHz oscillator characteristics and Table 32: LSE oscillator characteristics (fLSE = 32.768 kHz).Added f PLL48_OUT maximum value in Table 35: Main PLL characteristics .Modified equation 1 and 2 in Section 5.3.11: PLL spread spectrum clock generation (SSCG) characteristics .Updated Table 38: Flash memory characteristics , Table 39: Flash memory programming , and Table 40: Flash memory programming with VPP .Updated Section : Output driving current .Table 53: I2C characteristics : Note 4 updated and applied to t h(SDA) in Fast mode, and removed note 4 related to t h(SDA) minimum value.Updated Table 67: ADC characteristics . Updated note concerning ADCaccuracy vs. negative injection current below Table 68: ADC accuracyat fADC = 30MHz .Added WLCSP90 thermal resistance in Table 96: Package thermalcharacteristics .Updated Table 90: WLCSP90 - 0.400 mm pitch wafer level chip sizepackage mechanical data .Updated Figure 83: UFBGA176+25 - ultra thin fine pitch ball grid array10 × 10 × 0.6 mm, package outline and Table 94: UFBGA176+25 -ultra thin fine pitch ball grid array 10 × 10 × 0.6 mm mechanical data .Added Figure 85: LQFP176 recommended footprint .Removed 256 and 768 Kbyte Flash memory density from Table 97:Ordering information scheme .Table 98. Document revision history (continued)Date Revision ChangesSTM32F405xx, STM32F407xx Revision history04-Jun-20134Modified Note1 below Table2: STM32F405xx and STM32F407xx: features and peripheral counts.Updated Figure4 title.Updated Note3 below Figure21: Power supply scheme.Changed simplex mode into half-duplex mode in Section2.2.25: Inter-integrated sound (I2S).Replaced DAC1_OUT and DAC2_OUT by DAC_OUT1 andDAC_OUT2, respectively.Updated pin 36 signal in Figure15: STM32F40x LQFP176 pinout. Changed pin number from F8 to D4 for PA13 pin in Table7:STM32F40x pin and ball definitions.Replaced TIM2_CH1/TIM2_ETR by TIM2_CH1_ETR for PA0 and PA5 pins in Table9: Alternate function mapping.Changed system memory into System memory + OTP in Figure18: STM32F40x memory map.Added Note1 below Table16: VCAP_1/VCAP_2 operating conditions. Updated I DDA description in Table74: DAC characteristics.Removed PA9/PB13 connection to VBUS in Figure86: USB controller configured as peripheral-only and used in Full speed mode and Figure87: USB controller configured as host-only and used in full speed mode.Updated SPI throughput on front page and Section2.2.24: Serial peripheral interface (SPI)Updated operating voltages in Table2: STM32F405xx andSTM32F407xx: features and peripheral countsUpdated note in Section2.2.14: Power supply schemesUpdated Section2.2.15: Power supply supervisorUpdated “Regulator ON” paragraph in Section2.2.16: Voltage regulatorRemoved note in Section2.2.19: Low-power modesCorrected wrong reference manual in Section2.2.28: Ethernet MAC interface with dedicated DMA and IEEE1588 supportUpdated Table15: Limitations depending on the operating power supply rangeUpdated Table24: Typical and maximum current consumptions in Standby modeUpdated Table25: Typical and maximum current consumptions in VBAT modeUpdated Table36: PLLI2S (audio PLL) characteristicsUpdated Table43: EMI characteristicsUpdated Table48: Output voltage characteristicsUpdated Table50: NRST pin characteristicsUpdated Table55: SPI dynamic characteristicsUpdated Table56: I2S dynamic characteristicsDeleted Table 59Updated Table62: ULPI timingUpdated Figure47: Ethernet SMI timing diagramTable 98. Document revision history (continued)Date Revision ChangesDocID022152 Rev 4181/185Revision history STM32F405xx, STM32F407xx 182/185DocID022152 Rev 404-Jun-20134(continued)Updated Figure 83: UFBGA176+25 - ultra thin fine pitch ball grid array 10 × 10 × 0.6 mm, package outline Updated Table 94: UFBGA176+25 - ultra thin fine pitch ball grid array 10 × 10 × 0.6 mm mechanical data Updated Figure 5: STM32F40x block diagram Updated Section 2: Description Updated footnote (3) in Table 2: STM32F405xx and STM32F407xx: features and peripheral counts Updated Figure 3: Compatible board design between STM32F10xx/STM32F2xx/STM32F4xx for LQFP144 package Updated Figure 4: Compatible board design between STM32F2xx and STM32F4xx for LQFP176 and BGA176 packages Updated Section 2.2.14: Power supply schemes Updated Section 2.2.15: Power supply supervisor Updated Section 2.2.16: Voltage regulator , including figures.Updated Table 14: General operating conditions , including footnote (2).Updated Table 15: Limitations depending on the operating power supply range , including footnote (3).Updated footnote (1) in Table 67: ADC characteristics .Updated footnote (3) in Table 68: ADC accuracy at fADC = 30MHz .Updated footnote (1) in Table 74: DAC characteristics .Updated Figure 9: Regulator OFF .Updated Figure 7: Power supply supervisor interconnection with internal reset OFF .Added Section 2.2.17: Regulator ON/OFF and internal reset ON/OFFavailability .Updated footnote (2) of Figure 21: Power supply scheme .Replaced respectively “I2S3S_WS" by "I2S3_WS”, “I2S3S_CK” by“I2S3_CK” and “FSMC_BLN1” by “FSMC_NBL1” in Table 9: Alternatefunction mapping .Added “EVENTOUT” as alternate function “AF15” for pin PC13, PC14,PC15, PH0, PH1, PI8 in Table 9: Alternate function mappingReplaced “DCMI_12” by “DCMI_D12” in Table 7: STM32F40x pin andball definitions .Removed the following sentence from Section : I2C interfacecharacteristics : ”Unless otherwise specified, the parametersgiven in Table 53 are derived from tests performed under theambient temperature, f PCLK1 frequency and V DD supply voltageconditions summarized in Table 14.”.In Table 7: STM32F40x pin and ball definitions on page 45:–For pin PC13, replaced “RTC_AF1” by “RTC_OUT, RTC_TAMP1,RTC_TS”–for pin PI8, replaced “RTC_AF2” by “RTC_TAMP1, RTC_TAMP2,RTC_TS”.–for pin PB15, added RTC_REFIN in Alternate functions column.In Table 9: Alternate function mapping on page 60, for portPB15, replaced “RTC_50Hz” by “RTC_REFIN”.Table 98. Document revision history (continued)Date Revision ChangesSTM32F405xx, STM32F407xx Revision history04-Jun-20134(continued)Updated Figure6: Multi-AHB matrix.Updated Figure7: Power supply supervisor interconnection withinternal reset OFFChanged 1.2V to V12 in Section: Regulator OFFUpdated LQFP176 pin 48.Updated Section1: Introduction.Updated Section2: Description.Updated operating voltage in Table2: STM32F405xx andSTM32F407xx: features and peripheral counts.Updated Note1.Updated Section2.2.15: Power supply supervisor.Updated Section2.2.16: Voltage regulator.Updated Figure9: Regulator OFF.Updated Table3: Regulator ON/OFF and internal reset ON/OFFavailability.Updated Section2.2.19: Low-power modes.Updated Section2.2.20: VBAT operation.Updated Section2.2.22: Inter-integrated circuit interface (I²C) .Updated pin 48 in Figure15: STM32F40x LQFP176 pinout.Updated Table6: Legend/abbreviations used in the pinout table.Updated Table7: STM32F40x pin and ball definitions.Updated Table14: General operating conditions.Updated Table15: Limitations depending on the operating powersupply range.Updated Section5.3.7: Wakeup time from low-power mode.Updated Table33: HSI oscillator characteristics.Updated Section5.3.15: I/O current injection characteristics.Updated Table47: I/O static characteristics.Updated Table50: NRST pin characteristics.Updated Table53: I2C characteristics.Updated Figure39: I2C bus AC waveforms and measurement circuit.Updated Section5.3.19: Communications interfaces.Updated Table67: ADC characteristics.Added Table70: Temperature sensor calibration values.Added Table73: Internal reference voltage calibration values.Updated Section5.3.25: FSMC characteristics.Updated Section5.3.27: SD/SDIO MMC card host interface (SDIO)characteristics.Updated Table23: Typical and maximum current consumptions in Stopmode.Updated Section: SPI interface characteristics included Table55.Updated Section: I2S interface characteristics included Table56.Updated Table64: Dynamic characteristics: Ehternet MAC signals forSMI.Updated Table66: Dynamic characteristics: Ethernet MAC signals forMII.Table 98. Document revision history (continued)Date Revision ChangesDocID022152 Rev 4183/185Revision history STM32F405xx, STM32F407xx 184/185DocID022152 Rev 404-Jun-20134(continued)Updated Table 64: Dynamic characteristics: Ehternet MAC signals for SMI .Updated Table 66: Dynamic characteristics: Ethernet MAC signals for MII .Updated Table 79: Synchronous multiplexed NOR/PSRAM read timings .Updated Table 80: Synchronous multiplexed PSRAM write timings .Updated Table 81: Synchronous non-multiplexed NOR/PSRAM read timings .Updated Table 82: Synchronous non-multiplexed PSRAM writetimings .Updated Section 5.3.26: Camera interface (DCMI) timing specificationsincluding Table 87: DCMI characteristics and addition of Figure 73:DCMI timing diagram .Updated Section 5.3.27: SD/SDIO MMC card host interface (SDIO)characteristics including Table 88.Updated Chapter Figure 9.Table 98. Document revision history (continued)Date Revision ChangesSTM32F405xx, STM32F407xxPlease Read Carefully:Information in this document is provided solely in connection with ST products. STMicroelectronics NV and its subsidiaries (“ST”) reserve the right to make changes, corrections, modifications or improvements, to this document, and the products and services described herein at any time, without notice.All ST products are sold pursuant to ST’s terms and conditions of sale.Purchasers are solely responsible for the choice, selection and use of the ST products and services described herein, and ST assumes no liability whatsoever relating to the choice, selection or use of the ST products and services described herein.No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted under this document. If any part of this document refers to any third party products or services it shall not be deemed a license grant by ST for the use of such third party products or services, or any intellectual property contained therein or considered as a warranty covering the use in any manner whatsoever of such third party products or services or any intellectual property contained therein.UNLESS OTHERWISE SET FORTH IN ST’S TERMS AND CONDITIONS OF SALE ST DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY WITH RESPECT TO THE USE AND/OR SALE OF ST PRODUCTS INCLUDING WITHOUT LIMITATION IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE (AND THEIR EQUIVALENTS UNDER THE LAWS OF ANY JURISDICTION), OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT.ST PRODUCTS ARE NOT AUTHORIZED FOR USE IN WEAPONS. NOR ARE ST PRODUCTS DESIGNED OR AUTHORIZED FOR USE IN: (A) SAFETY CRITICAL APPLICATIONS SUCH AS LIFE SUPPORTING, ACTIVE IMPLANTED DEVICES OR SYSTEMS WITH PRODUCT FUNCTIONAL SAFETY REQUIREMENTS; (B) AERONAUTIC APPLICATIONS; (C) AUTOMOTIVE APPLICATIONS OR ENVIRONMENTS, AND/OR (D) AEROSPACE APPLICATIONS OR ENVIRONMENTS. WHERE ST PRODUCTS ARE NOT DESIGNED FOR SUCH USE, THE PURCHASER SHALL USE PRODUCTS AT PURCHASER’S SOLE RISK, EVEN IF ST HAS BEEN INFORMED IN WRITING OF SUCH USAGE, UNLESS A PRODUCT IS EXPRESSLY DESIGNATED BY ST AS BEING INTENDED FOR “AUTOMOTIVE, AUTOMOTIVE SAFETY OR MEDICAL” INDUSTRY DOMAINS ACCORDING TO ST PRODUCT DESIGN SPECIFICATIONS. PRODUCTS FORMALLY ESCC, QML OR JAN QUALIFIED ARE DEEMED SUITABLE FOR USE IN AEROSPACE BY THE CORRESPONDING GOVERNMENTAL AGENCY.Resale of ST products with provisions different from the statements and/or technical features set forth in this document shall immediately void any warranty granted by ST for the ST product or service described herein and shall not create or extend in any manner whatsoever, any liability of ST.DocID022152 Rev 4185/185万联芯城专注电子元器件配单服务,只售原装现货库存,万联芯城所售芯片IC,电阻电容,二三极管等物料,原装质量有保障,价格有明显优势,已为全国多家企业提供配套服务,客户只需提交BOM表,即可获得优势报价,整单采购有优惠,万联芯城拥有完善的产品供应链体系及现代化仓储系统,可满足多种BOM报价需求,PDF完整版点击进入万联芯城。

STM32-参考手册-中文.pdf

STM32-参考⼿册-中⽂.pdf23 串⾏外设接⼝(SPI)⼩容量产品是指闪存存储器容量在16K ⾄32K 字节之间的STM32F101xx、STM32F102xx和STM32F103xx微控制器。

中容量产品是指闪存存储器容量在64K⾄128K字节之间的STM32F101xx、STM32F102xx和STM32F103xx微控制器。

⼤容量产品是指闪存存储器容量在256K⾄512K字节之间的STM32F101xx和STM32F103xx微控制器。

互联型产品是指STM32F105xx和STM32F107xx微控制器。

除⾮特别说明,本章描述的模块适⽤于整个STM32F10xxx微控制器系列。

23.1 SPI简介在⼤容量产品和互联型产品上,SPI接⼝可以配置为⽀持SPI协议或者⽀持I2S⾳频协议。

SPI接⼝默认⼯作在SPI⽅式,可以通过软件把功能从SPI模式切换到I2S模式。

在⼩容量和中容量产品上,不⽀持I2S⾳频协议。

串⾏外设接⼝(SPI)允许芯⽚与外部设备以半/全双⼯、同步、串⾏⽅式通信。

此接⼝可以被配置成主模式,并为外部从设备提供通信时钟(SCK)。

接⼝还能以多主配置⽅式⼯作。

它可⽤于多种⽤途,包括使⽤⼀条双向数据线的双线单⼯同步传输,还可使⽤CRC校验的可靠通信。

I2S也是⼀种3引脚的同步串⾏接⼝通讯协议。

它⽀持四种⾳频标准,包括飞利浦I2S标准,MSB 和LSB对齐标准,以及PCM标准。

它在半双⼯通讯中,可以⼯作在主和从2种模式下。

当它作为主设备时,通过接⼝向外部的从设备提供时钟信号。

警告:由于 SPI3/I2S3 的部分引脚与 JTAG 引脚共享 (SPI3_NSS/I2S3_WS 与 JTDI ,SPI3_SCK/I2S3_CK与JTDO),因此这些引脚不受IO控制器控制,他们(在每次复位后)被默认保留为JTAG⽤途。

如果⽤户想把引脚配置给SPI3/I2S3,必须(在调试时)关闭JTAG并切换⾄SWD接⼝,或者(在标准应⽤时)同时关闭JTAG和SWD接⼝。

stm32f407数据手册中文

1,参考资料1. Stm32f4数据手册:stm32f407zgt6.pdf2. Stm32f4中文手册:stm32f4xx中文参考手册.pdf3.开发板原理图:Explorer stm32f4_ Vxx_ SCH.pdf2,芯片内部资源1.芯片图片2.芯片参数表3.内核(1)32位高性能Arm Cortex-M4处理器(2)时钟:高达168MHz,实际上可以稍微超频一点(3)支持FPU(浮点运算)和DSP指令4. IO端口(1)Stm32f407zgt6:144针114 IO端口(2)大多数IO端口可以承受5V(模拟通道除外)(3)支持调试:SWD和JTAG,SWD只需要2条数据线5.记忆(1)内存容量:1024k闪存,192K SRAM6.时钟,复位和电源管理(1)1.8〜3.6V电源和IO电压(2)上电复位和可编程掉电监控(3)强大的时钟系统-4〜26m外部高速晶体振荡器内部16 MHz高速RC振荡器-内部锁相环(PLL,倍频),PLL倍频后,一般系统时钟是外部或内部高速时钟-外部低速32.768k晶体振荡器,主要用作RTC时钟源7.低功耗(1)三种低功耗模式:睡眠,停止和待机(2)RTC和备用寄存器可以由电池供电8,广告(1)3个12位AD [最多24个外部测试通道](2)内部通道可用于内部温度测量(3)内置参考电压9,DA(1)两个12位Da10,DMA(1)16个具有FIFO和突发支持的DMA通道(2)支持的外设:定时器,ADC,DAC,SDIO,I2S,SPI,I2C和USART 11.多达17个计时器(1)10个通用计时器(TIM2和tim5为32位)(2)2个基本计时器(3)2个高级计时器(4)1个系统计时器(5)2个看门狗定时器12.多达17个通讯接口(1)三个I2C接口(2)6个串口(3)3个SPI接口(4)2个CAN2.0(5)2个USB OTG (6)个SDIO。

STM32F407之USART翻译

●发送方为同步传输提供时钟 ● IRDA SIR 编码器解码器

- 在正常模式下支持 3/16 位的持续时间 ●智能卡模拟功能

- 智能卡接口支持 ISO7816-3 标准里定义的异步 智能卡协议

- 智能卡用到的 0.5 和 1.5 个停止位 单线半双工通信 可配置的使用 DMA 的多缓冲器通信 在 SRAM 里利用集中式 DMA 缓冲接收/发送字节 单独的发送器和接收器使能位 传输检测标志:

发送器 发送器根据 M 位的状态发送 8 位或 9 位的数据字。当发送使能位(TE)被设置时,

发送移位寄存器中的数据在 TX 脚上输出,相应的时钟脉冲在 SCLK 脚上输出。

字符发送 在 USART 发送期间,在 TX 引脚上首先移出数据的最低有效位。在此模式里,

USART_DR 寄存器包含了一个内部总线和发送移位寄存器之间的缓冲器(见图 236)。 每个字符之前都有一个低电平的起始位;之后跟着的停止位,其数目可 配置。 注意:1.在数据传输期间不能复位 TE 位,否则将破坏 TX 脚上的数据,因为波 特率计数器停止计数。正在传输的当前数据将丢失。 2. TE 位被激活后将发送一个空闲帧。

●全双工的,异步通信 ●NRZ 标准的格式(Mark/Space) ●可以在速度和时钟容限之间灵活的配置 16 位或 8 位过采样方法 ● 分数波特率发生器系统

- 通用可编程的发送和接收波特率(参考数据表最 大 APB 频率值。)

●可编程的数据字长度( 8 位或 9 位) ●可配置的停止位 - 支持 1 或 2 个停止位 ●LIN 主发送同步断开符的功能和 LIN 从检测断开符的能力

stm32f407数据手册中文

1.参考1. Stm32f4数据手册:stm32f407zgt6.pdf2. Stm32f4中文手册:stm32f4xx中文参考手册.pdf3.开发板示意图:Explorer stm32f4_ Vxx_ SCH.pdf 2.芯片内部资源1.芯片图片2.芯片参数表3.内核(1)32位高性能Arm Cortex-M4处理器(2)时钟:最高168MHz,实际上比频率高一点(3)支持FPU(浮点运算)和DSP指令4. IO端口(1)Stm32f407zgt6:144针114 IO端口(2)大多数IO端口可以承受5V(模拟通道除外)(3)支持调试:SWD和JTAG,SWD只需要2条数据线5.记忆(1)内存容量:1024k闪存,192K SRAM6.时钟,复位和电源管理(1)1.8〜3.6V电源和IO电压(2)上电复位和可编程掉电监控(3)强大的时钟系统-4〜26m外部高速晶体振荡器内部16 MHz高速RC振荡器-内部锁相环(PLL),在PLL频率加倍后,一般系统时钟是外部或内部高速时钟-外部低速32.768k晶体振荡器,主要用作RTC时钟源7.低功耗(1)三种低功耗模式:睡眠,停止和待机(2)RTC和备用寄存器可以由电池供电8.广告(1)3个12位AD [最多24个外部测试通道](2)内部通道可用于内部温度测量(3)内置参考电压9,DA(1)两个12位Da10,DMA(1)16个具有FIFO和突发支持的DMA通道(2)支持的外设:定时器,ADC,DAC,SDIO,I2S,SPI,I2C和USART 11.多达17个计时器(1)10个通用计时器(TIM2和tim5为32位)(2)2个基本计时器(3)2个高级计时器(4)1个系统计时器(5)2个看门狗定时器12.多达17个通讯接口(1)三个I2C接口(2)6个串口(3)3个SPI接口(4)2个CAN2.0(5)2个USB OTG (6)SDIO。

【STM32F407开发板用户手册】第24章STM32F407的USART应用之八个串口F。。。

【STM32F407开发板⽤户⼿册】第24章STM32F407的USART应⽤之⼋个串⼝F。

第24章 STM32F407的USART应⽤之⼋个串⼝FIFO实现本章节为⼤家讲解STM32F407的6个串⼝的FIFO驱动实现,后⾯的ESP8266,GPS,RS485,GPRS等试验都是建⽴在这个驱动的基础上实现。

除了串⼝FIFO的驱动实现,RS232通信也通过本章节做个讲解。

24.1 初学者重要提⽰24.2 硬件设计24.3 串⼝驱动设计24.4 串⼝FIFO板级⽀持包(bsp_uart_fifo.c)24.5 串⼝FIFO驱动移植和使⽤24.6 实验例程设计框架24.7 实验例程说明(MDK)24.8 实验例程说明(IAR)24.9 总结24.1 初学者重要提⽰1. 学习本章节前,务必优先学习第23章。

2. 串⼝FIFO的实现跟前⾯章节按键FIFO的机制是⼀样的。

3. 本章节⽐较重要,因为后⾯的ESP8266,GPS,RS485,GPRS等试验都是建⽴在这个驱动的基础上实现。

4. ⼤家⾃⼰做的板⼦,测试串⼝收发是乱码的话,重点看stm32f4xx_hal_conf.h⽂件中的HSE_VALUE的⼤⼩跟板⼦上实际晶振⼤⼩是否⼀致,然后再看PLL配置。

5. CH340/CH341的USB转串⼝Windows驱动程序的安装包,⽀持32/64位 Windows 10/8.1/8/7。

24.2 硬件设计STM32F407IGT6最多可以⽀持6个独⽴的串⼝。

其中串⼝4和串⼝5和SDIO的GPIO是共⽤的,也就是说,如果要⽤到SD卡,那么串⼝4和串⼝5将不能使⽤。

串⼝功能可以分配到不同的GPIO。

我们常⽤的引脚分配如下:串⼝USART1 TX = PA9, RX = PA10串⼝USART2 TX = PA2, RX = PA3串⼝USART3 TX = PB10, RX = PB11串⼝UART4 TX = PC10, RX = PC11 (和SDIO共⽤)串⼝UART5 TX = PC12, RX = PD2 (和SDIO共⽤)串⼝USART6 TX = PG14, RX = PC7STM32-V5开发板使⽤了4个串⼝设备。

stm32f407zgt6中文资料

stm32f407zgt6中文资料程序设计:程序设计是给出解决特定问题程序的过程,是软件构造活动中的重要组成部分。

程序设计往往以某种程序设计语言为工具,给出这种语言下的程序。

程序设计过程应当包括分析、设计、编码、测试、排错等不同阶段。

专业的程序设计人员常被称为程序员。

任何设计活动都是在各种约束条件和相互矛盾的需求之间寻求一种平衡,程序设计也不例外。

在计算机技术发展的早期,由于机器资源比较昂贵,程序的时间和空间代价往往是设计关心的主要因素;随着硬件技术的飞速发展和软件规模的日益庞大,程序的结构、可维护性、复用性、可扩展性等因素日益重要。

STM32程序设计案例教程:本书系统介绍了STM32程序设计的基础知识和实战技巧。

本书案例丰富、结构清晰、实用性强。

本书可作为高职高专院校电类专业学生的教材使用,也可供相关工程技术人员作为参考用书。

目录:项目1 STM32的开发步骤及STM32的GPIO端口的输出功能(1)任务1-1 控制一颗LED发光二极管闪烁(1)1.1 初步认识STM32的GPIO端口的输出功能(10)1.2 寄存器及其地址信息(15)1.3 volatile修饰符的使用及寄存器定义(17)习题1 (18)项目2 认识模块化编程(19)任务2-1 控制一颗LED发光二极管闪烁(19)2.1 模块化编程(24)2.2 其他C语言注意事项(25)2.2.1 用#define和typedef定义类型别名(25)2.2.2 一些常见的运算符问题(25)2.2.3 文件包含(26)2.2.4 关于注释(27)习题2 (28)项目3 认识STM32的存储器结构(29)任务3-1 LED0闪烁控制(29)3.1 存储器基础知识(30)3.2 Cortex-M4内核和STM32的存储器结构(31)3.2.1 Cortex-M4内核的存储器结构(31)3.2.2 STM32的存储器结构(33)3.2.3 位带(Bit Band)及位带别名区(Bit Band Alias)的关系(37)3.3 结构体在STM32中的应用(40)3.4 通用的I/O端口功能设置函数的设计(42)任务3-2 跑马灯的实现(44)习题3 (47)项目4 精确延时的实现—SysTick 定时器的原理及其应用(48)任务4-1 蜂鸣器发声控制(48)4.1 SysTick定时器介绍(52)4.2 嘀嗒定时器的延时应用(55)习题4 (57)项目5 机械按键的识别——初步认识GPIO端口的输入功能(58)任务5-1 识别机械按键的按下与弹起(58)5.1 STM32的GPIO端口的数据输入功能(65)5.1.1 GPIO端口位的数据输入通道(65)5.1.2 GPIO端口位的输入配置及上/下拉电阻使能(66)5.2 按键状态的判断(67)习题5 (68)项目6 深入了解STM32F407的时钟系统(69)6.1 STM32F4的时钟系统简介(69)6.2 STM32F4的时钟系统(69)6.3 STM32F4的系统时钟和各模块时钟(72)6.3.1 系统时钟SYSCLK (72)6.3.2 由SYSCLK模块提供时钟源的时钟(73)6.3.3 RCC模块的相关寄存器及其作用(75)习题6 (77)项目7 认识STM32的串口结构(78)任务7-1 使用STM32的串口向PC端发送字符串(78)7.1 串口基础知识(83)7.2 STM32的串口结构(84)7.3 引脚复用(90)7.4 端口初始化函数的重新组织(93)习题7 (95)项目8 STM32F407的中断管理(96)任务8-1 使用STM32的外部中断(96)8.1 内嵌中断向量控制器NVIC对中断的控制(102)8.1.1 STM32的中断源(102)8.1.2 STM32的中断使能控制(105)8.1.3 STM32的中断优先级(106)8.1.4 中断函数接口及中断函数的实现(112)8.2 外部中断(113)8.2.1 外部中断的中断源(113)8.2.2 外部中断的设置(114)习题8 (116)项目9 认识STM32的定时器(118)任务9-1 使用定时器中断控制LED0的闪烁(118)9.1 STM32的定时器概述(122)9.2 TIM3内部结构及其计数原理(122)9.2.1 TIM3的内部结构(122)9.2.2 STM32定时器的定时原理(124)9.3 定时器中断的实现(127)9.4 应用定时器产生PWM调制信号(128)9.4.1 TIM14的PWM调制原理(130)9.4.2 TIM14产生PWM信号涉及的寄存器(132)9.4.3 TIM14产生PWM信号的实现流程(133)任务9-2 使用TIM14产生周期为500s、占空比为80%的脉冲信号(134)习题9 (136)项目10 认识STM32的独立看门狗(137)任务10-1 认识STM32的独立看门狗的工作原理(137)10.1 看门狗电路概述(140)10.2 STM32F407的看门狗电路(140)10.3 独立看门狗相关的寄存器(141)10.4 独立看门狗的设置、启动及工作流程(142)习题10 (143)项目11 认识STM32F407的实时时钟(144)任务11-1 认识STM32的RTC (144)11.1 RTC实时时钟介绍(149)11.2 STM32的RTC的工作原理(149)11.3 STM32的RTC的操作步骤(153)习题11 (155)项目12 STM32迷你开发板电路设计(156)项目13 认识ARM处理器(161)13.1 架构简介(161)13.2 Cortex-M4的操作状态、工作模式和访问等级(161)13.3 数据长度(162)13.4 存储器大小端(162)13.5 Cortex-M4的寄存器(163)13.6 堆和栈的概念(166)13.7 内存分配(167)习题13 (170)项目14 汇编语言基础和Cortex-M4指令集(172)14.1 汇编语言基础(172)14.2 Cortex-M4的指令集(174)14.3 Cortex-M4的伪操作和伪指令(180)14.3.1 伪操作(180)14.3.2 伪指令(186)习题14 (187)项目15 认识启动文件startup_stm32f40_41xxx.s (188)习题15 (191)附录A STM32F407ZGT6的引脚结构与功能(192)附录B STM32F407ZGT6核心电路设计(203)附录C STM32F407ZGT6外围电路设计(204)附录D 关于编译信息的解释(205)参考文献(207)。

STM32F405xx、STM32F407xx中文资料

1 带嵌入式闪存和静态随记存取存储器 SRAM(静态随记存取存储器)的 ARM®Cortex™-M4F 内核

ARM Cortex-M4F 处理器是最新一代用于嵌入式系统的 ARM 处理器。它的开发旨在提供 一个低成本平台,以满足 MCU 实现的需求,同时减少引脚数量和降低功耗,并提供卓越407xx

设备概述

目录

1 带嵌入式闪存和静态随记存取存储器 SRAM(静态随记存取存储器)的 ARM®Cortex™-M4F 内核 ..................................................................................................................................................1 2 自适应实时存储器加速器(ART Accelerator™) ........................................................................1 3 内存保护单元...............................................................................................................................1 4 嵌入式闪存...................................................................................................................................1 5 CRC(循环冗余校验)计算单元 ..............................

stm32f407勘误手册

stm32f407勘误手册

摘要:

1.引言

2.STM32F407系列介绍

3.勘误手册的目的和范围

4.勘误内容概述

4.1 硬件设计

4.2 软件设计

4.3 用户手册

5.勘误处理流程

6.附录

正文:

【引言】

STM32F407勘误手册旨在记录并解决STM32F407系列产品在使用过程中可能遇到的问题。

本手册将提供关于硬件设计、软件设计以及用户手册等方面的勘误信息,以帮助用户更好地理解和使用STM32F407系列产品。

【STM32F407系列介绍】

STM32F407系列是基于ARM Cortex-M4内核的32位Flash微控制器,具有高性能、低功耗、丰富的外设接口等特点,广泛应用于工业控制、消费电子、通信等领域。

【勘误手册的目的和范围】

本勘误手册旨在记录并解决STM32F407系列产品在使用过程中可能遇到的问题。

本手册包含硬件设计、软件设计以及用户手册等方面的勘误信息,但不包括产品固件升级、应用技巧以及与产品使用无关的问题。

【勘误内容概述】

4.1 硬件设计

硬件设计勘误主要包括电路设计、PCB布局、器件选型等方面的问题。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

1.参考

1. Stm32f4数据手册:stm32f407zgt6.pdf

2. Stm32f4中文手册:stm32f4xx中文参考手册.pdf

3.开发板示意图:Explorer stm32f4_ Vxx_ SCH.pdf 2.芯片内部资源

1.芯片图片

2.芯片参数表

3.内核

(1)32位高性能Arm Cortex-M4处理器

(2)时钟:最高168MHz,实际上比频率高一点(3)支持FPU(浮点运算)和DSP指令

4. IO端口

(1)Stm32f407zgt6:144针114 IO端口

(2)大多数IO端口可以承受5V(模拟通道除外)

(3)支持调试:SWD和JTAG,SWD只需要2条数据线

5.记忆

(1)内存容量:1024k闪存,192K SRAM

6.时钟,复位和电源管理

(1)1.8〜3.6V电源和IO电压

(2)上电复位和可编程掉电监控

(3)强大的时钟系统

-4〜26m外部高速晶体振荡器

内部16 MHz高速RC振荡器

-内部锁相环(PLL),在PLL频率加倍后,一般系统时钟是外部或内部高速时钟-外部低速32.768k晶体振荡器,主要用作RTC时钟源

7.低功耗

(1)三种低功耗模式:睡眠,停止和待机

(2)RTC和备用寄存器可以由电池供电

8.广告

(1)3个12位AD [最多24个外部测试通道]

(2)内部通道可用于内部温度测量

(3)内置参考电压

9,DA

(1)两个12位Da

10,DMA

(1)16个具有FIFO和突发支持的DMA通道

(2)支持的外设:定时器,ADC,DAC,SDIO,I2S,SPI,I2C和USART 11.多达17个计时器

(1)10个通用计时器(TIM2和tim5为32位)

(2)2个基本计时器(3)2个高级计时器(4)1个系统计时器(5)2个看门狗定时器12.多达17个通讯接口(1)三个I2C接口(2)6个串口

(3)3个SPI接口(4)2个CAN2.0(5)2个USB OTG (6)SDIO。