实验一Virtuoso原理图和图标编辑器的基本使用

Virtuoso软件的使用技巧

添加元件

修改元件属性

每次 重新 打开 电路 图都 要进 行设 置。

连线需要注意:1、规则 2、快捷

Check and save

添加管脚需要注意: 1、命名 2、方向

Make a symbol:Design →Create Cellview →From Pin List

管脚命名必须与电路图中一致

• Virtuoso的主要功能有: 1、绘制电路图 2、绘制版图 3、模拟电路的仿真分析(specture)

• Virtuoso其他功能:Verilog-Editor、 VerilogAEditor、 VHDL-Editor、 VHDLAMS-Editor、 Graphics-Editor、Text-Editor

LVS-2

• • • • • • • • • • • • • • • • • • • • • • 111 # add full/relative path to replace xxx 112 setenv SOURCE_PATH "/home/zhaozhe/lvs_as/op_schematic" 113 #setenv SOURCE_PATH "mpw_08" 114 #setenv SOURCE_PATH "good" 115 116 # add schematic topcell name to replace xxx 117 setenv SOURCE_PRIMARY "opamp" 118 119 #setenv SOURCE_PRIMARY "top_ma" 120 #setenv SOURCE_PRIMARY "HDPWM_top_with_buffer" 121 #setenv SOURCE_PRIMARY "dual_vco_top" 122 #setenv SOURCE_PRIMARY "dual_vco_vc_gen" 123 124 # add full/relative path to replace xxx 125 setenv LAYOUT_PATH "/home/zhaozhe/lvs_as/OP_CL_3p.calibre.gds" 126 #setenv LAYOUT_PATH "mpw_08.gds" 127 #setenv LAYOUT_PATH "../gdsDPWM/dual_vco_top.gds" 128 129 # add layout topcell name to replace xxx 130 setenv LAYOUT_PRIMARY "OP_CL_3p" 131 #setenv LAYOUT_PRIMARY "mpw_08" 132 #setenv LAYOUT_PRIMARY "HDPWM_top_with_buffer"

Cadence-virtuoso的使用简介(版图绘制)

第二章Virtuoso Editing的使用简介全文将用一个贯穿始终的例子来说明如何绘制版图这个例子绘制的是一个最简单的非门的版图§ 2 1 建立版图文件使用library manager首先建立一个新的库myLib关于建立库的步骤在前文介绍cdsSpice时已经说得很清楚了就不再赘述与前面有些不同的地方是由于我们要建立的是一个版图文件因此我们在technology file选项中必须选择compile a new tech file,或是attach to an exsiting tech file这里由于我们要新建一个tech file因此选择前者这时会弹出load tech file的对话框如图2-1-1所示图2-1-1在ASCII Technology File中填入csmc1o0.tf即可接着就可以建立名为inv的cell了为了完备起见读者可以先建立inv的schematic view和symbol view具体步骤前面已经介绍其中pmos长6u宽为0.6u nmos长为3u宽为0.6u model 仍然选择hj3p和hj3n 然后建立其layout view其步骤为在tool中选择virtuoso layout然后点击ok§ 22绘制inverter掩膜版图的一些准备工作首先在library manager中打开inv这个cell的layout view即打开了virtuoso editing窗图2-2-1 virtuoso editing窗口口如图2-2-1所示版图视窗打开后掩模版图窗口显现视窗由三部分组成Icon menu , menu banner ,status banner.Icon menu(图标菜单)缺省时位于版图图框的左边列出了一些最常用的命令的图标,要查看图标所代表的指令只需要将鼠标滑动到想要查看的图标上图标下方即会显示出相应的指令menu banner菜单栏,包含了编辑版图所需要的各项指令并按相应的类别分组几个常用的指令及相应的快捷键列举如下Zoom In -------放大 (z)Zoom out by 2------- 缩小2倍(Z)Save ------- 保存编辑(f2) Delete ------- 删除编辑(Del)Undo ------- 取消编辑(u)Redo -------恢复编辑 (U)Move ------- 移动(m)Stretch ------- 伸缩(s)Rectangle -------编辑矩形图形(r)Polygon ------- 编辑多边形图形(P)Path ------- 编辑布线路径(p) Copy -------复制编辑 (c) status banner状态显示栏位于menu banner的上方显示的是坐标当前编辑指令等状态信息在版图视窗外的左侧还有一个层选择窗口Layer and Selection Window LSWLSW视图的功能1可选择所编辑图形所在的层2可选择哪些层可供编辑3可选择哪些层可以看到由于我们所需的部分版图层次在初始LSW中并不存在因此下一步要做的是建立我们自己的工艺库所需的版图层次及其显示属性为了简单起见以下仅列出绘制我们这个版图所需的最少版图层次层次名称说明Nwell N阱Active 有源区Pselect P型注入掩膜Nselect N型注入掩膜Contact 引线孔连接金属与多晶硅/有源区Metal1 第一层金属用于水平布线如电源和地Via 通孔连接metal1和metal2Metal2 第二层金属用于垂直布线如信号源的I/O口Text 标签Poly 多晶硅做mos的栅下图是修改后的LSW图2-2-2 LSW如何来修改LSW中的层次呢以下就是步骤1切换至CIW窗口在technology file的下拉菜单中选择最后一项edit layers出现如图窗口图2-2-3 edit layers2在technology library中选择库mylib先使用delete 功能去除不需要的层次然后点击add添加必需的层次add打开如下图的窗口图2-2-4其中layer name中填入所需添加的层的名称Abbv是层次名称缩写Number是系统给层次的内部编号系统保留128256的数字作为其默认层次的编号而将1127留给开发者创造新层次Purpose是所添加层次的功用如果是绘图层次一般选择drawing Priority是层次在LSW中的排序位置其余的选项一般保持默认值在右边是图层的显示属性可以直接套用其中某些层次的显示属性也可以点击edit resources自己编辑显示属性如图2-2-5所示这个窗口还可以在LSW中调出编辑方法很简单读者可以自己推敲就不再赘述上述工作完毕后就得到我们所需的层次接着我们就可以开始绘制版图了§ 2 3 绘制版图一画pmos的版图新建一个名为pmos的cell1画出有源区在LSW中点击active dg注意这时LSW顶部显示active字样说明active层为当前所选层次然后点击icon menu中的rectangle icon在vituoso editing窗口中画一个宽为 3.6u长为6u的矩形这里我们为了定标必须得用到标尺点击misc/ruler即可得到清除标尺点击misc/clear ruler如果你在绘制时出错点击需要去除的部分然后点击delete icon2画栅在LSW中点击poly dg画矩形与有源区的位置关系如下图0.6u6u(gate width)1.5u3.6u图2-2-5 display resource editor3画整个pmos为了表明我们画的是pmos管我们必须在刚才图形的基础上添加一个pselect层这一层将覆盖整个有源区0.6u接着我们还要在整个管子外围画上nwell它覆盖有源区1.8u 如下图所示pselect1.8unwell4衬底连接pmos的衬底nwell必须连接到vdd首先画一个1.2u乘1.2u的active矩形然后在这个矩形的边上包围一层nselect层覆盖active06u最后将nwell的矩形拉长完成后如下图所示nselectactivepselect这样一个pmos的版图就大致完成了接着我们要给这个管子布线二布线pmos管必须连接到输入信号源和电源上因此我们必须在原图基础上布金属线1首先我们要完成有源区源区和漏区的连接在源区和漏区上用contact dg层分别画三个矩形尺寸为0.6乘0.6注意contact间距为1.5u2用metal1dg层画两个矩形他们分别覆盖源区和漏区上的contact覆盖长度为0.3u3为完成衬底连接我们必须在衬底的有源区中间添加一个contact这个contact每边都被active覆盖0.3u4画用于电源的金属连线宽度为3u将其放置在pmos版图的最上方布线完毕后的版图如下图所示图2-3-1 pmos版图通过以上步骤我们完成了pmos的版图绘制接下来我们将绘制出nmos的版图三画nmos的版图绘制nmos管的步骤同pmos管基本相同新建一个名为nmos的cell无非是某些参数变化一下下面给出nmos管的图形及一些参数具体绘制步骤就不再赘述图2-3-2nmos四完成整个非门的绘制及绘制输入输出1新建一个cell inv将上面完成的两个版图拷贝到其中并以多晶硅为基准将两图对齐然后我们可以将任意一个版图的多晶硅延长和另外一个的多晶硅相交2输入为了与外部电路连接我们需要用到metal2但poly和metal2不能直接相连因此我们必须得借助metal1完成连接具体步骤是a在两mos管之间画一个0.6乘0.6的contactb在这个contact上覆盖poly过覆盖0.3uc在这个contact的左边画一个0.6乘0.6的via然后在其上覆盖metal2dg过覆盖0.3ud用metal1连接via和contact过覆盖为0.3u从下图中可以看得更清楚metal13输出连起来任意延长一个的metal1与另一个相交然后在其上放置一个via接着在via上放置metal2五作标签1在LSW中选择层次text d3点击create/label在弹出窗口中的label name中填入vdd并将它放置在版图中相应的位置上2按同样的方法创制gnd A和Out的标签完成后整个的版图如下图2-3-4 非门的版图至此我们已经完成了整个非门的版图的绘制下一步将进行DRC检查以检查版图在绘制时是否有同设计规则不符的地方第三章 Diva验证工具使用说明 版图绘制要根据一定的设计规则来进行也就是说一定要通过DRC Design RuleChecker检查编辑好的版图通过了设计规则的检查后有可能还有错误这些错误不是由于违反了设计规则而是可能与实际线路图不一致造成版图中少连了一根铝线这样的小毛病对整个芯片来说都是致命的所以编辑好的版图还要通过LVS Layout VersusSchematic验证同时编辑好的版图通过寄生参数提取程序来提取出电路的寄生参数电路仿真程序可以调用这个数据来进行后模拟下面的框图可以更好的理解这个流程图 3-0-1 IC后端工作流程验证工具有很多我们采用的是Cadence环境下集成的验证工具集DIV A下面先对DIV A作一个简单介绍DIV A是Cadence软件中的验证工具集用它可以找出并纠正设计中的错误它除了可以处理物理版图和准备好的电气数据从而进行版图和线路图的对查LVS外还可以在设计的初期就进行版图检查尽早发现错误并互动地把错误显示出来有利于及时发现错误所在易于纠正DIV A工具集包括以下部分1设计规则检查iDRC2版图寄生参数提取iLPE3寄生电阻提取iPRECadence cdsSPICE 使用说明资料收藏 PCB 收藏天地4 5电气规则检查 iERC 版图与线路图比较程序 iLVS 需要提到的是 Diva 中各个组件之间是互相联系的 有时候一个组件的执行要依赖另 一个组件先执行 例如 要执行 LVS 就先要执行 DRC 在 Cadence 系统中 Diva 集成在版 图编辑程序 Virtuoso 和线路图编辑程序 Composer 中 在这两各环境中都可以激活 Diva 要 运行 Diva 前 还要准备好规则验证的文件 可以把这个文件放在任何目录下 这些规则文 件的写法下面专门会进行说明 也会给出例子 这些文件有各自的默认名称 如 做 DRC 时的文件应以 divaDRC.rul 命名 版图提取文件以 divaEXT.rul 命名 做 LVS 时规则文件应 以 divaLVS.rul 命名§31DRC 规则文件的编写我们制定了以下规则 n 阱的最小宽度 阱与阱之间的最小间距 ndiff 到 nwell 的最小间距 pdiff 到 nwell 的最小间距 p mos 器件必须在 nwell 内 有源区的最小宽度 有源区之间的最小间距 多晶硅的最小宽度 多晶硅间的最小宽度 多晶硅与有源区的最小间距 多晶硅栅在场区上的最小露头 源 漏与栅的最小间距 引线孔的最小宽度 引线孔间的最小间距 多晶硅覆盖引线孔的最小间距 metal1 覆盖引线孔的最小间距 金属 1 的最小宽度 金属 1 间的最小间距 金属 2 的最小宽度 金属 2 间的最小间距 金属 2 的最小挖槽深度 通孔的最小宽度 通孔间的最小间距 通孔与引线孔间的最小间距 metal1 覆盖通孔的最小间距 4.8u 1.8u 0.6u 1.8u仍旧以前面的非门为例 1.a n 阱(well) 1.b 1.c 1.d 1.e 2.a 2.b 3.a 3.b 3.c 3.d 3.e 4.a 4.b 4.c 4.d 5.a 5.b 6.a 6.b 6.c 7.a 7.b 7.c 7.d 有源区 active1.2u 1.2u 0.6u 0.6u 0.6u 0.6u 0.6u 0.6u 0.9u 0.3u 0.3u 1.2u 0.9u 1.2u 1.2u 1.2u 0.6u 0.9u 0.6u 0.3u第 11 页 共 11 页多晶硅poly引线孔 contact金属 1metal1金属 2metal2通孔 viaCadence cdsSPICE 使用说明资料收藏 PCB 收藏天地7.e metal2 覆盖通孔的最小间距 0.3u 7.f 通孔与多晶硅的最小间距 0.3u 结合上述规则 我们就可以编写出相应的 DRC 规则检查文件 见附录 1 取名为 divaDRC.rul 这个文件的第一部分是层次处理 用于生成规则文件中所要应用到的层 次 可以是原始层或是衍生层 例如 nwell=geomOr("nwell") 在文件中引用到的所 有原始物理层次都要用双引号括起来 这一句的目的是在后面应用到 nwell 这个原始物 理层次时 不需要再用引号括起来 前面几句都是这个意思 后面四句则生成版图验证 中必须的一些层次 有一点需要注意的是 在 geomOr 的关键字和 ( 之间不能出现 空格 nwell=geomOr (“nwell”)的写法系统在编译时会报错 下面这个语句相当于一个条件转移语句 当有drc命令时 执行下面的规则 否则跳 转到下一个命令 ivIf( switch( "drc?" ) then 在设计规则检查中 主要的语句就是drc 了 先简单介绍一下这个语句的语法 [outlayer]=drc(inlayer1 [inlayer2] function [modifiers] ) outlayer表示输出层 如果定义 给出 输出层 则通过drc检查的出错图形就可以保 存在该输出层中 此时 如果没有modifiers选项 则保存的是原始的图形 如果在modifiers 选项中定义了修改方式 那么就把修改后的结果保存在输出层中 如果没有定义outlayer 层 出错的信息将直接显示在出错的原来层次上 Inlayer1和inlayer2代表要处理的版图层次 有些规则规定的是只对单一层次的要求 比如接触孔的宽度 那么可以只有inlayer1 而有些规则定义的是两个层次之间的关系 如 接触孔和铝线的距离 那么要注明两个层次 Function中定义的是实际检查的规则 关键字有sep 不同图形之间的间距 , width 图形的宽度 , enc 露头 , ovlp(过覆盖), area 图形面积 , notch 挖槽的宽度 等 关系有>, <, >=, <=, ==等 结合起来就是 sep<3, width<4, 1<enc<5 这些关系式 例如 drc(nwell width < 4.8 "Minimum nwell width =4.8") 在此例中 没有outlayer 的定义 也没有modifiers的定义 所以发现的错误都直接显示在nwell层上 例子中 inlayer 就是nwell 检查的只是n阱层的规则 function是width<4.8 表示n阱宽度小于4.8微米 所以上面这句的执行结果就是把n阱层中宽度小于4.8u的图形当做错误输出 后面引号中的 信息起到说明提示作用 需要时可以查询 对查错没有实际意义 同样需要注意的是 在drc 和 之间同样不能有空格 否则系统会提示没有drc语句 从上面讨论不难看出 DIVA 规则文件的编写对格式有一定要求 在规则文件中我们还可以看到saveDerived语句 如 saveDerived(geomAndNot(pgate nwell) "p mos device must in nwell") 这一句将输出不在nwell内部的pgate pmos 这种写法在规则文件的编写中经常碰到 要熟练掌握 另外 在DRC文件中 引号引出的行是注释行 以上就是对DRC文件编写的一些简单介绍 对于其中使用的关键字 作者有专门的说明 文章 同时在本文后面作者还会给出一个完整的DRC校检文件并给出详细说明 读者可以参 照它 以加深对文件编写的理解§32 版图提取文件的介绍上面已经提到 通过DRC验证的版图还需要进行LVS也就是版图和线路图对查比较 实际 上就是从版图中提取出电路的网表来 再与线路图的网表比较 那么如何提取版图网表呢 这里我们就要使用到DIVA的extract文件 下面是它的简单介绍 首先 同DRC一样 extract文件的最开始同样是这样一条语句第 12 页 共 12 页Cadence cdsSPICE 使用说明资料收藏 PCB 收藏天地ivIf switch extract then 它相当于一个条件转移语句 当有extract这个命令时 执行下面的规则 否则跳转到另外 的循环 接着 extract文件中要进行的是层次定义 它一般分为三个步骤 1 识别层定义 recognition layer 2 终端层定义 terminal layer 3 伪接触层定义 psuedo_contact layer 然后是定义层次间的连接关系 使用geomConnect语句将版图间的不同层次连接起来 一个 extract文件只能有一个geomConnect语句 构成完整的网表 例如句子 geomConnect via contact psd nsd poly metal1 via via metal1 metal2 其中 via语句的作用是使用连接层连接任意数目的层次 但要注意的是 一个via语句中只 能出现一个连接层 但在geomConnect语句中via语句可以出现的次数不限 以上语句表示 在有contact的地方 psd nsd poly metal1 是相互连接的 在有via 的地方metal1和metal2 相连 注意后一个via和前一个的意义不同 上述工作完成之后 我们接着要进行的工作是器件的提取 device extraction 使 用extractDevice语句 extractDevice 语句定义电路中用到的元器件 这是提取文件中的 关键语句 语法说明如下 extractDevice( reclayer termlayer model physical ) 其中reclayer是识别层 它应该是后来通过逻辑关系生成的提取层 这个层上的每一个图形 都会被当作是一个元器件 Termlayer是端口层 它表示的是元器件的端口 一定要是可以连接的层次 具体的端口定 义因元器件而异 Model指的是元器件的类型 与端口要对应 例如下两句 extractDevice( pgate (GT "G")(psd "S" "D")(NT "B")"pfet ivpcell" ) extractDevice( ngate (GT "G")(nsd "S" "D")(pwell "B")"nfet ivpcell" ) 分别提取出pmos管和nmos管 接着很重要的一步是器件尺寸测量 使用measureParameter语句 例如 w1 measureParameter length ngate butting nsd .5 这一句测量的是nmos的沟道宽度 注意后面的.5必须加上 否则测出的将是两倍的沟道宽度 下面使用saveInterconnect 这个命令把连接的层次写到提取出来的网表中 以便在做 LVS时 可以与线路图中的网表互相对比 saveInterconnect( nsd psd poly contact metal1 ) saveRecognition 这个命令将提取产生的可以识别的图形保存下来 通常和 extractDevice语句中的识别层一致 saveRecognition( ngate "ngate" ) saveRecognition( pgate "pgate" ) 以上就是对extract文件的一个简要介绍 读者可以参看附录中完整的例子 以加深对它的 理解§3接下来 就是LVS检查了3LVS文件的介绍LVS文件在diva中 由于版图提取在extract中就已经完成第 13 页 共 13 页Cadence cdsSPICE 使用说明资料收藏 PCB 收藏天地中的逻辑结构相对就比较简单 只需进行网表比较 参数比较 以及把一些 并联或串联 的元器件归并等即可 所以这一部分文件不会因为工艺层次不同而有很大不同 可以根据范 本做少许改动 以下只介绍一下LVS的基本结构 lvsRules procedure(mosCombine(value1,value2) ……. ) Procedure(mosCompare(lay,sch) ……. ) permuteDevice(parallel “pmos” mosCombine) compareDeviceProperty(“pmos” mosCompare) ) 至于例子 读者可以参考附录§3一 DRC 的说明4Diva 的用法编 辑 好 的 验 证 文 件 都 存 在 ..\export\home\wmy\myLib\ 下 文件名分别是 divaDRC.rul divaEXT.rul divaLVS.rul 有了这三个文件就可以进行版图验证了 下面 将以一个非门为例子来进行说明 在编辑版图文件的同时就可以进行DRC检查 在virtuoso版图编辑环境中 单击Verify 菜单 上面提到的DIVA工具都集成在这个菜单下 先介绍设计规则检查DRC 单击第一个子 菜单DRC就会弹出DRC的对话框 如下图 3-4-1 DRC 菜单窗口第 14 页 共 14 页Cadence cdsSPICE 使用说明资料收藏 PCB 收藏天地Checking Method 指的是要检查的版图的类型 Flat 表示检查版图中所有的图形 对子版图块不检查 与电路图中类似 最上层电路 由模块组成 而模块由小电路构成 有些复杂的版图也是如此 Hierarchical 利用层次之间的结构关系和模式识别优化 检查电路中每个单元块内部是 否正确 hier w/o optimization 利用层次之间的结构关系而不用模式识别优化 来检查电路中每 个单元块 Checking Limit 可以选择检查哪一部分的版图 Full 表示查整个版图 Incremental 查自从上一次 DRC 检查以来 改变的版图 by area 是指在指定区域进行 DRC 检查 一般版图较大时 可以分块检查 如果选择这种方式后 Coordinate 这个输入框就变为可输入 可以在这个框内输入坐标 用矩形的左下角和右上角的坐标来表示 格式为 12599:98991 115682:194485 或者先单击 Sel by Cursor,然后用鼠标在版图上选中一个矩形 这个输入框也会出现相应 的坐标 如果不出现可以多选几次 Switch Names 在DRC文件中 我们设置的switch在这里都会出现 这个选项可以方便我们对版图文件进行 分类检查 这在大规模的电路检查中非常重要 Run-Specific Command FileInclusion Limit上面的两项并不是必需的 可以根据默认设定 Echo Commands 选上时在执行DRC的同时在CIW窗口中显示DRC文件 Rules File 指明DRC规则文件的名称 默认为divaDRC.rul Rules Library 这里选定规则文件在哪个库里 Machine 指明在哪台机器上运行DRC命令 local 表示在本机上运行 对于我们来说 是在本机运行的 选local remote 表示在远程机器上运行 Remote Machine Name 远程机器的名字 在填好规则文件的库和文件名后 根据实际情况填好 Checking Method 和 Checking Limit就可以单击OK运行 这时可以在CIW窗口看到运行的信息 同时在版图上也会出现发 亮的区域 如果有错误 错误在版图文件中可以看到 另外也可以选择Verify-Markers-Find菜单来帮助找错 单 击菜单后会弹出一个窗口 在这个窗口中单击apply就可以显示第一个错误 这个窗口较简 单 大家看一下 再试几次就可以了 同样 可以选择Verify-Markers-Explain来看错误的原因提示 选中该菜单后 用鼠标 在版图上出错了的地方单击就可以了 也可以选择Verify-Markers-Delete把这些错误提示删 除 Virtuoso版图编辑环境下的菜单见图3-4-2第 15 页 共 15 页Cadence cdsSPICE 使用说明资料收藏 PCB 收藏天地图 3 –4-2Virtuoso 菜单二版图提取Extractor说明为了进行版图提取 还要给版图文件标上端口 这是LVS的一个比较的开始点 在LSW 窗口中 选中 metal1 pn 层 然后在 Virtuoso 环境菜单中选择 pn 指得是引脚 pin Create-Pin 这时会出来一个窗口 如下图 3-2-3 创建版图端口窗口 填上端口的名称 Terminal Names 和Schematic中的名字一样 模式 Mode 一般选 rectangle 输入输出类型 I/O Type 等 至于Create Label属于可选择项 选上后 端口 的名称可以在版图中显示 填好可以直接在版图中画上端口 往往有好几个端口 可以都画好在单击Hide 这 些端口仅表示连接关系 并不生成加工用的掩模板 只要求与实际版图上铝线接触即可 也没有规则可言第 16 页 共 16 页Cadence cdsSPICE 使用说明资料收藏 PCB 收藏天地版图的完成后 就可以提取了 在版图编辑环境下选择Verify –extractor 下弹出菜单如图 3-2-4Extractor 窗口图 3-2-5 提取出的文件 填好提取文件库和文件名后 单击OK就可以了 然后打开Library Manager 在库myLib下 nmos单元中增加了一个文件类型叫extracted的文件 可以用打开版图文件同样的方式打开 它 图3-2-5就是提取出来的版图 可以看到提取出来的器件和端口 要看连接关系的话 可以选择Verify-probe菜单 在弹出窗口中选择查看连接关系 版图的准备工作基本上就完成了 接下来是线路图的准备工作 线路图的准备工作相第 17 页 共 17 页Cadence cdsSPICE 使用说明资料收藏 PCB 收藏天地对较简单 有几个要注意的地方 首先 在库的选用上 要用Sample库中的元件 其次 线 路图的端口名称要与版图中的端口名称一致 最后 在线路编辑完成后要进行检查 可以直 接单击左边第一个快捷键 也可以选择菜单Check--Current Cellview 在版图和线路图的准备工作完成后就可以进行LVS了图3-2-6 LVS 参照图3-2-6的弹出菜单 填好规则文件的库和文件名 要进行LVS的两个网表 其实 在LVS中比较的是两个网表 一个是schematic中 另一个是extracted 所以两个schematic文 件也可以比较 只是一般没这个必要 设置完以后单击RUN 片刻后就回弹出一个窗口表 示LVS完成或者失败 失败时可以在上面的菜单中单击Info看运行的信息再进行处理 LVS 完成后 可以在上面的弹出菜单中单击Output 这时会弹出LVS的结果 当然 LVS完成并不是说LVS通过了 可能会有很多地方不匹配 这时要查看错误可以 在LVS窗口中单击Error Display 即可在Extracted和Schematic 中查看错误第 18 页 共 18 页Cadence cdsSPICE 使用说明资料收藏 PCB 收藏天地第四章 Cadence 中 Verilog 的一些使用方法§41Verilog 的文本编辑器随着电路规模的增大和复杂 传统的图形输入模式已不可行 语言描述电路 成为潮流 它的方便性和好的更改性 维护性在实践中得到很好的体现 尤其现 在强大的综合工具 和系统集成对核的需求性使 Verilog 更有用武之地 每个硬 件工程师应该学习掌握它 在进入 Cadence 后在命令行中键入 textedit *.v↙ (此处*为文件名 在 textedit 命令后应带上文件名) 键入上述命令后进入文本编辑框 和 Windows 中常用的文本编辑框很象图 4-1-1textedit 文本编辑框界面 图中的主菜单 File View Edit Find 及各自底下的子菜单和 Windws 中的 文本编辑器差不多 使用方法相似 这里就不多说了 编好程序保存可以进 行后续工作了§4一2Verilog 的模拟仿真命令的选择 在命令行中键入 verilog↙ 会出现关于此命令的一些介绍 如下 -f <filename> read host command arguments from file. -v <filename> specify library file -y <filename> specify library directory -c compile only -s enter interactive mode immediately第 19 页 共 19 页Cadence cdsSPICE 使用说明资料收藏 PCB 收藏天地-k <filename> set key file name -u convert identifiers to upper case -t set full trace -q quiet -d decompile data structure Special behavioral performance options (if licensed): +turbo speed up behavioral simulation. +turbo+2 +turbo with second level optimizations. +turbo+3 +turbo+2 with third level optimizations. +listcounts generate code for maintaining information for $listcounts +no_turbo don't use a VXL-TURBO license. +noxl disable XL acceleration of gates in all modules Special environment invocation options (if licensed): +gui invoke the verilog graphical environment 在上面的参数选择中 简单介绍几个常用的: (1)-c 首先应该保证所编程序的语法正确性 先进行语法的检查 选择参数- c 键入 如下命令 verilog –c *.v↙ 根据 Cadence 的报告 查找错误信息的性质和位置 然后进入文本编辑器进 行修改 再编译 这是个反复的过程 直到没有语法错误为止 (2)-s 进入交互式的环境 人机交互运行和下面的参数联合使用 (3)+gui & verilog 仿真有命令和图形界面两种方式 图形界面友好和 windows 使用很 象 很好掌握 一般都使用图形方式 &”符号是后台操作的意思 不影响 前台工作 如此时你可以在命令行输入其它的命令 其它的命令参数选择比较复杂 这里就不介绍了 故我们这里常用的命令是 verilog –s *.v +gui &↙ (*代表文件名) 进入图形交互界面 $附 命令行输入 !!↙ 是执行上一条命令 命令行输入 !* ↙ (*代表字母) 是执行最近的以*开头的命令 上述附注对命令输入速度提高有所帮助 二 SimVision 图形环境 SimVision 是 Verilog-XL 的图形环境 主要有 SimControl Navigator Signal Flow Browswer Wactch Objects Window SimWave 等窗口第 20 页 共 20 页。

培训资料Virtuoso软件使用技巧

Tool:Composer-Schematic

.精品课件.

14

主要内容

• 1、Virtuoso简介 • 2、如何正确进入Virtuoso • 3、电路图的绘制 • 4、电路图的仿真与分析 • 5、幅员的绘制 • 6、幅员的验证DRC/LVS • 7、幅员后仿真

.精品课件.

15

添加元件

.精品课件.

e:进入下一层模块 ctrl+e:返回上一层模块 [ : 缩小两倍 ] :放大两倍

.精品课件.

26

主要ห้องสมุดไป่ตู้容

• 1、Virtuoso简介 • 2、如何进入Virtuoso • 3、电路图的绘制 • 4、电路图的仿真与分析 • 5、幅员的绘制 • 6、幅员的验证DRC/LVS • 7、幅员后仿真

.精品课件.

Options→Display →Minor spacing

.精品课件.

42

LSW

• AV (all visible) ;NV (non visible) ; • AS (all selectable) ;.精N品课S件.(non selectable) 。 43

常用的快捷键

• r:绘制长方形 • c:copy • F4:part/full • s:stretch • o:添加contact或via • i:调用模块 • q:修改属性 • k:尺 • shift+k:取消所有尺 • l:加label

.精品课件.

50

由幅员生

成.gds文件

there is no

errors and

warning

messages

.精品课件.

51

LVS-1

.精品课件.

实验一Virtuoso原理图和图标编辑器地基本使用

实验一Virtuoso原理图和图标编辑器的基本使用目录1.实验目的2.创建一个新的自定义单元库3.使用 Cadence Virtuoso 原理图编辑器构建一个反相器4.创建一个自定义元器件图标1.实验目的本实验采用AMI06工艺设计一个反相器,以此使学生达到熟悉 Cadence Virtuoso 原理图和图标编辑器使用,记住常用热键组合以及掌握与特定工艺库关联之目的。

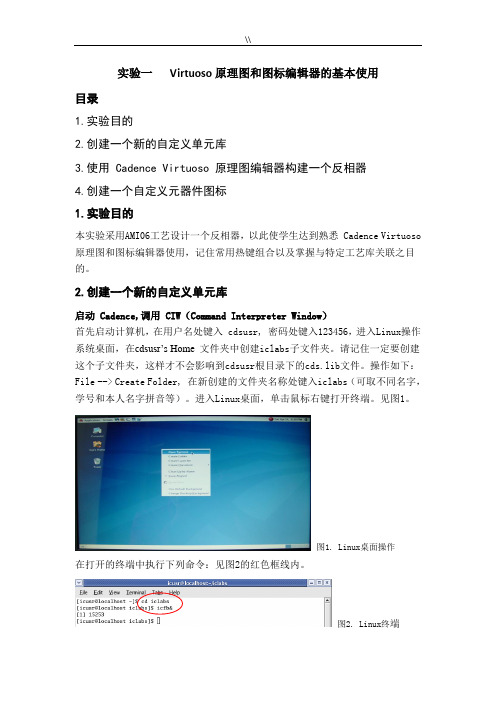

2.创建一个新的自定义单元库启动 Cadence,调用 CIW(Command Interpreter Window)首先启动计算机,在用户名处键入 cdsusr, 密码处键入123456,进入Linux操作系统桌面,在cdsusr’s Home文件夹中创建iclabs子文件夹。

请记住一定要创建这个子文件夹,这样才不会影响到cdsusr根目录下的cds.lib文件。

操作如下:File --> Create Folder, 在新创建的文件夹名称处键入iclabs(可取不同名字,学号和本人名字拼音等)。

进入Linux桌面,单击鼠标右键打开终端。

见图1。

图1. Linux桌面操作在打开的终端中执行下列命令:见图2的红色框线内。

图2. Linux终端执行第二个命令后你就可看见Cadence软件的CIW窗口出现。

见图3所示。

图3. Cadence软件的CIW窗口在CIW窗口中点击Tools-->Library Manager..., 将打开库管理器(图4)。

图4. 库管理器你可看到NCSU提供的库已显示在Library栏目中,有 NCSU_Analog_Parts,...等。

点击库管理器中的File-->New-->Library..., 将打开New Library 对话窗口, 现创建一个新库取名为IClab1。

见图5。

图5. 创建一个自定义元件库点击OK弹出关联工艺库对话框(图6),选择Attach to an existing techfile。

(word完整版)实验三 Virtuoso版图编辑器的基本使用

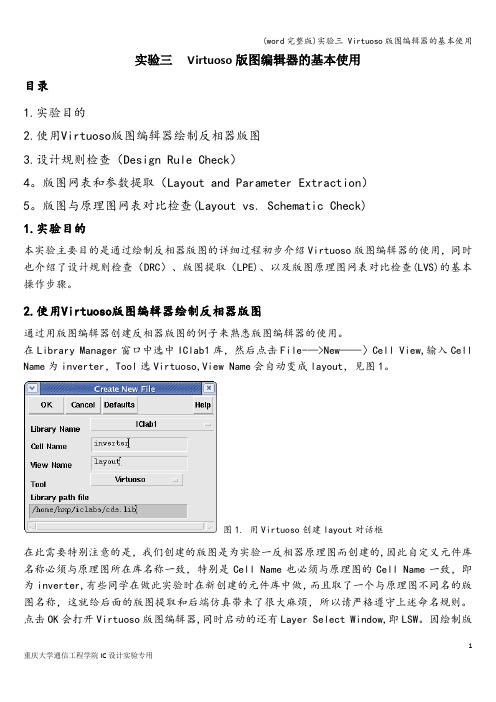

实验三Virtuoso版图编辑器的基本使用目录1.实验目的2.使用Virtuoso版图编辑器绘制反相器版图3.设计规则检查(Design Rule Check)4。

版图网表和参数提取(Layout and Parameter Extraction)5。

版图与原理图网表对比检查(Layout vs. Schematic Check)1.实验目的本实验主要目的是通过绘制反相器版图的详细过程初步介绍Virtuoso版图编辑器的使用,同时也介绍了设计规则检查(DRC)、版图提取(LPE)、以及版图原理图网表对比检查(LVS)的基本操作步骤。

2.使用Virtuoso版图编辑器绘制反相器版图通过用版图编辑器创建反相器版图的例子来熟悉版图编辑器的使用。

在Library Manager窗口中选中IClab1库,然后点击File-—>New——〉Cell View,输入Cell Name为inverter,Tool选Virtuoso,View Name会自动变成layout,见图1。

图1. 用Virtuoso创建layout对话框在此需要特别注意的是,我们创建的版图是为实验一反相器原理图而创建的,因此自定义元件库名称必须与原理图所在库名称一致,特别是Cell Name也必须与原理图的Cell Name一致,即为inverter,有些同学在做此实验时在新创建的元件库中做,而且取了一个与原理图不同名的版图名称,这就给后面的版图提取和后端仿真带来了很大麻烦,所以请严格遵守上述命名规则。

点击OK会打开Virtuoso版图编辑器,同时启动的还有Layer Select Window,即LSW。

因绘制版图时一定先要与某一工艺库关联,而LSW将与关联的工艺库联动,所以不同的工艺库会有不同的LSW窗口出现。

本实验中的IClab1自定义库是与NCSU_TechLib_ami06工艺库关联的,所以该工艺库的名称会显示在LSW窗口的上面。

Virtuoso Layout Editing 使用简介

Virtuoso Layout Editing 使用简介本文以INV为例介绍virtuoso Layout Editing 的基本操作方法一、建立目录结构首先选择项目的名称为最top的目录名称,这里假设为MyLib(为了文章的语言简洁,以下将不会过多描述)。

具体命令如下:%mkdir MyLib%cd MyLib%mkdir opus db dracula%cd dracula%mkdir loglvs lvs drc相关目录名称意义:MyLib 主目录opus 运行Virtuoso环境db 存放database,即将你所画的图export出来dracula 进行检测,这里使用dracula这个工具对所画的版图进行验证loglvs 进行LVS(版图对电路)检测时用到的netlist(电路描述)lvs 进行LVSdrc 进行drc(设计规则检查)二、建立数据库现在进到opus目录中,准备technology file(建立数据库时必须的文件)和display file(图层描述)%icfb& ,接着跳出cadance的控制界面图示如下:点击File-->New-->Library ,在跳出的对话框中Name填入MyLib,选中Compile a new techfile,点击ok在ASCII Technology file 里填入准备好的tech file,点击ok,库便建好了。

三、建立新的版图inv点击File-->New-->Cellview在跳出的对话框中Library Name选择MyLib,Cell Name填入inv,View Name选择layout,点击ok接着就是版图inv的工作区了图为layout工作区,所进行的layout都在些工作区内完成。

工具框中介绍几个常用的工具,为保存,点击保存当前工作区的内容。

这三个图标依次为fit全部显示,zoom in放大视图,zoom out缩小视图。

Virtuoso软件的使用技巧

精品课件

LVS-1

精品课件

LVS-1

精品课件

Run LVS

精品课件

LVS-2

•

111 # add full/relative path to replace xxx

•

112 setenv SOURCE_PATH "/home/zhaozhe/lvs_as/op_schematic"

精品课件

保存仿真参数:Session → Save state

精品课件

netlist and run 与run

精品课件

simulation → Output log

精品课件

瞬态/静态电压、瞬态/静态电流精、品课幅件 度、相位、工作状态……

仿真结果的测量

精品课件

主要内容

• 1、Virtuoso简介 • 2、如何进入Virtuoso • 3、电路图的绘制 • 4、电路图的仿真与分析 • 5、版图的绘制 • 6、版图的验证DRC/LVS • 7、版图后仿真

精品课件

打开icfb

使icfb和终端可以同时使 用

精品课件

Tools →Library Manager

精品课件

精品课件

新建库: File→New →Library

精品课件

精品课件

精品课件

File→New →Cell View

精品课件

Tool:Composer-Schematic

精品课件

LVS(Layout versus Schematic)。

精品课件

Calibre →Run DRC

精品课件

Rules →Run DRC

精品课件

Virtuoso软件的使用技巧

打开icfb

使icfb和终端可以同时使用

Tools →Library Manager

新建库: File→New →Library

File→New →Cell View

Tool:Composer-Schematic

主要内容

• 1、Virtuoso简介 • 2、如何正确进入Virtuoso • 3、电路图的绘制 • 4、电路图的仿真与分析 • 5、版图的绘制 • 6、版图的验证DRC/LVS • 7、版图后仿真

•

128

•

129 # add layout topcell name to replace xxx

•

130 setenv LAYOUT_PRIMARY "OP_CL_3p"

•

131 #setenv LAYOUT_PRIMARY "mpw_08"

•

132 #setenv LAYOUT_PRIMARY "HDPWM_top_with_buffer"

warning messages

LVS-1

LVS-1

Run LVS

LVS-2

•

111 # add full/relative path to replace xxx

•

112 setenv SOURCE_PATH "/home/zhaozhe/lvs_as/op_schematic"

•

113 #setenv SOURCE_PATH "mpw_08"

常用的快捷键

• r:绘制长方形 • c:copy • F4:part/full • s:stretch • o:添加contact或via • i:调用模块 • q:修改属性 • k:尺 • shift+k:取消所有尺 • l:加label

Virtuoso软件的使用技巧

Tools →Library Manager

新建库: File→New →Library

File→New →Cell View

Tool:Composer-Schematic

主要内容

1、Virtuoso简介 2、如何正确进入Virtuoso 3、电路图的绘制 4、电路图的仿真与分析 5、版图的绘制 6、版图的验证DRC/LVS 7、版图后仿真

主要内容

1、Virtuoso简介 2、如何进入Virtuoso 3、电路图的绘制 4、电路图的仿真与分析 5、版图的绘制 6、版图的验证DRC/LVS 7、版图后仿真

Calibre →Run PEX

128

129 # add layout topcell name to replace xxx

130 setenv LAYOUT_PRIMARY "OP_CL_3p"

131 #setenv LAYOUT_PRIMARY "mpw_08"

132 #setenv LAYOUT_PRIMARY "HDPWM_top_with_buffer"

调用生成的模块

常用的快捷键

i (instance):插入元件 f (full screen):全屏幕 w (wire) :连线 p (pin):加管脚 q (quality):编辑属性

e:进入下一层模块 ctrl+e:返回上一层模

块

[ : 缩小两倍 ] :放大两倍

主要内容

1、Virtuoso简介 2、如何进入Virtuoso 3、电路图的绘制 4、电路图的仿真与分析 5、版图的绘制 6、版图的验证DRC/LVS 7、版图后仿真

Virtuoso软件的使用技巧(PPT分析)

35

simulation → Output log

2021-01-04

36

2021-01-0瞬4 态/静态电压、瞬态/静态电流、幅度、相位、工作状态……

37

仿真结果的测量

2021-01-04

38

主要内容

• 1、Virtuoso简介 • 2、如何进入Virtuoso • 3、电路图的绘制 • 4、电路图的仿真与分析 • 5、版图的绘制 • 6、版图的验证DRC/LVS • 7、版图后仿真

2021-01-04

3

• Exceed Broadcast →选择用户

2021-01-04

4

设置环境变量:setenv DISPLAY IP:0

2021-01-04

5

打开icfb

使icfb和终端可以同时使用

2021-01-04

6

Tools →Library Manager

2021-01-04

7

2021-01-04

8

新建库: →Library

2021-01-04

9

2021-01-04

10

2021-01-04

11

→Cell View

2021-01-04

12

Tool:Composer-Schem

主要内容

• 1、Virtuoso简介 • 2、如何正确进入Virtuoso • 3、电路图的绘制 • 4、电路图的仿真与分析 • 5、版图的绘制 • 6、版图的验证DRC/LVS • 7、版图后仿真

• Virtuoso其他功能:Verilog-Editor、 VerilogAEditor、 VHDL-Editor、 VHDLAMS-Editor、 Graphics-Editor、Text-Editor

Virtuoso软件的使用技巧

打开icfb

使icfb和终端可以同时使用

Tools →Library Manager

新建库: File→New →Library

File→New →Cell View

Tool:Composer-Schematic

主要内容

1、Virtuoso简介 2、如何正确进入Virtuoso 3、电路图的绘制 4、电路图的仿真与分析 5、版图的绘制 6、版图的验证DRC/LVS 7、版图后仿真

Virtuoso的主要功能有: 1、绘制电路图 2、绘制版图 3、模拟电路的仿真分析(specture)

Virtuoso其他功能:Verilog-Editor、 VerilogAEditor、 VHDL-Editor、 VHDLAMS-Editor、 Graphics-Editor、Text-Editor

warning messages

LVS-1

LVS-1

Run LVS

LVS-2

111 # add full/relative path to replace xxx

112 setenv SOURCE_PATH "/home/zhaozhe/lvs_as/op_schematic"

113 #setenv SOURCE_PATH "mpw_08"

114 #setenv SOURCE_PATH "good"

115

116 # add schematic topcell name to replace xxx

117 setenv SOURCE_PRIMARY "opamp"

Virtuoso软件的使用技巧

精品PPT

主要内容

• 1、Virtuoso简介 • 2、如何进入Virtuoso • 3、电路图的绘制 • 4、电路图的仿真与分析 • 5、版图的绘制 • 6、版图的验证DRC/LVS • 7、版图后仿真

精品PPT

• 版图的设计错误可以分成两类: 违反几何设计规则的错误——检查工具

精品PPT

Browse →Add

精品PPT

设定仿真参数:Analyses →Choose

精品PPT

精品PPT

精品PPT

节点电流:Outputs →To Be Saved Select On Schematic

精品PPT

保存仿真参数:Session → Save state

精品PPT

netlist and run 与run

精品PPT

必须确保绘制版图需要的工艺文件与 版图所在的库是精在品PPT同一个目录下的

Options→Display →Minor spacing

精品PPT

LSW

• AV (all visible) ;NV (non visible) ; • AS (all selectable) ;精N品PSPT (non selectable) 。

DRC(Design Rules Check)。 版图与原理图一致性的错误——检查工具

LVS(Layout versus Schematic)。

精品PPT

Calibre →Run DRC

精品PPT

Rules →Run DRC 精品PPT

查找错误

精品PPT

LVS(Layout vs. Schematic) Input the netlist

连线需要注意:1、规则 2

Virtuoso软件的使用技巧

仿真环境:Tools →Analog Environment

添加库文件:Setup →Model Libraries

Browse →Add

设定仿真参数:Analyses →Choose

节点电流:Outputs →To Be Saved Select On Schematic

保存仿真参数:Session → Save state

•

128

•

129 # add layout topcell name to replace xxx

•

130 setenv LAYOUT_PRIMARY "OP_CL_3p"

•

131 #setenv LAYOUT_PRIMARY "mpw_08"

•

132 #setenv LAYOUT_PRIMARY "HDPWM_top_with_buffer"

•

125 setenv LAYOUT_PATH "/home/zhaozhe/lvs_as/OP_CL_3p.calibre.gds"

•

126 #setenv LAYOUT_PATH "mpw_08.gds"

•

127 #setenv LAYOUT_PATH "../gdsDPWM/dual_vco_top.gds"

•

114 #setenv SOURCE_PATH "good"

•

115

•

116 # add schematic topcell name to replace xxx

•

117 setenv SOURCE_PRIMARY "opamp"

Virtuoso软件的使用技巧

添加元件

修改元件属性

每次 重新 打开 电路 图都 要进 行设 置。

连线需要注意:1、规则 2、快捷

Check and save

添加管脚需要注意: 1、命名 2、方向

பைடு நூலகம்

Make a symbol:Design →Create Cellview →From Pin List

管脚命名必须与电路图中一致

调用生成的模块

常用的快捷键

i (instance):插入元件 f (full screen):全屏幕 w (wire) :连线 p (pin):加管脚 q (quality):编辑属性

e:进入下一层模块 ctrl+e:返回上一层模块 [ : 缩小两倍 ] :放大两倍

主要内容

• 1、Virtuoso简介 • 2、如何进入Virtuoso • 3、电路图的绘制 • 4、电路图的仿真与分析 • 5、版图的绘制 • 6、版图的验证DRC/LVS • 7、版图后仿真

•

114 #setenv SOURCE_PATH "good"

•

115

•

116 # add schematic topcell name to replace xxx

•

117 setenv SOURCE_PRIMARY "opamp"

•

118

• •

119 #setenv SOURCE_PRIMARY "top_ma" 120 #setenv SOURCE_PRIMARY "HDPWM_top_with_buffer"

版图与原理图一致性的错误——检查工具 LVS(Layout versus Schematic)。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

实验一Virtuoso原理图和图标编辑器的基本使用目录1.实验目的2.创建一个新的自定义单元库3.使用 Cadence Virtuoso 原理图编辑器构建一个反相器4.创建一个自定义元器件图标1.实验目的本实验采用AMI06工艺设计一个反相器,以此使学生达到熟悉 Cadence Virtuoso 原理图和图标编辑器使用,记住常用热键组合以及掌握与特定工艺库关联之目的。

2.创建一个新的自定义单元库启动 Cadence,调用 CIW(Command Interpreter Window)首先启动计算机,在用户名处键入 cdsusr, 密码处键入123456,进入Linux操作系统桌面,在cdsusr’s Home 文件夹中创建iclabs子文件夹。

请记住一定要创建这个子文件夹,这样才不会影响到cdsusr根目录下的cds.lib文件。

操作如下:File --> Create Folder, 在新创建的文件夹名称处键入iclabs(可取不同名字,学号和本人名字拼音等)。

进入Linux桌面,单击鼠标右键打开终端。

见图1。

图1. Linux桌面操作在打开的终端中执行下列命令:见图2的红色框线内。

图2. Linux终端执行第二个命令后你就可看见Cadence软件的CIW窗口出现。

见图3所示。

图3. Cadence软件的CIW窗口在CIW窗口中点击Tools-->Library Manager..., 将打开库管理器(图4)。

图4. 库管理器你可看到NCSU提供的库已显示在Library栏目中,有 NCSU_Analog_Parts,...等。

点击库管理器中的File-->New-->Library..., 将打开New Library 对话窗口, 现创建一个新库取名为IClab1。

见图5。

图5. 创建一个自定义元件库点击OK弹出关联工艺库对话框(图6),选择Attach to an existing techfile。

图6. 选择关联工艺库的操作不同的工艺库对应不同的MOS器件模型,在对原理图进行仿真时需要选择相应工艺库中的模型,这样得到的结果更接近实际情况。

NCSU提供的CDK一共包含有9个工艺库,其中MOSIS_layout_Test库显示在最上端。

点击OK弹出选择特定工艺库对话窗口,对本实验,选择NCSU_TechLib_ami06库。

图7. 关联特定工艺库在库管理器中选中刚创建的IClab1库,单击菜单File-->New-->Cell View...,弹出 Create New File 对话窗(图8),Cell Name 可自己命名如inverter, Tool选 Composer- Schematic, View Name 就会默认选中schematic(原理图)。

图8. 指定创建的具体元件的名称和类型点击 Create New File 中的OK,就会启动Virtuoso Schematic Editor(图9)图9. Virtuoso 原理图编辑器工作界面若在上一步创建Library的过程中由于操作太快而不知道是否已正确关联了特定的工艺库,可在Library Manager窗口中鼠标右键点击IClab1,选择弹出菜单中的Properties...弹出对话框(图10)即可查看到底关联了哪个工艺库。

图10. 元件库属性编辑器上图正确显示了本次实验需要关联的工艺库。

若不正确而需要重新关联这个工艺库时,并不需要重新创建自定义元件库,而可在CIW窗口中进行操作,鼠标点击Tools-->Technology File Manager...弹出窗口(图11):图11. 重新关联工艺库的方法点击Attach...弹出对话框如图12所示即可重新关联工艺库了。

图12. 重新关联工艺库3.使用 Cadence Virtuoso 原理图编辑器构建一个反相器你需要在此编辑器中进行诸如放置和移动元器件,使用连线将各元器件相连以及对元器件属性做修改等操作,图13给出了常用热键,当然你也可进行菜单操作。

图13. 原理图编辑器常用热键另外上面没有列出的“Esc”键是用来退出正在执行的命令的键,经常会用到它。

构建一个反相器需要一个PMOS管和一个NMOS管,鼠标左击原理图编辑器的空白处,按热键I将会打开Add Instance对话窗口,按Browse会打开Component Browse窗,图14. 添加元器件窗口在Component Browse窗口中,Library选择NCSU_Analog_Parts,点击列出栏目中的N_Transistors或P_Transistors即可选择其中的器件,先点击N_Transistors,会打开以下窗口(见图15左图)。

图15. 选择所需添加的元器件选择nmos器件,其参数会显示在Add Instance 窗口中(见图15右图)。

移动鼠标到原理图编辑器中,nmos器件将显示在鼠标光标处,选择一个合适的位置(中间稍微偏下方)按鼠标左键放置nmos器件。

对于pmos器件,先点击(Go up 1 level)其余操作步骤完全相同,不同之处在于需要点击列出栏目中的P_Transistors。

图16. 添加pmos器件接下来需要放置电源以及地的连接关系符号,这些符号在Component Browse对话窗中的Supply_Nets分类栏目中,点击该栏目,在打开的电源地连接符号中你可依次选择gnd (地)和vdd (电源连接)符号,并将其放置到合适的位置。

至此按Esc 键即可结束放置元器件的命令。

原理图编辑器应该显示如图17所示:图17.大家注意到放置的pmos 和nmos 晶体管旁有参数显示,它们的值可根据设计者的要求进行更改。

要改变值时,先点击需要更改属性值的器件图标,再点击编辑器左侧的属性图标或按热键Q ,即可打开Edit Object Properties 对话窗口(图18)。

图18. 器件属性值对话框移动窗口右侧的滚动条可看到更多的属性值。

对pmos 或nmos 器件来说,改变得最多的值就是沟道的Width 和Length。

需要注意的是,不同的工艺这两个属性值是有相应的最小值限制的,如上图中带阴影的两项分别为最小宽度和最小长度,所以你输入的长和宽数值不能比它们小。

在大多数反相器设计中,为了使反相器的各项性能指标基本对称,pmos器件的沟道宽度一般选取为nmos器件的2-3倍,本次实验中将nmos器件的沟道宽度默认值1.5u修改为3u,而将pmos器件的宽度修改为6u。

更改数值后点击OK完成。

接着就是将元器件按照反相器的工作原理进行电气连接,连线采用Wire(narrow),点击编辑器左侧的Wire图标,分别移动鼠标至各元器件连接点(小红方块)将pmos源极连到vdd,nmos源极连到gnd,pmos漏极连到nmos漏极,pmos 栅极连到nmos栅极。

最后从栅极和漏极节点分别引出两根线用来连接引脚,按Esc 键退出连线。

此时的编辑器应显示如图19所示:图19. 构建中的反相器下一步点击Add Pin图标或按热键P添加引脚,栅极引出线连接输入引脚,漏极引出线连接输出引脚。

在弹出的添加引脚对话窗中,需要给引脚取名和选择类型,根据需要选定引脚方向为输入或输出,按回车键即可添加引脚,如图20所示:图20.添加引脚对话框完成添加输入输出引脚后按Esc键退出。

此时原理图编辑器应显示如下:图21. 一个完整的反相器电路图点击左侧工具条上方的Check and Save图标或按f8键保存你的设计,若电路有错误或警告信息则会弹出一个窗口告诉你,详细信息会显示在CIW窗口中。

若无信息窗口弹出则表示电路正常。

图22在CIW窗口中显示原理图没有错误。

图22. 原理图保存后CIW信息窗口4.创建一个自定义元器件图标刚设计的反相器就是一个新的元器件,下一步就是要为它创建一个图标,以便于在测试台电路(Testbench)中调用它进行电气性能的仿真和被其他电路反复调用。

从原理图编辑器的菜单中选择Design-->Create Cellview-->From Cellview, 会打开一个创建图标的对话窗。

被创建的图标应该保存在IClab1库中,对话框中的From View Name 应该为 schematic, To View Name 应该为 symbol,如果一切正确,请点击OK完成创建自定义元器件图标操作,见图23。

图23. 创建自定义元器件图标对话框此时图标编辑器将自动打开并创建了一个图标如图24所示:图24. 图标编辑器自动创建的反相器图标图中红色的线框表示整个图标的外部轮廓,称为Selection Box,其大小因图标大小可调整,在图标被其他电路调用时是不可见的。

绿色线框表示图标的实际形状,可被删除后修改成它所表示的器件的外形。

绿色的文本表示器件在其他电路中被调用时的名称,点击选中它后可移动至不同的位置,其内容可通过按Q键对其属性进行编辑修改,上图中为[@partName],表示其被调用时将自动命名为与cell name相同,即被调用时将显示为inverter,而这正是我们所希望要显示的名称。

在此要注意:中括号[]和@符号是不能少的,否则将会显示不同的结果。

红色的文本表示器件在其他电路中被调用时的编号,虽可被修改但请不要轻易改变其内容,而应将其移动到最靠近图标的位置。

红色文本中的中括号[]和@符号也同样不能少,且文本名称instanceName字母大小写也不能更改,否则在被调用时将不会显示器件编号。

若红色的线框不小心被删除,可在图标编辑器中使用菜单Add-->Selection Box自动或手动添加。

若红色文本或绿色文本不小心被删除,点击编辑器左侧的[@abc]添加label图标,或使用菜单Add-->Label... 则会弹出Add Symbol Label对话框,应根据需要选择Label Choice为instance label或logical label,如图25所示:instance label添加红色文本。

logical label添加绿色文本。

图25. 添加红色文本和绿色文本的说明既然创建的符号为反相器,自动创建的矩形图标显然是不合适的,反相器的外形整体应该为一个三角形,且在输出端顶点有一个小圆圈,因此我们就可以将绿色的矩形线框完全删除,选中绿色矩形线框,点击编辑器左侧的delete图标即可。

要画一个三角形,先点击编辑器左侧的line图标,Add Symbol Shape 对话窗口弹出,如图26所示,从对话框中可以看到,除了可画线以外,还可画多边形,园等多种形状。

在此需要特别注意的是,Draw Mode选项要按图中所示选斜线,否则你只能画90°的直角线。