fifo参数说明

FIFO详解

3.FIFO的一些重要参数

FIFO的宽度:也就是英文资料里常看到的THE WIDTH,它只的是FIFO一次读写操作的数据位,就像MCU有8位和16位,ARM 32位等等,FIFO的宽度在单片成品IC中是固定的,也有可选择的,如果用FPGA自己实现一个FIFO,其数据位,也就是宽度是可以自己定义的。

说到此,我们已经清楚地看到,FIFO设计最关键的就是产生空/满标志的算法的不同产生了不同的FIFO。但无论是精确的空满还是保守的空满都是为了保证FIFO工作的可靠。

====================================================================================================================

读时钟:读操作所遵循的时钟,在每个时钟沿来临时读数据。

写时钟:写操作所遵循的时钟,在每个时钟沿来临时写数据。

读指针:指向下一个读出地址。读完后自动加1。

写指针:指向下一个要写入的地址的,写完自动加1。

读写指针其实就是读写的地址,只不过这个地址不能任意选择,而是连续的。

4.FIFO的分类

根均FIFO工作的时钟域,可以将FIFO分为同步FIFO和异步FIFO。同步FIFO是指读时钟和写时钟为同一个时钟。在时钟沿来临时同时发生读写操作。异步FIFO是指读写时钟不一致,读写时钟是互相独立的。

fifo深度计算公式

fifo深度计算公式FIFO深度计算公式在计算机科学领域中,FIFO(First In, First Out)是一种常见的数据结构,用于管理数据的存储和检索。

FIFO深度指的是在FIFO队列中可存储的元素数量,也可以理解为队列的长度或容量。

在实际应用中,计算FIFO深度是非常重要的,可以帮助我们合理地规划和管理数据的存储。

FIFO深度的计算公式可以通过简单的数学推导来得到。

假设我们有一个固定大小的FIFO队列,其最大容量为N。

当我们向队列中插入一个新元素时,如果队列已满,则需要将队首的元素移除,以保持FIFO的特性。

因此,队列的深度始终不会超过N,即深度最大为N。

在实际应用中,我们可以通过以下公式来计算FIFO深度:FIFO深度 = min(N, 当前队列中元素的数量 + 1)这个公式的含义很简单,即FIFO深度不会超过队列的最大容量N,同时考虑到插入新元素时可能需要移除队首元素,因此需要在当前队列元素数量的基础上再加1。

举个例子,假设我们有一个最大容量为10的FIFO队列,当前队列中已经有8个元素。

如果我们要插入一个新元素,那么根据上面的公式,FIFO深度为min(10, 8+1) = min(10, 9) = 9。

换句话说,队列的深度将会是9。

通过计算FIFO深度,我们可以更好地规划数据存储空间,避免队列溢出或浪费空间的情况发生。

同时,深度的计算也有助于优化数据的管理和检索效率,提高系统的整体性能。

总的来说,FIFO深度计算公式是在实际应用中非常有用的工具,可以帮助我们更好地管理数据队列,提高系统的效率和性能。

希望通过本文的介绍,读者对FIFO深度的计算有了更清晰的认识。

一般工程上fifo的深度

一般工程上fifo的深度标题:从理论到实际——一般工程中FIFO的深度探究引言:FIFO(First In, First Out)是一种常见的数据存储和传输方式,即先进入队列的数据首先被处理。

在工程应用中,FIFO的深度是一个重要的参数,它决定了存储能力和数据传输的效率。

本文将一步一步回答“一般工程上FIFO的深度”这一主题,介绍FIFO深度的概念、计算方法以及实际应用中的相关考虑因素。

一、认识FIFO的深度FIFO深度是指FIFO队列中可以同时存储的数据数量。

它与队列的大小直接相关,通常以寄存器或存储单元的个数表示。

在设计FIFO深度时,需要考虑数据传输速率、处理要求和缓冲需求等因素。

二、计算FIFO深度的方法1. 根据数据传输速率:FIFO深度应该能够满足数据传输速率的需求。

根据数据传输频率和每个数据包的大小,可以通过以下公式来计算FIFO深度:FIFO深度= (数据传输速率×数据包延迟) / 数据包大小2. 根据处理要求:如果数据需要进行处理或加工,FIFO深度应能够存储足够长的时间,以便处理完成。

此时,可以通过以下公式计算FIFO深度:FIFO深度= 处理时间/ 数据传输周期3. 根据缓冲需求:FIFO深度还可以根据缓冲需求来计算。

如果需要缓冲一定数量的数据,以平衡生产者和消费者之间的速率差异,可以采用以下公式计算FIFO深度:FIFO深度= 缓冲区数据量/ 数据传输速率三、实际应用中的考虑因素1. 数据流量波动性:如果数据流量具有明显的波动性,FIFO深度应能够适应最高峰值,以防止数据丢失。

因此,在设计FIFO深度时,应考虑到流量的峰值和波动范围。

2. 系统延迟要求:如果系统对延迟有严格要求,FIFO深度应足够大,以防止数据在传输过程中发生堆积,导致发送和接收之间的延迟增加。

3. 成本和资源限制:FIFO深度的增加会带来成本和资源的增加,包括电路面积、功耗以及芯片上可用的存储单元数量等。

07.IP核之FIFO使用讲解

07.IP核之FIFO使用讲解HELLO FPGA 之软件工具篇第七节IP核之FIFO使用讲解§1.1 IP核之FIFO的介绍FIFO(First Input First Output),即先进先出队列,在计算机中,先进先出队列是一种传统的按序执行方法,先进入的指令先完成并引退,跟着才执行第二条指令。

就好比我们在超市购物,买好了东西之后,我们便会推着我们满满的购物车来到收银台排在结账队伍的最后面等待结账,前面先来排队的客户先得到结账,然后一个一个的结完帐离开,后面后来的客户需要等到前面的客户结完帐之后才能进行结账。

这就是一种先进先出的机制,相信大家还是很容易就能理解的。

FIFO一般用于不同时钟域之间的数据传输,比如FIFO的一端是采样速率比较慢的一个接口,另一端是采样速度比较快的一个接口,假设采样慢的接口速度为1Mhz,而采样快的接口速度为100Mhz,如果我们直接将这两个接口相连接,那么将会出现各种问题,如何解决呢,我们可以在这两个不同的时钟域间采用FIFO来作为数据缓冲。

另外对于不同宽度的数据接口也可以用FIFO,比如一端的接口输出数据是8位的,而另一端输出数据可能是16位的,我们就可以在这两个不同宽度的数据接口中使用FIFO来达到数据匹配的。

同我们之前讲的PLL、ROM和RAM IP核一样,Altera也提供了FIFO IP核,用于实现FIFO存储器。

§1.2 IP核之FIFO的配置介绍完了FIFO IP核,接下来我们来看一下FIFO IP核是如何进行配置的。

大家看,如图7.1所示是FIFOIP核的配置页面。

图7.1 FIFO IP核的配置页面从该图中我们可以看出,FIFO IP核的配置也是很简单的,我们想要配置一个FIFO IP核,也同ROM和RAMIP核一样,只需要完成以下三个步骤:1、Parameter Settings(参数设置);2、EDA(电子设计自动化);3、Summary(总结);1.2.1参数设置(Parameter Settings)首先我们先来介绍一下ParameterSettings(参数设置),在Parameter Settings(参数设置)配置中,我们可以看到它有4个标签,这4个标签分别是Width,Clks,Synchronization、SCFIFO Options、Rdreq Option,Blk Type和Optimization,Circuitry Protection。

vivado之fifo

vivado之fifo⼀、FIFO简介 FIFO是英⽂First In First Out 的缩写,是⼀种先进先出的数据缓存器,它与普通存储器的区别是没有外部读写地址线,这样使⽤起来⾮常简单,但缺点就是只能顺序写⼊数据,顺序的读出数据,其数据地址由内部读写指针⾃动加1完成,不能像普通存储器那样可以由地址线决定读取或写⼊某个指定的地址。

⽤途1: 异步FIFO读写分别采⽤相互异步的不同时钟。

在现代集成电路芯⽚中,随着设计规模的不断扩⼤,⼀个系统中往往含有数个时钟,多时钟域带来的⼀个问题就是,如何设计异步时钟之间的接⼝电路。

异步FIFO是这个问题的⼀种简便、快捷的解决⽅案,使⽤异步FIFO可以在两个不同时钟系统之间快速⽽⽅便地传输实时数据。

⽤途2: 对于不同宽度的数据接⼝也可以⽤FIFO,例如单⽚机位8位数据输出,⽽DSP可能是16位数据输⼊,在单⽚机与DSP连接时就可以使⽤FIFO来达到数据匹配的⽬的。

⼆、分类 同步FIFO是指读时钟和写时钟为同⼀个时钟,在时钟沿来临时同时发⽣读写操作; 异步FIFO是指读写时钟不⼀致,读写时钟是互相独⽴的。

三、FIFO的常见参数FIFO的宽度:即FIFO⼀次读写操作的数据位;FIFO的深度:指的是FIFO可以存储多少个N位的数据(如果宽度为N)。

满标志:FIFO已满或将要满时由FIFO的状态电路送出的⼀个信号,以阻⽌FIFO的写操作继续向FIFO 中写数据⽽造成溢出(overflow)。

空标志:FIFO已空或将要空时由FIFO的状态电路送出的⼀个信号,以阻⽌FIFO的读操作继续从FIFO 中读出数据⽽造成⽆效数据的读出(underflow)。

读时钟:读操作所遵循的时钟,在每个时钟沿来临时读数据。

写时钟:写操作所遵循的时钟,在每个时钟沿来临时写数据。

=====================================================================。

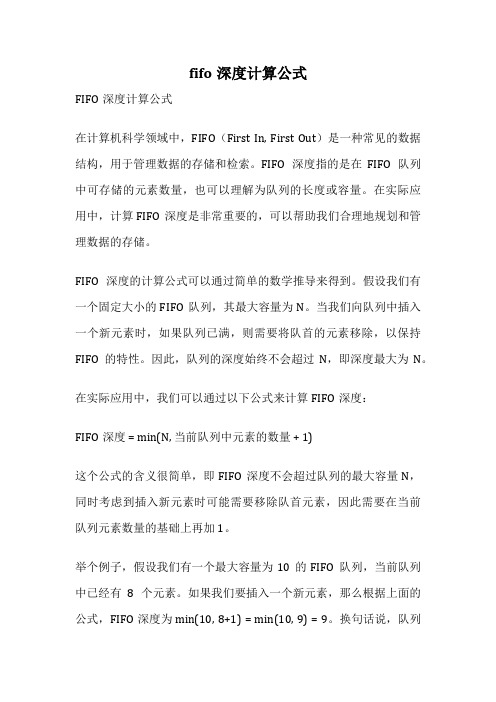

操作系统:FIFO算法详解及代码演示

操作系统:FIFO算法详解及代码演⽰FIFO算法FIFO算法是最简单的页⾯置换算法。

FIFO算法为每个页⾯记录了调到内存的时间。

当必须置换页⾯的时候,选择最旧的页⾯。

通俗来说,每次进⼊主存的时候如果主存中不存在这个页⾯,那么最先进⼊的页⾯出队。

如果主存存在这个页⾯,那么内存不动。

下⾯是C++⾯向对象写法代码。

这个说明⼀下为什么不⽤容器Queue。

是因为queue并没有迭代器,所以⽆法去寻找⾥⾯是否含有某块页⾯。

直接使⽤线性表即可,⽅便简单且快速。

// 在分页式虚拟存储管理中,要求通过键盘输⼊分配给⼀个作业的物理块数和作业依次访问的10个页⾯号,// 采⽤先进先出(FIFO)页⾯置换后// ,顺序输出缺页中断时所淘汰的页⾯号,并计算缺页中断率。

#include <iostream>using namespace std;#define MAX 20class Work{public:void seta(){int c, i = 1;cout << "输⼊10个页⾯号,以任意符号结尾" << endl;cin >> c;a[0] = c;while (cin >> c){a[i] = c;i++;}}void geta(){cout << "10个页⾯号分别为: ";for (int i = 0; i < 10; i++){cout << a[i] << " ";}cout << endl;}int index(int i){return a[i];}~Work(){cout<<"work 已被释放"<<endl;}private:int a[10];};class space{public:// 初始化构造函数,把除了物理块⼤⼩的其他空间都设置成其他值// 将初始化空间设置成-1space(int i){size=i;for (int j = 0; j < i; j++){s[j] = -1;}}// 显⽰物理块现在的状态void getSpace(){int i=0;cout<<"-------------物理块现在的状态是-------------"<<endl; while(s[i]!=-999){if(s[i]==-1){cout<<"NaN"<<" -||- ";i++;continue;}cout<<s[i]<<" -||- ";i++;}cout<<endl;cout<<"------------------------------------------"<<endl;}int find(int n){for(int i=0;i<size;i++){if(s[i]==n){return i;}}return -1;}// 先进先出,去掉第⼀个物理块,改变最后⼀个物理块。

FIFO的使用方法

第一章 FIFO配置全攻略1.1如何配置自己需要的FIFO配置FIFO的方法有两种:一种是通过QUARTUS II 中TOOLS下的MegaWizard Plug-In Manager 中选择FIFO参数编辑器来搭建自己需要的FIFO,这是自动生成FIFO的方法二通过手动编写HDL来实现需要的FIFO,这里主要第一种方法,因为本人也是菜鸟1.2输出输出端口表一中列出FIFO中各个IO的详细描述端口类型是否必选描述clock input Yes 上升沿触发时钟wrclk input Yse 上升沿触发时钟,下列信号与之同步:datawrreqwrfullwremptywrusedwrdclk input Yes 上升沿触发时钟,下列信号与之同步:qrdreqrdfullrdemptywremptyrdempty读空,此时不能再进行读操作;almost_full output No 准装满信号,当usedw大于参数almost_full_value或相同时,该信号被激活,即是full信号被激活的预示;almost_empty output No 准读空信号,当usedw小于参数almost_empty_value或相同时,该信号被激活,即是empty信号被激活的预示;usedwwrusedwrdusedwoutput No 显示当前FIFO中数据存量表一1.3时序要求1.如果设置了溢出保护电路或设置overflow_checking参数为ON,则在FIFO满时会自动无视wrreq信号,FIFO空时同理;2.如果没有做上述两种措施中的任意一种,则当FIFO在装满时的同一时钟周期内不能对wrreq信号做出相应,即在此期间不能拉高wrreq,FIFO空时同理。

3.下面通过两幅时序图来具体说明:1.4输出状态标记和潜伏期对于DCFIFO,输出潜伏期如下图所示:。

fifo参数

fifo参数FIFO参数是指在计算机系统中用于管理数据流的一组参数,其中包括缓冲区大小、数据传输速率、数据传输方向等。

FIFO参数的设置对于系统的性能和稳定性有着重要的影响,因此在进行系统优化和调试时需要对其进行合理的配置和调整。

一、FIFO参数的概述1.1 FIFO的定义FIFO(First In First Out)是一种先进先出的数据结构,通常用于管理数据流。

在计算机系统中,FIFO可以用来缓存数据,以提高数据传输效率和稳定性。

1.2 FIFO参数的作用FIFO参数是指控制FIFO缓冲区大小、数据传输速率、传输方向等一系列参数。

这些参数对于保证数据传输的正确性和稳定性至关重要,因此需要进行合理配置和调整。

二、FIFO参数的分类2.1 缓冲区大小缓冲区大小是指FIFO缓冲区能够存储的最大数据量。

通常情况下,缓冲区越大,则可以存储更多的数据,从而提高了系统吞吐量和稳定性。

但是过大的缓冲区也会导致延迟增加,从而降低了实时性能。

2.2 数据传输速率数据传输速率是指从FIFO缓冲区中读取或写入数据的速率。

通常情况下,传输速率越高,则可以更快地完成数据传输,从而提高了系统性能和响应速度。

但是过高的传输速率也会导致数据丢失或错误,从而降低了系统可靠性。

2.3 数据传输方向数据传输方向是指从FIFO缓冲区中读取或写入数据的方向。

通常情况下,数据传输方向可以分为单向和双向两种。

单向传输只能在一个方向上进行数据传输,而双向传输可以在两个方向上进行数据传输。

选择合适的数据传输方向可以提高系统性能和灵活性。

三、FIFO参数的配置3.1 缓冲区大小的配置缓冲区大小的配置需要考虑到系统实时性能和稳定性之间的平衡。

通常情况下,较小的缓冲区大小适合要求较高实时性能的应用场景,而较大的缓冲区大小适合要求较高吞吐量和稳定性的应用场景。

一般来说,可以通过测试不同缓冲区大小对系统实时性能和稳定性的影响来确定最佳缓冲区大小。

3.2 数据传输速率的配置数据传输速率的配置需要考虑到系统的处理能力和数据传输的实际需求。

FIFO的定义与作用

FIFO的定义与作用一、先入先出队列(First Input First Output,FIFO)这是一种传统的按序执行方法,先进入的指令先完成并引退,跟着才执行第二条指令。

1.什么是FIFO?FIFO是英文First In First Out 的缩写,是一种先进先出的数据缓存器,他与普通存储器的区别是没有外部读写地址线,这样使用起来非常简单,但缺点就是只能顺序写入数据,顺序的读出数据,其数据地址由内部读写指针自动加1完成,不能像普通存储器那样可以由地址线决定读取或写入某个指定的地址。

2.什么情况下用FIFO?FIFO一般用于不同时钟域之间的数据传输,比如FIFO的一端时AD数据采集,另一端时计算机的PCI总线,假设其AD采集的速率为16位100K SPS,那么每秒的数据量为100K×16bit=1.6Mbps,而PCI总线的速度为33MHz,总线宽度32bit,其最大传输速率为1056Mbps,在两个不同的时钟域间就可以采用FIFO来作为数据缓冲。

另外对于不同宽度的数据接口也可以用FIFO,例如单片机位8位数据输出,而DSP可能是16位数据输入,在单片机与DSP连接时就可以使用FIFO来达到数据匹配的目的。

3.FIFO的一些重要参数FIFO的宽度:也就是英文资料里常看到的THE WIDTH,它只的是FIFO一次读写操作的数据位,就像MCU有8位和16位,ARM 32位等等,FIFO的宽度在单片成品IC中是固定的,也有可选择的,如果用FPGA自己实现一个FIFO,其数据位,也就是宽度是可以自己定义的。

FIFO的深度:THE DEEPTH,它指的是FIFO可以存储多少个N位的数据(如果宽度为N)。

如一个8位的FIFO,若深度为8,它可以存储8个8位的数据,深度为12 ,就可以存储12个8位的数据,FIFO的深度可大可小,个人认为FIFO深度的计算并无一个固定的公式。

在FIFO实际工作中,其数据的满/空标志可以控制数据的继续写入或读出。

FIFO深度的解释

深入理解FIFO(包含有FIFO深度的解释)FIFO:一、先入先出队列(First Input First Output,FIFO)这是一种传统的按序执行方法,先进入的指令先完成并引退,跟着才执行第二条指令。

1.什么是FIFOFIFO是英文First In First Out 的缩写,是一种先进先出的数据缓存器,他与普通存储器的区别是没有外部读写地址线,这样使用起来非常简单,但缺点就是只能顺序写入数据,顺序的读出数据,其数据地址由内部读写指针自动加1完成,不能像普通存储器那样可以由地址线决定读取或写入某个指定的地址。

2.什么情况下用FIFOFIFO一般用于不同时钟域之间的数据传输,比如FIFO的一端时AD数据采集,另一端时计算机的PCI总线,假设其AD采集的速率为16位 100K SPI,那么每秒的数据量为100K×16bit=,而PCI总线的速度为33MHz,总线宽度32bit,其最大传输速率为1056Mbps,在两个不同的时钟域间就可以采用FIFO来作为数据缓冲。

另外对于不同宽度的数据接口也可以用FIFO,例如单片机位8位数据输出,而DSP 可能是16位数据输入,在单片机与DSP连接时就可以使用FIFO来达到数据匹配的目的。

3.FIFO的一些重要参数FIFO的宽度:也就是英文资料里常看到的THE WIDTH,它只的是FIFO一次读写操作的数据位,就像MCU有8位和16位,ARM 32位等等,FIFO的宽度在单片成品IC中是固定的,也有可选择的,如果用FPGA自己实现一个FIFO,其数据位,也就是宽度是可以自己定义的。

FIFO的深度:THE DEEPTH,它指的是FIFO可以存储多少个N位的数据(如果宽度为N)。

如一个8位的FIFO,若深度为8,它可以存储8个8位的数据,深度为12 ,就可以存储12个8位的数据,FIFO的深度可大可小,个人认为FIFO深度的计算并无一个固定的公式。

在FIFO实际工作中,其数据的满/空标志可以控制数据的继续写入或读出。

FIFO——精选推荐

FIFOFIFO(first in first out),具备读写端⼝各⼀个,外部⽆需控制地址。

FIFO与普通RAM的区别在于FIFO外部忽略对读写地址的管理,⽽只需要关注空满状态。

异步FIFO设计框图参数:时钟、数据位宽、深度、读写指针、空满判断、RAM空间⼤⼩实质:控制信号+RAM设计要点读、写时钟域的地址管理写地址到读时钟域的同步读地址到写时钟域的同步读时钟域的空和将空信号控制写时钟域的满和将满信号控制判满判空以深度为1024的FIFO为例,假设⼀直没有读操作,读指针停在地址0处。

当写完1024个数据后,写指针⼜回到了地址0处,此时读写地址相等。

⽽随写随读,读写地址也相等。

所以⽆法通过读写地址进⾏判满判空。

因此可以对地址增加1个⾼bit,来指⽰是否发⽣了回卷。

此时若读写地址相等,则为空。

若最⾼bit不同,但其余位相同,那么则为满。

判满时,需要将读地址同步到写时钟域进⾏判断。

判空时,需要将写地址同步到读时钟域进⾏判断。

为什么采⽤格雷码同步地址因为FIFO的地址是逐1增加的,因此可以把逐1增加的地址编码为相邻数只有1位不同的格雷码。

在实现跨时钟域信号采集时,如果数据每次只改变⼀位,那么就可以使⽤单⽐特跨时钟域处理⽅式直接采样。

⼆进制码和格雷码转换B2G⼆进制码右移⼀位,⾼位补0,与原⼆进制码按位相异或。

assign gray = (bin >> 1)^ binG2BGn = Bn;Gi-1=Bi ^ Bi-1; ( i=1,2,n-1; )assign bin[N-1] = gray[N-1] ;generategenvar i;for(i=0;i<N-1;i=i+1) begin:b2gassign binary[i] = grey[i]^binary[i+1];endendgenerateFIFIO深度。

stm32 dma fifo用法

stm32 dma fifo用法STM32的DMA(Direct Memory Access)是一种允许处理器在内存和外设之间直接传输数据的技术。

FIFO(First-In, First-Out)是DMA传输的一种数据存储方式,它可以在DMA传输完成后,以FIFO的方式将数据存储在指定的内存区域中。

下面介绍STM32 DMA FIFO的用法:1.配置FIFO模式首先,需要配置DMA通道为FIFO模式。

这可以通过设置DMA通道的CR (Control Register)寄存器的MODE位来实现。

MODE位为0时,DMA通道工作在正常模式;MODE位为1时,DMA通道工作在FIFO模式。

2.配置FIFO阈值FIFO模式下的DMA传输可以在达到一定数量的数据后产生中断或触发事件。

这个数量就是FIFO的阈值。

可以通过设置DMA通道的FCR(FIFO Control Register)寄存器的THRESHOLDBYTE位来设置FIFO的阈值。

3.配置传输参数在FIFO模式下,需要设置每次传输的数据量(块大小)以及传输的数据数量(块数目)。

这可以通过设置DMA通道的CCR(Common Control Register)寄存器的MSIZE、PSIZE、MCOUNT和PCOUNT位来实现。

4.启动DMA传输当所有配置完成后,可以启动DMA传输。

这可以通过设置DMA通道的CCR (Common Control Register)寄存器的EN位来实现。

当EN位为1时,DMA通道启动;当EN位为0时,DMA通道停止。

5.检查传输状态和中断事件在DMA传输期间,可以通过查询DMA通道的状态寄存器来检查当前传输的状态以及是否产生了中断事件。

例如,可以通过检查DMA1_Channel4的HISR(High-Integrity Status Register)寄存器的TCIF4位来判断该通道是否完成了传输。

如果TCIF4位为1,则说明通道完成了传输;如果TCIF4位为0,则说明通道还在传输中。

fifo深度计算方法

fifo深度计算方法嗨,宝子!今天咱们来唠唠FIFO深度计算方法这个事儿。

FIFO呢,就是先入先出队列啦。

那它的深度计算其实也没有那么神秘哦。

咱先得知道一些基本的信息,比如说数据的写入速率和读出速率。

要是写入快,读出慢,那FIFO就很容易满啦。

比如说写入速率是每秒钟10个数据,读出速率是每秒钟5个数据。

这时候呀,每秒钟就会有5个数据在FIFO里堆积起来呢。

那怎么算深度呢?咱得考虑一下在一段时间内,这个FIFO最多能堆积多少数据。

假设我们要考虑的这段时间是10秒钟。

按照前面的速率,10秒钟就会堆积50个数据。

那这个50呢,就大概是我们FIFO需要的一个最小深度啦。

不过呢,这里面还有一些小细节要注意哦。

比如说数据的突发情况。

有时候呀,数据不是那么规规矩矩地按照平均速率来的。

可能突然一下子来一大堆数据。

这时候我们就得考虑这个突发长度啦。

要是有一个突发长度是20的数据一下子要写入FIFO,而我们的读出速率还是每秒5个数据。

那在这突发的瞬间,FIFO就需要能够容纳下这20个数据才行呢。

所以呀,FIFO的深度就得根据这个突发长度来调整啦。

再比如说,我们的系统可能有一些特殊的要求,像是在某些特定的时刻,不管前面的数据有没有读完,都要开始写入新的数据。

这时候我们就得把这些特殊情况都考虑进去,来确定FIFO的深度。

总的来说呢,FIFO深度计算就是要把写入速率、读出速率、突发情况还有特殊要求这些因素都综合起来考虑。

就像我们做菜一样,要把各种调料的量都搭配好,才能做出一道美味的菜。

计算FIFO深度也是,要把各种因素搭配好,才能让我们的FIFO 在系统里好好地工作呢。

宝子,现在是不是觉得FIFO深度计算也没有那么难啦?嘻嘻。

altera scfifo参数

altera scfifo参数

对于 Altera 的 SCFIFO(Simple Dual-Port FIFO)IP 核,可

以通过修改参数来定制其功能和性能。

以下是一些常见的参数以及

它们的作用:

1. 容量参数,可以调整 FIFO 的深度,以适应特定的应用需求。

较大的深度会增加存储器资源的消耗,但可以提供更大的缓冲区。

较小的深度则可以减少资源消耗,但可能无法满足高吞吐量的要求。

2. 数据宽度参数,可以设置 FIFO 的数据宽度,以匹配特定的

数据总线宽度。

这可以确保数据在 FIFO 和外部系统之间的正确传输。

3. 空/满标志位参数,可以选择是否包含空/满标志位,以便外

部系统可以轻松地监视 FIFO 的状态。

这可以帮助控制数据的流动,并防止数据丢失或溢出。

4. 时钟控制参数,可以调整时钟控制逻辑,以适应特定的时序

要求。

这包括时钟域交叉域处理和时钟域转换。

5. 读写控制参数,可以配置读写控制逻辑,以适应不同的读写模式和时序要求。

这包括读写时序的优化和数据通路的控制。

通过修改这些参数,可以定制 SCFIFO IP 核以满足特定的应用需求,包括数据宽度、时序要求、资源消耗和接口兼容性等方面。

在修改参数之前,建议仔细分析应用需求和系统约束,以确保所做的定制能够正常工作并满足预期的性能目标。

4.异步FIFO的设计

利用异步FIFO在跨时钟域中降低亚稳态发生概率在数字电路设计中,时钟是整个电路最重要、最特殊的信号,系统内大部分器件的操作都是在时钟的跳变沿上进行,如果时序不满足要求,就可能造成逻辑状态出错甚至整个系统设计的失败。

随着SOC技术的不断发展,数字系统设计的复杂度也在日益增加,经常需要跨时钟域的数据传输,通信技术等异步设计才能实现特定的功能需求。

本文设计的异步FIFO就是为了解决将数据从一个时钟域同步的读/写到另一个时钟域,并且能很好的避免亚稳态的发生。

1.异步系统任意的两个系统如果满足以下条件之一,如图1-2所示,就可称其为异步的:(1)工作在不同的时钟频率上;(2)工作在相同频率上,但相位不同图1-2 异步系统时钟当两个不同时钟域的系统进行数据传输,由于接口处是异步的,就可能会违反建立时间和保持时间规则导致亚稳态以及不可靠的数据传输,因此处理起来较同步逻辑复杂困难。

在同步系统中,输入信号必须总是满足寄存器时序要求,所以亚稳态不会发生。

亚稳态问题通常发生在当一个信号在无关的线路中或异步时钟域中传输。

在所有的异步系统中,亚稳态是不可避免的。

1.1亚稳态所有的数字器件寄存器都定义了一个信号时序要求,满足了这个要求寄存器才可以正确地在输入端获取(capture)数据在输出端产生数据。

为了确保数据的可靠与正确性,在数据传输过程中必须满足寄存器的建立时间和保持时间,如图1-1,即输入数据在时钟沿之前必须稳定一段时间(寄存器建立时间Tsu)并且在时钟沿之后稳定一段时间(寄存器保持时间Th),然后寄存器输出经过一个特定的时钟到输出延时(clock to output ,Tco)后有效。

图1-1 建立时间与保持时间如果一个数据信号在翻转中违反了一个寄存器的建立和保持时间的要求,寄存器的输出可能就会出现亚稳态。

在亚稳态中,寄存器的输出值在高和低之间徘徊一段时间,这就意味着输出翻转到一个确定的高或低的延时会超过固定的时钟到输出延时。

FIFO FIFO

谢谢

跨时钟域数据传输。

用途2:

不同位宽数据缓冲。

广州创龙电子科技有限公司 04

FIFO 分类 同步FIFO

读时钟和写时钟为同一个时钟,在时钟沿来临时同时发生读写操作;

异步FIFO

读写时钟不一致,读写时钟是互相独立的。

广州创龙电子科技有限公司 05

FIFO 的常见参数

FIFO的宽度:FIFO一次读写操作的数据位数。 FIFO的深度:FIFO可以存储多少个N位的数据(N为FIFO的宽度)。 满标志:FIFO已满或将要满时由FIFO的状态电路送出的一个信号,继续向FIFO写数据可能会造成溢

出(overflow)。

空标志:FIFO已空或将要空时由FIFO的状态电路送出的一个信号,继续从FIFO读数据可能会造成无

效数据的读出(underflow)。

读时钟:读操作的时钟,在每个时钟边沿读数据。 写时钟:写操作的时钟,在每个时钟边沿写数据。

广州创龙电子科技有限公司 06

FIFO 的常见参数

FIFO 与 UPP

广州创龙电子科技有限 公司

Guangzhou Tronlong Electronic Technology Co., Ltd

本节我们结合UPP接口给大家介绍一下FIFO在实际工程中的使用。

广州创龙电子科技有限公司 01

FIFO 与 UPP

广州创龙电子科技有限 公司

Guangzhou Tronlong Electronic Technology Co., Ltd

本节我们结合UPP接口给大家介绍一下FIFO在实际工程中的使用。

广州创龙电子科技有限公司 01

01 FIFO 02 UPP 03 实战

广州创龙电子科技有限公司 02

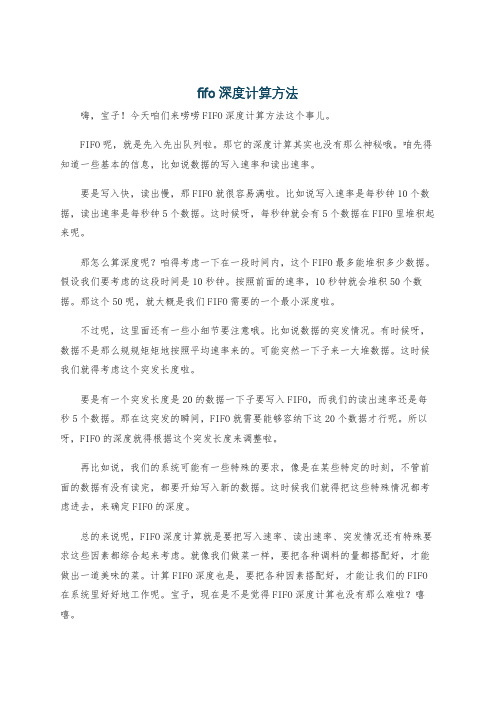

FIFO的简单知识

FIFO的简单知识新型的 FIFO芯片采用基于 RAM方式的结构FF EF复位RS基本时序及功能逻辑为:RS引脚置低时,IDT7204复位,内部读写指针都被复位到起始位置,每次上电后必须执行复位,当RS复位时R和W引脚必须为高,直到RS变高后才能进行读写操作.若无数据满标志FF低,那么每次W操作,就执行一次外部数据的写入,内部写指针自动加一,数据顺次进入FIFO.当缓冲区写满一半 ( 2K)时,下一次的W操作使中间指示XO/HF置低,表示未读数据已填满了一半空间,该信号可以提前提醒系统机进行读数操作.为避免写入数据溢出,当写入最后一个字节的写信号的下降沿出现时,满指示FF置低,禁止写入操作,FF有效期间,写指针不再移动,直到进行一次读出有效操作后FF才会被消除.若空指示EF未置低,每次R操作,就执行一次数据读出,读指针自动加一,数据顺次从FIFO读出.当所有的数据被读出后,空指示EF置低,禁止读出操作,EF有效期间,读指针不再移动,读出数据总线为高阻,直到进行一次写入有.IDT—7204,可用于深度扩展;在单片使用时,则其为重传数据,负脉冲有效.一个重传操作将使读指针回到首地址,不影响写指针.这种 FIFO芯片由大规模集成电路构成。

内部存储单元采用一个双端口 RAM,具有两套数据线——输入和输出。

独立的读写地址指针在读写时钟的控制下顺序地从存储单元读写数据,类似一个环形指针——从第一个存储单元开始到最后一个存储单元,然后又回到第一个存储单元。

控制比较部分给出RAM的空或满的状态指示,甚至还有中间指示。

由于采用 RAM结构,数据从输入到读出的延迟将大大缩小。

这种 FIFO芯片能在存储深度和宽度上得到很大发展。

新型大规模集成电路技术的日趋先进,使得较大容量的 FIFO芯片成为可能。

目前,为了使容量得到更大提高,存储单元采用动态 RAM代替静态RAM,并将刷新电路集成在芯片内,且内部仲裁单元决定器件的输入、读出及自动刷新操作。

fpga不同位宽 fifo使用方法

fpga不同位宽fifo使用方法FPGA(现场可编程门阵列)是一种高度集成的硬件设备,可以根据用户需求进行定制化设计。

在FPGA中,FIFO(先进先出)是一种常用的模块,用于数据缓存和传输。

位宽则是描述数据宽度的一个重要参数。

本文将介绍FPGA 中不同位宽FIFO的使用方法。

1.FPGA中FIFO的基本概念FIFO是一种线性缓冲区,具有先进先出(FIFO)的特性。

在FPGA中,FIFO模块通常包括输入端、输出端和存储器单元。

当数据从输入端写入时,存储器单元会按照先进先出的原则存储数据。

当数据从输出端读出时,同样按照先进先出的原则进行。

2.位宽与FIFO的关系位宽是指FIFO模块一次传输或存储的数据位数。

位宽越大,FIFO传输和存储的数据量越大,但同时所需的资源和功耗也越多。

在选择FIFO的位宽时,需要根据实际应用场景和需求进行权衡。

3.不同位宽FIFO的使用方法在使用不同位宽的FIFO时,主要需要注意以下几点:(1)根据需求选择合适的位宽。

例如,若数据处理过程中需要较高的数据吞吐量,可以选择较大位宽的FIFO。

(2)注意FIFO的容量。

容量越大,FIFO模块的存储时间越长,但同时也增加了功耗和资源占用。

(3)合理设置FIFO的读写速度。

根据实际应用场景,调整FIFO的读写速度,以提高数据传输效率。

(4)使用FIFO时,需关注模块间的时序关系,确保数据传输的稳定性。

4.应用实例及注意事项以下是一个使用不同位宽FIFO的实例:假设某FPGA应用需要处理的数据位宽为8位,吞吐量较大。

在这种情况下,可以选择位宽为32位的FIFO。

在使用过程中,需注意以下事项:(1)合理分配FIFO的读写速度,以充分发挥硬件性能。

(2)监控FIFO的使用状态,避免数据溢出或丢失。

(3)若需与其他模块共享FIFO,注意时序和同步问题。

总之,在FPGA中使用不同位宽的FIFO时,需根据实际需求进行合理配置,并关注模块间的协同工作。

stm32 fifo等级 阈值

主题:STM32 FIFO等级阈值I. 介绍STM32 FIFO1. STM32是由意法半导体推出的一款32位的嵌入式处理器,广泛应用于各类嵌入式系统中。

2. FIFO(First in, First out)是一种常见的数据缓冲区,可以按照先进先出的顺序操作数据。

II. STM32中的FIFO1. 在STM32中,许多外设模块都配备了FIFO缓冲区,如串口、SPI、ADC等。

2. FIFO可以帮助处理器在高速数据流中缓存数据,防止数据丢失或溢出。

III. FIFO等级1. 在STM32的外设模块中,通常会设置FIFO的等级阈值,用于触发数据传输或者中断。

2. 等级阈值是指FIFO中数据的数量达到一定值时,触发相应的触发事件或中断。

IV. FIFO等级设置1. 在STM32中,可以通过编程的方式设置FIFO的等级阈值。

2. 通过设置合适的等级阈值,可以提高数据传输的效率,减少CPU的负担。

V. FIFO等级阈值的应用1. 在串口通信中,设置合适的FIFO等级阈值可以平衡数据传输的速度和处理器的负载。

2. 在ADC采集数据时,通过调整FIFO等级阈值可以优化数据的采集和处理过程。

VI. 总结1. STM32中的FIFO等级阈值在各种外设模块中都起着重要的作用。

2. 合理设置FIFO等级阈值可以提高系统的性能和稳定性,是嵌入式系统设计中需要重点关注的部分。

VII. FIFO等级阈值的优化1. 在实际应用中,优化FIFO等级阈值是提高系统性能的重要手段。

2. 通过合理的FIFO等级阈值设置,可以减少中断触发的次数,从而降低系统的功耗,提高系统的响应速度。

3. 合适的FIFO等级阈值可以减少数据的丢失,并且可以提高数据处理的效率,降低系统的延迟。

4. 在设计嵌入式系统时,需要考虑不同外设模块的FIFO等级阈值,以达到整个系统的最佳性能。

VIII. FIFO等级阈值的调试1. 当系统出现数据传输不稳定或者中断频繁触发时,需要对FIFO等级阈值进行调试。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

fifo参数说明

FIFO(First In First Out)是一种先进先出的数据缓存器,用于数据的缓存或高速异步数据的交互。

以下是FIFO的一些主要参数:

1. 宽度:FIFO的宽度表示每次读写操作的数据位数。

2. 深度:FIFO的深度表示FIFO可以存储的数据量,计算方式为深度=2的宽度位数次方。

3. 空标志:当FIFO为空时,会产生空标志,此时无法进行读操作。

4. 满标志:当FIFO已满时,会产生满标志,此时无法进行写操作。

5. 读写时钟:对于同步FIFO,读写操作使用同一时钟;对于异步FIFO,读写操作使用不同的时钟。

6. 读写地址:FIFO具有自动加一的读写地址,用于数据的读写操作。

7. 计数器:用于产生空满标志,当计数器的值为0时产生空标志,当计数器的值为FIFO深度时产生满标志。

8. 数据宽度:FIFO存储的数据宽度,用于定义数据在FIFO中的位宽。

了解这些参数对于设计和应用FIFO非常重要,它们会影响FIFO的性能和适用性。

同时,根据具体的应用需求,还可以定制其他参数,如数据预取、奇偶校验等。