中断优先级同级顺序

单片机的一些面试题整理

单片机的一些面试题整理1.MCS51的中断系统有几个中断源?几个中断优先级?中断优先级是如何控制的?在出现同级中断申请时,CPU按什么顺序响应(按由高级到低级的顺序写出各个中断源)?各个中断源的入口地址是多少?答:MCS51单片机有5个中断源,2个中断优先级,中断优先级由特殊功能寄存器IP控制,在出现同级中断申请时,CPU按如下顺序响应各个中断源的请求:INT0、T0、INT1、T1、串口,各个中断源的入口地址分别是0003H、000BH、0013H、001BH、0023H。

单片机是将微处理器、一定容量的 RAM 和ROM以及 I/O 口、定时器等电路集成在一块芯片上而构成的微型计算机。

当CPU访问片外的存储器时,其低八位地址由P0口提供,高八位地址由P2口提供,8位数据由P0口提供。

在I/O口中,P0口在接LED时,必须提供上拉电阻,P3口具有第二功能。

19、是非题:工作寄存器区不允许做普通的RAM单元来使用。

F20、是非题:工作寄存器组是通过置位PSW中的RS0和RS1来切换的。

T21、是非题:特殊功能寄存器可以当作普通的RAM单元来使用。

F22、是非题:访问128个位地址用位寻址方式,访问低128字节单元用直接或间接寻址方式。

T23、是非题:堆栈指针SP的内容可指向片内00H~7FH的任何RAM单元,系统复位后,SP初始化为00H。

F24、数据指针DPTR是一个16位的特殊功能寄存器寄存器。

25、是非题:DPTR只能当作一个16位的特殊功能寄存器来使用。

F26、是非题:程序计数器PC是一个可以寻址的特殊功能寄存器。

F28、当系统处于正常工作状态且振荡稳定后,在RST引脚上加一个高电平并维持 2 个机器周期,可将系统复位。

29、是非题:单片机89C51复位后,其PC指针初始化为0000H,使单片机从该地址单元开始执行程序。

T31、是非题:单片机系统上电后,其内部RAM的值是不确定的。

T36、以下哪一条指令的写法是错误的(C)。

51单片机的中断优先级及中断嵌套

51 单片机的中断优先级及中断嵌套

说最基本的,老的51 单片机(80C51 系列)有5 个中断源,2 个优先级,

可以实现二级中断服务嵌套。

现在很多扩展的51 单片机已经有4 个优先级(或更多)和更多的中断源了。

在说到中断之前,我先来定义一下优先级,明白了什幺是优先级,后面的阐述就容易明白了。

实际上很多人都是混淆了优先级的含义,所以才觉得糊里糊涂。

中断的优先级有两个:查询优先级和执行优先级。

什幺是查询优级呢?我们从datasheet 或书上看到的默认(IP 寄存器不做设

置,上电复位后为00H)的优先级:

外部中断0 > 定时/计数器0 > 外部中断1 > 定时/计数器1 > 串行中断

或int0,timer0,int1,timer1,serial port 或INT0、T0、INT1、T1、UART

或PX0>PT0>PX1>PT1>PS>......

其实都是查询优级。

首先查询优先级是不可以更改和设置的。

这是一个中断优先权排队的问题。

是指多个中断源同时产生中断信号时,中断仲裁器选择对哪个中断源优先处理的顺序。

而这与是否发生中断服务程序的嵌套毫不。

MCS51的中断系统有几个中断源

.MCS51的中断系统有几个中断源?几个中断优先级?中断优先级是如何控制的?在出现同级中断申请时,CPU按什么顺序响应(按由高级到低级的顺序写出各个中断源)?各个中断源的入口地址是多少?答:MCS51单片机有5个中断源,2个中断优先级,中断优先级由特殊功能寄存器IP控制,在出现同级中断申请时,CPU按如下顺序响应各个中断源的请求:INT0、T0、INT1、T1、串口,各个中断源的入口地址分别是0003H、000BH、0013H、001BH、0023H。

3.MCS51系列单片机的内部资源有哪些?说出8031、8051和8751的区别。

答:MCS51系列单片机上有1个8位CPU、128B的RAM、21个SFR、4个并行口、1个串行口、2个定时计数器和中断系统等资源。

8031、8051和8751的区别是8031内无ROM;8051内有4KB的掩膜ROM;8751内有4KB的EPROM。

五、作图题(10分)用6264(8K*8)构成16K的数据存储系统。

要求采用线选法产生片选信号,并计算6264的地址范围答:WR接6264的WERD接6264的OEAB0---AB12接6264的A0---A12DB0—DB7接6264的D0—D7AB15、AB14分别接Y0和Y1地址:0000H---1FFFH;2000H---3FFFH六、设计题(1题13分;2题12分,共25分)1.某单片机控制系统有8个发光二极管。

试画出89C51与外设的连接图并编程使它们由左向右轮流点亮。

2.某控制系统有2个开关K1和K2,1个数码管,当K1按下时数码管加1,K2按下时数码管减1。

试画出8051与外设的连接图并编程实现上述要求1.某单片机控制系统有8个发光二极管。

试画出89C51与外设的连接图并编程使它们由右向左轮流点亮。

答:图 (5分) 构思 (3分)MOV A,#80H (1分)UP:MOV P1,A (1分)RR A (2分)SJMP UP (1分2.某控制系统有2个开关K1和K2,1个数码管,当K1按下时数码管加1,K2按下时数码管减1。

CS,S5一的五个中断源优先级。

CS,S5一的五个中断源优先级。

mcs-51单片机有5个中断源,分别为:

1、外部中断0(INT0):默认中断级别最高,中断入口地址0003H;

2、定时/计数器0(T1):默认中断级别第2,中断入口地址000BH;

3、外部中断1(INT1):默认中断级别第3,中断入口地址0013H;

4、串行口中断(TX/RX):默认中断级别第4,中断入口地址0023H;

5、定时/计数器1(T1):默认中断级别最低,中断入口地址001BH。

中断请求源有两个中断优先级,每一个中断请求源可由软件设置为高优先级中断或低优先级中断,也可实现两级中断嵌套。

两级中断嵌套,就是正在执行低优先级中断的服务程序时,可被高优先级中断请求所中断,待高优先级中断处理完毕后,再返回低优先级中断服务程序。

中断优先级程序设计

中断优先级程序设计中断是计算机系统中一种重要的机制,它可以在程序执行过程中,根据特定的条件或事件发生时,暂停当前正在执行的程序,转而执行相应的中断服务程序。

中断优先级程序设计是指在多个中断同时发生时,根据优先级的设定,决定中断的处理顺序。

中断优先级程序设计的目的是为了提高系统的响应速度和效率。

在实际应用中,不同的中断可能具有不同的紧急程度和重要性,因此需要根据实际需求,合理地设置中断的优先级。

一般来说,中断的优先级可以分为高优先级和低优先级两种。

在中断优先级程序设计中,高优先级的中断会立即打断正在执行的低优先级中断或主程序,转而执行高优先级中断的服务程序。

这样可以确保高优先级中断的及时处理,避免因低优先级中断或主程序的执行而延误高优先级中断的处理。

而低优先级中断则会在高优先级中断处理完毕后再继续执行。

中断优先级程序设计的实现需要借助硬件和软件的支持。

在硬件方面,可以通过设置中断控制器的优先级寄存器来确定中断的优先级。

在软件方面,可以通过编程的方式,设置中断的优先级。

一般来说,中断的优先级可以通过设置中断向量表或中断服务程序的调用顺序来实现。

在实际应用中,中断优先级程序设计可以应用于各种场景。

例如,在实时操作系统中,可以根据任务的紧急程度和重要性,设置不同的中断优先级,以确保系统对关键任务的及时响应。

在通信系统中,可以根据不同的通信协议和数据传输方式,设置不同的中断优先级,以确保数据的准确传输和处理。

在嵌入式系统中,可以根据外部设备的特性和工作模式,设置不同的中断优先级,以确保系统对外部设备的及时响应。

总之,中断优先级程序设计是一种重要的程序设计方法,它可以提高系统的响应速度和效率。

通过合理地设置中断的优先级,可以确保系统对不同事件的及时处理,提高系统的可靠性和稳定性。

在实际应用中,我们需要根据具体的需求和场景,灵活地运用中断优先级程序设计,以实现更好的系统性能和用户体验。

中断中断优先级

中断中断优先级interrupt 表示中断优先级,using表示所用工作寄存器组。

interrupt x using y跟在interrupt 后面的xx 值得是中断号,就是说这个函数对应第几个中断端口,一般在51中0 外部中断01 定时器02 外部中断13 定时器14 串行中断其它的根据相应得单片机有自己的含义,实际上c在编译的时候就是把你这个函数的入口地址放到这个对应中断的跳转地址using y 这个y是说这个中断函数使用的那个寄存器组就是51里面一般有4个 r0 -- r7寄存器,如果你的终端函数和别的程序用的不是同一个寄存器组则进入中断的时候就不会将寄存器组压入堆栈返回时也不会弹出来节省代码和时间外部中断INT0void intsvr0(void) interrupt 0 using 1定时/计数器T0void timer0(void) interrupt 1 using 1外部中断INT1void intsvr1(void) interrupt 2 using 1定时/计数器T1void timer1(void) interrupt 3 using 1串口中断void serial0(void) interrupt4 using 1单片机的C语言HNBCC培训一,中断的概念中断:当计算机执行正常程序时,系统中出现某些急需处理的异常情况和特殊请求.中断的执行:当CPU正在执行某一程序时,若有中断响应,则CPU转而执行中断服务程序,当中断服务程序执行完毕后,CPU自动返回原来的程序继续执行.中断服务程序的语句写法与函数的写法完全相同,所以,中断服务程序也是函数,只在函数头部有不同(后续).中断服务程序的执行与函数的执行不同:函数的执行是有固定位置的,是通过函数的调用来完成的;而中断服务程序的执行是不固定位置的,只要有中断响应,在一定条件下都会去响应中断,即执行中断服务程序.二,中断源中断源:任何引起计算机中断的事件,一般一台机器允许有许多个中断源.8051系列单片机至少有5个可能的中断(8052有6个,其它系列成员最多可达15个).下面以5个中断源为例.8051单片机的五个中断源是:外部中断请求0,由INT0(P3.2)输入;外部中断请求1,由INT1(P3.3)输入;片内定时器/计数器0溢出中断请求;片内定时器/计数器1溢出中断请求;片内串行口发送/接收中断请求.三,与中断有关的寄存器1,定时/计数器控制寄存器TCONTF1 TR1 TF0 TR0 IE1 IT1 IE0 IT0D7 D6 D5 D4 D3 D2 D1 D0. IT0,IT1:外部中断0,1触发方式选择位,由软件设置;1→下降沿触发方式,INT0/INT1管脚上高到低的负跳变可引起中断;0→电平触发方式, INT0/INT1管脚上低电平可引起中断.. IE0,IE1:外部中断0,1请求标志位;当外部中断0,l依据触发方式满足条件,产生中断请求时由硬件置位(IE0/IE1=1);当CPU响应中断时由硬件清除(IE0/IE1= 0).. TR0,TR1: 启动定时/计数器0,1.. TF0,TF1:定时器/计数器0,1(T/C0,T/C1)溢出中断请求标志;当T/C0,1计数溢出时由硬件置位(TF0/TF1=l);当CPU响应中断由硬件清除(TFO/TF1=0).三,与中断有关的寄存器2,串行口控制寄存器SCONTI RID7 D6 D5 D4 D3 D2 D1 D0. RI:串行口接收中断请求标志位;当串行口接收完一帧数据后请求中断,由硬件置位(RI=1)RI必须由软件清"0".. TI:串行口发送中断请求标志位.当串行口发送完一帧数据后请求中断,由硬件置位(TI=1)TI必须由软件清"0".三,与中断有关的寄存器3,中断允许寄存器IEEA ET2 ES ET1 EX1 ET0 EX0D7 D6 D5 D4 D3 D2 D1 D0. EX0,EX1:外部中断0,1的中断允许位;l→外部中断0,1开中断;0→外部中断0,1关中断.. ET0,ET1:定时器/计数器0,1(T/C0,T/C1)溢出中断允许位;1→T/C0,T/Cl开中断;0→T/C0,T/Cl关中断.. ES:串行口中断允许位;1→串行口开中断;0→串行口关中断.. ET2:定时器/计数器2(T/C2)溢出中断允许位;1→T/C2开中断;0→T/C2关中断.. EA:CPU开/关中断控制位.1→CPU开中断.0→CPU关中断.8051复位时,IE被清"0",此时CPU关中断,各中断源的中断也都屏蔽三,与中断有关的寄存器4,中断优先级寄存器IPPS PT1 PX1 PT0 PX0D7 D6 D5 D4 D3 D2 D1 D0. PX0,PX1:外部中断0,1中断优先级控制位;1→高优先级;0→低优先级.. PT0,PT1:定时器/计数器0,1中断优先级控制位;1→高优先级;0→低优先级.. PS:串行口中断优先级控制位;1→高优先级;0→低优先级.8051复位时,IP被清"0",5个中断源都在同一优先级,其内部优先级的顺序从高到低为: 外部中断0(IE0)定时器/计数器0(TF0)外部中断1(IE1)定时器/计数器1(TF1)串行口中断(RI+TI)四,中断响应8051的CPU在每个机器周期采样各中断源的中断请求标志位,如果没有下述阻止条件,将在下一个机器周期响应被激活了的最高级中断请求:1.CPU正在处理同级或更高级的中断;2.现行机器周期不是所执行指令的最后一个机器周期;3.正在执行的是RETI或是访问IE或IP的指令.CPU在中断响应后完成如下的操作:1.硬件清除相应的中断请求标志;2.执行一条硬件子程序,保护断点,并转向中断服务程序人口3.结束中断时执行RETI指令,恢复断点,返回主程序.8051的CPU在响应中断请求时,由硬件自动形成转向与该中断源对应的服务程序入口地址,这种方法为硬件向量中断法.五,中断服务程序的入口地址编号中断源人口地址0 外部中断0 0003H1 定时器/计数器0 000BH2 外部中断1 0013H3 定时器/计数器1 001BH4 串行口中断 0023H各中断服务程序入口地址仅间隔8个字节,编译器在这些地址放入无条件转移指令跳转到服务程序的实际地址.六,中断服务程序的语法规则中断服务程序的语法规则如下:函数的返回值函数名([参数]) interrupt n [using m]{函数体;}对中断程序而言,函数的返回值和参数一般为void.interrupt n 中n的取值为0~31的常数,不允许用表达式,表示中断向量的编号.using m 中m的取值为0~3的常数,不允许用表达式,表示内部RAM中的工作寄存器.七,中断说明中断不允许用于外部函数,它对函数目标代码影响如下z·当调用函数时,SFR中的ACC,B,DPH,DPL和PSW(当需要时)入钱;.如果不使用寄存器组切换,甚至中断函数所需的所有工作寄存器都入钱;.函数退出前,所有的寄存器内容出钱;·函数由8051的指令"RETI"终止.中断服务程序使用的任何程序也使用同一寄存器组.八,中断例子#include 〈reg51.h〉unsigned char status;bit flag;void service_int() interrupt 2 using 2{ flag=1;status=P1;}void main(void){IP=0x04; IE=0x84;for(;;){if(flag){switch(status){case 0: break;case 1: break;case 2: break;case 3: break;default: ;}flag=0;}}}图见书中P148习题试设计满足下列要求的电路图:1 单片机采用89C51,时钟11.0592MHz;2 有4个指示灯表示状态;3 外接12位A/D芯片AD574;4 有4 * 4的键盘;5 有字符型LCD(画成插座形式,12Pin插座,管脚接法见书P253);6 有串行接口与计算机连接;7 设置8位二进制的地址,地址范围可表示为0~255;8 外接EEPROM.定时器/计数器(T/C)8051系列单片机至少有两个16位内部定时器/计数器,8052有三个定时器/计数器,其中有两个是基本定时器/计数器是定时器/计数器.它们既可以编程为定时器使用,也可以编程为计数器使用.若是计数内部晶振驱动时钟,它是定时器;若是计数,8051的输入管脚的脉冲信号,它是计数器.当T/C工作在定时器时,对振荡源12分频的脉冲计数,即每个机器周期计数值加1,计数率=1/12f osc.例当晶振为12MHz时,计数率=1000kHz,即每1μs计数值加1.当T/C工作在计数器时,计数脉冲来自外部脉冲输入管脚T0(P3.4)或T1(P3.5),当T0或T1脚上负跳变时计数值加1.识别管脚上的负跳变需两个机器周期,即24个振荡周期.所以T0或T1脚输入的可计数外部脉冲的最高频率为1/24fosc,当晶振为12MHZ时,最高计数率为500kHz,高于此频率将计数出错.一,与T/C有关的SFR1,计数寄存器Th和TLT/C是16位的,计数寄存器由TH高8位和TL低8位构成.在特殊功能寄存器(SFR) 中,对应T/C0为TH0和TL0;对应T/C1为TH1和TL1.定时器/计数器的初始值通过TH1/TH0和TL1/TL0设置.2,定时器/计数器控制寄存器TCON前面已介绍.二,与T/C有关的SFR3,T/C的方式控制寄存器TMOD. C/T:计数器或定时器选择位;1→为计数器;0→为定时器.. GATE :门控信号;1 → T/C的启动受到双重控制,即要求TR0/TR1和INT0/INT1同时为高;0 → T/C的启动仅受TR0或TR1控制.GATE C/T M1 M0 GATE C/T M1M0D7 D6 D5 D4 D3 D2 D1 D0T/C1T/C0三,四种工作方式M1 M0 方式功能0 0 0 13位定时器/计数器,TL是低5位,TH是高8位0 1 1 16位定时器/计数器1 02 常数自动重装的8位定时器/计数器1 1 3 仅用于T/C0,是两个8位定时器/计数器利用定时器编写时钟程序.四,T/C工作方式的说明1. 方式0:当TMOD中MlM0=00时,T/C工作在方式0;方式0为13位的T/C,由TH的高8位,TL的低5位的计数值,满计数值213,但启动前可以预置计数初值.若T/C开中断(ET=1)且CPU开中断(EA=1)时,则定时器/计数器溢出时,CPU转向中断服务程序时,且TF白动清0.2. 方式1:当TMOD中MlM0=01时,T/C工作在方式1;方式1与方式0基本相同.唯一区别在于计数寄存器的位数是16位的,由TH和TL寄存器各提供8位,满计数值为216.四,T/C工作方式的说明3. 方式2:当TMOD中MlM0=10时,T/C工作在方式2;方式2是8位的可自动重载的T/C,满计数值为28;在方式0和方式1中,当计数满后,若要进行下一次定时/计数,须用软件向TH和TL重装预置计数初值;方式2中TH和TL被当作两个8位计数器,计数过程中,TH寄存8位初值并保持不变,由TL进行8位计数.计数溢出时,除产生溢出中断请求外,还自动将TH中初值重装到TL,即重装载.4. 方式3:方式3只适合于T/C0.当T/CO工作在方式3时,TH0和TL0成为两个独立的8位计数器.五,定时器/计数器的初始化在使用8051的定时器/计数器前,应对它进行编程初始化,主要是对TCON和TMOD编程;计算和装载T/C的计数初值.一般完成以下几个步骤:(1)确定T/C的工作方式——编程TMOD寄存器;(2)计算T/C中的计数初值,并装载到TH和TL;(3)T/C在中断方式工作时,须开CPU中断和源中断——编程IE寄存器;(4)启动定时器/计数器——编程TCON中TR1或TR0位.六,定时器/计数器的初值计算在定时器方式下,T/C是对机器周期脉冲计数的,若fosc=12MHz,一个机器周期为12/fosc=1μs,则:方式0 13位定时器最大定时间隔=213 × 1μs=8.192ms;方式1 16位定时器最大定时间隔=216 × 1μs=65.536ms;方式2 8位定时器最大定时间隔=28×1μs=256μs.若使T/C工作在定时器方式1,要求定时1ms,求计数初值.设计数初值为x,则有:(216-x)×1μs=1000μs或x=216一1000因此,TH,TL可置-1000;即:TH= -1000/256;TL= -1000%256.对一般fosc有下列公式(设定时时间为timeμs):(216-x)×12/fosc= time μs例1,设单片机的fosc=12MHz,要求在P1.0脚上输出周期为2ms 的方波采用查询方式.#include 〈reg51.h〉sbit P1_0=P1^0;void main(void〉{ TMOD=0x01; TR0=1;for(;;){TH0= -1000/256;TL0= -1000%256;do {} while(!TF0);P1_0=!P1_0;TF0=0;}}采用中断方式.#include 〈reg51.h>sbit P1_0=P1^0;void timer0(void) interrupt 1using 1 {P1_0=!P1_0; TH0= -1000/256;TL0= -1000%256;}void main(void){TMOD=0x01; P1_0=0;TH0= -1000/256;TL0= -1000%256;EA=1;ET0=1;TR0=1;do {} while(1);}例2,设单片机的fosc=6MHz,要求在P1.7脚上的指示灯亮一秒灭一秒.void main(void){P1_7=0; P1_0=1;TMOD=0x61;TH0= -50000/256;TL0= -50000%256;TH1= -5; TL1= -5;IP=0x08;EA=l; ET0=1;ET1=l; TR0=l;TR1=1;for (;;){}}#includesbit P1_0=P1^0;sbit P1_7=P1^7;void timer0( ) interrupt 1 using 1{P1_0=!P1_0;TH0= -50000/256;TL0= -50000%256;}void timer1( ) interrupt3 using 2{P1_7=!P1_7;}例3,设单片机的fosc=10MHz,要求在P1.0脚上输出周期为2.5μs,占空比20%.#include#define uchar unsigned charuchar time;uchar period=250;uchar high=50;void timer0( ) interrupt l using 1{TH0= -8333/256;TL0= -8333%256;if(++time==high)P1=0;else if(time==period){time=0; P1=1;}}void main(void){TMOD=0x01;TH0= -8333/256;TL0= -8333%256;EA=l;ET0=1;TR0=1;do {)while(1);}#include#define uchar unsigned char#define uint unsigned intuchar time,status,percent,period;bit one_round;uint oldcount,target=500;void pulse(void) interrupt 1using l {TH0= -833/256;TL0= -833%256; ET0=l;if(++time==percent)P1=0;else if (time ==100){time=0;P2=l;}void tachmeter(void) interrupt 2 using 2 {union {uint word;struct{uchar hi;uchar lo;}byte; }newcount; newcount_byte.hi=TH1;newcount_byte.lo=TLl;period=newcount.word--oldcounts; oldcount=newcount.word;one -round=1;void main(void){IP=0x04;TMOD=0x01;TCON=0x54;TH1=0;TL1=0;IE=0x86;for(;;){if(one_round){if(period{if(percent0)--percent;}}}串行口8051系列单片机有一个标准的串行通信接口,发送数据时由TXD 端口送出,接收数据时由RXD端口输入.内置两个缓冲器SBUF,一个接受缓冲器,另一个是接收缓冲器,可实行全双工的串行通信.近距离可直接用TTL电平,若与计算机通信,则需要将电平转换成RS232电平形式,若需长距离通信可以采用RS485电平形式,通信的数据必须通过软件的编写来完成.一,与串行口有关的SFR1,串行口控制寄存器SCONSM0 SM1 SM2 REN TB8 RB8 TI RID7 D6 D5 D4 D3 D2 D1 D0. SM0,SM1:串行口工作方式控制位(见书P158).. SM2:多机通信控制位(方式2,3);1→只有接收到第9位(RB8)为1,RI才置位;0→接收到字符RI就置位.. REN :串行口接收允许位;1→允许串行口接收;0→禁止串行口接收.. TB8:方式2和方式3时,为发送的第9位数据,也可以作奇偶校验位.. RB8:方式2和方式3时,为接收到的第9位数据;方式1时,为接收到的停止位.. TI:发送中断标志;由硬件置位,必须由软件清0.. RI:接收中断标志;由硬件置位,必须由软件清0.一,与串行口有关的SFR2,电源控制寄存器PCONSMODD7 D6 D5 D4 D3 D2 D1 D0PCON的第7位SMOD是与串行口的波特率设置有关的选择位.. SMOD:串行口波特率加倍位.1→方式1,3波特率=定时器1溢出率/16;方式2波特率为fosc/32;0→方式1,3波特率=定时器1溢出率/32;方式2波特率为fosc/64.二,串行口的工作方式1. 方式0方式0为移位寄存器输入/输出方式,串行数据通过RXD输入/输出 ,TXD则用于输出移位时钟脉冲.方式0时,收发的数据为8位,低位在前.波特率固定为fosc/12,其中fosc为单片机外接晶振频率.发送是以写SBUF寄存器的指令开始的,8位输出结束时TI被置位.方式0接收是在REN=1和RI=0同时满足时开始的.接收的数据装入SBUF中,结束时RI被置位.移位寄存器方式的也可用于两个单片机之间的通信.和通常9600波特相比,lMHz通信能力对短距离通信很吸引人.二,串行口的工作方式2. 方式1方式1是10位异步通信方式,1位起始位(0),8位数据位和1位停止位(1).其中的起始位和停止位在发送时是自动插入的.任何一条以SBUF为目的寄存器的指令都启动一次发送,发送的条件是TI=0,发送完置TI为1;方式l接收的前提条件是SCON中的REN为l,同时下列两个条件都满足,本次接收有效,将其装入SBUF和RB8位.否则放弃接收结果.两个条件是:(1)RI=0;(2)SM2=0或接收到的停止位为1;方式1的波特率是可变的,波特率可由以下计算公式计算得到: 方式1波特率=2SMOD.(定时器1的溢出率)/32其中的SMOD为PCON的最高位.定时器1的方式0,1,2,都可以使用,其溢出率为定时时间的倒数值.二,串行口的工作方式3. 方式2和方式3这两种方式都是11位异步接收/发送方式,它们的操作过程完全一样,所不同的是波特率:方式2波特率=2SMOD.(fosc/64);方式3波特率同方式1(定时器l作波特率发生器).方式2和方式3的发送起始于任何一条"写SBUF"指令,当第9位数据(TB8)输出之后,置位TI.方式2和方式3的接收前提条件也是REN为1.在第9位数据接收到后,如果下列条件同时满足(1)RI=0;(2)SM2=0或接收到的第9位为1,则将已接收的数据装入SBUF和RB8,并置位RI,如果条件不满足,则接收无效.三,串行口的初始化在使用串行口之前,应对它进行编程初始化,主要是设置产生波特率的定时器1,串行口控制和中断控制寄存器.具体步骤如下:(1) 确定定时器1的工作方式——编程TMOD寄存器;(2) 计算定时器1的初值——装载TH1,TL1,具体TH1和TL1的值可查表得到;(3) 启动定时器1——编程TCON中的TR1位,即置TR1为1;(4) 确定串行口的控制——编程SCON;(5) 串行口在中断方式工作时,须开CPU和源中断——编程IE寄存器.四,串行口举例1#include 〈reg51.h>#define uchar unsigned char#define uint unsigned intuchar idata trdata[10]={'M','C','S','-','5','1', 0x0d,0x0a,0x00};void main(void){ uchar i; uint j;TMOD=0x20;TL1=0xfd;TH1=0xfd; SCON=0xd8;PCON=0x00; TR1=1;while(1){i=0;while(trdata[i]!=0x00) {SBUF=trdata[i];while(TI==0);TI=0; i++;}for (j=0;jvoid main(void〉{unsigned char a;TMOD=Ox20;TL1=0xfd;TH1=0xfd; SCON=Oxd8;PCON=0x00; TR1=1;while (1){while (RI==0); RI=0;a=SBUF; SBUF=a;while (TI==O); TI=0;}}#include 〈reg51.h〉#define uchar unsigned char uchar xdata r_buf[32]; uchar xdata t_buf[32]; uchar r_in,r_out,t_in,t_out;bit r_full,t_empty,t_done;code uchar m[]={"this is a test programrn"};serial( ) interrupt 4 using 1{ifRI&&~r_full){ r_buf[r_in]=SBUF; RI=0;r_in=++r_in&0xlf;if(r_in==r_out) r_full=1;}else if (TI &&~t_empty){SBUF=t_buf[t_out]; TI=0;t_out=++t_out&0x1f;if{t_out==t_in)t_empty=l;else if(TI){TI=0;t_done =1;}}void loadmsg(uchar code *msg){ while((*msg!=0)&&((((t_in+1)^ t_out)&0xlf)!=0)) { t_buf[t_in]= *msg; msg++;t_in=++t_in&0x1f;if(t-done){TI=1;t_empty=t_done =0 ;}}}void process(uchar ch){return;}void processmsg(void){while(((r_out+1)^r_in)!=0){process(r_buf[r_out]);r_out=++r_out&0x1f;}}void main(){TMOD=0x20;TH1=0xfd;TCON=0x40; SCON=0x50;IE=0x90;t_empty=t_done =1;r_full=0;r_out=t_in=t_out=l;r_in=1;for(;;){loadmsg(&m);processmsg();}}。

中断习题和参考题参考答案(课后)

中断习题和参考题1、什么是中断向量?中断向量表是什么?非屏蔽中断的类型为多少?8086中断系统优先级顺序怎样?①所谓中断响量,实际上就是中断处理子程序的入口地址,每个中断类型对应一个中断响量②中断向量按照中断类型的顺序在内存0段0单元开始有规则排列的一张表③类型02H④内部中断>非屏蔽中断>可屏蔽中断>单步中断2、8259的全嵌套和特殊全嵌套方式有何异同?优先级自动循环是什么?什么特殊屏蔽方式?如何设置成该方式?①全嵌套方式是8259A最常用的工作方式,只有在单片情况下,在全嵌套方式中,中断请求按优先级0-7进行处理,0级中断的优先级最高。

特殊全嵌套方式和全嵌套方式基本相同,只有一点不同,就是在特殊全嵌套方式下,还可满足同级中断打断同级中断,从而实现一种对同级中断请求的特殊嵌套,而在全嵌套方式中,只有当更高级的中断到时,才会进行嵌套。

②优先级自动循环方式一般在系统中多个中断源优先级相等的场合。

在这种方式下,优先级队列是在变化的,一个设备受到中断服务以后,它的优先级自动降为最低。

③仅仅禁止同级中断嵌套,开放高级中断和低级中断④两步:1步设置OCW3,设置成特殊屏蔽方式,2步设置OCW1屏蔽某级中断。

3、8259有几种中断结束方式?应用场合如何?1.中断自动结束方式,不需要设置中断结束命令,在单片系统中且不会出现中断嵌套时用。

2.一般中断结束方式,在全嵌套方式下用。

3.特殊中断结束方式,在任何场合均可使用。

4、8259的ICW与中断类型码有什么关系?说明类型码为30H,36H,38H的2异同。

①高五位相同,低三位不同(中断类型码的低三位和引脚的编码有关,ICW2的低三位无意义)②30H,36H高五位相同,ICW2=30H,30H为8259A IR0对应的中断类型码,36H为8259A IR0对应的中断类型码。

38H ICW2=38H 38H为8259A IR0对应的中断类型码5、88CPU响应可屏蔽中断的条件是什么?①在现行指令周期内无总线请求;②中断允许标志IF=1;③现行指令执行完毕6、具有中断屏蔽的接口电路中的“屏蔽”同“屏蔽中断”中的“屏蔽”是否一回事,若不是,有何区别不是一回事。

MCS—51系统中断优先级...

摘要鉴于MCS-51系统只提供“二级中断嵌套”,提出扩展51系统中断优先级的纯软件方法。

其利用51系统内建的中断允许寄存器IE和中断优先级寄存器IP,通过屏蔽字机制来实现;以C51的形式,给出这种扩展方法的函数库实现,为该方法的使用赋予友好、简洁的用户接口。

大家都知道,MCS-51系统只提供“二级中断嵌套”,而大多数嵌入式系统希望有多于两级的优先级别。

因为一般来说,系统都有掉电中断,且应置为最高优先级,这样所有其它中断只能共用一个最低优先级,如此,往往不能满足实际的逻辑需求。

为了使系统具有多于两级的中断优先级别,可以利用8259A之类的中断控制芯片实现中断优先级的硬扩展,但却增加了系统的造价和复杂性。

因复杂性的提高,系统的可靠性将受到影响。

本文提出一种扩展MCS-51系统中断优先级的纯软件方法,不需增加任何硬件,且所需的额外资源消耗也很小。

实际应用表明这种方法是可行的和有效的。

关键词:MCS-51单片机、中断优先级、软扩展、C51Abstract51 - MCS due to provide only "secondary interruption, expand nested" 51 system of pure software interrupt priority. The use of the built-in 51 system allows register interrupt and interrupt priority IE IP, through the shield word registers mechanism to realize, In the form of C51 extension methods for realizing the function of library, the use of this method gives friendly user interface, concise.As is known to all, 51 - MCS provide only "2" and interrupt nested most embedded system is more than two level to priority level. Because in general, systems have power to be interrupted, and the highest priority, so that all the other interrupts can share a lowest priority, so, often cannot meet the practical needs of logic. In order to make the system has more than two levels of interrupt priority level, can use 8259A interrupt control chip realization of hardware interrupt priority, but increased the cost of system and complexity. Because of the complexity of improving the reliability of the system will be affected. This paper proposes a kind of expansion MCS - 51 system software interrupt priority methods of pure, do not need to add any additional hardware, and resource consumption is small. Actual application shows that this method is feasible and effective.Keywords: MCS - 51 SCM、interrupt priority、soft extension、C51目录第一章 MCS-51单片机介绍及中断系统简介 (1)第一节 MCS-51单片机介绍 (1)第二节中断系统简介 (1)第二章中断优先级软扩展的方法 (3)第一节方法一 (3)第二节方法二 (6)第三节方法三 (6)第三章优先级软扩展的函数库实现 (7)结束语 (11)谢辞 (12)参考文献 (13)第一章 MCS-51单片机介绍及中断系统简介第一节 MCS-51单片机介绍MCS-51单片机是指由美国INTEL公司(大名鼎鼎的INTEL)生产的一系列单片机的总称,这一系列单片机包括了好些品种,如8031,8051,8751,8032,8052,8752等,其中8051是最早最典型的产品,该系列其它单片机都是在8051的基础上进行功能的增、减、改变而来的,所以人们习惯于用8051来称呼MCS-51系列单片机,而8031是前些年在我国最流行的单片机,所以很多场合会看到8031的名称。

中断优先级以及中断嵌套

中断优先级以及中断嵌套

中断优先级有两种,叫默认优先级和嵌套优先级,假如A,B两个中断,如果A比B嵌套优先级(通过优先级寄存器设置)更高,就不需要看默认优先级了,A、B同时发生中断时A中断先执行而B后执行,而且B中断执行之间A可以抢断(嵌套)B的中断服务程序,B不可以抢断A;而如果嵌套优先级一样的话,只是A默认优先级比B更高(不需要设置),只能支持A、B同时中断时A先执行,而A不能嵌套B了,有的CPU甚至硬件上不支持嵌套,需要模拟嵌套,这个跟CPU平台有关。

关于嵌套的寄存器备份是这样进行的,进入一级中断便进行一次全套寄存器的压栈操作,压栈是把寄存器里面的值保存到栈区(属于内存区域,而并非你说的后背状态寄存器SPSR,其实后背状态寄存器SPSR也要一起压入栈区),每压入一个寄存器,SP会移动相应的距离,不会重叠;每退出一级中断便进行一次全套寄存器的出栈操作,这样就实现了保护现场和恢复现场。

可以通过编译器反汇编码窗口查看中断压栈、出栈的实现。

c语言 通信中断的优先级

c语言通信中断的优先级在进行通信时,不可避免地会遇到各种中断情况,这些中断可能会对通信过程产生不同程度的影响。

因此,对于通信中断的处理,我们需要根据其优先级进行合理的处理和应对。

本文将从不同的优先级角度,探讨通信中断的处理方法。

一、硬件中断的优先级硬件中断是指由硬件设备引发的中断,例如设备故障、数据传输错误等。

硬件中断的优先级通常较高,因为它们可能会导致系统的不稳定和数据丢失。

在处理硬件中断时,我们应该及时检测和处理,以避免进一步的故障发生。

为了提高硬件中断的处理效率,我们可以采用中断向量表的方式,将不同的硬件中断分配给不同的中断服务程序。

中断向量表按照优先级进行组织,高优先级的中断被优先处理,以确保系统的稳定性和可靠性。

二、软件中断的优先级软件中断是指由软件程序引发的中断,例如软件错误、系统调用等。

与硬件中断不同,软件中断的优先级相对较低,因为它们通常不会对系统的正常运行产生严重影响。

在处理软件中断时,我们可以采用延迟处理的方式,将其放入一个队列中,等待系统空闲时再进行处理。

为了确保软件中断的处理顺序,我们可以为每个软件中断分配一个优先级。

优先级较高的软件中断将被优先处理,以保证系统的稳定性和响应速度。

同时,我们还可以根据软件中断的紧急程度,设置不同的处理策略,例如提供相应的错误提示或自动修复功能。

三、网络中断的优先级网络中断是指由网络故障引发的中断,例如网络连接断开、数据包丢失等。

网络中断的优先级较高,因为它们会直接影响到通信的正常进行。

在处理网络中断时,我们应该及时检测和修复网络故障,以确保通信的可靠性和稳定性。

为了提高网络中断的处理效率,我们可以使用心跳机制来监测网络连接的状态。

心跳机制可以定期发送心跳包,检测网络是否正常。

一旦网络中断发生,系统可以立即做出响应,例如重新建立连接或者发送错误报告。

四、系统中断的优先级系统中断是指由操作系统引发的中断,例如系统崩溃、内存溢出等。

系统中断的优先级最高,因为它们会导致系统的完全失效。

STM32-NVIC中断优先级分组-中断优先级设置

STM32-NVIC中断优先级分组-中断优先级设置STM32-中断优先级管理NVIC1.NVIC中断优先级分组NVIC的全称是Nested vectoredinterrupt controller,即嵌套向量中断控制器。

STM32F中⽂参考⼿册中搜索向量表可以找到相应的中断说明。

CM4/CM7 内核⽀持256个中断,其中包含了16个内核中断和240个外部中断,并且具有256级的可编程中断设置。

STM32F4/F7并没有使⽤CM4内核的全部东西,⽽是只⽤了它的⼀部分。

STM32F40xx/STM32F41xx总共有92个中断。

10个内核中断,82个可屏蔽中断。

STM32F42xx/STM32F43xx则总共有97个中断。

10个内核中断,87个可屏蔽中断。

STM32F76x总共118个中断,10个内核中断,108个可屏蔽中断。

STM32具有16级可编程的中断优先级,⽽我们常⽤的就是这些可屏蔽中断。

⼏⼗个中断,怎么管理?⾸先,对STM32中断进⾏分组,组0~4。

同时,对每个中断设置⼀个抢占优先级和⼀个响应优先级值。

分组配置是在寄存器SCB->AIRCR中配置: IP bit[7:4]有4位,2^4=16,所以说它们的优先级可以有16个值,这时候如果是2位抢占优先级,那么它的值可能为0、1、2、3。

也就是抢占优先级可以取0到3 。

⾸先进⾏分组来决定⼏位抢占优先级、⼏位响应优先级。

数越⼩它的优先级越⾼。

组AIRCR[10:8]IP bit[7:4]分配情况分配结果01110:40位抢占优先级,4位响应优先级11101:31位抢占优先级,3位响应优先级21012:22位抢占优先级,2位响应优先级31003:13位抢占优先级,1位响应优先级40114:04位抢占优先级,0位响应优先级抢占优先级 & 响应优先级区别:⾼优先级的抢占优先级是可以打断正在进⾏的低抢占优先级中断的。

抢占决定了是否能打断别⼈。

51单片机中的中断优先级总结

51单片机中的中断优先级总结这段时间编写51的控制板程序,两个大牛技术指导对51中断嵌套问题的看法不一样,后来亲自验证了一下,得到了一下的一些结论,发上来大家参考,表达不清的地方还望理解,呵呵。

51单片机的中断可嵌套,但至多支持二级嵌套。

51单片机的默认(此时的IP寄存器不做设置)中断优先级为:外部中断0 > 定时/计数器0 > 外部中断1 > 定时/计数器1 > 串行中断;但这种优先级只是逻辑上的优先级,当同时有几种中断到达时,高优先级中断会先得到服务。

这种优先级实际上是中断同时到达的情况下,谁先得到服务的优先级,而不是可提供中断嵌套能力的优先级。

这种优先级被称为逻辑优先级。

例如:当计数器0中断和外部中断1(优先级计数器0中断>外部中断1)同时到达时,会进入计时器0的中断服务函数;但是在外部中断1的中断服务函数正在服务的情况下,这时候任何中断都是打断不了它的,包括逻辑优先级比它高的外部中断0计数器0中断。

要实现真正的嵌套形式的优先级,也即高优先级中断服务可以打断低优先级中断服务的情况,必须通过设置中断优先级寄存器IP来实现;这种优先级被称为物理优先级。

例如:设置IP = 0x10,即设置串口中断为最高优先级,则串口中断可以打断任何其他的中断服务函数实现嵌套,且只有串口中断能打断其他中断的服务函数。

若串口中断没有触发,则其他几个中断之间还是保持逻辑优先级,相互之间无法嵌套。

回复于:2009-10-26 16:09:35只要硬件堆栈足够.嵌套没有级数限制。

#4楼得分:0回复于:2009-10-28 10:57:5851只有两个优先级所以只能有两级嵌套!SEI是AVR单片机的,他没有分优先级,所以支持这种嵌套!C51中interrupt和using的用法void INT0()interrupt 0 using 1{.........}interrupt 0 指明是外部中断0;interrupt 1 指明是定时器中断0;interrupt 2 指明是外部中断1;interrupt 3 指明是定时器中断1;interrupt 4 指明是串行口中断;using 0 是第0组寄存器;using 1 是第1组寄存器;using 2 是第2组寄存器;using 3 是第3组寄存器;51单片机内的寄存器是R0--R7(不是R0-R3)R0-R7在数据存储器里的实际地址是由特殊功能寄存器PSW里的RS1、RS0位决定的。

51单片机基础知识 (问答题)

1、单片机的机器周期、状态周期、振荡周期和指令周期之间是什么关系?答:一个机器周期恒等于6个状态周期或12个振荡周期,即1M=6S=12P。

2、存储器中有几个保留特殊功能的单元用做入口地址?作用是什么?答:MCS-51系列单片机的存储器中有6个保留特殊功能单元;作用:0000H为复位入口、0003H为外部中断0入口、000BH为T0溢出中断入口、0013H为外部中断1入口、001BH为T1溢出中断入口、0023H为串行接口中断入口。

3、开机复位后,CPU使用是的哪组工作寄存器?它们的地址是什么?CPU如何确定和改变当前工作寄存器组?答:开机复位后,CPU使用的是第0组工作寄存器。

它们的地址是00H~07H。

CPU通过对程序状态字PSW中RS1、RS0的设置来确定和改变当前工作寄存器组。

如:RS1、RS0为00则指向第0组;为01则指向第1组;为10则指向第2组;为11则指向第3组。

4、MCS-51的时钟周期、机器周期、指令周期的如何分配的?当振荡频率为8MHz时,一个单片机时钟周期为多少微秒?答:MCS-51的时钟周期是最小的定时单位,也称为振荡周期或节拍。

一个机器周期包含12个时钟周期或节拍。

不同的指令其指令周期一般是不同的,可包含有1~4个机器周期。

当振荡频率为8MHz时,一个单片机时钟周期为0.125μs 。

5、EA/V引脚有何功用?8031的引脚应如何处理?为什么?PP答:EA/V是双功能引脚:PP(1)EA接高电平时,在低4KB程序地址空间(0000H~0FFFH),CPU执行片内程序存储器的指令,当程序地址超出低4KB空间(1000H~FFFFH)时,CPU将自动执行片外程序存储器的指令。

(2)EA接低电平时,CPU只能执行外部程序存储器的指令。

8031单片机内部无ROM,必须外接程序存储器。

因此,8031的EA引脚必须接低电平。

在对8751单片机内部的 EPROM编程时,此引脚V外接+12V电压,用于固化EPROM程PP序。

操作系统中的中断处理与中断嵌套机制

操作系统中的中断处理与中断嵌套机制中断处理与中断嵌套机制在操作系统中起着重要的作用。

中断是指计算机在执行过程中遇到了某些特定条件或事件,需要立即打断当前正在执行的任务去执行其他任务的机制。

操作系统通过中断处理和中断嵌套机制,实现了对计算机的及时响应和多任务处理能力。

本文将详细介绍操作系统中的中断处理和中断嵌套机制。

一、中断的概念和分类中断是指计算机执行过程中的一种打断机制,当计算机遇到特定条件或事件时,会暂停当前的任务,转而执行其他任务。

中断处理系统根据中断的来源和作用可以分为外部中断和内部中断。

外部中断是指来自计算机外部设备的中断信号,如硬盘读写中断、键盘输入中断等。

内部中断则是发生在CPU内部的一些特殊事件,如非法指令或运算溢出等。

二、中断处理的过程中断处理一般包括中断请求、中断响应和中断服务三个主要过程。

1.中断请求:当计算机遇到中断事件时,外设或者硬件会发送中断请求信号给CPU,请求将当前任务暂停,去执行其他任务。

2.中断响应:CPU接收到中断请求信号后,会把正在执行的指令暂停,保存现场,然后根据中断类型跳转到相应的中断服务程序。

3.中断服务:中断服务程序是为了处理中断事件而编写的一段程序,其中包含了具体的中断处理逻辑。

在中断服务过程中,系统会执行一系列操作来响应中断事件,如读取输入缓冲区、操作外设等。

中断服务处理完成后,将会恢复之前的任务继续执行。

三、中断嵌套机制中断嵌套机制是指在处理一个中断的过程中,是否可以被更高优先级的中断打断,从而处理更紧急的中断请求。

中断嵌套机制可以提高操作系统的处理效率和响应能力。

1.中断优先级:在中断处理过程中,不同的中断具有不同的优先级。

通常,系统中的中断优先级分为高优先级和低优先级。

当高优先级中断请求到来时,会打断正在执行的低优先级中断服务程序,处理高优先级中断。

2.中断屏蔽:当CPU正在执行一个中断服务程序时,如果有更高优先级的中断请求到来,需要保证这个更高优先级的中断能够立即得到响应。

1、80C51中断系统中有几个中断源请写出这些中断源同级

1、80C51中断系统中有几个中断源?请写出这些中断源同级时优先级的顺序。

80C51有五个中断源。

由最高到最低的次序依次为外部中断0中断、定时器0中断、外部中断1中断、定时器1中断、串行口中断2、80c51各中断标志是如何产生的,又是如何清0的?产生中断标志可以外部中断的低电平触发或者是下降沿触发,定时器/计数器的溢出以及串行口的发送和接受。

中断的清除可有三种方式:硬件自动清除(适用于T0、T1以及下降沿触发的外部中断)、软件清除(适用于串行口中断)、外加硬件清除(适用于低电平触发的外部中断)3、在外部中断中,有几种触发方式?如何选择中断源的触发方式?有两种触发方式,分别为低电平触发和下降沿触发。

中断的触发方式有TCON 中的IT0、IT1控制,若为0,则是低电平触发;若为1,则是下降沿触发。

4、80c51中断系统中有几个优先级别?如何设定?有高低两个优先级。

中断系统中本来就存在自然优先级,同样也可以通过特殊功能寄存器IP中各个位的设置,改变原来的优先级。

置位时为高优先级组,清零时为低优先级组。

5、简述MCS-51中断响应的过程。

1:CPU在每个机器周期的S5P2检测中断源。

在下一个机器周期的S6期间,若有某中断标志位为1,则按优先级高低进行处理,响应中断。

2:响应中断后,CPU首先使被响应中断的相应的优先级激活触发器置位,以阻挠同级和低优先级的中断响应,然后执行硬件生成的长调用指令“LCALL”,将程序计数器PC的内容压入堆栈保护起来。

3:将对应中断源的中断矢量地址装入程序计数器PC,使程序转向该中断矢量地址,去执行中断服务程序,直至遇到RETI为止。

4:执行RETI指令,从堆栈中弹出断点地址进入PC,恢复原程序的执行。

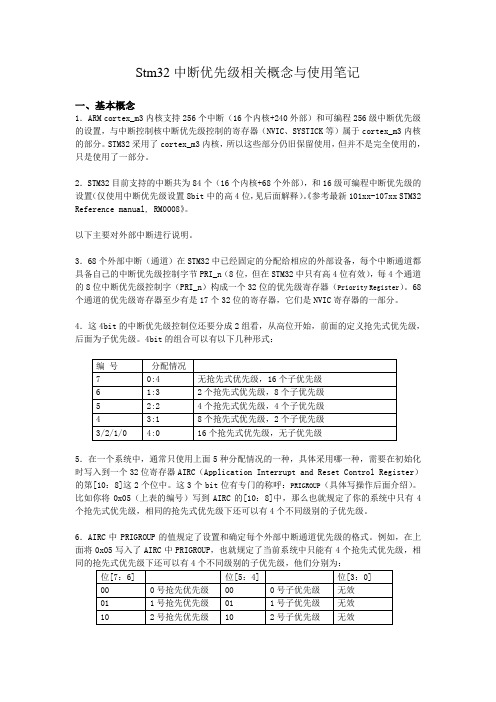

Stm32中断优先级相关概念与使用笔记Word文档

Stm32中断优先级相关概念与使用笔记一、基本概念1.ARM cortex_m3内核支持256个中断(16个内核+240外部)和可编程256级中断优先级的设置,与中断控制核中断优先级控制的寄存器(NVIC、SYSTICK等)属于cortex_m3内核的部分。

STM32采用了cortex_m3内核,所以这些部分仍旧保留使用,但并不是完全使用的,只是使用了一部分。

2.STM32目前支持的中断共为84个(16个内核+68个外部),和16级可编程中断优先级的设置(仅使用中断优先级设置8bit中的高4位,见后面解释)。

《参考最新101xx-107xx STM32 Reference manual, RM0008》。

以下主要对外部中断进行说明。

3.68个外部中断(通道)在STM32中已经固定的分配给相应的外部设备,每个中断通道都具备自己的中断优先级控制字节PRI_n(8位,但在STM32中只有高4位有效),每4个通道的8位中断优先级控制字(PRI_n)构成一个32位的优先级寄存器(Priority Register)。

68个通道的优先级寄存器至少有是17个32位的寄存器,它们是NVIC寄存器的一部分。

4.这4bit的中断优先级控制位还要分成2组看,从高位开始,前面的定义抢先式优先级,后面为子优先级。

4bit的组合可以有以下几种形式:5.在一个系统中,通常只使用上面5种分配情况的一种,具体采用哪一种,需要在初始化时写入到一个32位寄存器AIRC(Application Interrupt and Reset Control Register)的第[10:8]这2个位中。

这3个bit位有专门的称呼:PRIGROUP(具体写操作后面介绍)。

比如你将0x05(上表的编号)写到AIRC的[10:8]中,那么也就规定了你的系统中只有4个抢先式优先级,相同的抢先式优先级下还可以有4个不同级别的子优先级。

6.AIRC中PRIGROUP的值规定了设置和确定每个外部中断通道优先级的格式。