CMOS晶体管基础

cmos的原理

cmos的原理

CMOS(亦称Complementary Metal-Oxide-Semiconductor)是

一种集成电路技术,也是一种制造这种技术的电晶体。

CMOS 芯片由NMOS和PMOS两种类型的晶体管组成,其原理基于

这两种晶体管的互补关系。

NMOS晶体管是N沟道开关型晶体管,由P型基质,在其中

形成了N型沟道。

当输入电压为高电平(逻辑“1”)时,基质

和源结之间的电势差足够大,导电层形成,电流可以通过。

而当输入电压为低电平(逻辑“0”)时,P基质和源结之间的电

势差不足以形成导电层,导致电流断开,此时晶体管处于关断状态。

PMOS晶体管是P沟道开关型晶体管,由N型基质,在其中

形成了P型沟道。

与NMOS晶体管相反,当输入电压为高电

平时,P基质和源结之间的电势差足够大,导电层形成,电流

可以通过。

而当输入电压为低电平时,N基质和源结之间的电势差不足以形成导电层,导致电流断开,晶体管处于关断状态。

CMOS技术通过将NMOS和PMOS晶体管连接在一起,形成

了互补的结构。

这样的结合使得CMOS电路具有很高的抗干

扰能力和功耗效率。

CMOS电路在逻辑门设计和数字电路中

得到广泛应用,如存储器、微控制器以及在电脑芯片等领域。

CMOS技术还可以实现低电平逻辑设计,从而让电路工作在

更低的功耗和噪声水平上。

总之,CMOS电路的原理基于NMOS和PMOS晶体管的互补

特性,利用两种晶体管之间的开关行为来实现逻辑功能。

这种技术带来了高性能、低功耗、高抗干扰能力和可靠性的优势,在现代集成电路设计中起着至关重要的作用。

CMOS工艺要点

CMOS工艺要点1.CMOS工艺的基本结构是互补的NMOS(N型金属氧化物半导体)和PMOS(P型金属氧化物半导体)晶体管。

这两种晶体管的结构和工作原理互补,可以实现低功率消耗和高集成度。

2.CMOS工艺的制备过程基于晶圆的批量生产。

首先,在硅衬底上生长一层二氧化硅(SiO2)薄膜,然后通过光刻和蚀刻工艺形成了晶体管的控制门电极。

接下来,通过注入掺杂物来形成NMOS和PMOS的源与漏区域。

最后,通过金属引脚和连线将晶体管连接在一起。

3.CMOS工艺采用高纯度晶体硅材料作为衬底,使得晶体管的电子迁移率高。

同时,CMOS工艺还采用了硅二氧化物(SiO2)作为绝缘层来隔离晶体管和金属导线,提高了电路的良好性能。

4.CMOS工艺具有极低的功耗特性。

由于互补的晶体管结构,只有在逻辑电路切换时才会产生瞬态电流,其他时候几乎没有电流通过。

这使得CMOS工艺非常适合移动设备,如智能手机和平板电脑,因为电池寿命可以得到更好的保持。

5.CMOS工艺的集成度很高。

由于可以在晶圆上同时制造多个晶体管和其他电子器件,因此CMOS工艺可以实现非常复杂的电路设计,从而提供更强大的计算和功能性能。

6.CMOS工艺具有一定的可靠性和稳定性。

晶体管的硅二氧化物绝缘层可以提供良好的电离隔离,使得晶体管具有较低的泄漏电流和较高的开关速度。

此外,CMOS工艺还提供了对精密电流和电压控制的良好性能。

总之,CMOS工艺是现代集成电路制造中最重要的工艺之一、它具有低功耗、高集成度、高性能和可靠性的特点,使得它成为各种电子设备和系统的首选工艺。

随着科技的进步,CMOS工艺仍然在不断发展,以适应越来越高的性能和集成度要求。

CMOS基础及基本工艺流程

CMOS基础及基本工艺流程

1.单晶硅衬底制备:首先需要准备单晶硅衬底,它是整个集成电路的

基础。

这一步骤通常会涉及硅片切割和粗化,最终得到大小合适的硅衬底。

2.外延生长:在单晶硅衬底上外延生长蓝宝石或氮化硅等薄膜,这些

薄膜将作为隔离层使用,以电隔离各个晶体管。

3.门电极制备:在隔离层上制备门电极。

通常使用化学气相沉积(CVD)或物理气相沉积(PVD)等技术,在薄膜上沉积一层金属,如铝或钨。

4.掺杂:利用掺杂技术向单晶硅衬底中注入掺杂物(例如硼或磷),

以改变硅的电子特性。

5.晶体管制备:利用光刻技术定义出晶体管的结构,通过曝光、阻挡、显影等步骤,制造出源极、栅极和漏极之间的结构。

6.金属互连:使用金属沉积和光刻技术,在晶体管上制造出金属互连层,将各个晶体管连接在一起。

7.电介质和过程模拟:制备电介质层,通常使用氧化硅或氧化铝等材料。

过程模拟是为了检测制造过程中的缺陷和问题。

8.上下电极制备:制造上下电极用于晶体管之间的连接。

9.晶体管测试:测试晶体管的性能和可靠性。

10.封装和测试:最后,将制造好的芯片封装成集成电路,并进行最

终的测试。

以上是CMOS基本工艺流程的主要步骤,每个步骤都需精确控制和复杂操作,以确保芯片的性能和可靠性。

CMOS技术由于其功耗低、稳定性好和集成度高等优点,被广泛应用于各种电子设备中,如微处理器、存储器、传感器等。

cmos电路和器件基本结构

cmos电路和器件基本结构CMOS电路和器件基本结构一、引言CMOS(亦称为互补金属-氧化物-半导体)电路是一种常用的逻辑电路,它由NMOS(N型金属-氧化物-半导体)和PMOS(P型金属-氧化物-半导体)两种互补型的MOSFET(金属-氧化物-半导体场效应晶体管)组成。

CMOS电路以其低功耗、高集成度和低电压操作等特点,在现代集成电路设计中得到广泛应用。

本文将介绍CMOS电路和器件的基本结构。

二、CMOS电路的基本结构1. NMOS器件NMOS器件由P型衬底上生长的N型沟道和两个掺入P型源极和漏极的P型扩散区组成。

沟道区域上方由一层薄的氧化硅(SiO2)作为绝缘层,上面再覆盖一层金属(通常为铝)作为电极。

当沟道区没有电压施加时,NMOS处于截止状态,导通状态需要在沟道区施加正电压。

2. PMOS器件PMOS器件与NMOS器件相反,由N型衬底上生长的P型沟道和两个掺入N型源极和漏极的N型扩散区组成。

沟道区域上方同样有一层氧化硅和金属电极。

当沟道区施加负电压时,PMOS处于导通状态,截止状态需要在沟道区施加正电压。

3. CMOS电路CMOS电路是通过将NMOS和PMOS器件相互串联或并联而构成的。

在CMOS电路中,NMOS器件的漏极与PMOS器件的源极相连,共同组成电路的输出端;NMOS器件的源极与PMOS器件的漏极相连,共同组成电路的输入端。

当输入信号施加到NMOS和PMOS器件上时,根据不同的输入信号电平,其中一个器件处于导通状态,另一个器件处于截止状态,从而实现电路的逻辑功能。

三、CMOS电路的工作原理CMOS电路的工作原理是基于MOSFET的三个重要特性:沟道截止、沟道饱和和门极电势控制。

当输入信号为低电平时,NMOS处于导通状态,PMOS处于截止状态,此时电路输出为高电平;当输入信号为高电平时,NMOS处于截止状态,PMOS处于导通状态,此时电路输出为低电平。

由于CMOS电路的输出仅在输入发生变化时才会改变,且输出信号的上升和下降均经过一个NMOS和一个PMOS器件,因此CMOS电路具有较低的功耗和较高的抗噪声能力。

cmos晶体管原理

cmos晶体管原理CMOS晶体管原理什么是CMOS晶体管CMOS(Complementary Metal-Oxide-Semiconductor,互补金属氧化物半导体)晶体管是一种常用于数字集成电路中的半导体器件。

它由P型沟道MOSFET(PMOS)和N型沟道MOSFET(NMOS)组成。

CMOS的基本原理CMOS晶体管的基本原理是利用P型和N型MOSFET的互补特性,实现器件的低功耗、高集成度和高可靠性。

P型MOSFET•噪声:P型MOSFET受控极为基区,电流由基区中的电子恢复时间决定,因此噪声较大。

•寿命:电荷注入效应会导致电子在基区游离,造成寿命的降低。

N型MOSFET•噪声:N型MOSFET的噪声较小,因为电流由电子决定,而电子的恢复时间较短。

•寿命:寿命较长,因为电子注入基区不会关联到电子的迁移。

互补特性CMOS晶体管由P型和N型MOSFET组成,因此能够克服P型和N 型MOSFET各自的缺点,实现高性能和低功耗的优势。

CMOS工作原理CMOS晶体管工作分为两个阶段:开关阶段和恢复阶段。

开关阶段在开关阶段,当输入信号为高电平时,P型MOSFET导通,N型MOSFET截止;当输入信号为低电平时,P型MOSFET截止,N型MOSFET 导通。

这样就实现了输出信号的高低电平反转。

恢复阶段在恢复阶段,当输入信号经过传输延时后,P型MOSFET和N型MOSFET同时切换状态,完成信号的恢复。

CMOS的应用CMOS晶体管由于其低功耗、高集成度和高可靠性的特点,在各种数字集成电路中得到广泛应用:1.微处理器和微控制器:CMOS晶体管实现了高速运算和低功耗。

2.存储器:CMOS晶体管实现了高密度集成和快速读写。

3.传感器:CMOS晶体管用于光电传感器和温度传感器等。

4.通信系统:CMOS晶体管用于射频功率放大器和射频开关等。

综上所述,CMOS晶体管是一种重要的数字集成电路器件,它的工作原理和特性使得其在现代科技中起着不可或缺的作用。

cmos的基本原理

cmos的基本原理CMOS的基本原理CMOS是一种重要的集成电路技术,其基本原理是通过控制两个互补的金属氧化物半导体(Metal-Oxide-Semiconductor)场效应晶体管(MOSFET)的导通和截断来实现电路的逻辑运算。

CMOS电路由p型和n型MOSFET组成,可以实现低功耗、高集成度和高可靠性的电路设计。

CMOS电路的基本元件是MOSFET,它是一种三端口器件,包括栅极、漏极和源极。

根据栅极的工作电压,MOSFET可以分为两种类型:pMOSFET和nMOSFET。

pMOSFET的栅极与源极之间的电压为正时,pMOSFET导通;nMOSFET的栅极与源极之间的电压为负时,nMOSFET导通。

通过适当的电路连接,可以实现不同的逻辑操作。

CMOS电路的关键是通过pMOSFET和nMOSFET之间的互补工作来实现逻辑功能。

在CMOS电路中,pMOSFET和nMOSFET是互补的,即当pMOSFET导通时,nMOSFET截断;当nMOSFET导通时,pMOSFET截断。

这种互补工作方式使得CMOS电路具有低功耗特性,因为只有在逻辑操作时才会有电流流过器件。

CMOS电路的逻辑门是由多个MOSFET组成的。

最常见的逻辑门有与门、或门、非门和异或门。

与门由两个或多个输入和一个输出组成,只有当所有输入均为高电平时,输出才为高电平;或门也由两个或多个输入和一个输出组成,只要输入中有一个为高电平,输出就为高电平;非门只有一个输入和一个输出,当输入为高电平时,输出为低电平,反之亦然;异或门有两个输入和一个输出,当两个输入相等时,输出为低电平,否则输出为高电平。

CMOS电路的优点是低功耗和高集成度。

由于CMOS电路只在逻辑操作时才有电流流过,因此其功耗相对较低。

此外,CMOS电路的工作电压范围广,可以适应不同的应用场景。

CMOS技术还具有高集成度的特点,可以在一块芯片上集成大量的逻辑门和其他功能模块,实现复杂的系统设计。

第08章-CMOS工艺双极型晶体管和二极管

白雪飞 中国科学技术大学电子科学与技术系

提纲

• CMOS工艺双极型晶体管 • CMOS工艺二极管

2

CMOS工艺双极型晶体管

寄生双极型晶体管

• CMOS工艺是为了制造MOS电路而优化设计的 • CMOS工艺只能生成寄生双极型晶体管,其性能不及标准双极工艺或 BiCMOS工艺的双极型晶体管

• CMOS工艺寄生双极型晶体管在电路设计中也可以加以利用

4

衬底PNP晶体管

• 任何N阱CMOS工艺都可以制作衬底PNP晶体管

– 发射区:P型扩散 – 基 区:N阱 – 集电区:P型衬底

5

衬底PNP晶体管版图

(A) 采用叉指状发射区的版图 (B) 采用小接触孔大面积发射区的版图

6

横向PNP晶体管

N阱CMOS工艺横向PNP晶体管

可以获得较高的增益

7

浅阱晶体管

Байду номын сангаас

CMOS工艺浅阱NPN晶体管

8

CMOS工艺二极管

CMOS结型二极管

PSD/N阱二极管 可用于ESD保护结构

10

CMOS肖特基二极管

CMOS工艺制造的PSD保护环肖特基二极管

11

匹配PN结二极管

匹配PSD/N阱二极管

12

本章结束

cmos电路和器件基本结构

cmos电路和器件基本结构CMOS电路和器件基本结构CMOS(Complementary Metal-Oxide-Semiconductor)电路是一种广泛应用于数字集成电路中的技术。

CMOS电路由CMOS 器件构成,它是一种特殊的半导体器件。

本文将介绍CMOS电路和器件的基本结构。

一、CMOS电路的基本原理CMOS电路的基本原理是利用n型MOS(NMOS)和p型MOS (PMOS)两种互补型的场效应晶体管(FET)来实现电路的逻辑功能。

NMOS和PMOS的特性互补,通过它们的联合工作可以实现低功耗、高集成度和高噪声抑制的优点。

二、CMOS器件的基本结构CMOS器件由一对互补型的MOSFET组成,即NMOS和PMOS。

这两种器件的基本结构如下:1. NMOS结构NMOS器件由一个n型沟道和两个控制电极(栅极和源极)组成。

栅极用于控制沟道的导电性,源极和漏极用于连接电路。

当栅极施加高电压时,沟道会形成导电通道,电流可以从源极流向漏极;当栅极施加低电压时,导电通道关闭,电流无法流动。

2. PMOS结构PMOS器件由一个p型沟道和两个控制电极(栅极和源极)组成。

栅极用于控制沟道的导电性,源极和漏极用于连接电路。

与NMOS 相反,当栅极施加低电压时,沟道会形成导电通道,电流可以从源极流向漏极;当栅极施加高电压时,导电通道关闭,电流无法流动。

三、CMOS电路的工作原理CMOS电路的工作原理是利用两个互补型MOSFET的特性,通过不同的输入信号来控制输出信号。

当输入信号为高电平时,NMOS 导通,PMOS截止;当输入信号为低电平时,PMOS导通,NMOS 截止。

这样就实现了输入信号与输出信号之间的逻辑关系。

四、CMOS电路的优点CMOS电路具有以下几个优点:1. 低功耗:CMOS电路只在切换时才消耗电能,而静态时几乎不消耗电能,因此功耗较低。

2. 高集成度:CMOS电路中的晶体管可以非常小型化,因此可以实现高度集成的芯片设计。

CMOS制作基本工艺解读

CMOS制作基本步骤CMOS的制作步骤是需要经过一系列的复杂的化学和物理操作最终形成集成电路。

而做为一名集成电路版图(ic layout)工程师,对于这个在半导体制造技术中具有代表性的CMOS工艺流程有个系统的了解是有很大帮助的。

个人认为只有了解了工艺的版工才会在IC Layout的绘制中考虑到你所画的版图对流片产生的影响。

芯片制造厂(Fab)大概分为:扩散区,光刻区,刻蚀区,离子注入区,薄膜区和抛光区。

扩散是针对高温工艺,光刻利用光刻胶在硅处表面刻印,刻蚀将光刻胶的图形复制在硅片上,离子注入对硅片掺杂,薄膜区淀积介质层和金属层,抛光主要是平坦化硅片的上表面。

简化的CMOS工艺由14个生产步骤组成:(1)双阱注入在硅片上生成N阱和P阱。

(2)浅槽隔离用于隔离硅有源区。

(3)通过生长栅氧化层、淀积多晶硅和刻印得到栅结构。

(4)LDD注入形成源漏区的浅注入。

(5)制作侧墙在随后的源、漏注入当中保护沟道。

(6)中等能量的源、漏注入,形成的结深大于LDD的注入深度。

(7)金属接触形成硅化物接触将金属钨和硅紧密结合在一起。

(8)局部互连形成晶体管和触点间的第一层金属线。

(9)第一层层间介质淀积,并制作连接局部互连金属和第一层金属的通孔1。

(10)用于第一次金属刻蚀的第一层金属淀积金属三明治结构并刻印该层金属。

(11)淀积第二层层间介质并制作通孔2。

(12)第二层金属通孔3淀积第二层金属叠加结构,并淀积和刻蚀第三层层间介质。

(13)第三层金属到压点刻蚀、合金化重复这些成膜工艺直到第五层金属压焊淀积完毕,随后是第六层层间介质和钝化层的制作。

(14)最后一步工艺是参数测试,验证硅片上每一个管芯的可靠性。

在之前的文章中以一个PMOS和一个NMOS构成的反相器为例,简单的分步介绍了CMOS制作的基本步骤,整个流程就是对上述步骤的详细解说。

不同的是(9)(10)被合在一起介绍,(11)(12)(13)被合在一起介绍,而(14)则没有列入到详解步骤中。

cmos工作原理

cmos工作原理CMOS工作原理。

CMOS是一种常见的集成电路制造工艺,它在现代电子设备中扮演着至关重要的角色。

CMOS工作原理是指在CMOS集成电路中,晶体管的工作原理和电荷传输的机制。

下面我们将详细介绍CMOS工作原理的相关内容。

首先,我们来看看CMOS的基本结构。

CMOS由N型金属氧化物半导体场效应晶体管(NMOS)和P型金属氧化物半导体场效应晶体管(PMOS)组成。

这两种晶体管的工作原理是互补的,它们共同构成了CMOS电路的基础。

在CMOS中,NMOS和PMOS晶体管是交替连接的,当NMOS导通时,PMOS截止,反之亦然。

这种结构使得CMOS在工作时能够实现低功耗和高稳定性的特性。

其次,我们来了解一下CMOS的工作原理。

在CMOS中,当输入信号为高电平时,NMOS导通,PMOS截止;当输入信号为低电平时,NMOS截止,PMOS导通。

通过这种方式,CMOS能够实现在不同输入信号下的高低电平输出。

这种工作原理使得CMOS在数字电路中有着广泛的应用,如逻辑门、寄存器、存储器等。

另外,CMOS的工作原理还涉及到电荷传输的过程。

在CMOS中,当输入信号改变时,NMOS和PMOS晶体管中的电荷会发生变化,从而导致输出信号的变化。

这种电荷传输的机制是CMOS能够实现高速、低功耗的重要原因之一。

此外,CMOS还能够实现多路复用、集成度高、抗干扰能力强等特性,这些都与其工作原理密切相关。

总结一下,CMOS的工作原理是基于NMOS和PMOS晶体管的互补工作特性,通过控制输入信号来实现高低电平输出,从而完成数字电路中的各种逻辑功能。

同时,CMOS还依靠电荷传输的机制来实现高速、低功耗的特性。

这些特点使得CMOS在现代集成电路中得到了广泛的应用,成为了数字电路设计中不可或缺的一部分。

通过本文的介绍,相信大家对CMOS的工作原理有了更深入的了解。

在今后的学习和工作中,我们可以更好地利用CMOS的特性,设计出更加高效、稳定的电子设备和系统。

CMOS集成电路基础知识

CMOS集成电路基础知识CMOS是ComplementaryMetal-OxideSemiconductor一词的缩写。

在业余电子制作中我们经常会用到它,这里系统、详细的介绍一些CMOS 集成电路基础知识及使用注意事项。

CMOS集成电路的性能及特点功耗低CMOS集成电路采用场效应管,且都是互补结构,工作时两个串联的场效应管总是处于一个管导通,另一个管截止的状态,电路静态功耗理论上为零。

实际上,由于存在漏电流,CMOS电路尚有微量静态功耗。

单个门电路的功耗典型值仅为20mW,动态功耗(在1MHz工作频率时)也仅为几mW。

工作电压范围宽CMOS集成电路供电简单,供电电源体积小,基本上不需稳压。

国产CC4000系列的集成电路,可在3~18V电压下正常工作。

逻辑摆幅大CMOS集成电路的逻辑高电平“1”、逻辑低电平“0”分别接近于电源高电位VDD及电影低电位VSS。

当VDD=15V,VSS=0V时,输出逻辑摆幅近似15V。

因此,CMOS集成电路的电压电压利用系数在各类集成电路中指标是较高的。

抗干扰能力强CMOS集成电路的电压噪声容限的典型值为电源电压的45%,保证值为电源电压的30%。

随着电源电压的增加,噪声容限电压的绝对值将成比例增加。

对于VDD=15V的供电电压(当VSS=0V时),电路将有7V 左右的噪声容限。

输入阻抗高CMOS集成电路的输入端一般都是由保护二极管和串联电阻构成的保护网络,故比一般场效应管的输入电阻稍小,但在正常工作电压范围内,这些保护二极管均处于反向偏置状态,直流输入阻抗取决于这些二极管的泄露电流,通常情况下,等效输入阻抗高达103~1011Ω,因此CMOS集成电路几乎不消耗驱动电路的功率。

温度稳定性能好由于CMOS集成电路的功耗很低,内部发热量少,而且,CMOS电路线路结构和电气参数都具有对称性,在温度环境发生变化时,某些参数能起到自动补偿作用,因而CMOS集成电路的温度特性非常好。

7nmcmos逻辑芯片的主体晶体管结构

7nmcmos逻辑芯片的主体晶体管结构7nm CMOS逻辑芯片的主体晶体管结构一、引言CMOS(Complementary Metal-Oxide-Semiconductor)逻辑芯片是现代电子设备中常见的集成电路,它由许多晶体管组成,其中晶体管是其核心部件之一。

本文将重点介绍7nm CMOS逻辑芯片的主体晶体管结构。

二、7nm CMOS逻辑芯片的晶体管简介晶体管是一种控制电流的器件,由半导体材料制成。

在CMOS逻辑芯片中,晶体管的主要作用是实现信号的放大和开关控制。

7nm CMOS逻辑芯片采用了7纳米工艺制造,相比于传统的工艺,具有更小的尺寸和更高的集成度。

三、7nm CMOS逻辑芯片的主体晶体管结构7nm CMOS逻辑芯片的主体晶体管结构主要包括NMOS(N-type Metal-Oxide-Semiconductor)和PMOS(P-type Metal-Oxide-Semiconductor)两种类型的晶体管。

1. NMOS晶体管NMOS晶体管由N型半导体材料构成,其结构包括源极(Source)、漏极(Drain)和栅极(Gate)。

在7nm CMOS逻辑芯片中,NMOS晶体管的源极和漏极是金属材料,栅极是由金属和氧化物构成的。

NMOS晶体管的工作原理是:当栅极电压低于源极电压时,NMOS 晶体管处于关闭状态,没有电流通过;当栅极电压高于源极电压时,NMOS晶体管处于导通状态,电流可以从源极流向漏极。

2. PMOS晶体管PMOS晶体管由P型半导体材料构成,其结构也包括源极、漏极和栅极。

在7nm CMOS逻辑芯片中,PMOS晶体管的源极和漏极是金属材料,栅极同样由金属和氧化物构成。

PMOS晶体管的工作原理与NMOS晶体管相反:当栅极电压高于源极电压时,PMOS晶体管处于关闭状态;当栅极电压低于源极电压时,PMOS晶体管处于导通状态。

3. CMOS逻辑门电路在7nm CMOS逻辑芯片中,利用NMOS和PMOS晶体管的不同工作原理,可以构建出各种逻辑门电路,如与门、或门、非门等。

《CMOS晶体管基础》课件

需要建立更完善的可靠性测试与评估方法,以确 保CMOS晶体管的可靠性和稳定性。

新材料与新器件结构的探索

新材料的应用

为了克服现有材料的限制,需要探索新的材 料应用于CMOS晶体管中,如高迁移率材料 、二维材料等。

新器件结构的探索

为了提高CMOS晶体管的性能和功能,需要探索新 的器件结构,如新型的逻辑门电路、三维集成等。

CMOS晶体管的发展历程

总结词

CMOS晶体管的发展经历了从20世纪60年代的初期研究到现在的广泛应用的过程。

详细描述

20世纪60年代初期,人们开始研究CMOS晶体管,并逐渐认识到其低功耗和高可靠性的优点。随着半导体工艺 技术的不断进步,CMOS晶体管的性能得到了显著提升,应用领域也不断扩大。现在,CMOS晶体管已经成为集 成电路中的基本元件,广泛应用于各种电子设备中。

等。

03

CMOS晶体管的制造工 艺

衬底材料的选择

01

02

03

衬底材料

硅是最常用的衬底材料, 因为它具有高导热性、高 耐久性和低成本。

晶向选择

根据晶体管的设计要求, 选择适当的晶向以获得最 佳性能。

衬底质量

衬底应无缺陷、杂质和裂 缝,以确保晶体管的可靠 性和稳定性。

掺杂工艺

元素选择

选择适当的元素进行掺杂,以改变材料的导电性 能。

《cmos晶体管基础》ppt课件

目录

• CMOS晶体管简介 • CMOS晶体管的工作原理 • CMOS晶体管的制造工艺 • CMOS晶体管的性能优化 • CMOS晶体管的挑战与展望

01

CMOS晶体管简介

定义与特性

总结词

CMOS晶体管是一种集成电路的基本元件,具有低功耗、高噪声容限、高可靠性等特性 。

cmos晶体管原理

CMOS晶体管原理CMOS(Complementary Metal-Oxide-Semiconductor)晶体管是一种常用的半导体器件,广泛应用于数字集成电路和微处理器等领域。

CMOS晶体管由P型和N型金属氧化物半导体场效应晶体管(MOSFET)组成,具有低功耗、高集成度和可靠性等优点。

本文将详细解释与CMOS晶体管原理相关的基本原理。

1. MOSFET基本结构MOSFET是一种三层结构的器件,包括源极(Source)、漏极(Drain)和栅极(Gate)三个区域。

其中,源极和漏极之间通过一个薄的氧化层隔离,形成了一个通道,栅极则位于氧化层的上方控制通道的导电性。

MOSFET根据不同的掺杂类型和导电性可以分为两种类型:N沟道MOS(NMOS)和P 沟道MOS(PMOS)。

在CMOS技术中,NMOS和PMOS结合使用,构成了CMOS逻辑电路。

2. MOSFET工作原理MOSFET的工作原理可以分为三个阶段:截止区、线性区和饱和区。

下面将详细介绍每个阶段的工作原理。

2.1 截止区当栅极电压低于阈值电压时,MOSFET处于截止区。

此时,栅极和漏极之间的通道被隔断,无法形成导电通路。

该状态下,MOSFET的漏极电流非常小,可以忽略不计。

2.2 线性区当栅极电压高于阈值电压时,MOSFET进入线性区。

此时,栅极电压的变化会影响通道的导电性,从而控制漏极电流的大小。

当栅极电压增加,通道导电性增强,漏极电流也相应增大。

2.3 饱和区当栅极电压进一步增加,超过一定阈值电压时,MOSFET进入饱和区。

在饱和区,通道已经完全形成,栅极电压的增加不会再影响漏极电流。

此时,漏极电流保持稳定,不再增大。

3. CMOS逻辑门电路CMOS技术利用NMOS和PMOS的互补特性构建逻辑门电路。

逻辑门电路是数字电路的基本组成单元,用于实现逻辑运算和数据处理。

CMOS逻辑门电路由一对互补的NMOS和PMOS组成,通过电压的控制来实现逻辑运算。

CMOS集成电路设计基础1

dUTH 4mV / C dT dUTH 2mV / C dT

重掺杂 轻掺杂

λn、 λp——沟道调制系数, 即UDS对沟道长 度的影响。

NMOS PMOS

n

1 UA

0.01/V

p

1 UA

0.02 /V

式中, UA为厄尔利电压(Early Voltage)

对于典型的0.5 μm工艺的MOS管, 忽略沟道调制效应, 其 主要参数如下表所示

衬底的连接

UDD

G

B

S

D

G

B

S

D

N+

P+

P+

N型 衬 底 (a)

P+

N+

N+

P型 衬 底 (b)

为了使MOS管的电流只在导电沟道中沿表面流动而不产生垂直 于衬底的额外电流, 源区、 漏区以及沟道和衬底间必须形成反

偏的PN结隔离, 因此, NMOS管的衬底B必须接到系统的最低 电位点(例如“地”), 而PMOS管的衬底B必须要接到系统的最 高电位点(例如正电源UDD)。 衬底的连接如图 (a)、 (b)所示。

L、 W尺寸对UTH的影响

在长沟道器件中, 阈值电压UTH与沟道长度L和沟 道宽度W的关系不大; 而在短沟道器件中, UTH与L、 W的关系较大。 UTH随着L的增大而增大, 随着W的 增大而减小。

UTH / V Nsub = 1107 cm- 3

Nsub = 1106 cm- 3

0

1

2

3

4

(a)

μp——空穴迁移率(单位电场作用下空穴的迁移速度)。 μp≈500 cm2/s·V

n 1300 2.6 p 500

Cox——单位面积栅电容

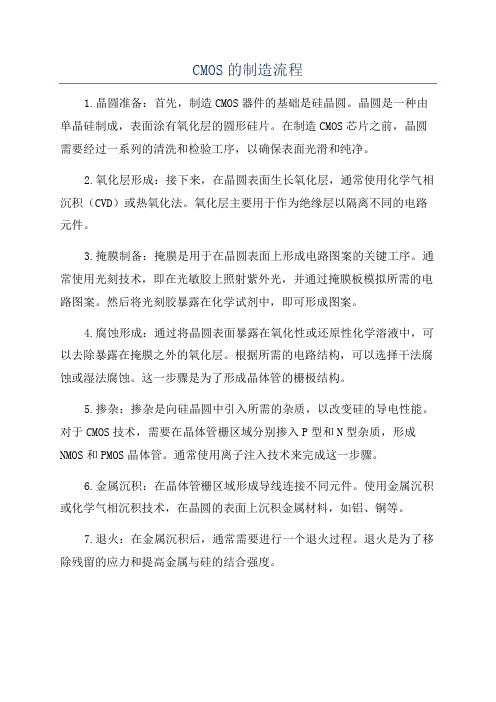

CMOS的制造流程

CMOS的制造流程1.晶圆准备:首先,制造CMOS器件的基础是硅晶圆。

晶圆是一种由单晶硅制成,表面涂有氧化层的圆形硅片。

在制造CMOS芯片之前,晶圆需要经过一系列的清洗和检验工序,以确保表面光滑和纯净。

2.氧化层形成:接下来,在晶圆表面生长氧化层,通常使用化学气相沉积(CVD)或热氧化法。

氧化层主要用于作为绝缘层以隔离不同的电路元件。

3.掩膜制备:掩膜是用于在晶圆表面上形成电路图案的关键工序。

通常使用光刻技术,即在光敏胶上照射紫外光,并通过掩膜板模拟所需的电路图案。

然后将光刻胶暴露在化学试剂中,即可形成图案。

4.腐蚀形成:通过将晶圆表面暴露在氧化性或还原性化学溶液中,可以去除暴露在掩膜之外的氧化层。

根据所需的电路结构,可以选择干法腐蚀或湿法腐蚀。

这一步骤是为了形成晶体管的栅极结构。

5.掺杂:掺杂是向硅晶圆中引入所需的杂质,以改变硅的导电性能。

对于CMOS技术,需要在晶体管栅区域分别掺入P型和N型杂质,形成NMOS和PMOS晶体管。

通常使用离子注入技术来完成这一步骤。

6.金属沉积:在晶体管栅区域形成导线连接不同元件。

使用金属沉积或化学气相沉积技术,在晶圆的表面上沉积金属材料,如铝、铜等。

7.退火:在金属沉积后,通常需要进行一个退火过程。

退火是为了移除残留的应力和提高金属与硅的结合强度。

8.电路封装:最后,在晶圆表面涂覆一层绝缘材料,以保护芯片表面和元件,同时形成芯片的外壳和导线连接孔。

接着将晶圆切割成小块,每一块成为一枚芯片。

总结来说,CMOS的制造流程主要包括晶圆准备、氧化层形成、掩膜制备、腐蚀形成、掺杂、金属沉积、退火和电路封装等多个步骤。

每个步骤都必须精确控制和按照设计要求执行,以确保制造出符合规格和性能要求的CMOS芯片。

通过这些精密的工艺步骤,最终可以制造出高性能、低功耗的CMOS集成电路。

最新CMOS晶体管基础

沟道夹断

2、阈值电压(Threshold Voltage)

➢ 阈值电压是当沟道反型时所需的电压 (i.e. 将沟道从p型变 到n型的电压).

➢ 阈值电压可按下式计算:

4、MOS Capacitance

MOS电容:由器件本生的构造引起的。 Cgs: 栅极和源极的寄生电容。(平板电容) Cgd: 栅极和漏极的寄生电容。(平板电容) Cgb: 栅极和衬底的寄生电容。 Cdb: 漏极和衬底的寄生电容。(PN结电容) Csb: 源极和衬底的寄生电容。(PN结电容)

是影响最大的

interface)

VSB = 源到衬底的电势差(Source to bulk voltage)

对于一般工艺,Vtn= 0.83V(NMOS的阈值电压), Vtp= - 0.91V(PMOS的阈值电压),

阈值电压由工艺参数决定

3、MOSFET的 I-V 特性 (线性区Triode Region)

➢ c 是非理想因子,它是考虑了随着漏极电压增加耗尽层加厚而造成的.

MOSFET I-V Characteristics(伏安特性)曲线

VGS:栅极和源极的电压差。 VDS: 漏极和源极的电压差。 ID : 流过漏极和源极的电流。 Vth: 器件的阈值电压,当VGS增加到一定的值时,栅极下面的P型 半导体会发生反型,形成N型半导体的沟道。此时D和S之间可以有 电流流过,这个特定的电压值,称之为值电压。

电容值的计算(了解)

Capacitance values are the same as Accumulation

cmos晶体管的工艺流程

cmos晶体管的工艺流程咱就来唠唠CMOS晶体管的工艺流程这事儿。

CMOS晶体管可是现代集成电路里的超级明星呢。

这工艺流程啊,就像是一场奇妙的旅行。

一、硅片准备。

这就好比盖房子要先找块好地一样。

硅片可是晶体管的基础呀。

得先把硅片弄干净,那些脏东西可不能留在上面,就像咱们打扫房间,得一尘不染才行。

硅片的质量也很重要,要是硅片本身就不好,那后面的晶体管肯定也好不到哪儿去。

而且这个硅片的纯度得相当高,杂质太多的话,晶体管的性能就会大打折扣啦。

二、氧化。

这一步就像是给硅片穿上一层特殊的衣服。

通过氧化反应,在硅片表面形成一层二氧化硅薄膜。

这层薄膜可有用了,它能起到绝缘的作用呢。

就像给硅片打了个预防针,防止电流到处乱跑。

这氧化的过程得控制好条件,温度啊、气体的浓度啊,都得恰到好处,就像厨师做菜,调料放错了,味道就不对了。

三、光刻。

光刻这步可太有趣了,就像是在硅片上画画。

先在硅片上涂上一层光刻胶,这光刻胶就像画布一样。

然后呢,通过光照,把设计好的图案印在光刻胶上。

这就要求这个光啊得特别精准,就像神枪手一样,指哪儿打哪儿。

那些不需要的光刻胶就被去掉了,留下来的光刻胶下的硅片就准备接受下一步的改造啦。

四、掺杂。

掺杂就像是给硅片做基因改造。

往硅片里加入一些特殊的原子,比如磷或者硼。

这些原子进去之后呢,就会改变硅片的电学性质。

如果加的是磷原子,硅片就会变得更容易导电,就像给一条小路拓宽了一样;要是加的是硼原子呢,导电性能就会降低一些。

这掺杂的量也得控制好,少了没效果,多了就过犹不及啦。

五、蚀刻。

蚀刻就是把不需要的部分去掉。

就像雕刻家雕刻作品,把多余的石头去掉,留下想要的形状。

通过化学或者物理的方法,把那些没有被光刻胶保护的硅片部分蚀刻掉,这样就可以形成晶体管的各种结构啦,比如说源极、漏极还有栅极。

这蚀刻的过程也得小心翼翼的,一不小心就可能把有用的部分也给弄坏了。

六、金属化。

最后呢,就是金属化。

这就像是给晶体管搭建高速公路。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

ID2

VGSVTHN2

WhereKPnW L

➢ 当晶体管被夹断(pinchoff)时, 发生了什么? ➢ 增大 VDS 使耗尽区扩大到沟道中. ➢ 这导致ID 随 VDS 的增加而增大. 因此ID 可写为:

ID 2V G S V TH 21 N cV D S V D _ S Sat WhereKPnW L

gm

iDS vGS

Q

g mb

iDS vBS

Q

g ds

iDS vDS

Q

➢ 式中,Q表示在静态工作点的值.

Small-Signal Model of MOSFET in Saturation

NMOS管的阈值电压VTHN可表示为:

V q C o s N A i x2 F V S B 2 F V T 0 H2 N F V S B 2 F

其中

ms = 栅和衬底的接触电势(contact potential between the gate and the bulk)

F = 衬底的静电势(electrostatic potential of the substrate) Q`bo = 耗尽区的电荷(charge in the depletion region) Q`ss = Si/SiO2 接触面的电荷(Si/Sicharge at the Si/SiO2

2、阈值电压(Threshold Voltage)

➢ 阈值电压是当沟道反型时所需的电压 (i.e. 将沟道从p型变 到n型的电压).

➢ 阈值电压可按下式计算:

V TH N m 2 sF Q b C o o Q s x s 2 q C o sN i x A 2 F V S B2 F

① VGS〈Vthn时

下面的结构是N+PN+,耗尽层内是没有 自由移动的电荷的。D、S之间没有形成 一条电流通道,所以IDS=0。

②,VGS>=Vthn时

由于电场的作用,P—SUB中的少量电子移动到了沟 道的顶部。这样就形成了一条电子移动的通道,如 果VDS>0,就会形成源漏电流IDS。

沟道夹断

电容值的计算(了解)

Capacitance values are the same as Accumulation

Co

x

ox

TOX

and

CoxCo xWL

Capacitance is comprised of three components

C gb ox LT 2O LX D W C g dC g s oT xLO W D X CG W D CO G W SO

➢ 晶体管偏置在 VGS VTHN , 此时沟道已形成. ➢ 漏源电压 (VDS) 较小. ➢ 漏极电流可用下式表示:

IDVGSVTHN VDSV2D 2S

WhereKPnW L

MOSFET I-V 特性 (饱和区Saturation Region)

➢ 晶体管偏置在 VGS VTHN ,此时沟道已形成. ➢ 漏源电压较大 (i.e. VDS VGS – VTHN). ➢ 理想的漏极电流可表示为:

CMOS晶体管基础

MOSFET的三个重要几何参数

Lmin、 Wmin和 tox 由工艺确定 Lmin: MOS工艺的特征尺寸(feature size)

决定MOSFET的速度和功耗等众多特性 L和W由设计者选定 通常选取L= Lmin,由此,设计者只需选取W W影响MOSFET的速度,决定电路驱动能力和功耗

Area (poly)

54 18 11 aF/um2

Area (M1)

46 17 aF/um2

Area (M2)

49 aF/um2

Area (N+act.)

3599

aF/um2

Area (P+act.)

3415

aF/um2

Fringe (sub.) 249 261

aF/um

5、MOSFET的交流小信号模型(Analog Model for the MOSFET)

MOSFET的高频模拟模型. 电容已经在以前提到. ro 是输出电阻,gm是栅跨导. Current sources model the gain associated with biasing the base and the body of the MOSFET.

Small-Signal Model of MOSFET

以上各式中:

Eox: 氧化层的介电常数。

Tox: 氧化层的厚度。

Cox’ : 表示单位面积氧化层的电容值。

LD: 表示栅极和S、D重叠的宽度(由工艺精度决定)。

深亚微米CMOS IC工艺的寄生电容(数据)

Cap. N+Act.P+Act. Poly M1 M2 M3 Units

Area (sub.) 526 937 83 25 10 8 aF/um2

interface)

VSB = 源到衬底的电势差(Source to bulk voltage)

对于一般工艺,Vtn= 0.83V(NMOS的阈值电压), Vtp= - 0.91V(PMOS的阈值电压),

阈值电压由工艺参数决定

3、MOSFET的 I-V 特性 (线性区Triode Region)

➢ 输入信号的幅度和电源电压相比很小, 它在直流偏置工作 点附近的变化, 可近似认为工作在线性区间(如iD:SidsIDS ).

➢ MOS管的小信号模型可以直接从直流模型得出。大多数应 用中, MOS管被偏置在饱和区工作。下面仅给出饱和区的 小信号参数.

➢ 沟道导纳gm, gmb和gds, 分别称为栅跨导, 衬底跨导, 漏电导, 定义如下:

➢ c 是非理想因子,它是考虑了随着漏极电压增加耗尽层加厚而造成的.

MOSFET I-V Characteristics(伏安特性)曲线

VGS:栅极和源极的电压差。 VDS: 漏极和源极的电压差。 ID : 流过漏极和源极的电流。 Vth: 器件的阈值电压,当VGS增加到一定的值时,栅极下面的P型 半导体会发生反型,形成N型半导体的沟道。此时D和S之间可以有 电流流过,这个特定的电压值,称之为值电压。