CMOS晶体管基础共28页文档

MOS场效应晶体管基础[001]

![MOS场效应晶体管基础[001]](https://img.taocdn.com/s3/m/b5f9396ddd3383c4ba4cd25a.png)

Ii G

V gs

C gsT

S

CM g mVgs

Id

D

RL V d

输入电流: Ii j (Cgs TC M)Vgs

输出电流: Id gmVgs

电压增益:

电流增益:

Q'SD(m ax eN )axdT

1

xdT

4 s f

eNa

p

2

f

p

Vth ln

Na ni

msmE 2eg fp

C ox

ox tox

V T Pto ox x4sea V N th ln N a/(n i) Q 'ss m E 2 e g V th ln N a/(n i)

V DS

D n

ID

VSB 0 1V 3V

9V

V SB es 2efp

Ec

e fp

E Fi EF

Ev

00.64 1 .3 2.19 3.9

es (2ef pVS B )

E Fn

V GS

Ec

e

fp

E Fi EF

Ev

4、小信号等效电路

G

V ' gs

V gs

C gdT C gsT g mV 'gs

VGS VT

G

ID

S

W

VDS

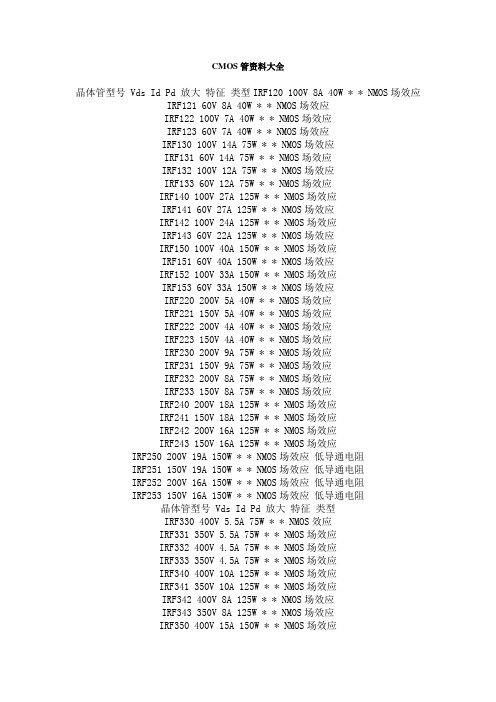

CMOS管资料大全

CMOS管资料大全

晶体管型号 Vds Id Pd 放大特征类型IRF120 100V 8A 40W * * NMOS场效应

IRF121 60V 8A 40W * * NMOS场效应

IRF122 100V 7A 40W * * NMOS场效应

IRF123 60V 7A 40W * * NMOS场效应

IRF130 100V 14A 75W * * NMOS场效应

IRF131 60V 14A 75W * * NMOS场效应

IRF132 100V 12A 75W * * NMOS场效应

IRF133 60V 12A 75W * * NMOS场效应

IRF140 100V 27A 125W * * NMOS场效应

IRF141 60V 27A 125W * * NMOS场效应

IRF142 100V 24A 125W * * NMOS场效应

IRF143 60V 22A 125W * * NMOS场效应

IRF150 100V 40A 150W * * NMOS场效应

IRF151 60V 40A 150W * * NMOS场效应

IRF152 100V 33A 150W * * NMOS场效应

IRF153 60V 33A 150W * * NMOS场效应

IRF220 200V 5A 40W * * NMOS场效应

IRF221 150V 5A 40W * * NMOS场效应

IRF222 200V 4A 40W * * NMOS场效应

IRF223 150V 4A 40W * * NMOS场效应

IRF230 200V 9A 75W * * NMOS场效应

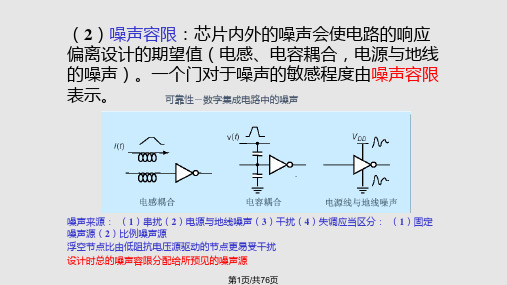

《CMOS集成电路基础》课件

静态功耗和动态功耗

静态功耗是指在CMOS集成电路处于静止状态时所消耗的功 耗,主要由晶体管漏电流引起。为了降低静态功耗,可以采 用降低电源电压或增加阈值电压的方法。

动态功耗是指在CMOS集成电路处于工作状态时所消耗的功 耗,主要由信号切换过程中的电流消耗引起。为了降低动态 功耗,可以采用降低工作频率或采用低功耗设计技术,如时 钟多路选择技术、动态逻辑技术等。

2

CMOS集成电路是数字集成电路的一种,其基本 单元是由n型和p型互补的晶体管组成的逻辑门电 路。

3

CMOS集成电路具有功耗低、集成度高、可靠性 高等优点,因此在计算机、通信、消费电子等领 域得到广泛应用。

CMOS集成电路的特点

低功耗

高速性能

CMOS集成电路的静态功耗极低,只有几 十微安,甚至几微安,因此非常适合用于 便携式电子设备和电池供电的应用。

故障检测与恢复

采用故障检测和恢复机制,及时发现和修复潜在的故障,提高系统的可靠性。

05

CMOS集成电路的发展趋 势和未来展望

发展趋势

技术进步

物联网和人工智能的推动

异构集成

可靠性提升

随着制程工艺的不断进步, CMOS集成电路的性能和集成 度将得到大幅提升,同时功耗 和成本也将进一步降低。

物联网和人工智能技术的快速 发展将推动CMOS集成电路在 智能传感器、边缘计算等领域 的应用,实现更高效的数据处 理和传输。

CMOS基础及基本工艺流程

CMOS基础及基本工艺流程

1.单晶硅衬底制备:首先需要准备单晶硅衬底,它是整个集成电路的

基础。这一步骤通常会涉及硅片切割和粗化,最终得到大小合适的硅衬底。

2.外延生长:在单晶硅衬底上外延生长蓝宝石或氮化硅等薄膜,这些

薄膜将作为隔离层使用,以电隔离各个晶体管。

3.门电极制备:在隔离层上制备门电极。通常使用化学气相沉积(CVD)或物理气相沉积(PVD)等技术,在薄膜上沉积一层金属,如铝或钨。

4.掺杂:利用掺杂技术向单晶硅衬底中注入掺杂物(例如硼或磷),

以改变硅的电子特性。

5.晶体管制备:利用光刻技术定义出晶体管的结构,通过曝光、阻挡、显影等步骤,制造出源极、栅极和漏极之间的结构。

6.金属互连:使用金属沉积和光刻技术,在晶体管上制造出金属互连层,将各个晶体管连接在一起。

7.电介质和过程模拟:制备电介质层,通常使用氧化硅或氧化铝等材料。过程模拟是为了检测制造过程中的缺陷和问题。

8.上下电极制备:制造上下电极用于晶体管之间的连接。

9.晶体管测试:测试晶体管的性能和可靠性。

10.封装和测试:最后,将制造好的芯片封装成集成电路,并进行最

终的测试。

以上是CMOS基本工艺流程的主要步骤,每个步骤都需精确控制和复杂操作,以确保芯片的性能和可靠性。CMOS技术由于其功耗低、稳定性好和集成度高等优点,被广泛应用于各种电子设备中,如微处理器、存储器、传感器等。

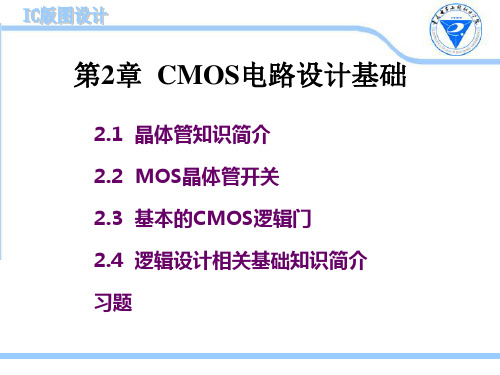

第2章 CMOS电路设计基础

先“或”后“与”最后“非”的逻辑关系的电 路为“或与非”(OAI OR-AND-INVERTER)电 路

2.4 逻辑设计相关基础知识简介

2.4.1 时钟信号 在数字电路中,一般都包含有时钟信号。时钟 信号有两个关键的参数:周期和频率,两者之间是 倒数的关系。周期T指的是一个全时钟周期所包含 的时间,单位为秒(s),频率的单位为赫兹(Hz)。

两输入或非门电路图及逻辑符号

2.3.4 CMOS传输门

通过将一个NMOS晶体管和一个PMOS晶体管 并联构成的,晶体管的源极和漏极作为信号线来使 用,栅极分别连接控制信号

传输门的电路图及逻辑符号图

传输门

当S=0时,NMOS晶体管截止,此时 =1, PMOS晶体管也截止,传输门断开,输入信号送 不到输出 当S=1时,NMOS晶体管导通,此时 =0, PMOS晶体管也导通,传输门导通,输入信号可 以传送到输出

– 或操作用PMOS的串联实现

– AB和CD的与操作可以分别用两个PMOS并联 完成 – 将两组开关串联就实现了AB和CD的或操作

用PMOS晶体管实现逻辑

F AB CD

用CMOS实现逻辑门

• 举例

总结

并联的NMOS和串联的PMOS都产生“或”操作

CMOS集成电路设计基础实用PPT课件

UG

Ui

Uo

Ui

CL

0

1

(a)

UG 0 1 1

(b)

Uo/(UG-UTH)

Uo 0 (理 想 0)

1

UG-UTH

1 (非 理 想 1)

0

1

Ui / (UG-UTH)

(c)

(a) 电路; (b) 等效开关; (c) 传输特性

第14页/共76页

(1) 当UG=“0”(接地)时, NMOS管截止(开关断开), 输出Uo=0。 (2) 当UG=“1”(UDD)时, NMOS管导通(开关合上), 此时视Ui的大小分两种情况: ① Ui<UG-UTH(UTH为NMOS管阈值电压),

Pcap(t)dt

T 0

Vouticap(t)dt

Vdd

CLVoutdVout

0

1 2

CL

•

Vd2d

第13页/共76页

MOS开关及CMOS传输门

单管MOS开关

NMOS单管开关

NMOS单管开关电路如图所示, CL为负载电容, UG为栅电压, 设“1”表示 UG=UDD, “0”表示UG=0(接地)。

即 UGDP=|Ui-Uo|<|UTHP|

第31页/共76页

3. CD段 当Ui进一步增大, 且满足 Uo+|UTHP|≤Ui≤Uo+UTHN N管和P管的电流相等, 根据电流方程:

CMOS工艺和器件完整版

耗尽区

p-衬底

B

NMOS管

NMOS管旳构造剖面示意图

衬底掺杂成为P型半导体,n+表达重度掺杂成为N型半导体(称扩散区)。在栅 与衬底之间电场作用下,栅下面旳衬底表面多数载流子空穴受排斥而降低,当空

穴基本被赶走时,在衬底表面形成耗尽层。当电场进一步增强时,不但空穴被赶 走,电子也被吸引到衬底表面,从而使P型半导体旳表面层变成电子占多数旳N型 层(反型层),使得源、漏、反型层形成一体旳N型区。而反型层也就是“沟道”。

p-well

substrate

n-well

CMOS工艺(双阱)环节示意 CMOS Process steps (2)

Pattern polysilicon before diffusion regions

poly p-well

gate oxide

poly n-well

CMOS工艺(双阱)环节示意 CMOS Process steps (3)

a CMOS Inverter:剖面图及版图(俯视图)

N-well process

N-well process with substrate contact

(a )

out VDD

in

PMOS衬底接电源、NMOS衬底接地

VDD

Vss

(b)

out

VDD

Vss

cmos工艺双极型晶体管

CMOS工艺双极型晶体管(Bipolar Junction Transistor,BJT)是一种用于电子设备的半导体器件。它由三个掺有不同材料的半导体区域(P 型、N型和P型)组成,形成了一个PNP结或一个NPN结。

在PNP型BJT中,P型区域为基极(Base),N型区域为发射极(Emitter),P型区域为集电极(Collector)。在NPN型BJT中,N型区域为基极,P型区域为发射极,N型区域为集电极。

当一个电压被施加到BJT的基极时,它将导致一个电流在基极和发射极之间流动,这个电流被称为基极电流(IB)。这个电流将激活BJT 中的载流子,使其在发射极和集电极之间流动。

BJT的放大效应是通过调节基极电流来实现的。当增加IB时,BJT的输出电流(IC)也会增加。因此,BJT可以被用作放大器或开关。

CMOS工艺指的是一种集成电路制造技术,其中使用的是互补金属-氧化物半导体(Complementary Metal-Oxide-Semiconductor,CMOS)技术。在CMOS工艺中,BJT是由P型和N型晶体管构成的,而不是单个P型或N型区域。这种结构被称为CMOS BJT。

CMOS BJT具有较低的功耗和噪声,并且在高速应用中具有较好的性能。它们通常用于模拟电路和RF电路中,如放大器、混频器、振荡

器等。

模拟cmos基础知识

模拟CMOS基础知识

一、什么是CMOS

1.1 CMOS的定义和作用

CMOS(Complementary Metal-Oxide-Semiconductor,互补金属-氧化物-半导体)

是一种集成电路的制造工艺,也是一种特定类型的晶体管。CMOS技术被广泛应用

于逻辑电路、模拟电路和数模混合电路中。

CMOS在数字电路方面具有优异的性能,相比于传统的TTL(Transistor-

Transistor Logic)和ECL(Emitter-Coupled Logic),CMOS电路功耗低、可靠

性高。它还具有良好的抗噪声特性和工作频率范围广的特点。

1.2 CMOS的组成结构

CMOS电路由nMOS(n型金属-氧化物-半导体)和pMOS(p型金属-氧化物-半导体)两种晶体管组成。

nMOS晶体管的工作原理是通过控制门电压,使得通道导电或截止,实现电流的控制。

pMOS晶体管则与nMOS相反,通过控制门电压控制通道的导电或截止。

这两种晶体管可以根据不同的逻辑功能进行灵活组合,从而实现复杂的电路功能。

二、CMOS工作原理

2.1 nMOS的工作原理

•当门端施加了高电压(高于阈值电压),nMOS的沟道导通,形成通路,电流通过;

•当门端施加了低电压(低于阈值电压),nMOS的沟道截止,电流停止。

2.2 pMOS的工作原理

•当门端施加了低电压(低于阈值电压),pMOS的沟道导通,形成通路,电流通过;

•当门端施加了高电压(高于阈值电压),pMOS的沟道截止,电流停止。

2.3 CMOS的工作原理

CMOS电路由nMOS和pMOS组成,其工作原理有以下几个重要特点:

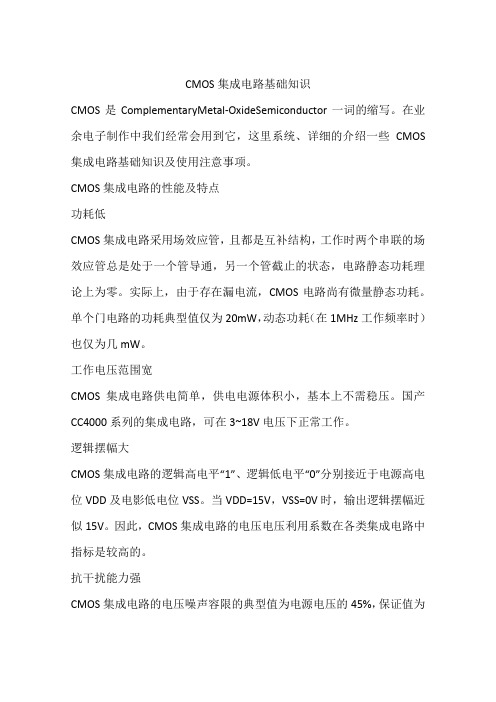

CMOS集成电路基础知识

CMOS集成电路基础知识

CMOS是ComplementaryMetal-OxideSemiconductor一词的缩写。在业余电子制作中我们经常会用到它,这里系统、详细的介绍一些CMOS 集成电路基础知识及使用注意事项。

CMOS集成电路的性能及特点

功耗低

CMOS集成电路采用场效应管,且都是互补结构,工作时两个串联的场效应管总是处于一个管导通,另一个管截止的状态,电路静态功耗理论上为零。实际上,由于存在漏电流,CMOS电路尚有微量静态功耗。单个门电路的功耗典型值仅为20mW,动态功耗(在1MHz工作频率时)也仅为几mW。

工作电压范围宽

CMOS集成电路供电简单,供电电源体积小,基本上不需稳压。国产CC4000系列的集成电路,可在3~18V电压下正常工作。

逻辑摆幅大

CMOS集成电路的逻辑高电平“1”、逻辑低电平“0”分别接近于电源高电位VDD及电影低电位VSS。当VDD=15V,VSS=0V时,输出逻辑摆幅近似15V。因此,CMOS集成电路的电压电压利用系数在各类集成电路中指标是较高的。

抗干扰能力强

CMOS集成电路的电压噪声容限的典型值为电源电压的45%,保证值为

电源电压的30%。随着电源电压的增加,噪声容限电压的绝对值将成比例增加。对于VDD=15V的供电电压(当VSS=0V时),电路将有7V 左右的噪声容限。

输入阻抗高

CMOS集成电路的输入端一般都是由保护二极管和串联电阻构成的保护网络,故比一般场效应管的输入电阻稍小,但在正常工作电压范围内,这些保护二极管均处于反向偏置状态,直流输入阻抗取决于这些二极管的泄露电流,通常情况下,等效输入阻抗高达103~1011Ω,因此CMOS集成电路几乎不消耗驱动电路的功率。

第08章-CMOS工艺双极型晶体管和二极管

来自百度文库

白雪飞 中国科学技术大学电子科学与技术系

提纲

• CMOS工艺双极型晶体管 • CMOS工艺二极管

2

CMOS工艺双极型晶体管

寄生双极型晶体管

• CMOS工艺是为了制造MOS电路而优化设计的 • CMOS工艺只能生成寄生双极型晶体管,其性能不及标准双极工艺或 BiCMOS工艺的双极型晶体管

• CMOS工艺寄生双极型晶体管在电路设计中也可以加以利用

4

衬底PNP晶体管

• 任何N阱CMOS工艺都可以制作衬底PNP晶体管

– 发射区:P型扩散 – 基 区:N阱 – 集电区:P型衬底

5

衬底PNP晶体管版图

(A) 采用叉指状发射区的版图 (B) 采用小接触孔大面积发射区的版图

6

横向PNP晶体管

N阱CMOS工艺横向PNP晶体管

可以获得较高的增益

7

浅阱晶体管

CMOS工艺浅阱NPN晶体管

8

CMOS工艺二极管

CMOS结型二极管

PSD/N阱二极管 可用于ESD保护结构

10

CMOS肖特基二极管

CMOS工艺制造的PSD保护环肖特基二极管

11

匹配PN结二极管

匹配PSD/N阱二极管

12

本章结束

CMOS晶体管基础

VSB = 源到衬底的电势差(Source to bulk voltage)

对于一般工艺,Vtn= 0.83V(NMOS的阈值电压), Vtp= - 0.91V(PMOS的阈值电压),

阈值电压由工艺参数决定

3、MOSFET的 I-V 特性 (线性区Triode Region)

MOSFET的温度特性主要来源于沟道中载流子的迁移率µ 和阈 值电压VT随温度的变化。

载流子的迁移率随温度变化的基本特征是: T µ

由于

所以,

W

gm tox L Vgs VT

T gm 阈值电压VT的绝对值同样是随温度的升高而减小:

T VT VT(T) (2 4) mV/°C VT的变化与衬底的杂质浓度Ni和氧化层的厚 度tox有关:

ID

2

VGS VTHN

2

Where

KP n

W L

➢ 当晶体管被夹断(pinchoff)时, 发生了什么?

➢ 增大 VDS 使耗尽区扩大到沟道中. ➢ 这导致ID 随 VDS 的增加而增大. 因此ID 可写为:

ID 2

VGS VTHN

2 1 c VDS VDS _ Sat

Where

二 CMOS晶体管基础

➢ 主要内容

1 、结构及工作原理 2、阈值电压 3、电流—电压方程(I-V特性) 4、MOS管寄生电容 5、小信号等效电路 6、gm、gds 7、MOSFET的数字模型 8、衬偏调制效应 9、MOSFET的温度特性 10、CMOS结构图

CMOS基础及基本工艺流程

MOSFET的分类 1.根据根据器件结构进行分类:

• N沟MOS晶体管(nMOST)的衬底为p型,源漏 区为重掺杂的n+区,沟道中的载流子为电子; • p沟MOS晶体管(pMOST)的衬底为n型,源漏区 为重掺杂的p+区,沟道中的载流子为空穴。 MOS器件在正常情况下,只有一种载流子(n沟 为电子,p沟为空穴)在工作,因此也称这种器件 为单极晶体管,这是与双极晶体管相对而言的, 双极晶体管在正常工作时与两种类型的载流子 (电子和空穴)都有关。

• 增加MOSFET增益的方法主要有: • ⑴ 增加Cox,即减小MOSFET的栅氧化层厚 度。 • ⑵ 提高器件的载流子迁移率。由于电子的 迁移率比空穴高,因此nMOST的增益比 pMOST高。 • ⑶增加沟道宽度W,缩小沟道长度L。

CMOS电路的闩锁效应

• 在阱和衬底之间 耦合的寄生PNP 和NPN三极管会 瞬间开启,它们 形成的正反馈会 引发大的电流 (这就是闩锁效 应) ,闩锁效应 会造成CMOS电路 的失效或永久损 坏。

2.根据工作模式进行分类:

四种不同类型的MOSFET

栅压 器件类型 常态 n沟 增强型 耗尽型 关 开 +Vg开启 -Vg关闭 p沟 -Vg开启 +Vg关闭

MOSFET直流特性

• 线性区 : 对于给定的Vgs(>Vth),线性区的Id随Vds线性 增加。 • 饱和区 : Ids不再随Vds增加而增加,它达到了饱和值。 • 击穿区 : 饱和区之后,若Vds进一步增加,晶体管将进入 击穿区。 在该区,Ids随Vds的增加而迅速增加,甚至引起漏衬pn结击穿,这是由漏端的高电场引起的。 • 截止区 : Vgs<Vth,器件未被开启

cmos基础知识

2012-3-15

16

MOS的I/V特性

此时D,S间体现为一个电阻,其阻值为:

Ron

=

∂VDS ∂I D

1

=

µ nCox

W L

(VGS

− VTH

)

(2.9)

2012-3-15

17

MOS的I/V特性

(2.9)式表示:

a:在满足 VDS << 2(VGS −VTH ) 的条件下,MOS管体

现出线性电阻的特性,其直流电阻与交流动态电阻相 等。 b:该线性电阻大小取决于VGS,即调节VGS,可调节 电阻的大小。因此我们常常把工作在这种区域的晶体 管称为“压控晶体管”。

或

2012-3-15

ID(x) [ = −WCox VGS −V (x) −VTH ]⋅ µn ⋅ (−dV(x) dx) [ = WCox VGS −V (x) −VTH ]⋅ µn ⋅(dV(x) dx)

13

MOS的I/V特性

边界条件 V (0) = 0,V (L) = VDS

两边积分可得

∫ ∫ [ ] L

MOSEFT

♦ MOSEFT的基本概念 ♦ MOSEFT的工作原理 ♦ MOSEFT的I/V特性

2012-3-15

1

MOSFET的基本概念

1. MOSFET的结构简图

图2.1 NMOSFET结构简图

cmos模拟集成电路设计基础

cmos模拟集成电路设计基础

CMOS模拟集成电路(Complementary Metal-Oxide-Semiconductor Analog Integrated Circuit)是一种基于CMOS技术的模拟电路集成化设计。以下是CMOS模拟集成电路设计的基础知识:

1.CMOS技术:CMOS是一种集成电路制造技术,其中包含

两种类型的晶体管:NMOS(N型金属氧化物半导体)和PMOS(P型金属氧化物半导体)。通过将NMOS和PMOS 晶体管结合,可以实现低功耗、高集成度和高性能的模拟集成电路设计。

2.基本元件:CMOS模拟集成电路设计中使用的基本元件包

括晶体管、电容器和电阻器。NMOS和PMOS晶体管用于实现放大和开关功能,电容器用于存储电荷和控制频率响应,电阻器用于调整电路的工作条件。

3.偏置电路:CMOS模拟集成电路中的偏置电路用于提供恒

定和稳定的电流或电压。它包括电流镜(Current Mirror)电路和电压源(Voltage Reference)电路。这些电路通过调整电流和电压的偏置,使电路在不同工作条件下具有可靠的性能。

4.放大电路:CMOS模拟集成电路中的放大电路用于增强输

入信号的幅度。放大电路通常由差分放大器(Differential Amplifier)和级联的共尺寸(Common-Source)放大器组

成。放大电路的设计需要考虑输入电阻、增益、带宽和稳定性等因素。

5.反馈电路:CMOS模拟集成电路中的反馈电路用于控制电

路的增益和稳定性。反馈电路通过将一部分输出信号反馈到输入端,调整输入和输出之间的关系,实现精确的控制和稳定性。

最新CMOS晶体管基础

VSB = 源到衬底的电势差(Source to bulk voltage)

对于一般工艺,Vtn= 0.83V(NMOS的阈值电压), Vtp= - 0.91V(PMOS的阈值电压),

阈值电压由工艺参数决定

3、MOSFET的 I-V 特性 (线性区Triode Region)

由于电场的作用,P—SUB中的少量电子移动到了沟 道的顶部。这样就形成了一条电子移动的通道,如 果VDS>0,就会形成源漏电流IDS。

wk.baidu.com

沟道夹断

2、阈值电压(Threshold Voltage)

➢ 阈值电压是当沟道反型时所需的电压 (i.e. 将沟道从p型变 到n型的电压).

➢ 阈值电压可按下式计算:

➢ 晶体管偏置在 VGS VTHN , 此时沟道已形成. ➢ 漏源电压 (VDS) 较小. ➢ 漏极电流可用下式表示:

IDVGSVTHN VDSV2D 2S

WhereKPnW L

MOSFET I-V 特性 (饱和区Saturation Region)

➢ 晶体管偏置在 VGS VTHN ,此时沟道已形成. ➢ 漏源电压较大 (i.e. VDS VGS – VTHN). ➢ 理想的漏极电流可表示为:

以上各式中:

Eox: 氧化层的介电常数。

Tox: 氧化层的厚度。

Cox’ : 表示单位面积氧化层的电容值。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

阈值电压(Threshold voltage): V TH N m 2 sF Q b C o o Q s x s 2 q C o sN i x A 2 F V S B2 F

对于一般工艺,Vtn=0.83V(NMOS的阈值电压), Vtp=-0.91V(PMOS的阈值电压), 阈值电压由工艺参数决定

1、工作原理

3D结构图

Polysilicon

Aluminum

L

W

Gate

Source

Drain

G

S

Poly D

Oxide

n+

p-substrate

Leff LDrawn

n+ LD

n+

n+

W

W

线宽(Linewidth), L

特征尺寸(Feature Size)指什么?

MOSFET的三个重要几何参数

4、MOS Capacitance

MOS电容:由器件本生的构造引起的。 Cgs: 栅极和源极的寄生电容。(平板电容) Cgd: 栅极和漏极的寄生电容。(平板电容) Cgb: 栅极和衬底的寄生电容。 Cdb: 漏极和衬底的寄生电容。(PN结电容) Csb: 源极和衬底的寄生电容。(PN结电容)

是影响最大的

VSB = 源到衬底的电势差(Source to bulk voltage)

对于一般工艺,Vtn= 0.83V(NMOS的阈值电压), Vtp= - 0.91V(PMOS的阈值电压),

阈值电压由工艺参数决定

3、MOSFET的 I-V 特性 (线性区Triode Region)

➢ 晶体管偏置在 VGS VTHN , 此时沟道已形成. ➢ 漏源电压 (VDS) 较小. ➢ 漏极电流可用下式表示:

以上各式中:

Eox: 氧化层的介电常数。

Tox: 氧化层的厚度。

Cox’ : 表示单位面积氧化层的电容值。

LD: 表示栅极和S、D重叠的宽度(由工艺精度决定)。

深亚微米CMOS IC工艺的寄生电容(数据)

Cap. N+Act.P+Act. Poly M1 M2 M3 Units

Area (sub.) 526 937 83 25 10 8 aF/um2

➢ c 是非理想因子,它是考虑了随着漏极电压增加耗尽层加厚而造成的.

MOSFET I-V Characteristics(伏安特性)曲线

VGS:栅极和源极的电压差。 VDS: 漏极和源极的电压差。 ID : 流过漏极和源极的电流。 Vth: 器件的阈值电压,当VGS增加到一定的值时,栅极下面的P型 半导体会发生反型,形成N型半导体的沟道。此时D和S之间可以有 电流流过,这个特定的电压值,称之为值电压。

电容值的计算(了解)

Capacitance values are the same as Accumulation

Co

x

ox

TOX

and

CoxCo xWL

Capacitance is comprised of three components

C gb ox LT 2O LX D W C g dC g s oT xLO W D X CG W D CO G W SO

截止区:

ID=0, VGS< Vth

线性区 (Linear):

IDVGSVTHN VDSV2D 2S

,VDS〈 VGS-Vth

饱和区 (Saturation):

ID 2V G S V TH 21 N cV D S V D _ S Sat WhereKPnW L

VDS >= VGS-Vth

Area (poly)

54 18 11 aF/um2

Area (M1)

46 17 aF/um2

Area (M2)

49 aF/um2

Area (N+act.)

3599

aF/um2

Area (P+act.)

3415

aF/um2

Fringe (sub.) 249 261

aF/Fra Baidu bibliotekm

5、MOSFET的交流小信号模型(Analog Model for the MOSFET)

F = 衬底的静电势(electrostatic potential of the substrate) Q`bo = 耗尽区的电荷(charge in the depletion region) Q`ss = Si/SiO2 接触面的电荷(Si/Sicharge at the Si/SiO2

interface)

Lmin、 Wmin和 tox 由工艺确定 Lmin: MOS工艺的特征尺寸(feature size)

决定MOSFET的速度和功耗等众多特性 L和W由设计者选定 通常选取L= Lmin,由此,设计者只需选取W W影响MOSFET的速度,决定电路驱动能力和功耗

① VGS〈Vthn时

下面的结构是N+PN+,耗尽层内是没有 自由移动的电荷的。D、S之间没有形成 一条电流通道,所以IDS=0。

VGSVTHN2

WhereKPnW L

➢ 当晶体管被夹断(pinchoff)时, 发生了什么? ➢ 增大 VDS 使耗尽区扩大到沟道中. ➢ 这导致ID 随 VDS 的增加而增大. 因此ID 可写为:

ID 2V G S V TH 21 N cV D S V D _ S Sat WhereKPnW L

➢ 阈值电压可按下式计算:

V TH N m 2 sF Q b C o o Q s x s 2 q C o sN i x A 2 F V S B2 F

其中

ms = 栅和衬底的接触电势(contact potential between the gate and the bulk)

②,VGS>=Vthn时

由于电场的作用,P—SUB中的少量电子移动到了沟 道的顶部。这样就形成了一条电子移动的通道,如 果VDS>0,就会形成源漏电流IDS。

沟道夹断

2、阈值电压(Threshold Voltage)

➢ 阈值电压是当沟道反型时所需的电压 (i.e. 将沟道从p型变 到n型的电压).

IDVGSVTHN VDSV2D 2S

WhereKPnW L

MOSFET I-V 特性 (饱和区Saturation Region)

➢ 晶体管偏置在 VGS VTHN ,此时沟道已形成. ➢ 漏源电压较大 (i.e. VDS VGS – VTHN). ➢ 理想的漏极电流可表示为:

ID2