CMOS晶体管基础教学讲义

《CMOS集成电路基础》课件

NMOS

当输入为0时,导通;当输入为1时,截止。

输出

输出反相的输入信号。

CMOS电路组成:CMOS传输门

1 输入端

接收多个输入信号。

3 PMOS

通过开关和截止的方式传递输入信号。

2 NMOS

通过开关和导通的方式传递输入信号。

4 输出端

输出根据输入信号进行逻辑运算的结果。

晶圆切割

将完成的硅片切割成晶圆,以便后续封 装和测试。

CMOS电路组成:MOS管

N沟道MOS管(NMOS)

由N型沟道和P型沟道构成,可以实现电流的传输和 放大。

P沟道MOS管(PMOS)

由P型沟道和N型沟道构成,用于控制电流的开关。

CMOS电路组成:CMOS反相器

输入

接收输入信号(0或1)。

PMOS

CMOS电路组成:CMOS与门

1

输入A

接收输入信号A。

输入B

2

接收输入信号B。

3

NMOS

当输入A为1且输入B为1时,导通。

PMOS

4

Байду номын сангаас

当输入A为0且输入B为0时,导通。

CMOS电路组成:CMOS或门

1

输入A

接收输入信号A。

输入B

2

接收输入信号B。

3

NMOS

当输入A为1且输入B为1时,截止。

PMOS

CMOS的基本工艺流程

1

清洗和蚀刻

2

对硅片进行清洗和蚀刻,去除杂质和氧

化物,并形成特定的表面。

3

沉积

4

在硅片上沉积各种材料,如金属、氧化

物和多晶硅等,用于构建电路的不同部

《晶体管》 讲义

《晶体管》讲义一、什么是晶体管在现代电子技术的领域中,晶体管是一种至关重要的元件。

简单来说,晶体管是一种能够控制电流流动的半导体器件。

它就像是电子世界中的一个“开关”,可以根据输入的信号来决定电流是否通过,以及通过的电流大小。

晶体管的出现彻底改变了电子学的面貌。

在晶体管发明之前,电子设备主要依赖体积庞大、功耗高且容易出故障的真空管。

而晶体管的出现,使得电子设备变得更小、更节能、更可靠。

二、晶体管的工作原理要理解晶体管的工作原理,我们首先需要了解一些半导体的基础知识。

半导体是一种导电性能介于导体和绝缘体之间的材料,常见的半导体材料有硅和锗。

晶体管主要有两种类型:双极型晶体管(BJT)和场效应晶体管(FET)。

双极型晶体管由发射极、基极和集电极三个极组成。

当在基极和发射极之间施加一个较小的电流时,就可以控制从集电极到发射极的较大电流的流动。

这是因为基极电流的变化会引起载流子在半导体中的分布发生改变,从而影响集电极和发射极之间的电流。

场效应晶体管则是通过在栅极上施加电压来控制源极和漏极之间的电流。

根据栅极结构的不同,场效应晶体管又分为结型场效应管(JFET)和金属氧化物半导体场效应管(MOSFET)。

以 MOSFET 为例,当在栅极上施加正电压时,会在半导体表面形成一个导电沟道,从而允许电流从源极流向漏极。

而当栅极电压为零时,导电沟道消失,电流无法通过。

三、晶体管的分类除了上述提到的双极型晶体管和场效应晶体管这两大类,晶体管还有很多细分的类型。

比如,按照材料不同,可以分为硅晶体管、锗晶体管等;按照封装形式不同,可以分为直插式晶体管、贴片式晶体管等;按照功率大小不同,可以分为小功率晶体管、中功率晶体管和大功率晶体管等。

不同类型的晶体管在性能、特点和应用场景上都有所不同。

小功率晶体管通常用于低功率的电子电路中,如放大器、逻辑电路等;中功率晶体管可用于一些中等功率的电路,如音频放大器;大功率晶体管则常用于电源电路、电机驱动等需要较大电流和功率的场合。

《CMOS集成电路基础》课件

智能传感器和可 穿戴设备的普及

随着智能传感器和可穿戴设 备的普及,CMOS集成电路 将在这些领域发挥重要作用 ,实现更高效、更低功耗的 数据采集和处理。

神经网络和类脑 计算的发展

CMOS集成电路将在神经网 络和类脑计算领域发挥重要 作用,推动人工智能技术的 进一步发展。

系统级芯片的广 泛应用

随着系统级芯片的广泛应用 ,CMOS集成电路将与不同 芯片和模块进行集成,实现 更高效、更低功耗的系

晶圆制备

将高纯度硅材料加工成晶圆, 作为集成电路的基底。

薄膜沉积

在晶圆表面沉积所需厚度的薄 膜,形成各种有源和无源器件

。

光刻与刻蚀

通过光刻技术将设计好的电路 版图转移到晶圆表面,然后进

行刻蚀,形成电路图形。

掺杂与退火

通过掺杂工艺在晶圆中引入不 同元素,形成PN结和导电通

道,并进行退火处理。

03

每个逻辑门电路由NMOS和PMOS晶体管组成,形成反相器或与门、或门等基 本逻辑门。

工作原理

01

CMOS集成电路的工作原理基于 NMOS和PMOS晶体管的开关特 性。当输入信号发生变化时, NMOS和PMOS晶体管会交替导

02 通和截止,从而实现逻辑功能。

CMOS电路的电压摆幅较小,因 此功耗较低。此外,CMOS电路 还具有噪声容限高、抗干扰能力 强等优点。

我们应该如何学习和掌握CMOS集成电路技术

理论与实践结合

在学习过程中,应注重理论与实践相结合 ,通过实验和项目实践加深对理论知识的

理解。

持续学习与更新知识

随着技术的不断进步,应保持持续学习的 态度,关注新技术、新工艺的发展,不断 更新自己的知识储备。

培养问题解决能力

集成电路原理课件-cmos

1

微电子学

• 微电子技术是电子计算机和通信的核心技术 • 微电子技术的核心是集成电路(Integrated Circuit, IC) 技术 • 微电子学是电子学的一门分支,主要研究电子或离 子在固体材料中的运动规律及其应用 • 微电子学是以实现电路和系统的集成为目的,研究 如何利用半导体的微观特性以及一些特殊工艺,在 一块半导体芯片上制作大量的器件,从而在一个微 小面积中制造出复杂的电子系统。

I

D

dx

V 0

WC

ox

n [VGS V ( x) VTH ]dV

I/V特性的推导(3)

W 1 2 I D = nCox [(VGS - VTH )VDS - VDS ] (2.8) L 2 W VGS - VTH 称为过驱动电压; 称为宽长比 L 三极管区(线性区)

每条曲线在VDS=VGS-VTH时取最 大值,且大小为:

CGD CGS

WLCOX WCOv 2

CGB可以忽略不计

CSB = CDB =

WE源极Cj (1 VSB /B ) WE漏极Cj (1 VDB /B )

mj mj

源极周长 C jsw (1 VSB /B )

m jsw

漏极周长 C jsw (1 VDB/B )

MOS器件电容

栅源、栅漏、栅衬电容与VGS关系

1) VGS < VTH截止区

CGD CGS WCOv

CGB W 2 L2 COX q si N sub / 4 F WLCOX Cd = 其中Cd=WL q si N sub / 4 F WLCOX Cd WLCOX WL q si N sub / 4 F

MOS晶体管PPT演示文稿

图2.1.1 NMOS晶体管

•10

图2.1.2 NMOS管截面图

•11

图2.1.3 实际的NMOS管衬底引线

•12

(a)增强型

(b)耗尽型

图2.1.4 MOS管在电路中的符号

耗尽型MOS管与增强型MOS管不同之处在于,耗尽型MOS管

在vGS=0时,导电沟道已经存在,它是通过加工过程中的离子注

图2.2.1 导电沟道没有形成

•15

图2.2.2 栅-源电压vGS控制导电沟道宽窄

•16

(a) vDSvGSVT

•17

(b) vDSvGSVT

•18

(c) vDSvGSVT

图2.2.3 NMOS管的工作状态示意图

•19

2.3 MOS晶体管的电流电压关系

1、非饱和区(线性电阻区)

IDK W L vG SV TvD S1 2vD2S (2.3.8)

[3] 陈中建主译. CMOS电路设计、布局与仿真.北京:机械工 业出版社,2006.

[4](美)Wayne Wolf. Modern VLSI Design System on Silicon. 北京:科学出版社,2002.

[5] 朱正涌. 半导体集成电路. 北京:清华大学出版社,2001. [6] 王志功,沈永朝.《集成电路设计基础》电子工业出版

•8

2.1 MOS晶体管结构

根据导电沟道的不同,MOS晶体管可分为P沟道MOS晶体 管(简称为PMOS管)和N沟道MOS晶体管(简称为NMOS管), 而根据在没有外加电压条件下导电沟道形成与否又可分为耗尽型 MOS管和增强型MOS管。

图2.1.1所示的是一只增强型NMOS管,它是在适度掺杂的 P型衬底上制作两个掺杂浓度较高的N型区,分别作为漏区和源 区,在漏区和源区之的区域上面制作一层绝缘层(一般是二氧 化硅物质),绝缘层上面沉积一层多晶硅作为栅区。我们把源区 和漏区两个掺杂区之间的距离称为沟道长度L,而垂直于沟道长 度的有效源漏区尺寸称为沟道宽度W。

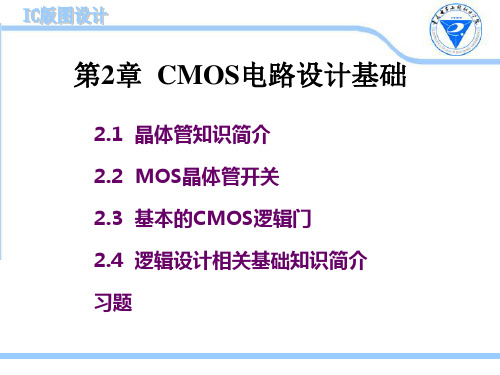

第2章 CMOS电路设计基础

2.2 MOS晶体管开关

CMOS简介 MOS晶体管(金属-氧化物-半导体场效应管)是构 成CMOS电路的基本元件,可分为NMOS和 PMOS晶体管两种。 NMOS晶体管和PMOS晶体管组合在一起,两者 互为补充,构成互补MOS(CMOS)。其实CMOS 是芯片的一种制作工艺。

2.2 MOS晶体管开关

两输入或非门电路图及逻辑符号

2.3.4 CMOS传输门

通过将一个NMOS晶体管和一个PMOS晶体管 并联构成的,晶体管的源极和漏极作为信号线来使 用,栅极分别连接控制信号

传输门的电路图及逻辑符号图

传输门

当S=0时,NMOS晶体管截止,此时 =1, PMOS晶体管也截止,传输门断开,输入信号送 不到输出 当S=1时,NMOS晶体管导通,此时 =0, PMOS晶体管也导通,传输门导通,输入信号可 以传送到输出

与非门的尺寸标注

2.3.3 CMOS或非门

当所给条件中的一个或一个以上被满足时,结 果就不能实现,这种逻辑关系就是“或非”关系。 或非门(NOR)就是实现“或非”逻辑关系的门电路

两输入或非门的真值表

IN1 0 0 1 1 IN2 0 1 0 1 OUT 1 0 0 0

或非门 当两个输入同时为“0”的时候,输出为“1”,这 可以通过将两个PMOS晶体管串联来实现 当有一个输入为“1”的时候,输出为“0”,这可 以通过将两个NMOS晶体管并联来实现

晶体管和电子管比较

④晶体管结实可靠,比电子管可靠100倍,耐冲 击、耐振动,这都是电子管所无法比拟的。

⑤另外,晶体管的体积只有电子管的十分之一到 百分之一,放热很少,可用于设计小型、复杂、 可靠的电路。

2. 晶体管的分类

按半导体材料:硅、锗 按极性:NPN, PNP 按结构及制造工艺:扩散型晶体管、合金型晶体 管和平面型晶体管 双极型晶体管,场效应管

最新最全《晶体管》教案(完整版)-2024鲜版

随着新材料、新工艺的不断涌现,未来晶体管将朝着更高性能、更低功耗、更 小尺寸的方向发展。同时,柔性电子器件、可穿戴设备等新兴领域的发展也将 为晶体管带来新的应用场景。

挑战

随着晶体管尺寸的缩小,量子效应、热效应等问题将逐渐凸显,对晶体管的性 能产生负面影响。此外,新型材料的可控性、稳定性等问题也需要进一步研究 和解决。

体管。

2024/3/28

20

结构创新设计思路探讨

异质结结构

通过不同材料之间的能带 工程,实现高性能的晶体 管设计。

2024/3/28

垂直结构

通过垂直堆叠多个晶体管, 实现高集成度、高性能的 电子器件。

光电器件集成

将光电器件与晶体管进行 集成,实现光电一体化设 计,提高器件性能。

21

未来发展趋势预测与挑战

特点

不同类型的晶体管具有不同的特点,如二极管具 有单向导电性,三极管具有放大和开关功能,场 效应管具有高输入阻抗和低噪声等优点。

2024/3/28

5

工作原理及主要参数

工作原理

晶体管的工作原理基于半导体的导电特性,通过控制输入电流或电压来控制输出电流或电压, 实现放大、开关等功能。

主要参数

晶体管的主要参数包括电流放大系数、截止频率、击穿电压、最大功耗等,这些参数决定了晶 体管的性能和使用范围。

竞争格局

当前,全球晶体管市场呈现多元化竞争格局,主要厂商包括英特尔、高通、AMD、 台积电等。这些厂商在技术研发、生产制造、市场营销等方面具有较强实力,形成 了较为稳定的市场格局。

发展前景

随着人工智能、5G通信、物联网等新兴技术的快速发展,晶体管作为电子设备的核 心元件之一,其市场前景广阔。未来,晶体管将不断向高性能、高集成度、低功耗 等方向发展,同时在新兴应用领域中将发挥更加重要的作用。

CMOS 讲义4 CMOS设计基础

4.2.2 CMOS反向器的功耗

动态功耗(瞬态功耗)PD

一周内CL充放电使管子产生的平均功耗

T1 T2 1 PD1 (iDP UDSP)dt (iDN UDSN )dt Te T1 0

式中Te为输入信号周期。

U UOL CL OH P ( U U ) d ( U U ) U dU D1 O DD O DD O O U U Te OH OL

(N管的导电因子) (P管的导电因子)

4.2.3 CMOS反向器的的直流传输特性 反向器的

分段讨论:

CD段 由于IDN=IDP,可以求得反相器的阈值电压UiT为:

U iT U THN

ቤተ መጻሕፍቲ ባይዱ

U DD U THN U THP

N 1 P

4.2.3 CMOS反向器的的直流传输特性 反向器的

I DM

nCox W

2

(U DD U THN ) L N

2

pCox W

2

2 (U DD U THP) L P

反相器总的动态功耗:

PD PD1 PD 2

4.2.3 CMOS反向器的的直流传输特性 反向器的

随着Ui(0~Udd)由小变大,反相器的工作状态可分为5 个阶段来描述,如图所示:

4.2.3 CMOS反向器的的直流传输特性 反向器的

CMOS反相器直流工作特性总结

区域

条件 AB 0 U i U THN

BC CD DE EF

PMOS NMOS

输出电压

线性 截止 U o U DD

U THN U i U DD

2

二CMOS晶体管基础PPT教案

➢ 沟导道, 定导义纳如g下m,:gmb和gds, 分别称为栅跨导, 衬底跨导, 漏电

➢ 式中g,m Q表viDG示SS 在Q 静态g工mb 作 点viDB的SS 值Q .

g ds

iDS vDS

Q

第19页/共33页

in Saturation

NMOS管的阈值电压VTHN可表示为:

饱VTH和N 区mNs M2 FO QSboC管oxQ的ss 漏2qC极osxi N电A 流2 FIDSVS可B 表2示F 为VTHN:0 2 F VSB 2 F

Cgs: 栅极和源极的寄生电容。(平板电容

)

是影响最大的

Cgd: 栅极和漏极的寄生电容。(平板电容 )

Cgb: 栅极和衬底的寄生电容。

Cdb: 漏极和衬底的第寄1生5页电/共容33。页(PN结电容

电容值的计算(了解 )

Capacitance values are the same as Accumulation

MOSFET的温度特性主要来源于沟道中载流子 的迁移率µ 和阈值电压VT随温度的变化。

载流子的迁移率随温度变化的基本特征是:

T由于gµm tox

W L

Vgs

VT

所以,

T gm 阈值电压VT的绝对值同样是随温度的升高而减

小:

T VT VT(T) (2 4) mV/°C VT的变化与衬底的杂质浓度Ni和氧化层的厚

度tox有关:

(Ni , tox) V第T2(T4页)/共33页

9、CMOS的剖面结构图

第25页/共33页

第26页/共33页

49

aF/um2

Area (N+act.)

3599

aF/um2

Area (P+act.)

第二章 CMOS器件基础

MOS管的电流方程

2. Cox单位面积栅电容 Cox=ɛ0ɛsio2/tox ɛ0:真空介电常数,8.854x10-12 F/m Ɛsio2:栅氧化层(SiO2)的相对介电常数 3.9 tox:栅氧化层厚度 可以计算:当tox=50A(1A=0.1nm)时, Cox=(8.854x10-12x3.9x10-6)/5x10-3 =6.9fF/μm2 (1fF=10-15F) (学会如何计算,注意单位统一)

同一衬底上的NMOS和PMOS器件

MOS管所有pn结 必须反偏: *N-SUB必须接最 高电位VDD! *P-SUB必须接最 低电位VSS! *阱中MOSFET衬 底常接源极S

寄生二极管

MOS管符号

G

G

(a)

四端器件,一般在模拟电 路设计中采用。

(b)

省去了衬底,默认为 衬底与源 管。只区分管子类 型。常用于数字电 路

在集成电路设计中,在同一硅片衬底上做许多管子,为

二级效应1:体效应

保证它们正常工作,一般N管衬底要全部接最低点位,P 管衬底接最高点位,因此,有些管子源极与衬底之间存在 电位差。 为了保证沟道与衬底之间的隔离,PN结必须反偏,图中 T2管的Vbs<0 当Vbs<0时,导致阈值电压Vth增大,沟道变窄,沟道电 阻变大,ID减小,称此效应为体效应,或者背栅效应, 衬底调制效应。

L=4µ

L=6µ

∂ID/∂VDS∝λ/L∝1/L2

二级效应3:亚阈值导电性

当VGSVTH时和略小于VTH ,“弱”反型层依然存在, 与VGS呈现指数关系。当VDS大于200mV时,

这里ζ>1,VT=kT/q

MOS管亚阈值电流ID一般为几十~几百 nA, 常用于低功耗放大器、带隙基准设计。

cmos基础知识

VDS

= (VGS −VTH )

点上,且相应各峰值电流为:

I D,max

=

1 2

µnCox

W L

(VGS

− VTH )2

(2.7)

VGS-VTH为过驱动(overdrive)电压,只有过驱动 电压可以形成反型层电荷。

VDS < VGS − VTH 时,器件工作在“三极管区”.

2012-3-15

15

MOS的I/V特性

2012-3-15

( ) (2.2)

量纲=

⎜⎛C ⎝

m3

⎟⎞ ⎠

*

m

s

=

A m2

10

MOS的I/V特性

(2) 考虑一个源漏都接地的NFET,反型层中的电荷密度为多少?

若假设VGS=VTH时开始反型,那么由栅氧化层电容引起的反 型电荷密度正比于VGS-VTH。当VGS>VTH时,栅电荷必定会被 沟道电荷所镜像,从而产生一个均匀的沟道电荷密度为:

2.2.3 MOS器件深Triode区时的导通电阻

MOS器件作为模拟开关,或小值线性电阻运用时,

都会工作于深Triode区。此时VGS较大,MOS管的

VDS很小,若满足:

VDS << 2(VGS −VTH )

此时(2.6)简化为:

ID≈µnCoxW L(VGS

−VTH

)VDS

(2.8)

(2.8)表明 ID ~ VDS 为直线关系,如图(2.12)所示.

(2.4)

2012-3-15

12

MOS的I/V特性

(3) 电荷漂移速度

υ = µE

(2.5)

υ :漂移速度 drift speed

《CMOS集成电路闩锁效应》第二章课件

对于NPN:Icn=αnIen ----------------------------------------- (式5)

由电源提供的总电流如下式:

Iep

I=Icp + Icn

I=αpIep + αnIen

I=αp (I -IP) + αn(I - In) ----------------------------------------- (式6)

VSS p+ PW

Rp

输出 n+

VDD

VSS

控制信号 输出

VDD

输出

p+

p+

p+

n+

Rn P-sub

Rp NW

(a)

Rn PNP

NPN

输出

VSS (b)

《CMOS集成电路闩锁效应》讲义

VSS

控制信号 输出

p+

n+

强,形成很强电场,使得集电区的电子和基区的空穴很 难通过集电结,扩散到集电结边界的电子会被强电场加 速进入集电区,最后被集电区收集,形成集电极漂移电 子流ICN。基区中少数载流子电子和集电区中少数载流

N+

IEN

IE

E IEP

PW IBN

NW

ICN

Ic

ICBO

C

子空穴在反向电场的作用下形成反向漂移电流,这部分

《CMOS集成电路闩锁效应》讲义

工作模式 正向有源

饱和 倒置 截止

发射结 正偏 正偏 反偏 反偏

集电结 反偏 正偏 正偏 反偏

3

双极型晶体管电路连接方式

根据双极型晶体管的电极被输入和输出共用的情况,可以把双极型晶体管分为三种电路连接 方式:第一种是共基极接法(基极作为公共电极);第二种是共发射极接法(发射极作为公 共电极);第三种是共集电极接法(集电极作为公共电极)。

精品课程IC原理CMOS基本逻辑单元课件

contents

目录

• IC原理简介 • CMOS逻辑单元基础 • CMOS基本逻辑单元详解 • CMOS逻辑单元的应用与实例 • CMOS逻辑单元的优化与挑战 • 总结与展望

01

IC原理简介

IC定义与分类

总结词

集成电路是将多个电子元件集成在一块衬底上,完成 一定的电路或系统功能的微型电子部件。根据使用功 能,IC可分为模拟集成电路和数字集成电路两大类。

04

CMOS逻辑单元的应用与实例

组合逻辑电路设计

总结词

组合逻辑电路是CMOS逻辑单元的重要应用之一,它根据输 入信号的组合实现特定的逻辑功能。

详细描述

组合逻辑电路设计主要涉及逻辑函数的实现,通过使用 CMOS门电路,如AND、OR、NOT等,将输入信号组合在 一起以产生输出信号。组合逻辑电路广泛应用于计算机、通 信、控制等领域。

IC发展历程

• 总结词:IC的发展经历了从晶体管、集成电路、超大规模集成电路到特大规模 集成电路和甚大规模集成电路四个阶段。

IC基本结构与工作原理

总结词

IC的基本结构包括输入端、输出端和中间 部分。IC的工作原理是通过输入端接收信 号,经过中间部分处理后,由输出端输 出结果。

VS

详细描述

IC的基本结构包括输入端、输出端和中间 部分。输入端负责接收外部信号,输出端 负责输出处理结果,中间部分则是对输入 信号进行处理的电路。IC的工作原理是通 过输入端接收信号,经过中间部分的处理 后,由输出端输出结果。中间部分的处理 电路是IC的核心部分,它可以根据需要进 行不同的设计和组合,实现各种不同的功 能和处理效果。IC的工作原理涉及到许多 复杂的电路和物理效应,需要深入研究和 理解才能更好地应用和发展。

《CMOS集成电路闩锁效应》第二章课件

n+

PW Rp

NW DNW

控制信号 输出

VDD

p+ PW

(a)

p+

p+

Rn P-sub

n+ NW

Rn

输出

PNP

Rp

NPN

VSS (b)

13

《CMOS集成电路闩锁效应》讲义

CMOS寄生SCR

1. N-diode与PMOS之间形成寄生PNPN 结构。

2. NMOS与P-diode之间形成寄生PNPN 结构。

VBE

B IB

VCB

电流取决于少数载流子浓度,称为反向饱和电流ICBO。

通常ICBO非常小,它并不会对电流的放大作用有贡献。

VSS

6

《CMOS集成电路闩锁效应》讲义

双极型晶体管的载流子传输过程

根据传输过程可知: IE=IB+ IC ----------------------------------------- (式1) 和IC= ICN+ ICBO ----------------------------------------- (式2) 集电结收集的电子流是发射结发射的总电子流的一部分,常用一系数α来表示,那么α=传输到集电极的电流/发射极注入 电流,即 α=ICN/IE, 通常IC >> ICBO 那么α≈IC/IE ----------------------------------------- (式3) α为电流放大系数。它只与管子的结构尺寸和掺杂浓度有关,与外加电压无关,一般α = 0.9~0.99。 设定β =IC/IB 根据式1可得β =IC/( IE -IC) 根据式3可得β = αIE /(1-α)IE 最终得到β = α /(1-α) β是另一个电流放大系数。同样,它也只与管子的结构尺寸和掺杂浓度有关,与外加电压无关,一般β >> 1。

第二章 CMOS器件基础

★ M1和M2在C点共用一个S/D结,M2和M3在N点共用一个S/D结。 ★ M3的多晶硅栅不能直接连接到M1的源极,因此需要金属互连。

MOS管的电流方程

NMOS

PMOS

MOS管的电流方程

1. 迁移率

μn: 电子迁移率 μp: 空穴迁移率 若 μn≈ 1300 cm2/s·V μp≈500 cm2/s·V 则: μn /μp=2.6 一般情况下, μn /μp=2~4,空穴迁移率小于电子迁移率。 因此,PMOS器件具有较低的电流驱动能力,工作速度比 NMOS要慢。

MOS管的电流方程

3. W/L,沟道宽度和沟道长度之比 电流与器件宽长比成正比。 器件的最小沟道长度Lmin标志着工艺水平,W 表示器件的大小,W越大,管子电流越大,导电能 力越强,等效电阻越小。

MOS管的电流方程

4. VTHN,VTHP为开启电压,假设VDD=5V 增强型NMOS管 VTHN≈(0.14~0.18)VDD ≈(0.7~0.9)V 增强型PMOS管 VTHP≈-0.16VDD ≈-0.8V 通过工艺控制可以将阈值电压降低,从而使器 件适合于低电源工作。

阱:局 部衬底

★ MOSFET : Metal-Oxide Semiconductor Field-Effect Transistor,金属氧化物半导体场效应管 ★ CMOS : 互补MOS ★ n型MOSFET :载流子为电子;p型MOSFET :载流子为空穴

《CMOS晶体管基础》课件

需要建立更完善的可靠性测试与评估方法,以确 保CMOS晶体管的可靠性和稳定性。

新材料与新器件结构的探索

新材料的应用

为了克服现有材料的限制,需要探索新的材 料应用于CMOS晶体管中,如高迁移率材料 、二维材料等。

新器件结构的探索

为了提高CMOS晶体管的性能和功能,需要探索新 的器件结构,如新型的逻辑门电路、三维集成等。

CMOS晶体管的发展历程

总结词

CMOS晶体管的发展经历了从20世纪60年代的初期研究到现在的广泛应用的过程。

详细描述

20世纪60年代初期,人们开始研究CMOS晶体管,并逐渐认识到其低功耗和高可靠性的优点。随着半导体工艺 技术的不断进步,CMOS晶体管的性能得到了显著提升,应用领域也不断扩大。现在,CMOS晶体管已经成为集 成电路中的基本元件,广泛应用于各种电子设备中。

等。

03

CMOS晶体管的制造工 艺

衬底材料的选择

01

02

03

衬底材料

硅是最常用的衬底材料, 因为它具有高导热性、高 耐久性和低成本。

晶向选择

根据晶体管的设计要求, 选择适当的晶向以获得最 佳性能。

衬底质量

衬底应无缺陷、杂质和裂 缝,以确保晶体管的可靠 性和稳定性。

掺杂工艺

元素选择

选择适当的元素进行掺杂,以改变材料的导电性 能。

《cmos晶体管基础》ppt课件

目录

• CMOS晶体管简介 • CMOS晶体管的工作原理 • CMOS晶体管的制造工艺 • CMOS晶体管的性能优化 • CMOS晶体管的挑战与展望

01

CMOS晶体管简介

定义与特性

总结词

CMOS晶体管是一种集成电路的基本元件,具有低功耗、高噪声容限、高可靠性等特性 。

模拟电子技术基础讲义晶体管PPT学习教案

黑表笔 1 2 3

红表笔 2 3 1 3 1 2

阻值 ∞ ∞ 4K 4K ∞ ∞

第23页/共50页

黑表笔接1,红表笔接3,接触2:100 K 黑表笔接3,红表笔接1,接触2:30 K

第24页/共50页

4、三极管的命名方式:

国产晶体管的命名方法: 日本半导体器件的命名方法: 美国晶体管型号命名方法: 欧洲晶体管型号命名方法: 韩国三星公司:

(1)发射结 正偏、 集电结 反偏; 工作在放 大区。

(2)发射结 正偏、 集电结 正偏; 工作在饱 和区。

(3)发射结 反偏; 工作在 截止区 。

第41页/共50页

测得PNP型、锗BJT的三个电极b、e、c的对 地电压 分别为 (1)Vb=-6.2V,Ve=-6V,VC=-9V (2) Vb=1V,Ve=1.2V,VC=1.5V (3) Vb=8V,Ve=7.8V,VC=7V 问:管子工作在输出特性曲线的什么 区?

第15页/共50页

(1) 三颠倒,找基极: 三极管是含有两个PN结的半导体器件。根据

两个PN结连接方式不同,只要找出两个PN结的公 共极,即为三极管的基极。

第16页/共50页

具体方法是将万用表调至电阻挡的 R×100或 R×1k挡,先用红表笔放在三极管的一只管脚上,用 黑表笔去碰三极管的另两只管脚,如果两次全通,则 红表笔所放的管脚就是三极管的基极。如果一次没找 到,则红表笔换到三极管的另一个管脚,再测两次; 如还没找到,则红表笔再换一下,再测两次。如果还 没找到,则改用黑表笔放在三极管的一个管脚上,用 红表笔去测两次看是否全通,若一次没成功再换。这 样最多测量12次,总可以找到基极。

PCM iCCE

第46页/共50页

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

MOSFET I-V Characteristics(伏安特性)曲线

VGS:栅极和源极的电压差。 VDS: 漏极和源极的电压差。 ID : 流过漏极和源极的电流。 Vth: 器件的阈值电压,当VGS增加到一定的值时,栅极下面的P型 半导体会发生反型,形成N型半导体的沟道。此时D和S之间可以有 电流流过,这个特定的电压值,称之为值电压。

电容值的计算(了解)

Capacitance values are the same as Accumulation

Co

x

ox

TOX

and

CoxCo xWL

Capacitance is comprised of three components

C gb ox LT 2O LX D W C g dC g s oT xLO W D X CG W D CO G W SO

Aluminum

L

W

Gate

Source

Drain

G

S

Poly D

Oxide

n+

p-substrate

Leff LDrawn

n+ LD

n+

n+

W

W

线宽(Linewidth), L

特征尺寸(Feature Size)指什么?

MOSFET的三个重要几何参数

Lmin、 Wmin和 tox 由工艺确定 Lmin: MOS工艺的特征尺寸(feature size)

➢ 晶体管偏置在 VGS VTHN , 此时沟道已形成. ➢ 漏源电压 (VDS) 较小. ➢ 漏极电流可用下式表示:

IDVGSVTHN VDSV2D 2S

WhereKPnW L

MOSFET I-V 特性 (饱和区Saturation Region)

➢ 晶体管偏置在 VGS VTHN ,此时沟道已形成. ➢ 漏源电压较大 (i.e. VDS VGS – VTHN). ➢ 理想的漏极电流可表示为:

4、MOS Capacitance

MOS电容:由器件本生的构造引起的。 Cgs: 栅极和源极的寄生电容。(平板电容) Cgd: 栅极和漏极的寄生电容。(平板电容) Cgb: 栅极和衬底的寄生电容。 Cdb: 漏极和衬底的寄生电容。(PN结电容) Csb: 源极和衬底的寄生电容。(PN结电容)

是影响最大的

截止区:

ID=0, VGS< Vth

线性区 (Linear):

IDVGSVTHN VDSV2D 2S

,VDS〈 VGS-Vth

饱和区 (Saturation):

ID 2V G S V TH 21 N cV D S V D _ S Sat WhereKPnW L

VDS >= VGS-Vth

ID2

VGSVTHN2

WhereKPnW L

➢ 当晶体管被夹断(pinchoff)时, 发生了什么? ➢ 增大 VDS 使耗尽区扩大到沟道中. ➢ 这导致ID 随 VDS 的增加而增大. 因此ID 可写为:

ID 2V G S V TH 21 N cV D S V D _ S Sathreshold voltage): V TH N m 2 sF Q b C o o Q s x s 2 q C o sN i x A 2 F V S B2 F

对于一般工艺,Vtn=0.83V(NMOS的阈值电压), Vtp=-0.91V(PMOS的阈值电压), 阈值电压由工艺参数决定

Area (poly)

54 18 11 aF/um2

Area (M1)

46 17 aF/um2

Area (M2)

49 aF/um2

Area (N+act.)

3599

aF/um2

以上各式中:

Eox: 氧化层的介电常数。

Tox: 氧化层的厚度。

Cox’ : 表示单位面积氧化层的电容值。

LD: 表示栅极和S、D重叠的宽度(由工艺精度决定)。

深亚微米CMOS IC工艺的寄生电容(数据)

Cap. N+Act.P+Act. Poly M1 M2 M3 Units

Area (sub.) 526 937 83 25 10 8 aF/um2

interface)

VSB = 源到衬底的电势差(Source to bulk voltage)

对于一般工艺,Vtn= 0.83V(NMOS的阈值电压), Vtp= - 0.91V(PMOS的阈值电压),

阈值电压由工艺参数决定

3、MOSFET的 I-V 特性 (线性区Triode Region)

沟道夹断

2、阈值电压(Threshold Voltage)

➢ 阈值电压是当沟道反型时所需的电压 (i.e. 将沟道从p型变 到n型的电压).

➢ 阈值电压可按下式计算:

V TH N m 2 sF Q b C o o Q s x s 2 q C o sN i x A 2 F V S B2 F

决定MOSFET的速度和功耗等众多特性 L和W由设计者选定 通常选取L= Lmin,由此,设计者只需选取W W影响MOSFET的速度,决定电路驱动能力和功耗

②,VGS>=Vthn时

由于电场的作用,P—SUB中的少量电子移动到了沟 道的顶部。这样就形成了一条电子移动的通道,如 果VDS>0,就会形成源漏电流IDS。

二 CMOS晶体管基础

➢ 主要内容

1 、结构及工作原理 2、阈值电压 3、电流—电压方程(I-V特性) 4、MOS管寄生电容 5、小信号等效电路 6、gm、gds 7、MOSFET的数字模型 8、衬偏调制效应 9、MOSFET的温度特性 10、CMOS结构图

1、工作原理

3D结构图

Polysilicon

其中

ms = 栅和衬底的接触电势(contact potential between the gate and the bulk)

F = 衬底的静电势(electrostatic potential of the substrate) Q`bo = 耗尽区的电荷(charge in the depletion region) Q`ss = Si/SiO2 接触面的电荷(Si/Sicharge at the Si/SiO2