Quartus II 时钟约束概念

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

Quartus II Handbook, Volume 3 6-28

时钟约束(Clock Specification):

约束所有时钟(包括你的设计中特有的时钟)对准确的时序分析结果而言是必不可少的。Quartus II TimeQuest Timing Analyzer为各种各样的时钟配置和典型时钟提供许多SDC命令。

这个章节将介绍SDC可用的应用编程接口,以及描述指定的时钟特性。

时钟(Clocks)

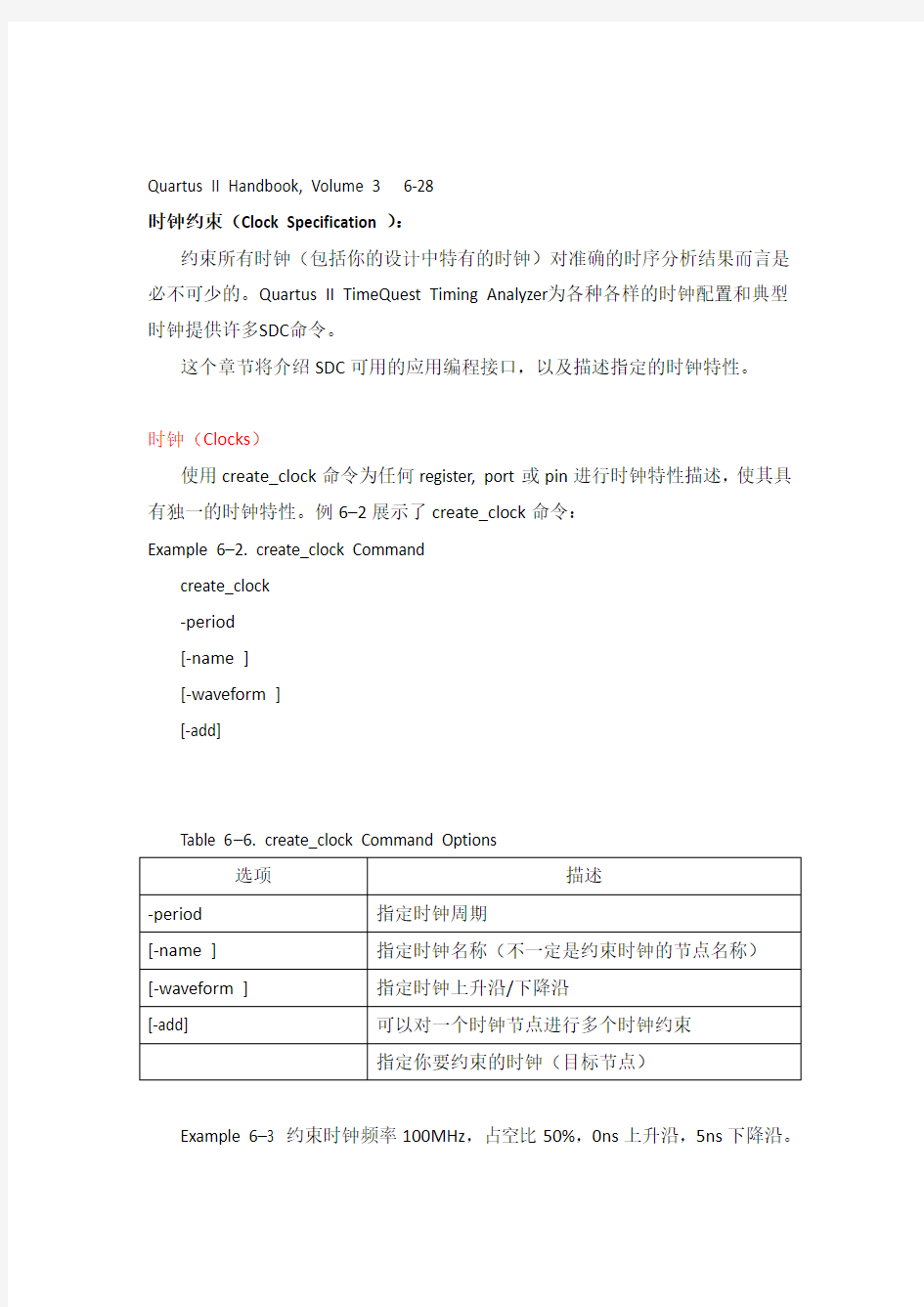

使用create_clock命令为任何register, port或pin进行时钟特性描述,使其具有独一的时钟特性。例6–2展示了create_clock命令:

Example 6–2. create_clock Command

create_clock

-period

[-name

[-waveform

[-add]

Table 6–6. create_clock Command Options

Example 6–3 约束时钟频率100MHz,占空比50%,0ns上升沿,5ns下降沿。

Example 6–3. 100MHz Clock Creation

create_clock –period 10 –waveform { 0 5 } clk

Example 6–4和上例相差90度的相位。

Example 6–4. 100MHz Shifted by 90 Degrees Clock Creation

create_clock –period 10 –waveform { 2.5 7.5 } clk_sys

使用create_clock命令约束时钟缺省的source Latency值为0。Quartus II TimeQuest Timing Analyzer自动为非虚拟时钟(non-virtual clocks)计算时钟网络延时(clock’s network latency)。

Quartus II Handbook, Volume 3 6-29

生成时钟(Generated Clocks)

Quartus II TimeQuest Timing Analyzer可以把修改或改变主时钟(或者引入时钟)特性的分频时钟、波纹时钟和电路作为生成时钟。

你可以定义这些电路的输出作为生成时钟。这些定义可以让Quartus II TimeQuest Timing Analyzer分析这些时钟以及关联的时钟网络延时(network latency)。

使用create_generated_clock命令定义生成时钟。

Example 6–5. create_generated_clock Command

create_generated_clock

[-name

-source

[-edges

[-edge_shift

[-divide_by

[-multiply_by

[-duty_cycle

[-add]

[-invert]

[-master_clock

[-phase

[-offset

Table 6–7. create_generated_clock Command Options

源延时是由于从主时钟(不一定是主管脚)开始的时钟网络延时所致。你可以使用set_clock_latency –source命令约束源延时。

Figure 6–17 展示了如何产生一个基于10ns时钟的反向生成时钟:

Figure 6–17. Generating an Inverted Clock

create_clock -period 10 [get_ports clk]

create_generated_clock -divide_by 1 -invert -source [get_registers clk] \

[get_registers gen|clkreg]

Figure 6–18 展示了如何使用-edges和-edge_shift选项以改变生成时钟。

Figure 6–18. Edges and Edge Shifting a Generated Clock

create_clock -period 10 -waveform { 0 5} [get_ports clk]

# Creates a divide-by-t clock

create_generated_clock -source [get_ports clk] -edges {1 3 5 } [get_registers \ clkdivA|clkreg]

# Creates a divide-by-2 clock independent of the master clocks’ duty cycle (now 50%)

create_generated_clock -source [get_ports clk] -edges {1 1 5} -edge_shift { 0 2.5 0 } \

Figure 6–19 展示了-multiply_by选项对生成时钟的影响。

Figure 6–19. Multiplying a Generated Clock

create_clock -period 10 -waveform { 0 5 } [get_ports clk]