数字电路习题-第七章

北京理工大学数字电路第七章答案

北京理工大学数字电路第七章答案二进制数10101转换为十进制数后为() [单选题] *A.15B.21(正确答案)C.18D.10逻辑函数式D+D,简化后结果是() [单选题] *A.2DB.D(正确答案)C.D²D.0一位十六进制数可以用二进制数来表示,需要二进制的位数是() [单选题] *A.1B.2C.4(正确答案)D.16当决定某个事件的全部条件都具备时,这件事才会发生。

这种关系称为() [单选题] *A.或逻辑B.与逻辑(正确答案)C.非D.异或010*********的8421码为() [单选题] *A.496(正确答案)B.495C.598D.4694位二进制数可用十六进制数来表示,需要十六进制的位数是() [单选题] *A.1(正确答案)B.2C.3D.48421BCD码用4位二进制数表示十进制数的位数是() [单选题] *A.1(正确答案)B.2C.3D.4在数字电路中,不属于基本逻辑门是() [单选题] *A.与门B.或门C.非门D.与非门(正确答案)如图所示门电路,电路实现的逻辑式Y= [单选题] *A.Y=(AB)\B.Y=ABC.Y=A+B(正确答案)D.Y=(A+B)\如图所示的波形图表示的逻辑关系是()[单选题] *A.F=A·B(正确答案)B.F=A+BC.F=(A·B)\D.F=(A+B)\异或门F=A⊕B两输入端A、B中,A=1,则输出端F为() [单选题] *A.A⊕BB.B\(正确答案)C.BD.0下列表所示的真值表完成的逻辑函数式为()[单选题] *A.F=ABB.F=ABC.F=A⊕BD.F=A+B(正确答案)当A=B=0时,能实现F=1的逻辑运算是() [单选题] *A.F=A·BB.F=A+BC.F=A⊕BD.F=(A+B)\(正确答案)八位二进制数能表示十进制数的最大值是() [单选题] *A.255(正确答案)B.248C.192D.168将(01101)2转换为十进制数为() [单选题] *A.13(正确答案)B.61C.51D.25逻辑函数式Y=A+A,化简后的结果是() [单选题] *A.2AB.A(正确答案)C.1D.A2逻辑函数式Y=EF+E\+F\的逻辑值为() [单选题] *A.EFB.(EF)\C.0D.1(正确答案)以下表达式中符合逻辑运算法则的是() [单选题] *=C2B.1+1=10C.A·1=1D.A+1=1(正确答案)当逻辑函数有n个变量时,取值组合有() [单选题] *A.nB.2nC.n²D.2"(正确答案)二进制数码为(11101),则对应的十进制数为() [单选题] *A.29(正确答案)B.28C.13D.14下列说法中与BCD码的性质不符的是() [单选题] *A.一组四位二进制组成的码只能表示一位十进制B.BCD码是一种人为选定的0~9十个数字的代码C.BCD码是一组四位二进制数,能表示十六以内的任何一个十进制数(正确答案)D.BCD码有多种数字信号和模拟信号的不同之处是() [单选题] *A.数字信号在大小上不连续,时间上连续,而模拟信号则相反B.数字信号在大小上连续,时间上不连续,而模拟信号则相反C.数字信号在大小、时间上均不连续,而模拟信号则相反(正确答案)D.数字信号在大小、时间上均连续,而模拟信号则相反“与非”运算的结果是逻辑“0”的输入是() [单选题] *A.全部输入是“0”B.任一输入是“0”C.仅一输人是“0”D.全部输入是“1”(正确答案)相同为“0”不同为“1”,它的逻辑关系是() [单选题] *A.或逻辑B.与逻辑C.异或逻辑(正确答案)D.同或逻辑一只四输入端或非门,使其输出为“1”的输入变量取值组合有种。

数字电路第七章答案

第七章可编程逻辑器件PLD第一节基本内容一、基本知识点(一)可编程逻辑器件PLD基本结构可编程逻辑器件PLD是70年代发展起来的新型逻辑器件,相继出现了只读存储器ROM、可编程只读存储器PROM、可编程逻辑阵列PLA、可编程阵列逻辑PAL、通用阵列逻辑GAL 和可擦写编程逻辑器件EPLD等多个品种,它们的组成和工作原理基本相似。

PLD的基本结构由与阵列和或阵列构成。

与阵列用来产生有关与项,或阵列把所有与项构成“与或”形式的逻辑函数。

在数字电路中,任何组合逻辑函数均可表示为与或表达式,因而用“与门-或门”两级电路可实现任何组合电路,又因为任何时序电路是由组合电路加上存储元件(触发器)构成的,因而PLD的“与或”结构对实现数字电路具有普遍意义。

在PLD中,输入电路中为了适应各种输入情况,每一个输入信号都配有一缓冲电路,使其具有足够的驱动能力,同时产生原变量和反变量输出,为与门阵列提供互补信号输入。

输出电路的输出方式有多种,可以由或阵列直接输出,构成组合方式输出,也可以通过寄存器输出,构成时序方式输出。

输出既可以是低电平有效,也可以是高电平有效;既可以直接接外部电路,也可以反馈到输入与阵列,由此可见PLD的输出电路根据不同的可编程逻辑器件有所不同。

(二)可编程逻辑器件分类1.按编程部位分类PLD有着大致相同的基本结构,根据与阵列和或阵列是否可编程,分为三种基本类型:(1)与阵列固定,或阵列可编程(2)与或阵列均可编程(3)与阵列可编程,或阵列固定归纳上述PLD的结构特点,列于表7-1。

表7-1 各种PLD的结构特点2.按编程方式分类(1)掩膜编程(2)熔丝与反熔丝编程(3)紫外线擦除、电可编程(4)电擦除、电可编程(5)在系统编程(Isp)(三)高密度可编程逻辑器件HDPLD243通常衡量可编程逻辑器件芯片的密度是以芯片能容纳等效逻辑门的数量,一般是以2000为界限,即芯片容纳等效逻辑门小于2000门,称它为低密度可编程逻辑器件或简单的可编程逻辑器件(SPLD),若大于2000等效逻辑门,称为高密度可编程逻辑器件(HDPLD)。

数字电子技术第七章作业及答案

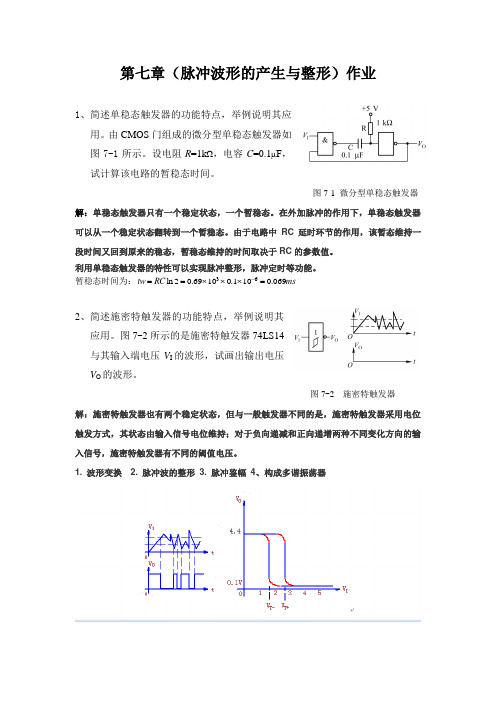

第七章(脉冲波形的产生与整形)作业1、简述单稳态触发器的功能特点,举例说明其应用。

由CMOS 门组成的微分型单稳态触发器如图7-1所示。

设电阻R =1k Ω,电容C =0.1μF ,试计算该电路的暂稳态时间。

图7-1 微分型单稳态触发器 解:单稳态触发器只有一个稳定状态,一个暂稳态。

在外加脉冲的作用下,单稳态触发器可以从一个稳定状态翻转到一个暂稳态。

由于电路中RC 延时环节的作用,该暂态维持一段时间又回到原来的稳态,暂稳态维持的时间取决于RC 的参数值。

利用单稳态触发器的特性可以实现脉冲整形,脉冲定时等功能。

暂稳态时间为:ms RC tw 069.0101.01069.02ln 63=⨯⨯⨯==-2、简述施密特触发器的功能特点,举例说明其应用。

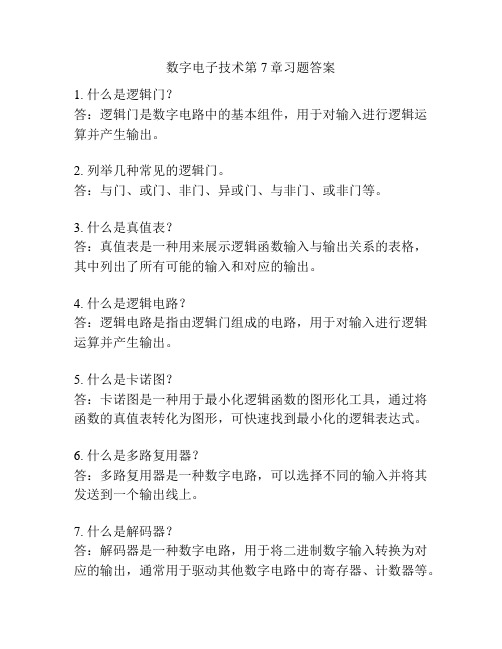

图7-2所示的是施密特触发器74LS14与其输入端电压V I 的波形,试画出输出电压V O 的波形。

图7-2 施密特触发器 解:施密特触发器也有两个稳定状态,但与一般触发器不同的是,施密特触发器采用电位触发方式,其状态由输入信号电位维持;对于负向递减和正向递增两种不同变化方向的输入信号,施密特触发器有不同的阈值电压。

1. 波形变换2. 脉冲波的整形3. 脉冲鉴幅 4、构成多谐振荡器3、用定时器555组成多谐振荡器,要求输出电压V O 的方波周期为1ms ,试选择电阻与电容的数值,并画出电路图。

解:周期T 计算如下:121269.0C R R T )(+=取C 1=0.1μF ,R 2=5.1k Ω则有:Ω=⨯-⨯=⨯⨯-⨯⨯=-=--k R C T R 3.4102.101045.1101.52101.069.010269.0343632114、试分析如图7-3所示脉冲信号产生电路。

(1)说明该电路各部分的功能。

(2)画出A 、B 、C 和v O 各点波形。

(3)已知施密特触发器CT4014的V T+=1.6V ,V T -=0.8V 。

求电路的输出脉宽t W 。

数字电路第七章答案

第七章可编程逻辑器件PLD第一节基本内容一、基本知识点(一)可编程逻辑器件PLD基本结构可编程逻辑器件PLD是70年代发展起来的新型逻辑器件,相继出现了只读存储器ROM、可编程只读存储器PROM、可编程逻辑阵列PLA、可编程阵列逻辑PAL、通用阵列逻辑GAL 和可擦写编程逻辑器件EPLD等多个品种,它们的组成和工作原理基本相似。

PLD的基本结构由与阵列和或阵列构成。

与阵列用来产生有关与项,或阵列把所有与项构成“与或”形式的逻辑函数。

在数字电路中,任何组合逻辑函数均可表示为与或表达式,因而用“与门-或门”两级电路可实现任何组合电路,又因为任何时序电路是由组合电路加上存储元件(触发器)构成的,因而PLD的“与或”结构对实现数字电路具有普遍意义。

在PLD中,输入电路中为了适应各种输入情况,每一个输入信号都配有一缓冲电路,使其具有足够的驱动能力,同时产生原变量和反变量输出,为与门阵列提供互补信号输入。

输出电路的输出方式有多种,可以由或阵列直接输出,构成组合方式输出,也可以通过寄存器输出,构成时序方式输出。

输出既可以是低电平有效,也可以是高电平有效;既可以直接接外部电路,也可以反馈到输入与阵列,由此可见PLD的输出电路根据不同的可编程逻辑器件有所不同。

(二)可编程逻辑器件分类1.按编程部位分类PLD有着大致相同的基本结构,根据与阵列和或阵列是否可编程,分为三种基本类型:(1)与阵列固定,或阵列可编程(2)与或阵列均可编程(3)与阵列可编程,或阵列固定归纳上述PLD的结构特点,列于表7-1。

表7-1 各种PLD的结构特点2.按编程方式分类(1)掩膜编程(2)熔丝与反熔丝编程(3)紫外线擦除、电可编程(4)电擦除、电可编程(5)在系统编程(Isp)(三)高密度可编程逻辑器件HDPLD243通常衡量可编程逻辑器件芯片的密度是以芯片能容纳等效逻辑门的数量,一般是以2000为界限,即芯片容纳等效逻辑门小于2000门,称它为低密度可编程逻辑器件或简单的可编程逻辑器件(SPLD),若大于2000等效逻辑门,称为高密度可编程逻辑器件(HDPLD)。

数字电子技术第七章习题答案

第七章D/A 和A/D 转换器7.1填空1、8位D/A转换器当输入数字量只有最高位为高电平时输出电压为5V,若只有最低位为高电平,则输出电压为40mV 。

若输入为10001000,则输出电压为5.32V 。

2、A/D转换的一般步骤包括采样、保持、量化和编码。

3、已知被转换信号的上限频率为10kH Z,则A/D转换器的采样频率应高于20kH Z。

完成一次转换所用时间应小于50μs。

4、衡量A/D转换器性能的两个主要指标是精度和速度。

5、就逐次逼近型和双积分型两种A/D转换器而言,双积分型抗干扰能力强;逐次逼近型转换速度快。

7.2CPU O-0.625V-1.25V-1.875V-2.5V7.32R 2R 2R 2R2R R R R 2R Q0 Q1 Q2 Q33RRRU O&-+-+CP ui+ -四位二进制计数器RdV AG首先将二进制计数器清零,使U o=0。

加上输入信号(U i>0),比较器A输出高电平,打开与门G,计数器开始计数,U o增加。

同时U i亦增加,若U i>U o,继续计数,反之停止计数。

但只要U o未达到输入信号的峰值,就会增加,只有当U o=U imax 时,才会永远关闭门G,使之得以保持。

7.41、若被检测电压U I(max)=2V,要求能分辨的最小电压为0.1mV,则二进制计数器的容量应大于20000;需用15位二进制计数器2、若时钟频率f CP=200kH Z,则采样时间T1=215×5μs=163.8ms3、TRC2V5V1⨯=RC=409.5ms7.5 1、完成一次转换需要36μs2、A/D转换器的输出为0100111118。

数字电路与数字电子技术 课后答案第七章

第七章 时序逻辑电路1.电路如图P7.1所示,列出状态转换表,画出状态转换图和波形图,分析电路功能。

图P7.1 解:(1)写出各级的W .Z 。

D 1=21Q Q ,D 2=Q 1,Z=Q 2CP( 2 ) 列分析表( 3 ) 状态转换表(4)状态转换图和波形图。

图7.A1本电路是同步模3计数器。

2. 已知电路状态转换表如表P7.1所示,输入信号波形如图P7.2所示。

若电路的初始状态为Q2Q1 = 00,试画出Q2Q1的波形图(设触发器的下降沿触发)。

Q 2 Q 1 D 2 D 1 Q 2n+1 Q 1n+1 Z0 0 0 1 0 1 0 0 1 1 0 1 0 0 1 0 0 0 0 0 1 1 1 1 0 1 0 1Q 2 Q 1 Q 2n+1 Q 1n+1 Z0 0 0 1 0 0 1 1 0 0 1 0 0 0 1 1 1 1 0 1CPCP X Q 1 0Q 2 0 Z CP Q 1 0 Q 1 0Z ( b ) Q 2 Q 1 /Z( a )011解:由状态转换表作出波形图3. 试分析图P7.3所示电路,作出状态转换表及状态转换图,并作出输入信号为0110111110相应的输出波形(设起始状态Q 2Q 1 = 00)。

( a )( b )解:(1)写W .Z 列分析表J K( 2 )CPX图P7.3CPX Q 1 0 Q 1 0 Z图P7.A2(3)作出输出波形图:1 根据状态转换表,作出状态的响应序列,设y = Q 2Q 1 X : 0 1 1 0 1 1 1 1 1 0 y n : 0 02 1 0 2 13 3 3 y n+1: 0 2 1 0 2 1 3 3 3 0 Z : 1 1 1 1 1 1 1 0 0 12 根据状态响应序列画响应的输出波形。

4.。

X :Z :0 0 0 0 0 0 0 0 0 0 1 1 0 0 … 解:(1)建立原始的状态转换图和状态转换表 设:A --- 输入“0”以后的状态。

数字集成电路分析与设计 第七章答案

CHAPTER 7P7.1. Assume that all nodes start at 0V. The first row outputs will be at DD T V V -. Since thesenodes are also the gate nodes of the second row of transistors, their source nodes will be at 2DD T V V -. Likewise, the last row of transistors have voltages of 3DD T V V -. However, this value is below 0V so we leave them at 0V.1.2V1.2V0.73V 0.73V 0.73V0.33V0.33V0.33V0V0V0VP7.2. (a)(b)(c)(d)P7.3. (a) First calculate V Q .()01.80.51.15Q DD T DD T V V V V V Vγ=-=-+=--=Since this is slightly below 1.3V (voltage at which the PMOS turns on), we assume that the PMOS is slightly on. Since the PMOS’s V GS is quite low (because Q is high) and its V DS is quite high (because Q is low), the transistor is very likely in saturation. Similarly for the NMOS, because its V GS is high and its V DS is low, it’s likely in the linear region. Equating the two currents:()()()()()()()()22,,222211DSNDSN CN NQ Q CN NSDP sat DSN linV N N OX GSN T DSN P sat OX GSP T V GSP T CP PN V N N OX Q T Q P sat OX DD Q T V DD Q T CP PE L N I I W C V V V W v C V V V V E L L W C V V V W v C V V V V V V E L L μμ=---=-++----=--++For simplicity we shall assume that 11Q CN NV E L +≈ and220QV ≈.()()()2N N OX Q T QP sat OX DD Q T DD Q T CP P NW C V V V W v C V V V V V V E L L μ---≈--+Solve to produce:0.0080V Q V ≈When the CLK goes low, the intermediate output suffers from clock feedthough. To calculate the effects of clock feedthrough, let us first compute the capacitances involved. The capacitance from the clock signal to Q is:(.2/)(.2)0.0.4fF GS OL C C fF um um ===The capacitance from the Q to ground is:()()()(),310.2320.2 1.4fF Q DN IN inv d g C C C C W C W =+=+=+=The capacitive feedthrough equation is:()210.04 1.80.05V 0.04 1.41.150.05 1.1VGS CLK Q GS Q Q Q Q C V V C C V V V -∆∆===-++=+∆=-=To get the new value of Q V , first determine the determine the regions of operation of the transistors in the inverter by calculating V S . Then, once again, use the currentequations to determine Q V .Since the new voltage of V Q is still greater than the switching voltage, the transistors are in the same regions:()()()()()()2000460.4100.2810P N sat OX DD Q T Q N N OX Q T DD Q T CP P OXW L v C V V V V W C V V V V V E L C μ---≈---+⨯⨯≈()()()21.8 1.10.50.2270OX C --()()0.016V1.10.5 1.8 1.10.5 4.8≈---+(b) In this case 1.8Q DD V V V == and 0Q V =. Clock feedthrough has no effect since the transmission gate CLK signals cancel each other out.()()()()()()()(),3151515315(23)312.5102100.2110(2)0.23(210)(0.2)312.5101100.2257.532.5pass pass inv d inv eqn g eff g eqn d t R C R C R C W C W C W R C Wps ps ps----=+=+++⎡⎤=⨯⨯+⨯+⨯+⎣⎦⨯⨯=+=P7.4.a. Out A BC =+BBOutb. Out AB BC C =++Outc. ()Out A B C AB ABC AB =+++=+BBOutd. ()()1Out A B C AB ABC AB AB C AB A B =+++=+=+==+OutP7.5.a. ()Out A B C =+b. ()()Out A B C D E =+++ P7.6.a. Out A BC =+c bclkclkV DDb. Out AB BCC =++a bclkclkV DDc.()Out A B C AB ABC AB =+++=+V DDd.()()()Out A B C AB A B C A B AB=+++=+++=+aclkclkV DDP7.7.Assuming that one of the transistors in each transmission gate is being driven by a min-sized inverter:a.()()()()122333passinvRC R R RLERC R R+====b.()()()()()()()()313133313133AAinvCCinvRRC RLERC R RRRC RLERC R R========()()()()339333BBinvRRC RLERC R R====P7.8.a. Out A sel B sel =⋅+⋅b.R inv 6.25k ΩC inv,diff 1.2fF C pass,gate 0.8fF C pass,diff0.8fFR pass 6.25k ΩCpass,diff0.8fFCpass,gate0.8fFfC inv,gate2.4f fFCpass,diff0.8fFc. ()()(),,,,,,2A C inv inv diff pass gate pass diff inv pass inv gate pass gate pass diff t R C C C R R fC C C -=++++++ d. (),,inv inv LOADC out inv diff LOAD inv inv diffR R C t fC C R C f f-=+=+ e.()()()()(),,,,,,,,220inv inv diff pass gate pass diff inv pass inv gate pass gate pass diff inv LOADinv inv diff inv LOAD inv pass inv gate t R C C C R R fC C C R C R C fR C dtR R C df f f =++++++++=+-===3.2=P7.9. In both of these cases, the logical effort is the same due to the fact that the longest pathfrom output to ground is three transistors long. Assume that the CLK arrives ahead of the signals. Then,12()26663R R LE R λλ+== P7.10. We will use 0.18um technology and the node names below:W=4W=4OutFor the two inverter inputs:()()()3230.2 1.2fF inv g C C W ===For the pass gate inputs:()0.4fF pass g C C W ==At node x:()(3)(2) 1.4x eff eff g C C W C W C W fF =++=At node y:()2((2))(2)2y eff g eff C C W C W C W fF =++=At node Out:()((2))(2) 1.2out eff g eff C C W C W C W fF =++=The shortest path is through the one of the G ND input nodes to the output:()()()()min 212.5 1.4212.5 1.247.5x out t RC RC k fF k fF ps =+=+=The longest path is through one of the inverters to the output.()()()()()()max 2312.5 1.4212.52312.5 1.2112.5sx y out t RC RC RC k fF k fF k fF p =++=++=P7.11. At 0t =: DD F V =0X =?Y =.When the a goes high the first time, the voltage at X would be computed using the charge-sharing formula:()101.21V 210F DDX X F C V V C C ===++But because the maximum allowable voltage at node x is 0.734V, set 0.734V X V = Then recomputed V F :()()()()10 1.220.734 1.05V 10F DD X X F F C V C V V C --===When Phi goes down, F DD V V = and V X and V Y remains the same. The next time the Phi goes up, all the internal nodes are 0. When Phi goes down, F DD V V = and V X and V Y remains at 0. P7.12.P7.13.a. The input settings that give you the worst-case charge sharing are any of 1a c e === and both of 0b d ==. Essentially, what you are doing it trying to create the greatest amount of parasitic capacitances without creating a path to G ND .b. Assuming that transistors share nodes to reduce capacitance.()()()()()()()12*11125(3)(5) 5.2fF 333190.2 1.8fF 5.2 1.8 1.34V 5.2 1.8g d g d C C W C W C W C C W W W C V V C C =++==++=====++ The actual voltage would be larger than this since the internal node cannot rise above V DD -V T .c. This circuit fails if the worse case voltage falls below the switching voltage which can be computed to be V S =0.92V. Therefore, the circuit will operate properly. P7.14. Both of these circuits act as latches. When EN is on, there is a path from the output toeither V DD or G ND . The first latch is better than the second because the second latch suffers from charge sharing. When EN is off, there is no path from the output to either of the sources, if IN is switching it is possible for whatever charge that is held on OUT to be shared with the internal nodes between the two NMOS’s or the two PMOS’s. Therefore, the second one is not as good as the first one. P7.15.a.OUT OL X DD TV V V V V ==-b. First, let ’s find the required change in voltage:()()2OUT DD OLX DD T DD T TV V V V V V V V V ∆=-∆=+--=Now, let’s set up the clock feedthrough equation and solve for C b :22b OUT X b XX X T Xb OUT X DD OL TC V V C C V C V C C V V V V V ∆∆=+∆==∆-∆--。

数字电子技术第7章习题答案

数字电子技术第7章习题答案

1. 什么是逻辑门?

答:逻辑门是数字电路中的基本组件,用于对输入进行逻辑运算并产生输出。

2. 列举几种常见的逻辑门。

答:与门、或门、非门、异或门、与非门、或非门等。

3. 什么是真值表?

答:真值表是一种用来展示逻辑函数输入与输出关系的表格,其中列出了所有可能的输入和对应的输出。

4. 什么是逻辑电路?

答:逻辑电路是指由逻辑门组成的电路,用于对输入进行逻辑运算并产生输出。

5. 什么是卡诺图?

答:卡诺图是一种用于最小化逻辑函数的图形化工具,通过将函数的真值表转化为图形,可快速找到最小化的逻辑表达式。

6. 什么是多路复用器?

答:多路复用器是一种数字电路,可以选择不同的输入并将其发送到一个输出线上。

7. 什么是解码器?

答:解码器是一种数字电路,用于将二进制数字输入转换为对应的输出,通常用于驱动其他数字电路中的寄存器、计数器等。

8. 什么是编码器?

答:编码器是一种数字电路,用于将多个输入端连接到一个二进制数字输出端,也可以实现将多个开关等输入转换为一个数字信号输出。

9. 什么是计数器?

答:计数器是一种数字电路,可用于记录电路所经过的时间或事件数量,通常用于计时器、频率计等应用。

10. 什么是触发器?

答:触发器是一种数字电路,可用于存储和控制数字信号,通常用于存储器、寄存器等应用。

《数字电路-分析与设计》第七章习题及解答(部分1) 北京理工大学出版社

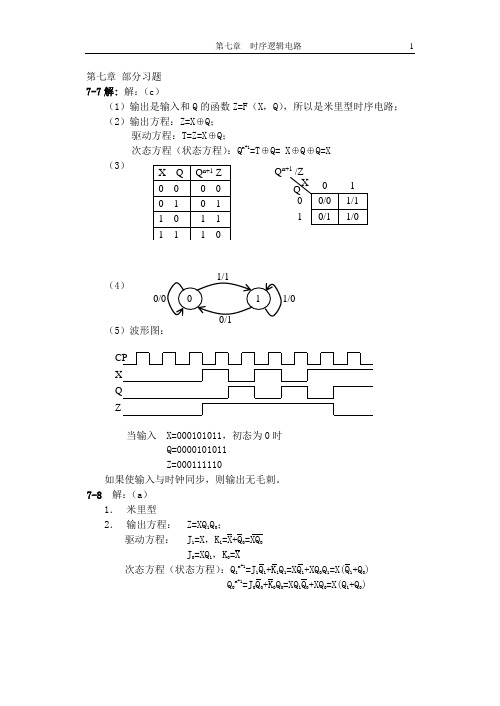

第七章 部分习题 7-7解: 解:(c )(1)输出是输入和Q 的函数Z=F (X ,Q ),所以是米里型时序电路; (2)输出方程:Z=X ⊕Q ;驱动方程:T=Z=X ⊕Q ;次态方程(状态方程):Q n+1=T ⊕Q= X ⊕Q ⊕Q=X(3)(4)(5)波形图:当输入 X=000101011,初态为0时 Q=0000101011 Z=000111110如果使输入与时钟同步,则输出无毛刺。

7-8 解:(a ) 1. 米里型2. 输出方程: Z=XQ 1Q 0;驱动方程: J 1=X ,K 1=X+Q 0=XQ 0J 0=XQ 1,K 0=X次态方程(状态方程):Q 1n+1=J 1Q 1+K 1Q 1=XQ 1+XQ 0Q 1=X(Q 1+Q 0)Q 0n+1=J 0Q 0+K 0Q 0=XQ 1Q 0+XQ 0=X(Q 1+Q 0)Q n+1CP X Q Z3.4.7-12某同步时序电路的逻辑方程如下:驱动方程:nQ X T 01⊕=,n Q X T 10=;输出方程:n Q X Z 1=。

要求: 解:1.同步时序电路的逻辑图示于图,这是米里型的状态机。

2.(a )状态方程: Q 1n+1=T 1⊕Q 1=X ⊕Q 0⊕Q 1Q 0n+1=T 0⊕Q 0=XQ 1⊕Q 0=XQ 1Q 0+XQ 0+Q 1Q 0(b )状态转换表: (c )状态转换图:(Q 1Q 0n+1Q7-15解:(a )“11”检测器,不重叠。

S 0:初始状态,输出0; S 1:输入一个“1”,输出0; S 2:输入两个“1”,输出1;(b ) “101”检测器,可重叠。

S 0:初始状态;S 1:输入序列为“1”;S 2:输入序列为“10”;S 3:输入序列为“101”;(c )(d )略7-34 “011”序列检测器,可重叠。

解:1.采用D(a ) 米里型状态图: S 0:初始状态;S 1:输入序列为“0”; S 2:输入序列为“01”;S 3:输入序列为“011”; (b ) 状态表(两种画法均可):(c ) 状态化简:由观察法知,S 0、S 3等价。

数字电路第7章习题解答

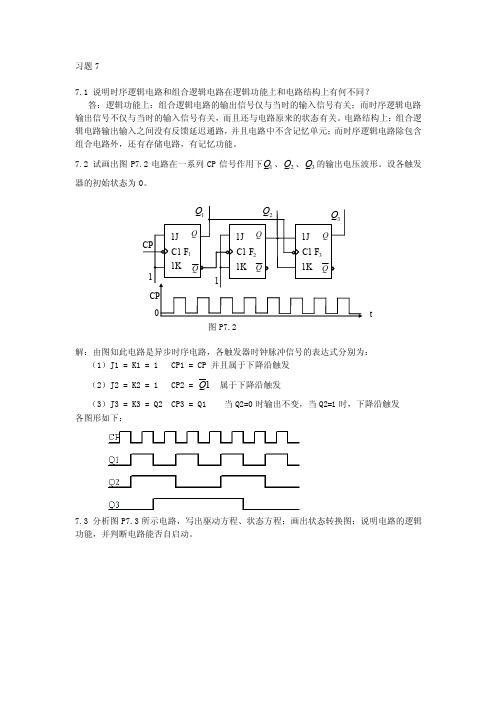

习题77.1 说明时序逻辑电路和组合逻辑电路在逻辑功能上和电路结构上有何不同?答:逻辑功能上:组合逻辑电路的输出信号仅与当时的输入信号有关;而时序逻辑电路输出信号不仅与当时的输入信号有关,而且还与电路原来的状态有关。

电路结构上:组合逻辑电路输出输入之间没有反馈延迟通路,并且电路中不含记忆单元;而时序逻辑电路除包含组合电路外,还有存储电路,有记忆功能。

7.2 试画出图P7.2电路在一系列CP 信号作用下1Q 、2Q 、3Q 的输出电压波形。

设各触发器的初始状态为0。

解:由图知此电路是异步时序电路,各触发器时钟脉冲信号的表达式分别为:(1)J1 = K1 = 1 CP1 = CP 并且属于下降沿触发 (2)J2 = K2 = 1 CP2 = 1Q 属于下降沿触发(3)J3 = K3 = Q2 CP3 = Q1 当Q2=0时输出不变,当Q2=1时,下降沿触发 各图形如下:7.3 分析图P7.3所示电路,写出驱动方程、状态方程;画出状态转换图;说明电路的逻辑功能,并判断电路能否自启动。

图P7.2CP1JC1 F 3 1K 1J C1 F 2 1K 1J C1 F 1 1K 1Q2Q3Q1 QQQ Q QQ1CP 0t解:由电路图可知:该电路是同步时序电路 它的驱动方程为:J0 = 2n Q K0 = 1 J1 = 1n Q K1=1状态方程为: 11n Q + = 2n Q *1nQ 12n Q + = 1nQ*2n Q状态表如下:2n Q 1n Q12n Q + 11n Q +0 0 0 10 1 1 01 0 0 01 1 0 0 由状态表可以得状态转换图如下:由其状态图可知,此电路具有计数功能。

并且可以看出,若此电路由于某种原因进入无效状态时,在CP 脉冲作用后,电路能够回到有效序列,因而具有自启动能力。

7.4 分析图P7.4所示电路,写出各触发器的驱动方程、状态方程;画出状态转换图;当X=1和X=0时,电路分别完成什么逻辑功能?CP11Q2Q图P7.3 1J1K C1 1J C11K Q QQQ00 011110解:由电路图可知,这是一个同步时序电路输出方程: nn n n Q Q X Q XQ Y 0101+= 驱动方程: J0 = K0 = 1 J1 = K1= 0n Q X ⊕状态方程: 10n Q += 0n Q 11n Q += ()01n n Q X Q ⊕⊕11n Q +10n Q + X 0 1 1n Q0n Q0 0 0 1 1 10 1 1 0 0 01 0 1 1 0 1 1 1 0 0 1 0由状态图可以画出其状态表如下图:由状态图可以看出,此电路是一个可控计数器。

数电-第七章-第2部分随机存取存储器(RAM)讲解

信息工程学院 1. RAM存储单元 • 静态SRAM(Static RAM)

Xi (行选择线)

本单元门控制管:控 制触发器与位线的 接通。Xi =1时导通

VDD VGG 存储 单元 T6

来自行地址译码 器的输出

T3 位 线 T5 T1

T4 T2

B

来自列地址译码 器的输出

数 据 线 D

T7

双稳态存储单元 电路

(b)

信息工程学院 3.SRAM的写操作及时序图 写操作时序图

tWC 地址 CE WE tSA 地址有效 tSCE tAW tSD 数据 输入数据有效

tWC 地址 CE WE tSA 数据 tAW tSD 输入数据有效 tHD tHA 地址有效

tHA tHD

信息工程学院

7.2.2 同步静态随机存取存储器(SSRAM)

片 选 无 效

开始 I/O输 I/O输 读A4 出A4 入A5 地址 数据; 数据; 单元 开始 开始 数据 写A5 写A6 数据, 数据

I/O输 出A6 数据; 开始 读A7 数据

ADV=1:丛发模式读写 丛发模式读写模式:在有新地址输入后,自动产生后续地址 进行读写操作,地址总线让出

1 CP CE ADV WE A I/O A1 A2

信息工程学院 32K×8位存储器系统的地址分配表

各 RAM 芯片 Ⅰ

译码器 有效输 出端

扩展的地 址输入端 A14 A13 0 0

8K×8位RAM芯片地址输入端

A12 A11 A10 A9 A8 A7 A6 A5 A4 A3 A2 A1 A0

对应的十 六进制地 址码

0000H 0001H 0002H ┇ 1FFFH 2000H 2001H 2002H ┇ 3FFFH 4000H 400H 4002H ┇ 5FFFH 6000H 6001H 6002H ┇ 7FFFH

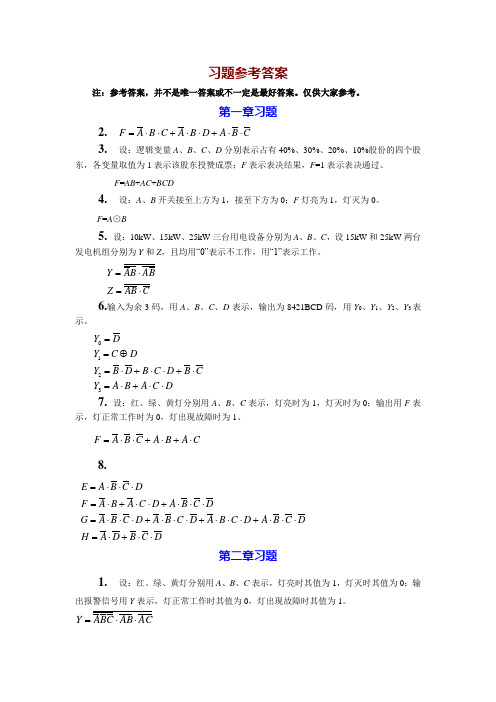

数字电路课后题参考答案

习题参考答案注:参考答案,并不是唯一答案或不一定是最好答案。

仅供大家参考。

第一章习题2. C B A D B A C B A F ⋅⋅+⋅⋅+⋅⋅=3. 设:逻辑变量A 、B 、C 、D 分别表示占有40%、30%、20%、10%股份的四个股东,各变量取值为1表示该股东投赞成票;F 表示表决结果,F =1表示表决通过。

F =AB +AC +BCD4. 设:A 、B 开关接至上方为1,接至下方为0;F 灯亮为1,灯灭为0。

F =A ⊙B5. 设:10kW 、15kW 、25kW 三台用电设备分别为A 、B 、C ,设15kW 和25kW 两台发电机组分别为Y 和Z ,且均用“0”表示不工作,用“1”表示工作。

C AB Z BA B A Y ⋅=⋅=6.输入为余3码,用A 、B 、C 、D 表示,输出为8421BCD 码,用Y 0、Y 1、Y 2、Y 3表示。

D C A B A Y CB DC BD B Y DC Y DY ⋅⋅+⋅=⋅+⋅⋅+⋅=⊕==32107. 设:红、绿、黄灯分别用A 、B 、C 表示,灯亮时为1,灯灭时为0;输出用F 表示,灯正常工作时为0,灯出现故障时为1。

C A B A C B A F ⋅+⋅+⋅⋅=8. D C B D A H DC B AD C B A D C B A D C B A G DC B AD C A B A F DC B A E ⋅⋅+⋅=⋅⋅⋅+⋅⋅⋅+⋅⋅⋅+⋅⋅⋅=⋅⋅⋅+⋅⋅+⋅=⋅⋅⋅=第二章习题1. 设:红、绿、黄灯分别用A 、B 、C 表示,灯亮时其值为1,灯灭时其值为0;输出报警信号用Y 表示,灯正常工作时其值为0,灯出现故障时其值为1。

AC AB C B A Y ⋅⋅=2. 设:烟、温度和有害气体三种不同类型的探测器的输出信号用A 、B 、C 表示,作为报警信号电路的输入,有火灾探测信号时用1表示,没有时用0表示。

报警信号电路的书躇用Y 表示,有报警信号时用1表示,没有时用0表示。

数字电子技术基础课后习题答案第7章习题答案

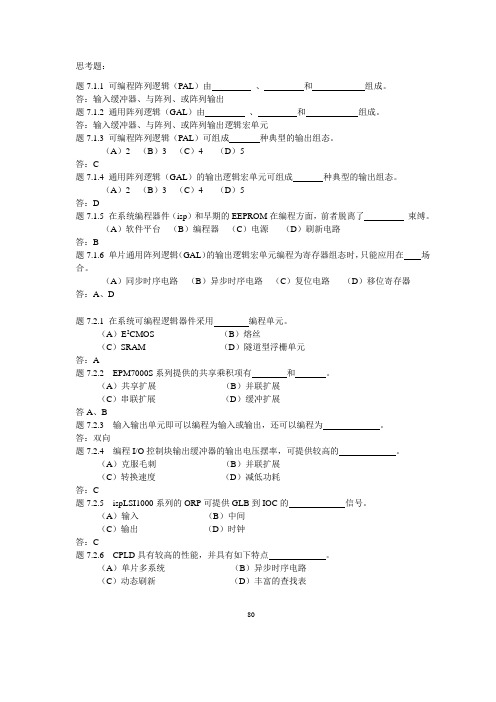

题7.1.1 可编程阵列逻辑(PAL)由、和组成。

答:输入缓冲器、与阵列、或阵列输出题7.1.2 通用阵列逻辑(GAL)由、和组成。

答:输入缓冲器、与阵列、或阵列输出逻辑宏单元题7.1.3 可编程阵列逻辑(PAL)可组成种典型的输出组态。

(A)2 (B)3 (C)4 (D)5答:C题7.1.4 通用阵列逻辑(GAL)的输出逻辑宏单元可组成种典型的输出组态。

(A)2 (B)3 (C)4 (D)5答:D题7.1.5 在系统编程器件(isp)和早期的EEPROM在编程方面,前者脱离了束缚。

(A)软件平台(B)编程器(C)电源(D)刷新电路答:B题7.1.6 单片通用阵列逻辑(GAL)的输出逻辑宏单元编程为寄存器组态时,只能应用在场合。

(A)同步时序电路(B)异步时序电路(C)复位电路(D)移位寄存器答:A、D题7.2.1 在系统可编程逻辑器件采用编程单元。

(A)E2CMOS (B)熔丝(C)SRAM (D)隧道型浮栅单元答:A题7.2.2 EPM7000S系列提供的共享乘积项有和。

(A)共享扩展(B)并联扩展(C)串联扩展(D)缓冲扩展答A、B题7.2.3 输入输出单元即可以编程为输入或输出,还可以编程为。

答:双向题7.2.4 编程I/O控制块输出缓冲器的输出电压摆率,可提供较高的。

(A)克服毛刺(B)并联扩展(C)转换速度(D)减低功耗答:C题7.2.5 ispLSI1000系列的ORP可提供GLB到IOC的信号。

(A)输入(B)中间(C)输出(D)时钟答:C题7.2.6 CPLD具有较高的性能,并具有如下特点。

(A)单片多系统(B)异步时序电路(C)动态刷新(D)丰富的查找表8081题7.3.1 现场可编程门阵列(FPGA )静态时无 ,称之为 。

(A) 功耗 (B) 电流(C) 零功耗器件 (D) 有源器件答:A 、C题7.3.2 CPLD 的信号通路固定,系统速度可以 。

FPGA 的内连线是分布在逻辑单元周围,而且编程的种类和编程点很多,使布线相当灵活,但在系统速度方面低于 。

哈工大数字电子技术第7章习题

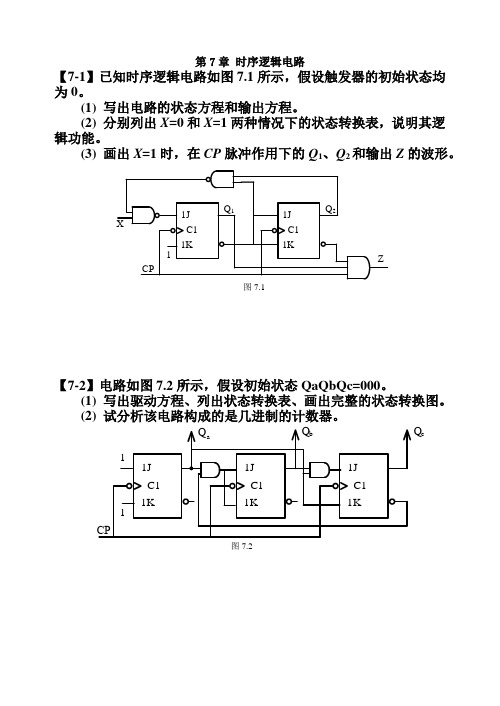

第7章 时序逻辑电路【7-1】已知时序逻辑电路如图7.1所示,假设触发器的初始状态均为0。

(1) 写出电路的状态方程和输出方程。

(2) 分别列出X =0和X =1两种情况下的状态转换表,说明其逻辑功能。

(3) 画出X =1时,在CP 脉冲作用下的Q 1、Q 2和输出Z 的波形。

1J 1KC11J 1KC1Q 1Q 2CPXZ1图7.1【7-2】电路如图7.2所示,假设初始状态QaQbQc=000。

(1) 写出驱动方程、列出状态转换表、画出完整的状态转换图。

(2) 试分析该电路构成的是几进制的计数器。

Q c图7.2【7-3】在二进制异步计数器中,请将正确的进位端或借位端(Q 或Q【7-4】电路如图7.4(a)所示,假设初始状态Q2Q1Q0=000。

1. 试分析由FF1和FF0构成的是几进制计数器;2. 说明整个电路为几进制计数器。

列出状态转换表,画出完整的状态转换图和CP 作用下的波形图。

1J 1KC11J 1KC11J 1KC1CPFF1FF2FF0CPQ 0Q 2Q 1(a) (b)图7.4【7-5】某移位寄存器型计数器的状态转换表如表7.5所示。

请在图7.5中完成该计数器的逻辑图,可以增加必要的门电路。

要求:写出求解步骤、画出完整的状态转换图。

(Q3为高位)图7.5【7-6】在图7.6(a)所示电路中,由D 触发器构成的六位移位寄存器输出Q 6Q 5Q 4Q 3Q 2Q 1的初态为010100,触发器FF 的初态为0,串行输入端D SR =0。

请在图7.6 (b)中画出A 、Q 及B 的波形。

CPCP(a)(b)图7.6【7-7】分析图7.7所示电路,说明它们是多少进制计数器?Q D 74LS161RCO Q C Q B Q A ET EP D C B A CR LDCPCP111(a) (b)图7.7【7-8】分析图7.8所示电路的工作过程1. 画出对应CP 的输出Q a Q d Q c Q b 的波形和状态转换图(采用二进制码的形式、 Q a 为高位)。

第七章触发器及时序电路

第七章触发器及时序电路第一节RS触发器一、填空题1触发器具有_______ 个稳定状态,在输入信号消失后,它能保持 __________ 不变。

2、“与非”门构成的基本RS触发器,输入端是 ____________ 和_____________ ;输出端是 _____________ 和_____________________ ,将 _____________ 称为触发器的0状态,称为触发器的1状态。

3、“与非”门构成的基本RS触发器R D =1,S D =0时,其输出状态为 ____ 。

4、触发器电路中,R D端、S D端可以根据需要预先将触发器____________ 或_______ ,而不受的同步控制。

5、同步RS 触发器状态的_________ 与___________ 同步。

二、判断题(正确的在括号中打“,错误的打“X” ))1、触发器只需具备两个稳态功能,不必具有记忆功能。

2、基本RS触发器要受时钟的控制。

3、Q n+1表示触发器原来所处的状态,即现态。

4、当CP处于下降沿时,触发器的状态一定发生翻转。

二、绘图题1、设“与非”门组成的基本RS触发器的输入信号波形如图所示,试在输入波形下方画出Q和Q端的信号波形。

R ----- ----------------------QQ2、已知同步RS触发器的S、R、CP脉冲波形如图所示。

试在它们下方画出Q端的信号波形(设触发器的初始状态为0)R -------------- ---------Q第二节JK触发器一、填空题1、在时钟脉冲的控制下,JK触发器根据输入信号J、K的不同情况,具有______、、和功能。

2、在时钟脉冲下,JK触发器输入端J = 0、K = 0时,触发器状态为_________ ; J= 0、K = 1时,触发器状态为 ________ ; J= 1、K = 0时,触发器状态为_______ ;J= 1、K = 1时,触发器状态随CP脉冲的到来而。

数电第七章答案

数电第七章答案7.2解:激励⽅程:211Q Q D ?'=,X Q D +'=22输出⽅程:21'?=Q Q Z 激励/转移表如下:21Q QX0 100 01 10 11 01 10 01 0001 11 01 01)21(21''Q Q D D状态输出表如下:S X Z 0 1A B C DB BCD B B A B0 0 1 0S '⼆者不是对偶关系,因为保存状态的触发器并没有对偶变换,对偶的概念并不适合于状态表。

7.4解:激励⽅程:激励/转移表为:采⽤题中要求的转态命名,状态表为:7.5解:由图形可知1Q =X'3*2*Q Y X Q += '3''*3**Q X Y X Q += 激励/转移表、状态/输出表如下:0 0 0 110 110 011 011 A G G D D 0 0 1 110 110 011 011 B G G D D 0 1 0 110 110 011 011 C G G D D 0 1 1 110 110 011 011 D G G D D 1 0 0 000 100 001 011 E A E B D 1 0 1 000 100 001 011 F A EB D 1 1 0 000 100 001 011 G A E B D 1 1 1 100 100 001 011 H A E B D7.6解:由图⾏可知激励⽅程:1''1*1**Q Y Q Y Q +=2'1''21''2*)**(***Q Q Y X Q Q Y X Q += '2'*Q X Z =激励/转移表、状态/输出表如下:0 0 00,1 01,1 00,0 01,0 A A,1 B,1 A,0 B,0 0 1 01,1 10,1 01,0 00,0 B B,1 C,1 B,0 A,0 1 0 10,0 11,0 10,0 11,0 C C,0 D,0 C,0 D,0 1 1 11,0 00,0 11,0 10,0 D D,0 A,0 D,0 C,07.7 This can be algebraically.If all of the input combinations are covered,the logical sum of the expressions on all the transitions leaving state must be 1.If the sum is not 1,it is 0 for all input combinations that are uncovered.For double-covered input combinations,we look at all possible pairs of transitions leaving a state.The product of a pair of transition equations is 1 for any double-covered input combinations.这部分可以由代数来完成,如果所有的输⼊组合被覆盖,在所有的转换过程中其余的状态的表达式的逻辑和必须为1。

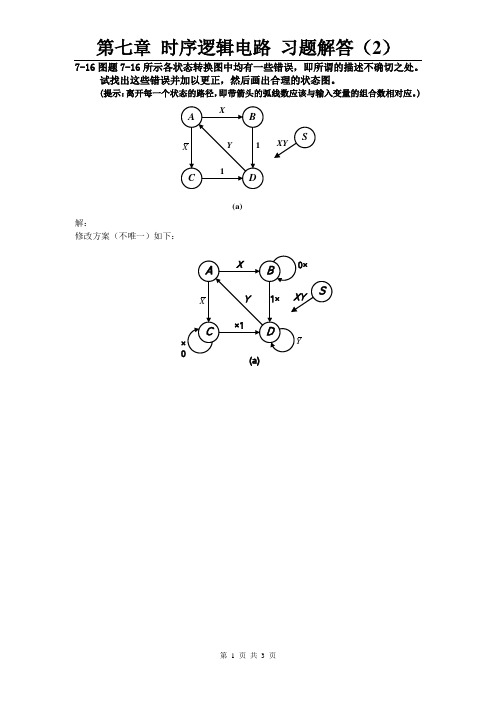

《数字电路-分析与设计》第七章习题及解答(部分4) 北京理工大学出版社

7-16图题7-16所示各状态转换图中均有一些错误,即所谓的描述不确切之处。

试找出这些错误并加以更正,然后画出合理的状态图。

(提示:离开每一个状态的路径,即带箭头的弧线数应该与输入变量的组合数相对应。

)

(a)

解:

修改方案(不唯一)如下:

(a)×

7-19找出表题7-19所描述的同步时序电路的最简状态转换表。

(a )用观察法;

(b )用隐含表法。

解:

(a)观察法:

S 1与S 4等价,S 0与S 3等价。

将状态表简化如下:

(a)隐含表法:

由隐含表看出,S 1、S 4状态对与S 0、S 3状态对互以对方的等价为前提,所以S 1与S 4等价,S 0与S 3等价。

S /Z

表题7-19简化状态转换表 S /Z S 1

S 2S 3S 4 S 0 S 1 S 2 S 3 题7-19隐含表化简

7-23用隐含表法简化表题7-23所示状态转换表的状态数量。

解:

隐含表如下:

由隐含表看出,S 1、S 2状态对与S 0、S 3状态对互以对方的等价为前提,所以S 1与S 2等价,S 0与S 3等价。

简化状态表如下:

S /Z S 1S 2S 3S 4

S 0 S 1 S 2 S 3 题7-23隐含表化简

表题7-23 简化状态转换表 S /Z。

数字电路习题-第七章

第七章 D/A转换器和A/D转换器A/D转换器和D/A转换器是反馈控制系统中,不可缺少的集成电路器件,它在系统中起着“数字至模拟”或“模拟至数字”的桥梁性作用。

本章要求学生理解D/A转换器和A/D转换器的工作原理,掌握他们的主要性能指标和使用方法。

第一节 基本知识、重点与难点一、基本知识(一)D/A转换器和A/D转换器的基本原理D/A转换器和A/D转换器的主要技术参数有转换速度、转换精度、抗干扰能力等。

在选用D/A转换器和A/D转换器时,一般根据这几个性能指标综合考虑。

分辨率和转换误差影响D/A转换器的精度,转换时间影响转换器的转换速度。

A/D转换器是将模拟量转换成数字量,转换过程包括采样、保持、量化和编码4个步骤。

D/A转换器是将数字量转换成模拟量,它通过电阻网络、模拟开关和运算放大器将数字量转换成电流,再用加法器将各有效支路电流相加并转换成电压。

(二)D/A转换器1.权电阻网络权电阻网络由一组电阻组成,其中每个权电阻的阻值与该电阻所对应的权位成反比。

使流过每个接到基准电源U REF上电阻的电流和对应的权值成正比。

权电阻网络D/A转换器的优点是电路结构简单,所用元器件数量较少。

但当二进制数位较多时,权电阻值种类多,且阻值分散,使得转换精度较低。

2.R-2R网络R-2R网络D/A转换器中各支路的电流直接流入运算放大器的反相端,它们之间不存在传输误差,因而提高了转换速度,减小了动态过程中在输出端可能出现的尖峰脉冲。

由于只采用了R和2R两种阻值,因此能比较容易保证电阻网络的精度,也容易集成化。

3.集成D/A转换器目前市场集成D/A转换器的芯片种类较多,可根据电路系统要求的技术参数,参考数据手册,综合考虑选用集成D/A转换器。

(三)A/D转换器1.并行比较型A/D转换器并行比较型A/D转换器是高速A/D转换器,其转换不需要反复,在所有种类A/D转换器中转换速度最快。

然而这种A/D转换器的缺点是分辨率低,比较器的数量也随着数字量的增加而增加。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

第七章 D/A转换器和A/D转换器A/D转换器和D/A转换器是反馈控制系统中,不可缺少的集成电路器件,它在系统中起着“数字至模拟”或“模拟至数字”的桥梁性作用。

本章要求学生理解D/A转换器和A/D转换器的工作原理,掌握他们的主要性能指标和使用方法。

第一节 基本知识、重点与难点一、基本知识(一)D/A转换器和A/D转换器的基本原理D/A转换器和A/D转换器的主要技术参数有转换速度、转换精度、抗干扰能力等。

在选用D/A转换器和A/D转换器时,一般根据这几个性能指标综合考虑。

分辨率和转换误差影响D/A转换器的精度,转换时间影响转换器的转换速度。

A/D转换器是将模拟量转换成数字量,转换过程包括采样、保持、量化和编码4个步骤。

D/A转换器是将数字量转换成模拟量,它通过电阻网络、模拟开关和运算放大器将数字量转换成电流,再用加法器将各有效支路电流相加并转换成电压。

(二)D/A转换器1.权电阻网络权电阻网络由一组电阻组成,其中每个权电阻的阻值与该电阻所对应的权位成反比。

使流过每个接到基准电源U REF上电阻的电流和对应的权值成正比。

权电阻网络D/A转换器的优点是电路结构简单,所用元器件数量较少。

但当二进制数位较多时,权电阻值种类多,且阻值分散,使得转换精度较低。

2.R-2R网络R-2R网络D/A转换器中各支路的电流直接流入运算放大器的反相端,它们之间不存在传输误差,因而提高了转换速度,减小了动态过程中在输出端可能出现的尖峰脉冲。

由于只采用了R和2R两种阻值,因此能比较容易保证电阻网络的精度,也容易集成化。

3.集成D/A转换器目前市场集成D/A转换器的芯片种类较多,可根据电路系统要求的技术参数,参考数据手册,综合考虑选用集成D/A转换器。

(三)A/D转换器1.并行比较型A/D转换器并行比较型A/D转换器是高速A/D转换器,其转换不需要反复,在所有种类A/D转换器中转换速度最快。

然而这种A/D转换器的缺点是分辨率低,比较器的数量也随着数字量的增加而增加。

因此,并行比较型A/D转换器一般用在转换速度快而精度要求不高的场合。

2.串行比较型A/D转换器串行比较型A/D转换将模拟信号依时间顺序通过一连串的比较器,后面比较器的输入信号反映了前面比较器的剩余。

由于后一位的比较需要使用前一位的结果,所以这种转换器的转换速率不可能做得很高。

但相同分辨率的A/D转换器,串行比较法较并行比较法少用了大量的比较器。

3.逐次比较型A/D转换器逐次比较型A/D转换器首先从高位进行比较,直到最低位。

进行转换的至少需要几个周期,数字量的位数越多,转换的时间越长。

其转换速度较并行比较型A/D转换器低,属于中型A/D转换器。

逐次比较型A/D转换器只采用了一个比较器,当位数较多时,具有很明显的价值,因而是目前应用较多的一种A/D转换器。

它的主要特点是电路简单,速度、精度都较高。

4.双积分型A/D转换器双积分型A/D转换器就是先把电压转换成中间量—时间,再将时间转换为数字,这种转换方法属于间接转换。

由于采用了以输入信号为被积函数进行积分的方式,积分电路响应是输入信号的平均值,所以它具有较强的抗脉冲干扰能力。

另外,在两次积分内,只要RC元件参数不发生瞬时改变,转换结果就与RC值无关,因此它对元件的稳定性要求不高。

但也正是由于积分,转换时间相对就要长些,而且第二次积分时间还不能固定,故此方法只能用于低速场合。

5.集成A/D转换器及其应用根据A/D转换器在系统中的作用以及与系统中其他电路的关系,可依据转换速率、精度和功能来选用合适的A/D转换器,这样可以减少电路连接中的辅助环节,还可以避免出现一些不易发现的逻辑与时序错误。

二、重点与难点重点:1.理解A/D转换器和D/A转换器的主要技术指标;2.熟练掌握各种A/D转换器和D/A转换器工作原理;3.集成A/D转换器和集成D/A转换器的应用。

难点:1.A/D转换器和D/A转换器的主要技术指标;2.集成A/D转换器、集成D/A转换器和中规模组合、时序电路的综合应用。

三、考核题型与考核重点1.概念与简答题型为填空、判断和选择;分配的分数为2~4分。

2.综合与设计题型1为A/D转换器和D/A转换器工作原理分析题型;题型2为集成A/D转换器、集成D/A转换器和中规模组合、时序电路的综合分析、设计应用题型。

分配的分数为8~16分。

第二节典型题解例题7.1 某一D/A转换器电路如例题7.1图(a)所示,图中74290输出端Q i=1时,相应的模拟开关S i在位置1;Q i=0时,相应的模拟开关S i在位置0。

请解答如下问题。

(1) 该电路是哪一种D/A 转换器? (2) 求u O 与数字量Q 3Q 2Q 1Q 0之间的关系式。

(3) 若U REF =1V ,求Q 3Q 2Q 1Q 0=0001和0101时的u O 值。

(4) 画出计数器输入连续计数脉冲CP 时的u O 波形,设计数器的初态为0。

解:(1)观察例题7.1图(a ),74290计数器是按8421BCD 码计数的方式连接,所以计数状态是10个,从0000~1001。

而图的右半部分是一个权电组D/A 转换器。

(2)u O =-U REF (23Q 3+22Q 2+21Q 1+20Q 0)(3)当U REF =1V ,Q 3Q 2Q 1Q 0=0001时,u O =-1V ;Q 3Q 2Q 1Q 0=0101时,u O =-5V 。

(4)输入连续计数脉冲CP 时,u O 为一阶梯波形,其波形如例题7.1图(b )所示。

(a )O(b )CPO tu O Ot-8V -6V -4V -2V例题7.1图例题7.2 例题7.2图(a )所示电路是10位D/A 转换器CB7520和4位右移移位寄存器74195组成的波形发生器电路。

已知CB7520的U REF =-10V ,试画出输出电压u O 的波形,并标出波形图上各点电压的幅度。

解:4位右移移位寄存器74195工作在扭循环状态,共有8个状态,在时钟信号CP 连续作用下,Q 3Q 2Q 1Q 0依此以此状态为0000、0001、0011、0111、1111、1110、1100、1000、0000…不断循环。

因此D 9D 8D 7D 6也按此8个状态不断循环。

D 9、D 8、D 7、D 6为1时在输出图(b )所示。

u O例题7.3 例题7.3图所示电路是一种A/D转换器简略框图,且串行输出数字信号,试分析其工作原理,并说明该A/D转换器的优缺点。

u ICPCP例题7.3图解:(1) 例题7.3图虚线框中所示电路在转换开始之前,u C为低电平0,计数器无CP A/D 脉冲,不计数,计数器的初始状态为0,DAC的输出电压u O=0V,最右侧的并行数字输出也为0。

当u C为高电平1时,如果模拟输入电压u I>0V,则u B为高电平1,与门开启,计数器开始计数,DAC的输出电压开始升高;只要u O<u I,此计数过程就一直继续下去,直到u O≥u I,u B=0,与门关闭,计数器停止计数。

此时的并行数字输出即为A/D转换的结果。

(2) 74161的输出端接到或非门的输入端,或非门的输出信号控制A/D转换器是否转换。

当74161的输出全为低电平时,或非门的输出为高电平,使u C为高电平,控制A/D转换器开始工作,并使输出寄存器禁止输出。

当74161的输出不全为低电平时,或非门的输出为低电平,使u C为低电平,控制A/D转换器不能转换,并使输出寄存器使能。

此时数据选择器将输入端的数据串行送到输出。

(3) 要求A/D转换器的转换时间要快,即并转串电路脉冲CP使74161的输出为0000时,使u C为高电平,A/D转换器输入脉冲频率CP A/D就得使转换完毕。

因此A/D转换器输入脉冲频率CP A/D大于或远大于并转串电路的频率CP。

(4) 当转换一个模拟量时,最低位地址0000时的数据移到串行数据输出的最后一位,即输出的顺序是1、2、…最高位、0。

(5) 此电路的优点是构思简单,缺点是速度较慢。

例题7.4 试将一个0V~5V的模拟电压信号转换成8位数字信号,并将其先低位后高位串行输出。

若先高位后低位串行输出,如何修改电路?若将8位数字输出修改为10位数字输出,如何修改电路?S例题7.4图解:0V~5V的模拟电压转换成8位数字信号电路图如例题7.4图所示。

电路构成如下:(1) 用8位ADC芯片ADC0809将模拟电压转换成8位数字信号。

1)ADC0809的电源电压U DD、参考电压U REF(+)和OE端(允许输出)都接+5V,而U REF(-)、GND接地。

2)模拟输入信号接ADC0809的8个输入端IN7~IN0中的任一通道。

如IN0,并设定相应的通道地址ABC=000。

3)A/D转换时钟CP A/D(1MHz)接ADC0809的CLK端,A/D转换启动信号START和通道地址锁存信号ALE并接,用计数芯片74161的低3位Q2Q1Q0控制,当计数到000时或非门输出高电平,A/D变换开始,约10us转换结束,转换结果由D7~D0端并行输出。

(2)用8选1数据选择器将ADC0809并行送出的数字信号变为串行输出。

1)选用8选1数据选择器74151,ADC0809的D0~D7端分别接74151的0~7端,以便先低位后高位顺序输出。

2)74151的地址信号A2A1A0用74161的低3位Q2Q1Q0控制,随着脉冲CP的不断输入,74151将依此送出ADC0809输出的数字信号。

(3)将输出转换为串行脉冲码。

ADC0809从START的正边沿(CP的正边沿)开始转换,10us内转换结束。

74151也从START的正边沿开始选择输出,所以为防止10us转换期间内码位交错,将输出转换为脉冲码输出。

用74151的输出Y同CP(即CP的后半周期)经过与非门获得脉冲码输出S。

(4)若先高位后低位串行输出,将ADC0809的D0~D7端接到的74151的0~7端改为ADC0809的D7~D0端分别接到74151的0~7端即可。

(5) 若将8为数字输出修改为10位数字输出,可做如下修改:1)可将74161换为74290。

74290接成8421BCD码输出,且4个输出接到4输入或非门的4个输入端。

2)将8位ADC0809换成10位ADC电路。

3)将8选1数据选择器换成16选1数据选择器,其地址信号A3A2A1A0用74290的4位输出来控制。

第三节题解自我检测题解题7.1答:在D/A转换中,量化单位是指输入数字的一个最低有效位(Least Significant Bit,LSB)所对应的模拟量。

题7.2答:双积分式A/D转换器对RC元件的稳定性要求不高。

题7.3答:由于 A ,所以数字系统的精度较高。