MOS管封装

MOS管封装分析报告

MOS管封装分析报告(含主流厂商封装)在完成MOS管芯片在制作之后,需要给MOS管芯片加上一个外壳,这就是MOS管封装。

该封装外壳主要起着支撑、保护和冷却的作用,同时还可为芯片提供电气连接和隔离,从而将MOS管器件与其它元件构成完整的电路。

而不同的封装、不同的设计,MOS管的规格尺寸、各类电性参数等都会不一样,而它们在电路中所能起到的作用也会不一样;另外,封装还是电路设计中MOS管选择的重要参考。

封装的重要性不言而喻。

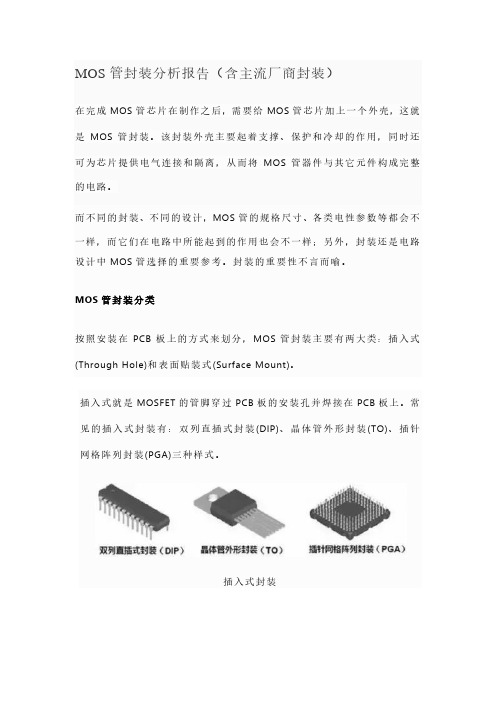

MOS管封装分类按照安装在PCB板上的方式来划分,MOS管封装主要有两大类:插入式(Through Hole)和表面贴装式(Surface Mount)。

插入式就是MOSFET的管脚穿过PCB板的安装孔并焊接在PCB板上。

常见的插入式封装有:双列直插式封装(DIP)、晶体管外形封装(TO)、插针网格阵列封装(PGA)三种样式。

插入式封装表面贴裝则是MOSFET的管脚及散热法兰焊接在PCB板表面的焊盘上。

典型表面贴装式封装有:晶体管外形(D-PAK)、小外形晶体管(SOT)、小外形封装(SOP)、方形扁平式封装(QFP)、塑封有引线芯片载体(PLCC)等。

表面贴装式封装随着技术的发展,目前主板、显卡等的PCB板采用直插式封装方式的越来越少,更多地选用了表面贴装式封装方式。

1、双列直插式封装(DIP)DIP封装有两排引脚,需要插入到具有DIP结构的芯片插座上,其派生方式为SDIP(Shrink DIP),即紧缩双入线封装,较DIP的针脚密度高6倍。

DIP封装结构形式有:多层陶瓷双列直插式DIP、单层陶瓷双列直插式DIP、引线框架式DIP(含玻璃陶瓷封接式、塑料包封结构式、陶瓷低熔玻璃封装式)等。

DIP封装的特点是可以很方便地实现PCB板的穿孔焊接,和主板有很好的兼容性。

但由于其封装面积和厚度都比较大,而且引脚在插拔过程中很容易被损坏,可靠性较差;同时由于受工艺的影响,引脚一般都不超过100个,因此在电子产业高度集成化过程中,DIP封装逐渐退出了历史舞台。

mosfet的封装流程

mosfet的封装流程MOSFET(金属氧化物半导体场效应晶体管)是一种常用的功率开关器件,广泛应用于电子电路中。

在MOSFET的生产过程中,封装是十分重要的一环。

封装是将芯片与外部环境隔离,并提供电气连接和机械支持的过程。

本文将介绍MOSFET的封装流程。

MOSFET的封装流程通常包括以下几个步骤:准备基材、制造封装、封装测试和质量控制。

首先是准备基材。

在封装流程开始之前,需要准备好基材,通常是由硅片制成的晶圆。

晶圆经过一系列的工艺步骤,如清洗、去除杂质和涂覆薄膜等,以确保其表面的平整度和纯度。

接下来是制造封装。

制造封装的第一步是将晶圆锯成小片,每个小片上都会有一个MOSFET芯片。

然后,这些芯片会通过一系列的工艺步骤,如金属化、蚀刻、光刻和沉积等,来形成MOSFET的结构。

这些工艺步骤的目的是在芯片上形成源极、漏极和栅极等电极,以及与之相连的金属线路。

完成芯片结构后,接下来是封装测试。

在封装测试中,会对芯片进行一系列的电性能测试,以确保其工作正常。

这些测试包括电流-电压特性测试、开关速度测试和温度特性测试等。

通过这些测试,可以评估MOSFET的性能是否符合要求。

最后是质量控制。

在封装流程的最后阶段,会对已经封装好的MOSFET进行质量控制。

质量控制的目的是检查封装过程中是否存在任何缺陷,如焊接问题、封装材料的质量等。

只有通过了质量控制的MOSFET才能出厂销售。

总结一下,MOSFET的封装流程包括准备基材、制造封装、封装测试和质量控制。

这个流程确保了MOSFET的性能和质量符合要求。

在封装过程中,需要经过多个工艺步骤,如金属化、蚀刻、光刻和沉积等,以形成MOSFET的结构。

而封装测试和质量控制则是对MOSFET进行电性能测试和质量检查,以确保其工作正常。

通过这些步骤,可以生产出高质量的MOSFET,满足各种电子电路的需求。

mos管封装类型

mos管封装类型MOS管封装(Metal-OxideSemiconductor)是一种常见的集成电路封装,它由多层金属薄膜和夹紧材料组成,通常用于集成电路芯片以及磁性头印刷电路板(PCB)上的元件、部件和其他元件的封装。

封装的主要功能是使电路板上的元件可靠地与外部电路连接,并且结构上做到密封和降低散热发热量。

MOS管封装类型有很多种,它们的形状大小正方形、圆形和多边形,像普通的条形芯片封装一样,可以根据用户的需求进行定制。

MOS 封装类型最常用的部分包括:1. TO-92(三脚插件):采用单一的外部封装,由一个半圆型的框、三个螺纹芯和一个型号定义的热焊接销组成,用于引出元件的脚。

2. TO-220(四脚插件):标准封装,主要用于高功率、高热量保护元件。

它由一个椭圆形框、两个螺纹芯和两个焊接螺丝组成,设计用于引出元件的四个腿。

3. DIP(双列插件):具有较低的均匀度,以及可以容纳电极管或其他封装类型的不同组件,是最常用的组件封装产品。

它由垂直双列引线,金属支架和型号定义的焊接钉组成,可供引出数字IC的脚位。

4. SOT-23(双列型):双列型封装,3脚和5脚型,结构紧凑,空间小,提供一个紧凑而密封的方案,有助于降低功耗,而且可以采用多种技术来封装多达8个引脚。

5. SMD(小型管件):表面贴装的封装,包括全封装、框架和附件等,适用于普通的表面贴装元件,它们的外形要求较为严格,可以进行更大规模的封装。

MOS管封装的优势在于其表面贴装的技术,能够实现紧凑的外形、高密度的封装,并可以采用机械装配以及自动安装,这有助于降低产品生产成本,提高生产效率,并且它们可以通过良好的电气特性,实现自动测试和自动贴装,更好地提高了制造质量和可靠性。

此外,MOS管封装与其他封装相比,还具有其他优点,例如具有较高的热稳定性,可以有效降低因应用程序的温度变化而导致的失效,而且可以使用金属支架有效减少封装温度和震动的影响,从而比其他封装类型更加高效地传输热量。

MOS管的封装类型分享

MOS管的封装类型分享

MOS管的封装类型,常常影响着电路的设计方向,甚至是产品性能走向;但面对形色各异的封装,我们该如何辨别?主流企业的封装又有什么特点?

在完成MOS管芯片在制作之后,需要给MOS管芯片加上一个外壳,这就是MOS管封装。

该封装外壳主要起着支撑、保护和冷却的作用,同时还可为芯片提供电气连接和隔离,从而将MOS管器件与其它元件构成完整的电路。

而不同的封装、不同的设计,MOS管的规格尺寸、各类电性参数等都会不一样,而它们在电路中所能起到的作用也会不一样;另外,封装还是电路设计中MOS管选择的重要参考。

封装的重要性不言而喻,今天我们就来聊聊MOS管封装的那些事。

MOS管封装分类

按照安装在PCB板上的方式来划分,MOS管封装主要有两大类:插入式(Through Hole)和表面贴装式(Surface Mount)。

插入式就是MOSFET的管脚穿过PCB板的安装孔并焊接在PCB板上。

常见的插入式封装有:双列直插式封装(DIP)、晶体管外形封装(TO)、插针网格阵列封装(PGA)三种样式。

插入式封装

表面贴裝则是MOSFET的管脚及散热法兰焊接在PCB板表面的焊盘上。

典型表面贴装式封装有:晶体管外形(D-PAK)、小外形晶体管(SOT)、小外形封装(SOP)、方形扁平式封装(QFP)、塑封有引线芯片载体(PLCC)等。

表面贴装式封装

随着技术的发展,目前主板、显卡等的PCB板采用直插式封装方式的越来越少,更多地选用了表面贴装式封装方式。

1、双列直插式封装(DIP)。

mosfet的封装流程

mosfet的封装流程MOSFET(金属-氧化物-半导体场效应晶体管)是一种主要用于电子设备的半导体器件。

它可以在低频和高频应用中控制电压和电流,同时也具有高度的可靠性和稳定性。

封装流程是将MOSFET芯片封装到外壳中的过程,本文将详细介绍MOSFET封装的流程。

第一步:芯片设计MOSFET芯片的设计是封装流程的起点。

在这个阶段,芯片设计师根据特定的应用需求,使用CAD软件设计出晶体管的晶片结构、电路连接、金属层和其他重要元件。

设计完成后,芯片的原型将通过多次验证和优化,确保其性能达到预期。

第二步:切割划分在芯片制造的过程中,多个MOSFET被同时加工在一块硅片上。

在封装流程中的第一步是将硅片切割成单个芯片。

通过切割划分可以分离出单个晶体管芯片,以便后续的工艺步骤。

第三步:清洗和制备划分得到的芯片需要进行清洗和制备,以去除可能存在的污染物和杂质。

一般来说,芯片会先进行机械清洗来去除表面的尘土和杂质,然后再进行化学清洗以去除更加顽固的污染物。

制备涉及到芯片表面的涂覆和处理,以便在后续步骤中使其更加适合封装。

第四步:引线焊接一旦芯片清洗和制备完毕,就可以进行引线焊接。

这一步是将芯片上的金属连接到引线上的关键步骤。

通常,在芯片的金属电极上加压形成连接。

第五步:封装引线焊接完成后,芯片需要被封装在外壳之中。

封装是将芯片保护在一个可靠且耐用的外壳中,以防止机械损坏和环境污染。

封装的过程通常涉及到预先设计的外壳底部,将引线和芯片放入外壳内部,然后封装上部分,使引线和芯片稳固地固定在外壳中。

第六步:测试和质量控制一旦完成封装,封装的MOSFET将会被送往测试和质量控制部门进行测试。

测试的目的是确保芯片在封装过程中没有受到损坏,并且在运行时能够按照预定的标准工作。

此外,还会检查芯片的功耗、速度、温度特性等重要参数,以保证其质量和性能稳定。

第七步:包装和出货经过测试和质量检查后,封装的MOSFET将会进行最终的包装和出货。

MOS管(金属氧化物半导体场效应管)的封装结构

MOS管(金属氧化物半导体场效应管)的封装结构MOS管(金属氧化物半导体场效应管,Metal Oxide Semiconductor Field Effect Transistor)的封装结构一般采用以下几种形式:

1.TO封装(Tin-Can Outline Package):这是一种传统的封装形

式,外观类似金属罐。

TO封装通常具有3个引脚,通过引脚与电路进行连接。

MOS管内部的芯片被放置在金属罐体内,并通过引脚与外部电路连接。

2.DIP封装(Dual Inline Package):DIP封装是一种常见的直插

式封装形式。

它通常包含了两排引脚,引脚与MOS管内部芯片相连。

DIP封装的主要优点是容易安装和替换。

3.SMD封装(Surface Mount Device Package):SMD封装是一

种表面贴装封装形式,常用于表面贴装技术(SMT)的电子设备制造中。

SMD封装通常具有平面外形,方便在PCB (Printed Circuit Board)上进行组装。

常见的SMD封装类型包括SOIC、QFN和QFP等。

4.Power Package(功率封装):功率MOS管通常需要具备较大

的功率承受能力和散热性能,因此采用特殊的功率封装结构。

常见的功率封装形式包括TO-220、TO-247和D2PAK等,具有较大的引脚和散热片。

mosfet封装工艺流程(一)

mosfet封装工艺流程(一)MOSFET封装工艺介绍MOSFET(金属氧化物半导体场效应晶体管)是一种重要的电子元件,广泛应用于各种电路中。

在生产中,封装工艺起到将MOSFET芯片封装成实际可用的器件的作用。

本文将介绍MOSFET封装工艺的各个流程。

1. 设计封装参数在MOSFET封装工艺中,首先需要进行封装参数的设计。

这包括选择适当的封装类型和尺寸,确定引脚排列和材料选择等。

封装参数的设计决定了器件的外观、性能和可靠性。

2. 器件封装在器件封装过程中,首先将MOSFET芯片粘连到封装基底上。

然后,使用焊接技术将芯片与引脚连接起来,以实现电气连接和机械强度。

这一步骤通常使用焊线或球(Wire Bonding or Ball Bonding)技术完成。

3. 导电胶连接导电胶连接是封装工艺中的关键步骤之一。

通过将导电胶覆盖在芯片和引脚之间,实现芯片与引脚之间的电气连接。

导电胶连接要求精准的控制和高品质的材料,以确保良好的电气性能和可靠性。

4. 封装密封封装密封是为了保护MOSFET芯片和引脚不受环境中的尘埃、湿气等污染物的侵害,提高器件的可靠性。

封装密封的常用材料包括环氧树脂、硅胶等。

5. 引脚整形引脚整形是将封装好的MOSFET器件的引脚进行整形和修剪,以满足各种应用的需求。

引脚整形可通过机械方式(例如剪切),也可通过热力方式(例如焊接)完成。

6. 器件测试最后,进行器件测试以确保封装完好的MOSFET器件的性能符合设计要求。

器件测试包括电性能测试、可靠性测试等,以验证封装质量和器件性能,为产品交付客户前的出货前测试。

结论MOSFET封装工艺是将MOSFET芯片封装成实际可用器件的关键步骤。

通过设计封装参数、实施器件封装、导电胶连接、封装密封、引脚整形和器件测试等流程,可以确保封装好的MOSFET器件具有良好的性能和可靠性,满足各种应用的需求。

以上是MOSFET封装工艺的详细流程介绍,希望本文能对读者对MOSFET封装工艺有所了解和认识。

mos管封装结构

mos管封装结构

MOS管(Metal-Oxide-Semiconductor Transistor)的封装结构可以分为以下几种:

1. DIP封装(Dual In-line Package):是最早使用的封装结构之一,通过在芯片两侧引出引脚,并在两侧焊接封装外壳来实现封装。

DIP封装常见于较早期的芯片,如74系列逻辑芯片。

2. TO封装(Transistor Outline):TO封装是一种带有金属外壳和引脚的封装形式,适用于功率较大的MOS管。

TO封装通过外壳的金属引脚将芯片内部的引脚引出,并通过螺旋和紧固装置将外壳紧固在散热器上,以便散热。

3. SMD封装(Surface Mount Device):SMD封装是一种表面贴装封装形式,适用于高集成度和小尺寸的MOS管。

SMD封装通过在芯片的底部引出金属焊盘,使芯片可以直接焊接在PCB上,而无需外部引脚。

常见的SMD封装包括SOT (Small-Outline Transistor)、SOT-23、SOT-89等。

4. BGA封装(Ball Grid Array):BGA封装是一种高密度封装形式,适用于需要更多引脚和更高集成度的MOS管。

BGA封装通过在芯片的底部引出多个金属球,这些金属球与PCB上的焊盘相连接,以实现连接。

BGA封装具有更好的散热性能和更高的可靠性,但制造和维修难度较大。

这些封装结构可以根据应用需求和芯片特性进行选择。

同时,随着技术的不断发展,新型的封装结构也在不断涌现,以满足不同的应用需求。

mos管封装结构

mos管封装结构摘要:1.MOS 管的概述2.MOS 管的封装结构分类3.常见MOS 管封装结构的特点及应用4.MOS 管封装结构的发展趋势正文:一、MOS 管的概述MOS 管,全称为金属- 氧化物- 半导体场效应晶体管(Metal-Oxide-Semiconductor Field Effect Transistor),是一种广泛应用于现代电子设备的半导体器件。

它依据半导体材料的导电特性,利用栅极电压的变化来控制源漏极之间的电流,具有高输入阻抗、低噪声和低功耗等特点。

二、MOS 管的封装结构分类根据封装形式和材料,MOS 管的封装结构可分为以下几类:1.塑料封装:采用塑料材料作为封装外壳,具有成本低、工艺简单等优点,但散热性能相对较差,适用于低功率MOS 管。

2.金属封装:采用金属材料作为封装外壳,具有良好的散热性能和高频特性,适用于高功率和超高频MOS 管。

3.陶瓷封装:采用陶瓷材料作为封装外壳,具有较高的散热性能和良好的密封性,适用于高功率MOS 管。

4.玻璃封装:采用玻璃材料作为封装外壳,具有良好的绝缘性能和较高的可靠性,适用于高压MOS 管。

三、常见MOS 管封装结构的特点及应用1.SOP(Small Outline Package):小型封装,具有体积小、成本低等特点,适用于低功率MOS 管。

2.DIP(Dual In-Line Package):双列直插式封装,具有插拔方便、可靠性高等特点,适用于中功率MOS 管。

3.TO(Transistor Outline):晶体管外形封装,具有散热性能好、可靠性高等特点,适用于高功率MOS 管。

4.QFN(Quad Flat No-lead Package):四侧无引脚扁平封装,具有体积小、引脚数多等特点,适用于高频、低功耗MOS 管。

四、MOS 管封装结构的发展趋势随着电子技术的发展,对MOS 管封装结构的要求也越来越高。

未来的发展趋势主要体现在以下几个方面:1.封装尺寸的微型化:为了满足电子设备轻薄短小的要求,MOS 管封装结构将朝着微型化方向发展。

MOS管的引脚,G、S、D分别代表什么?

MOS管的引脚,G、S、D分别代表什么?

MOS管是电路设计中常用的功率开关器件,是压控型的,有三个电极,分别是:栅极G、源极S、漏极D。

MOS管分为NMOS和PMOS,其电路符号如下图所示。

栅极G

MOS管的栅极G是控制端,名字为gate,在G端加入高低电平即可控制MOS管的开断。

对于NMOS而言,要求Vgs>0时,MOS 管导通,否则MOS关断;对于PMOS而言,要求Vgs<>

源极S

源极,名字为Source,简称S。

对NMOS而言,源极S是流出端,对PMOS而言,源极S是流入端。

漏极D

漏极,名字为Drain,简称D。

对NMOS而言,漏极D是流入端,对PMOS而言,源极S是流出端。

MOS管常用的封装有TO-220,TO-263,SOT23等,一般从左往右的顺序为G、S、D,对于具体的芯片大家可以查阅其datasheet。

mos封装工艺流程

mos封装工艺流程英文回答:Metal-Oxide-Semiconductor (MOS) Fabrication Process.The MOS fabrication process involves the following steps:1. Substrate Preparation: A silicon wafer is cleaned and polished to provide a smooth surface for subsequent processing.2. Gate Oxide Formation: A thin layer of silicon dioxide (SiO2) is grown on the silicon substrate through thermal oxidation. This layer serves as the gate insulator.3. Gate Deposition and Patterning: A conductive material, such as polysilicon or metal, is deposited on the gate oxide and patterned to form the gate electrode.4. Source/Drain Implantation: Impurities are implanted into specific regions of the silicon substrate to createthe source and drain terminals of the transistor.5. Activation Annealing: The implanted impurities are activated by a high-temperature anneal, which restores the electrical properties of the silicon.6. Contact Formation: Contact holes are opened in the gate oxide and metal layers are deposited to connect the gate, source, and drain terminals to the external circuit.7. Passivation: A protective layer is deposited on the device to prevent contamination and oxidation.8. Packaging: The device is encapsulated in a packageto provide mechanical protection and electrical connections.中文回答:MOS 封装工艺流程。

2302(MOS管封装资料)中文版

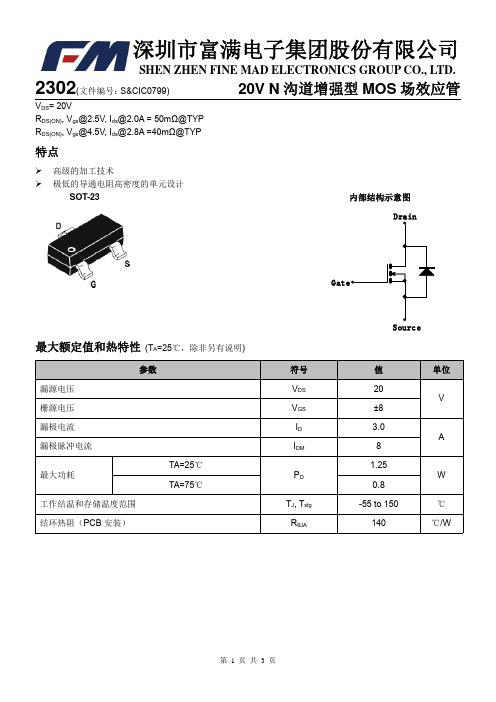

20V N 沟道增强型 MOS 场效应管

电特性

参数

符号

测试条件

静电

漏源击穿电压 漏源电阻

BVDSS RDS(on)

VGS = 0V, ID = 250uA VGS = 4.5V, ID = 2.8A VGS = 2.5V, ID = 2.0A

栅极阈值电压 栅源短路时,漏极电流 漏极短路时截止栅电流 漏源二极管

0.079

0.022 REF.

0.012

0.020

0°

8°

第3页共3页

典型

-40.0 50.0 0.7

---

--

最大

单位

--

V

60.0 mΩ

70.0

1.2

V

1

uA

±100

nA

1.3

V

V DD

S wi tc h in g

V IN

Test Circuit

RD D

V OU T

S wi tc hi ng Waveforms td (o n)

to n

tr

td (o ff )

9 0%

2302(文件编号:S&CIC0799)

20V N 沟道增强型 MOS 场效应管

符号

A A1 A2 b c D E E1 e e1 L L1 θ

毫米

最小

最大

0.900

1.150

0.000

0.100

0.900

1.050

0.300

0.500

0.080

0.150

2.800

3.000

1.200

1.400

2.250

VGS(th) IDSS IGSS

mos封装工艺流程

mos封装工艺流程英文回答:Metal-Oxide-Semiconductor (MOS) Fabrication Process.1. Substrate Preparation:A silicon wafer is polished and cleaned to remove any contamination.A thin layer of silicon dioxide (SiO2) is grown on the wafer to serve as an insulating layer.2. Gate Formation:A conductive material, typically polysilicon or metal, is deposited on the SiO2 layer.The conductive material is patterned and etched to create the gate electrode.3. Source/Drain Formation:Impurity atoms (e.g., phosphorus or boron) are introduced into specific regions of the wafer to create the source and drain contacts.The source and drain regions are formed by diffusion or ion implantation.4. Insulator Deposition:A second layer of SiO2 or another insulating material is deposited on the wafer to cover the gate electrode and the source/drain regions.5. Metal Contact Deposition:Metal contacts are deposited on the source, drain, and gate electrodes.The metal contacts are patterned and etched tocreate the necessary connections.6. Passivation:A protective layer, such as silicon nitride, is deposited on the MOS structure to protect it from environmental factors.7. Annealing:The MOS structure is subjected to a high-temperature annealing process to activate the implanted ions and improve device performance.8. Packaging:The MOS device is encapsulated in a protective package to protect it from physical damage and contamination.中文回答:MOS封装工艺流程。

mos管封装后阈值电压降低的原因

mos管封装后阈值电压降低的原因MOS管(金属氧化物半导体场效应晶体管)是一种常见的电子器件,广泛应用于各种电子设备中。

通过对MOS管进行封装,可以有效地保护电子元件,并提高其在复杂环境中的工作性能。

然而,封装后的MOS 管有时会出现阈值电压降低的情况,这是由于多种因素作用导致的。

首先,封装过程中可能会引入一些杂质。

封装材料、封装工艺以及封装环境都可能存在有害杂质,这些杂质会对MOS管的性能产生明显的影响。

尤其是一些金属杂质,很容易与MOS管内的金属电极发生反应,导致电极表面的能带结构发生改变,进而影响电荷传输和电压阈值。

其次,封装过程中的温度变化也会导致阈值电压降低。

封装过程中涉及到的高温环境,可能会引发电子与氧化物之间的相互作用,进而改变电荷传输层中的能带结构。

同时,高温还可能导致晶体管内部的材料热膨胀,从而引起晶体管结构变形,使得电荷传输的效率降低,导致阈值电压下降。

此外,封装过程中的机械应力也会对MOS管的性能产生影响。

封装过程中,MOS管常常会被固定在封装底座上,这会产生机械应力。

应力作用下,晶体管内部的结构可能会发生形变,导致晶体管的电学特性发生改变。

特别是对于细微的电子元件来说,即使是微小的应力变化也可能导致阈值电压的变动。

为了避免封装后MOS管阈值电压降低的问题,我们可以采取一些措施。

首先,封装过程中应选择高纯度、高质量的封装材料,尽量减少杂质的引入。

其次,在封装过程中控制好温度,避免温度过高引发的问题。

此外,还应该注意封装过程中的机械应力,避免产生过大的应力对MOS管产生影响。

总之,封装后的MOS管出现阈值电压降低的情况是由多种因素共同作用导致的。

了解这些因素对于我们正确选择封装材料、优化封装工艺,从而提高MOS管的工作性能非常重要。

通过采取适当的措施,我们可以最大程度地减少阈值电压的下降,确保MOS管在各种应用场景下的可靠性和稳定性。

常用全系列场效应管MOS管型号参数封装资料

常用全系列场效应管MOS管型号参数封装资料场效应管(MOS管)是一种常用的半导体器件,广泛应用于电子电路中。

在设计和选择MOS管时,我们通常需要考虑一些参数,如型号、封装形式、工作电压、电流、功率、频率特性等。

下面是一些常用的全系列MOS管型号参数封装资料:1.型号:MOS管有许多不同的型号,每个型号都有不同的特性和应用场景。

常见的MOS管型号有IRF44N、IRFP22N、IRF520N等。

2.封装形式:MOS管的封装形式有多种,常见的封装形式有TO-220、TO-247、DPAK、SOT-23等。

不同的封装形式适用于不同的应用场景,如TO-220适用于高功率应用,SOT-23适用于小功率应用等。

3.工作电压:MOS管的工作电压范围是选择MOS管时需要注意的一个重要参数。

常见的工作电压范围有10V、30V、60V、100V等。

4.电流:MOS管的电流处理能力也是一个重要的参数。

通常以最大电流(ID)来表示,最大电流是指在特定的工作条件下,MOS管能够承受的最大电流。

常见的最大电流有1A、5A、10A、20A等。

5.功率:MOS管的功率参数也需要考虑,在一定的工作电压和电流下,MOS管能够承受的最大功率是通过最大电流和额定工作电压计算得出的。

常见的功率参数有10W、50W、100W等。

6.频率特性:MOS管的频率特性也是一个重要的参数,表示MOS管在特定频率下的响应能力。

常见的频率特性有数十kHz、数百kHz、MHz等。

综上所述,常用全系列MOS管型号参数封装资料包括型号、封装形式、工作电压、电流、功率、频率特性等。

在选择MOS管时,我们需要根据具体的应用场景和需求,综合考虑这些参数,并选择最适合的型号和封装形式。

通过合理选择和使用MOS管,可以有效地满足电路设计和应用需求。

4953C(MOS管封装资料) 中文版

符号 VDS VGS ID IDM TJ, Tstg

D ra in

值 -20 ±12 -5.3 -20 -50 to 150

Байду номын сангаас

单位 V

A ℃

第1页共2页

深圳市富满电子有限公司

SHENZHEN FUMAN ELECTRONICS CO., LTD.

4953C (文件编号:S&CIC1071)

20V P 沟道增强型 MOS 场效应管

电特性

参数

符号

静电

漏源击穿电压

漏源电阻

栅极阈值电压 栅源短路时漏极电流 漏极短路时截止栅电流 跨导 漏源二极管

BVDSS RDS(on) RDS(on) VGS(th)

IDSS IGSS Gfs

二极管最大正向电流

IS

二极管正向电压

VSD

注:脉冲测试:脉冲宽度 <=300us,占空比<=2%

测试条件

最小

VGS = 0V, ID = -250uA -20

VGS = -4.5V, ID = -4.2A

--

VGS = -10V, ID = -5.3A

--

VDS = VGS, ID = -250uA

-1

VDS = -24V, VGS = 0V

--

VGS = ±20V, VDs= 0V

--

VDS = -10V, ID = -5.3A

深圳市富满电子有限公司

SHENZHEN FUMAN ELECTRONICS CO., LTD.

4953C (文件编号:S&CIC1071)

VDS= -20V RDS(ON), Vgs@-10V, Ids@-5.3A = 65mΩ@TYP RDS(ON), Vgs@-4.5V, Ids@-4.2A = 98mΩ@TYP

工程师常用mos管封装及图片

MOS管简介MOS管的英文全称叫MOSFET(Metal Oxide Semiconductor Field Effect Transistor),即金属氧化物半导体型场效应管,属于场效应晶体管中的绝缘栅型。

因此,MOS管有时被称为场效应管。

在一般电子电路中,MOS管通常被用于放大电路或开关电路。

而在板卡上的电源稳压电路中,MOSFET扮演的角色主要是判断电位。

MOS管的作用是什么MOS管对于整个供电系统而言起着稳压的作用。

目前板卡上所采用的MOS管并不是太多,一般有10个左右,主要原因是大部分MOS管被整合到IC芯片中去了。

由于MOS 管主要作用是为配件提供稳定的电压,所以它一般使用在CPU、GPU和插槽等附近。

MOS 管一般是以上下两个组成一组的形式出现板卡上。

MOS管封装形式MOSFET芯片在制作完成之后,需要给MOSFET芯片加上一个外壳,即MOS管封装。

MOSFET芯片的外壳具有支撑、保护、冷却的作用,同时还为芯片提供电气连接和隔离,以便MOSFET器件与其它元件构成完整的电路。

按照安装在PCB方式来区分,MOS管封装主要有两大类:插入式(Through Hole)和表面贴装式(Surface Mount)。

插入式就是MOSFET的管脚穿过PCB的安装孔焊接在PCB上。

表面贴裝则是MOSFET的管脚及散热法兰焊接在PCB表面的焊盘上。

常见的插入式封装MOSFET典型的表面贴装式封装MOSFET随着技术的革新与进步,主板和显卡的PCB板采用直插式封装的MOSFET越来越少了,而多改用表面贴装式封装的MOSFET。

故而本文中重点讨论表面贴装式封装MOSFET,并从MOS管外部封装技术、MOS管内部封装改进技术、整合式DrMOS、MOSFET发展趋势和MOSFET实例讲解等进行详细介绍。

MOS管外部封装-标准封装形式概览MOS管外部封装-标准封装形式概览下面我们对标准的封装形式进行如下简要的介绍。

场效应管封装类型和标识_解释说明以及概述

场效应管封装类型和标识解释说明以及概述1. 引言1.1 概述场效应管(MOSFET)是一种常用的电子元件,广泛应用于电路设计和功率控制系统中。

在实际应用中,不同的场效应管需要使用不同的封装类型和标识来满足特定的需求。

1.2 文章结构本文将重点介绍场效应管封装类型和标识的相关知识。

首先,我们将解释说明什么是场效应管封装类型,包括其定义、特点和主要分类。

然后,我们将详细讨论场效应管封装标识,介绍其作用、使用方法以及常见的标识符号含义。

最后,我们将对场效应管封装进行概述,总结各种封装的主要特点和适用范围。

1.3 目的通过本文对场效应管封装类型和标识进行详细说明和概述,旨在帮助读者更好地理解场效应管及其相关标识信息,并为正确选择合适的封装类型提供参考依据。

此外,本文还将为读者提供一个全面了解场效应管封装领域发展动态的基础,在电子领域中有关设计、测试和选型方面提供实用指导。

2. 场效应管封装类型和标识2.1 场效应管封装类型解释说明场效应管(MOSFET)是一种常用的电子器件,广泛应用于各种电路中。

场效应管的封装类型决定了其外观形状、引脚布局以及安装方式等特征。

常见的场效应管封装类型有TO-92、TO-220、SOT-23等。

TO-92是一种较小型的封装,通常具有三个引脚。

其中一个引脚是栅极(Gate),另外两个引脚分别是漏极(Drain)和源极(Source)。

这种封装适用于低功率的电路应用,如小型信号放大器和开关等。

TO-220是一种较大型的封装,通常具有三个或四个引脚。

其中一个引脚是栅极,其他引脚则用于漏极和源极之间的电流传输以及导热至散热器。

这种封装适用于中高功率的电路应用,如交流驱动器、开关稳压器和电机控制等。

SOT-23是一种更小型的表面贴片封装,通常具有三个引脚。

与TO-92相比,SOT-23封装更适用于小型空间集成电路和低功耗应用,如便携式设备和手机等。

2.2 场效应管封装标识解释说明场效应管的封装标识通常是指封装型号或代号,其目的是方便对不同类型的场效应管进行识别和选择。

mos管封装工艺

MOS管封装工艺1. 简介MOS管(Metal-Oxide-Semiconductor Field-Effect Transistor)是一种常用的半导体器件,用于放大和开关电路。

MOS管封装工艺是将MOS管芯片封装成可插拔的封装件,以便在电路中使用。

本文将详细介绍MOS管封装工艺的流程、材料和常见问题。

2. MOS管封装工艺流程MOS管封装工艺的主要流程包括芯片切割、引线焊接、封装和测试等步骤。

2.1 芯片切割芯片切割是将制造好的MOS管芯片切割成单个的小尺寸芯片。

切割过程需要使用切割机械,将芯片切割成所需的尺寸。

切割后的芯片需要进行清洗和检验,确保没有切割缺陷和杂质。

2.2 引线焊接引线焊接是将芯片与外部引线连接的过程。

通常使用金线或铜线作为引线材料,通过焊接机械将引线与芯片的金属电极连接起来。

焊接过程需要控制温度和焊接时间,以确保焊接质量。

2.3 封装封装是将焊接好的芯片封装到外壳中的过程。

封装过程需要使用封装机械,将芯片放置在外壳的合适位置,并使用封装材料将芯片封装起来。

封装材料通常是塑料或陶瓷,具有良好的绝缘性能和机械强度。

2.4 测试封装完成后,需要对封装好的MOS管进行测试。

测试过程包括电性能测试和可靠性测试。

电性能测试用于验证MOS管的电气参数是否满足设计要求,可靠性测试用于验证MOS管在长期使用中的可靠性和稳定性。

3. MOS管封装工艺材料MOS管封装工艺中使用的主要材料包括芯片、引线、封装材料和测试设备。

3.1 芯片芯片是MOS管封装工艺的核心部件。

芯片由半导体材料制成,具有金属电极和绝缘层。

芯片的制造需要先进行半导体工艺,包括沉积、刻蚀、掺杂等步骤。

制造好的芯片需要经过切割和清洗等步骤,才能进行封装。

3.2 引线引线是将芯片与外部电路连接的桥梁。

引线通常由金属线材制成,如金线或铜线。

引线需要具有良好的导电性和焊接性,以确保与芯片的连接可靠性。

3.3 封装材料封装材料是将芯片封装到外壳中的材料。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

MOS管外部封装-标准封装形式概览

下面我们对标准的封装形式进行如下简要的介绍。

按照“封装形式+要点介绍+相关图片”的方式进行如下说明。

TO(Transistor Out-line)封装

1、TO(Transistor Out-line)的中文即“晶体管外形”,是早期的封装规格,例如TO-92,TO-92L,TO-220,TO-252等等都是插入式封装设计。

2、近年来表面贴装市场需求量的增大也使得TO封装进展到表面贴装式封装。

TO252和TO263就是表面贴装封装。

其中TO-252又称之为D-PAK,TO-263又称

之为D2PAK。

TO封装的进展

D-PAK(TO-252)封装

SOT(Small Out-Line Transistor)封装

SOT(Small Out-Line Transistor)小外形晶体管封装。

这种封装就是贴片型小功率晶体管封装,比TO封装体积小,一般用于小功率MOSFET。

SOT封装

常用的四端引脚SOT-89 MOSFET

SOP(Small Out-Line Package)封装

1、SOP(Small Out-Line Package)的中文意思是“小外形封装”。

SOP是表面贴装型封装之一,引脚从封装两侧引出呈海鸥翼状(L 字形)。

材料有塑料和陶瓷两种。

SOP也叫SOL 和DFP。

2、SOP封装标准有SOP-8、SOP-16、SOP-20、SOP-28等等,SOP后面的数字表示引脚数。

MOSFET的SOP封装多数采用SOP-8规格,业界往往把“P”省略,叫SO(Small Out-Line )。

3、SO-8采用塑料封装,没有散热底板,散热不良,一般用于小功率MOSFET。

4、SO-8是PHILIP公司首先开发的,以后逐渐派生出TSOP(薄小外形封装)、VSOP(甚小外形封装)、 SSOP(缩小型SOP)、TSSOP(薄的缩小型SOP)等标准规格。

SOP-8封装

这些派生的几种封装规格中,TSOP和TSSOP常用于MOSFET封装QFN-56封装

1、QFN(Quad Flat Non-leaded package)是表面贴装型封装之一,中文叫做四边无引线扁平封装,是一种焊盘尺寸小、体积小、以塑料作为密封材料的新兴表面贴装芯片封装技术。

现在多称为LCC。

2、封装四边配置有电极接点,由于无引线,贴装占有面积比QFP小,高度比QFP低。

这种封装也称为LCC、PCLC、P-LCC等。

QFN本来用于集成电路的封装,MOSFET不会采用的。

INTEL提出的整合驱动与MOSFET的DrMOS采用QFN-56封装,56是指在芯片背面有56个连接Pin。

QFN56封装的DrMOS。