cadence 按分页编号

cadence hierarchical block里面元件位号

cadence hierarchical block里面元件位号Cadence是一款功能强大的集成电路设计软件,它提供了一个层次化的设计环境,允许用户创建和管理复杂的电路设计。

在Cadence中,层次化的设计方案使得大型电路设计变得更加简单,用户可以将整个电路分解成小的模块,然后分别进行设计和验证。

在层次化设计中,元件位号起着非常重要的作用,它们用来标识设计中的各个元件,如电阻、电容、晶体管等,以便于设计师能够清晰地了解电路的结构和连接关系。

在Cadence中,元件位号的分配是根据设计的实际情况进行的。

每个元件位号都代表了一个具体的元件,设计师需要根据元件的类型、功能以及连接关系来分配位号。

通常情况下,元件位号的分配需要遵循一定的规则,以确保设计的准确性和可读性。

在设计大型电路时,元件位号的合理分配可以显著提高设计效率和可维护性。

通过合理的位号分配,设计师可以快速定位和识别电路中的各个元件,便于设计和调试。

此外,元件位号还能够提供设计文档和交接时的参考,帮助工程师快速理解设计方案和寻找问题所在。

在进行层次化设计时,元件位号的管理和维护变得尤为重要。

Cadence提供了丰富的元件位号管理工具,例如位号编辑器、位号查找等,帮助设计师轻松地管理和维护设计中的元件位号。

通过这些工具,设计师可以方便地修改、更新和查找位号,有效地提高设计的可维护性和可读性。

总的来说,元件位号在Cadence层次化设计中扮演着非常重要的角色。

合理的位号分配能够提高设计效率和可维护性,帮助设计师快速理解和调试电路。

因此,在进行Cadence层次化设计时,设计师需要认真考虑元件位号的分配和管理,以确保设计的准确性和可读性。

Cadence SPB使用方法

Cadence SPB使用方法1.在用OrCad Capture CIS画电路原理图时,不同电路图页面之间的信号互联,单信号线(wire)用分页端口连接器(Off Page Connector)实现互联,总线(Bus)用端口(Port)实现互连(也可以用分页端口连接器(Off Page Connector))。

2.特别注意:在FPGA原理图设计中,在为FPGA设计原理图符号时,一般要将FPGA分为多个部分,这时一定要注意在管脚功能划分时,要将Bank2中用于配置的管脚,包括:配置模式选择管脚M0、M1,CCLK,DIN,INIT_B等与TMS,TCK,TDO,TDI 等一起划分到FPGA的配置(Configuration)部分。

3.在OrCad Capture CIS中制作原理图符号时,如果器件有多个(两个以上)管脚名称(pin name)相同,在保存该元件时就会弹出以下警告信息:因为ORCAD的封装(原理图符号)是有规则的,只有管脚为POWER属性才能同名,比如VCC,GND的管脚名等等,很好理解,这些属性在画PCB的时候默认的是同一个网络,是要连接在一起的,如GND连GND,VCC连VCC,有时候有很多的空脚NC 最好用NC1,NC2...来描述,避免不必要的错误,有的甚至连POWER属性的管脚名都不做重复的。

如果忽略这些这些警告信息,则当使用这些元件符号画电路图,在生成网表(Create Netlist)时就会产生错误:#79 Error [ALG0050] Duplicate Pin Name "SW" found on Package LM2852Y , U21 Pin Number 9: SCHEMATIC1, POWER SUPLLY (1.80, 3.20). Please renumber one of these.这时选中设计,可以利用accessories菜单的libcorrectionutil->library verification / correction来批量修改重复管脚定义(即:批量把重复的管脚名改为不同)。

Cadence_Allegro16.2常用操作方法

Cadence_Allegro16.2常用操作方法Orcad中图纸模版的设置1.Option—>Design Template—>Title Block,Symbol栏中输入Title Block所在的.OLB库文件位置(E:\cadence_design\schlib\DIDIDEV.OLB),Title Block中输入模版文件名“TitleBlock_SHU”,内有公司的logo。

2.Text栏内Title中输入正在设计的板的名称,Document Number中输入文件编号,Revision中输入版本号。

3.在添加新页时,模版图纸的上述信息会自动添加Orcad 中快速修改所有零件的Footprint方法一:一页一页修改,打开某页,按CTRL+A,选中当前页所有器件,再点右键,选Edit属性,在弹出对话框中选Parts栏,按要修改REF 排序,用左键拖拉要修改的为同种封装器件再点右键,然后击EDIT,填入封装就成批修改了方法二:选择顶层原理图(SCHEMATIC1),右键选Edit Object Properties,列出所有元件,找到PCB Footprint 那项,可以逐个填入,也可以相同封装填一个,然后拖动该黑框的右下角十字形复制。

Orcad BOM表中输出原件的PCBfootprint封装型号选中顶层项目设计.dsn标题,在tools菜单中选择bill of materials,在header栏追加填入“\tPCBFootPrint”,在Combined property string栏中追加填入“\t{PCB footprint}”,不选Open in Excel,生成.BOM文件后,用excel手工导入.BOM文件,在导入步骤三中选择“文本”方式。

然后在Excell 中修改BOM表的边框等格式。

Orcad还有一处地方可输出带有机械尺寸的BOM表,选中顶层项目设计.dsn标题,在report菜单中选择CIS bill of Materials,有standard和Crystal report两种形式输出。

cadence几种模式的用法

cadence几种模式的用法

Cadence几种模式分别是顺序模式、并行模式、Batch模式和Real-time模式。

1.顺序模式:按顺序执行每个任务,适用于简单的任务,如文本编辑或数据处

理。

2.并行模式:同时执行多个任务,适用于需要同时处理多个任务的情况。

3.Batch模式:适用于需要处理大量数据的场景,如数据清洗、数据转换、数

据分析等。

在此模式下,Cadence将任务分为多个小的子任务,并按照一定的顺序执行,每个子任务可以并行执行,从而提高整体的处理效率。

使用Batch模式时,可以使用Cadence提供的批处理工具来处理大规模数据。

这些工具提供了丰富的功能,如数据输入输出、任务调度、错误处理等。

开发人员只需定义数据处理的逻辑,而无需关心底层的分布式系统细节。

4.Real-time模式:适用于需要及时响应用户请求的场景,如实时推荐、实时

监控、实时报警等。

在此模式下,Cadence使用事件驱动的方式来处理任务,即根据事件的发生来触发相应的处理程序。

以上信息仅供参考,可以咨询计算机领域专业人士获取更全面准确的信息。

capure分立器件自动编号技巧

Cadence笔记--原理图1. OrCAD Capture CIS中分部份画原件库a. 如果在一个器件中分为几个功能基本相同,则创建分部分元件时使用默认的Homogeneous,如果几个部分的功能不一样,引脚数量也不一样,则应该先择Heterogeneous。

b. 如果选择Heterogeneous则在原理图中自动编号会出现错误,具体的解决为法是对于此类器件在画好所有部分后还要为每一个部分新建一个属性,以Pack_Group为属性名为例:然后在原理图中放置元件时按照想要的分组手工修改些属性,同一个元件的该属性值必须一样,并且还要在自动编号时修改参数如下图:然后在自动编号时就不会也现该问题了,当然其实如果报错时你也可以根据提示进行问题的解决!2. Cadence中的元件库默认目录:C:\Cadence\SPB_16.2\tools\capture\library3. 原理图编辑快捷键快捷放元键:P选中元件后对元件进行旋转:R放置网络标号:N放置总线管脚(Bus entry):E放置地:G在的理图中放置好总线的一个分支脚后,想要连续放置直接按F4就可以了,很方便,如果第一条总线分支完成了后,按F4更简单,连标号都会直接自动递增的放置。

节约时间,使放置总线更简单。

4. 在原理图中想画任意角度的连接线时,可以先按信Shift键,再画线,就可画了!5. 如果一个交叉点上不需要Junction点的话,只需要再往上重复添加一个即可去掉Junction 连接点标志。

电气上也就失去了连接。

6. 在放置总线时,总线的名字和信号线的标号的基本名必须一致,且开始和结尾的数字必须与总线定义的一致。

7. 即使使用了总线,信号线上也必须加上网络标号,否则软件会认为没有电气连接。

但要说明的是,总线与总线之间若构成T型连接,则系统会默认电气上已经连接上,若是构成十字型连接,则系统则会认为没有电气连接,需要手动添加Junction来添加电气连接。

OrCAD原理图中分裂元件自动编号的方法

原理图含有分裂元件时,Cadence 自动编号报错 Cannot perform annotation of heterogeneous part 'U?A(Value) at location (1.70, 7.10) on page ADC', part has not been uniquely grouped (using a common User Property with differing Values) or the device designation has not been chosen 网上搜了一下,得到一种简单的方法。 可按如下步骤修改软件设置,实现自动编号。 1. 工具栏选择 Accessories -> Cadence Tcl/Tk Utilities -> Utilities

2.

弹出的窗口选中 Extended Prefrences ,点击 Launch

3.

窗口中选择 Design Annotation,右边选择 First Match,保存即可

ቤተ መጻሕፍቲ ባይዱ

按照上述步骤设置完成后即可进行自动编号, 且不会报错, 解决了分裂器件软件无法正确识 别判断编号问题。

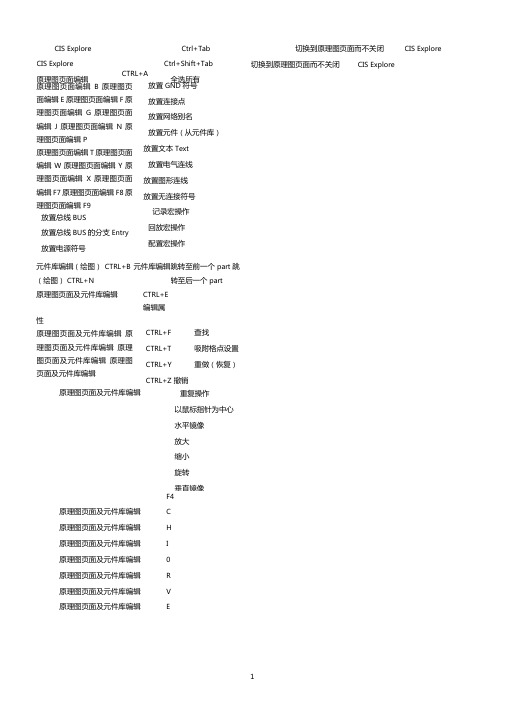

cadence操作常用快捷键总结

原理图页面编辑 B 原理图页面编辑 E 原理图页面编辑 F 原理图页面编辑 G 原理图页面编辑 J 原理图页面编辑 N 原理图页面编辑 P原理图页面编辑 T 原理图页面编辑 W 原理图页面编辑 Y 原理图页面编辑 X 原理图页面编辑 F7 原理图页面编辑 F8 原理图页面编辑 F9 放置总线BUS放置总线BUS 的分支Entry放置电源符号放置GND 符号 放置连接点 放置网络别名 放置元件(从元件库)放置文本Text 放置电气连线 放置图形连线 放置无连接符号 记录宏操作 回放宏操作 配置宏操作元件库编辑(绘图) CTRL+B 元件库编辑(绘图) CTRL+N原理图页面及元件库编辑CTRL+E编辑属性原理图页面及元件库编辑 原理图页面及元件库编辑 原理图页面及元件库编辑 原理图页面及元件库编辑CTRL+F 查找 CTRL+T 吸附格点设置 CTRL+Y 重做(恢复)CTRL+Z 撤销原理图页面及元件库编辑F4 原理图页面及元件库编辑 C 原理图页面及元件库编辑 H 原理图页面及元件库编辑 I 原理图页面及元件库编辑 0 原理图页面及元件库编辑 R 原理图页面及元件库编辑 V 原理图页面及元件库编辑ECIS Explore CIS Explore原理图页面编辑CTRL+ACtrl+Tab Ctrl+Shift+Tab全选所有 切换到原理图页面而不关闭切换到原理图页面而不关闭CIS ExploreCIS Explore跳转至前一个 part 跳转至后一个part重复操作 以鼠标指针为中心 水平镜像 放大 缩小 旋转垂直镜像9.嶂理剛页面窗口中的操作匸塢理图的显示.放大、縮小和滚动9.1放大.缩小的方法方法L放大:按键盘的I缩小,按钮盘的O <Zoom Out)放大r缩小时,以光标为中心进行方法2;集l P- : \^iew 江 oo in方法鉄右I貝理性I页面上.点击右僦’选择Zdcmi Out方法4:Ctrl 13,鼠标的滚轮向下转动.缩小”鼠标的滚轮向上转动”放大9,2上下洽动方法1;使用滚动条方法匕便用Page up 和Page down方法却鼠标的滚轮向下或向I9.3左右闹动抜住Ctrl SI * 冉按Page up;向At抜ft Ctrl址+再按Page dowix向右cadence操作常用快捷键总结x :检查并存盘s :存盘[:缩小]:放大F:整图居中显示u:撤销上一次操作Esc :清楚刚键入的命令c :复制m移动shift+m :移动器件但不移动连线Delete :删除i :添加元器件P:添加端口r:旋转器件并拖动连线q:属性编辑L:添加线名shift+L :标注N:添加几何图形shift+N :添加标号g:查看错误shift+z :缩小ctrl+z :放大F:整图居中显示u:撤销上一次操作Esc :清楚刚键入的命令Ctrl +D :取消选择,这个也可用鼠标点击空白区域实现。

OrCAD原理图中分裂元件自动编号的方法

OrCAD原理图中分裂元件自动编号的方法

OrCAD原理图中分裂元件自动编号的方法

原理图含有分裂元件时,Cadence自动编号报错

Cannot perform annotation of heterogeneous part 'U?A(V alue) at location (1.70, 7.10) on page ADC', part has not been uniquely grouped (using a common User Property with differing Values) or the device designation has not been chosen 网上搜了一下,得到一种简单的方法。

可按如下步骤修改软件设置,实现自动编号。

1.工具栏选择Accessories-> Cadence Tcl/Tk Utilities ->Utilities

2.弹出的窗口选中Extended Prefrences,点击Launch

3.窗口中选择Design Annotation,右边选择First Match,保存即可

按照上述步骤设置完成后即可进行自动编号,且不会报错,解决了分裂器件软件无法正确识别判断编号问题。

capture分立器件自动编号技巧

Cadence笔记--原理图1. OrCAD Capture CIS中分部份画原件库a. 如果在一个器件中分为几个功能基本相同,则创建分部分元件时使用默认的Homogeneous,如果几个部分的功能不一样,引脚数量也不一样,则应该先择Heterogeneous。

b. 如果选择Heterogeneous则在原理图中自动编号会出现错误,具体的解决为法是对于此类器件在画好所有部分后还要为每一个部分新建一个属性,以Pack_Group为属性名为例:然后在原理图中放置元件时按照想要的分组手工修改些属性,同一个元件的该属性值必须一样,并且还要在自动编号时修改参数如下图:然后在自动编号时就不会也现该问题了,当然其实如果报错时你也可以根据提示进行问题的解决!2. Cadence中的元件库默认目录:C:\Cadence\SPB_16.2\tools\capture\library3. 原理图编辑快捷键快捷放元键:P选中元件后对元件进行旋转:R放置网络标号:N放置总线管脚(Bus entry):E放置地:G在的理图中放置好总线的一个分支脚后,想要连续放置直接按F4就可以了,很方便,如果第一条总线分支完成了后,按F4更简单,连标号都会直接自动递增的放置。

节约时间,使放置总线更简单。

4. 在原理图中想画任意角度的连接线时,可以先按信Shift键,再画线,就可画了!5. 如果一个交叉点上不需要Junction点的话,只需要再往上重复添加一个即可去掉Junction 连接点标志。

电气上也就失去了连接。

6. 在放置总线时,总线的名字和信号线的标号的基本名必须一致,且开始和结尾的数字必须与总线定义的一致。

7. 即使使用了总线,信号线上也必须加上网络标号,否则软件会认为没有电气连接。

但要说明的是,总线与总线之间若构成T型连接,则系统会默认电气上已经连接上,若是构成十字型连接,则系统则会认为没有电气连接,需要手动添加Junction来添加电气连接。

cadence中元器件编号问题经验小结

cadence中元器件编号问题经验小结2012-09-10 11:44:44| 分类:pcb制作 | 标签:cadence学习|字号订阅当今社会,大部分的IT公司已经有自己的产品,研发人员都是在已有的产品的基础上进行修改,增加新的功能、使用新的技术……研发出新一代的产品,使其产品更加具备竞争力。

在这里我想谈一下成型产品在修改过程中的元器件编号问题。

成型的产品在电路原理图设计的过程中,各个元器件的编号已经确定,如果我们在这个过程中增加某种元器件的数量,对于这些元器件的编号就不知道从何编起,稍有不慎就会出错。

这个时候我们就会想起给这些元器件进行自动编号。

那么如何这些新增加的元器件进行编号呢?我从自己修改原理图的体验中提出了以下几种方案:1. 增加少量的元器件。

增加一些少量的元器件的过程中,我们在放置这些元器件的过程中把这些元器件的编号更改为“?”的形式,由于在原理图的设计过程中,工程制图软件会把一些关键字之后的?进行自动编号,否则自动编号将无法进行。

自动编号的操作指令如下:点击菜单栏中的”Tools” →“Annotate”弹出如下的对话框:这个默认的选项基本上就能够实现,元器件的自动编号,(注意:这个对话框的弹出必须是在工程菜单中点击Tools才会有Annotate)下面对上述的对话框进行说明:a,Scope中的:Update entire design是更新整个设计Update selection 更新选择的部分电路b,ActionIncremental reference update 在现有的基础上进行增加排序Unconditional reference update 无条件进行排序Reset part reference to “?” 把所有的序号都变成“?”Add intersheet reference 在分页图纸间的端口的序号加上图纸编号Delete intersheet references 删除分页图纸间的端口的序号上的图纸编号c,Combined property 网络表中要包含的属性d,Reset reference numbers to begin at 1 in each page编号时每张图纸都从1开始e,Do not change the page number不要改变图纸编号解释完这些,估计朋友们都能看出我们应该选择哪个选项以及不应该选择哪个选项。

Cadence 快速入门教程

Cadence SPB15.7 快速入门视频教程目录第1讲课程介绍,学习方法,了解CADENCE软件第2讲创建工程,创建元件库第3讲分裂元件的制作方法区别(Ctrl+B、Ctrl+N切换Part)点击View,点击Package可以显示所有的元件Part1、homogeneous 和heterogeneous2、创建homogeneous类型元件3、创建heterogeneous类型元件第4讲正确使用heterogeneous类型的元件增加packeg属性。

点击Option,选择Part Properties,选择new,增加属性。

用于在原理图中确定同一块的元件。

1、可能出现的错误2、出现错误的原因3、正确的处理方法第5讲加入元件库,放置元件1、如何在原理图中加入元件库2、如何删除元件库3、如何在元件库中搜索元件4、放置元件5、放置电源和地第6讲同一个页面内建立电气互连(设置索引编号,Tools里面,Annotate来设置)1、放置wire,90度转角,任意转角(画线时按住Shift)2、wire的连接方式3、十字交叉wire加入连接点方法,删除连接点方法(快捷键J)4、放置net alias方法(快捷键n)5、没有任何电气连接管脚处理方法(工具栏Place no Conection)6、建立电气连接的注意事项第7讲总线的使用方法1、放置总线(快捷键B)2、放置任意转角的总线(按住Shift键)3、总线命名规则(LED[0:31],不能数字结尾)4、把信号连接到总线(工具栏Place Bus entry 或者E)5、重复放置与总线连接的信号线(按住Ctrl向下拖)6、总线使用中的注意事项7、在不同页面之间建立电气连接(工具栏Place off-page connector)第8讲browse命令的使用技巧(选中dsn文件,选择Edit中的browse)1、浏览所有parts,使用技巧(浏览元件<编号,值,库中的名字,库的来源>,双击元件可在原理图上找到元件)2、浏览所有nets,使用技巧(浏览网络)3、浏览所有offpage connector,使用技巧(页面间的连接网络,一般一个网络至少会在两个页面中出现)4、浏览所有DRC makers,使用技巧(DRC检测)第9讲搜索操作使用技巧(右上脚的望远镜那,按下下拉三角可以设置搜索的范围)1、搜索特定part(查找元件)2、搜索特定net(查找网络)3、搜索特定power(查找电源)4、搜索特定flat nets(将搜索的网络在一个原理图中都高亮显示)第10讲元件的替换与更新(打开Designer Cache,选中元件,右键打击,选择Replace Cache或者Update Cache)1、replace cache用法(New Part Name 选择替换元件,Part Library 库的位置,Action 1、保存原理图属性(比如编号),2、去除所有属性)2、update cache用法(同replace Cache,如果更改了元件,可以用updata把最新的元件模型更新进来)3、replace cache与pdate cache区别(replace可以更改元件与元件库的连接关系,封装属性只能用replace的不保存属性来更新封装信息)第11讲对原理图中对象的基本操作1、对象的选择2、对象的移动(默认是保持现有连接的移动,可以按住Alt可以断开连接),(断开后如不能移动连接:打开菜单栏Options,打开prefrence,选择Miscellaneous,勾选右下角wire Drag)3、对象的旋转(选中元件,然后按住R键)4、对象的镜像翻转(选中元件,选择菜单栏edit中的mirror(文本和位图不能镜像))5、对象的拷贝、粘贴、删除(按住Ctrl,然后选中元件并拖动)第12讲1、修改元件的V ALUE及索引编号方法(双击V ALUE或者索引编号就可以直接改了)2、属性值位置调整(选中并拖动)3、放置文本(菜单栏place,text(换行按住Ctrl和Enter)。

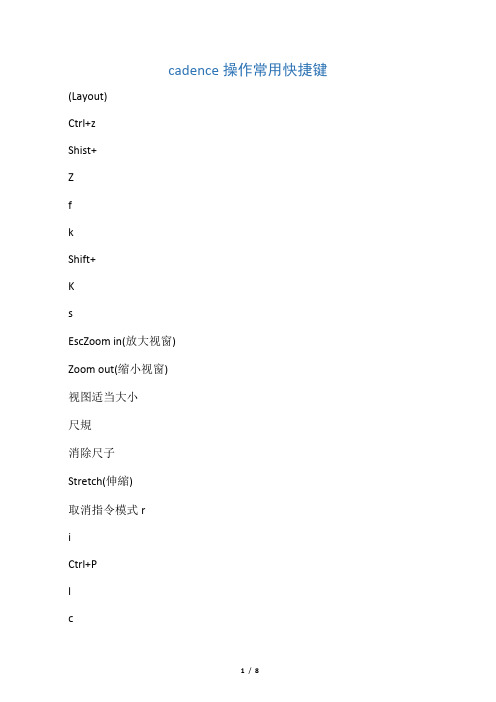

cadence操作常用快捷键

cadence操作常用快捷键(Layout)Ctrl+zShist+ZfkShift+KsEscZoom in(放大视窗)Zoom out(缩小视窗)视图适当大小尺規消除尺子Stretch(伸縮)取消指令模式riCtrl+PlcmdelqRectangular(画矩形)Instance(加入例元)加入Pin脚加入Label(标签)Copy(复制)Move(移動)Delete(删除)Property(属性)Mouse按左键选取,右键圈选放大Layout快捷键:shift+z:缩小W快速显示最小化的LSMctrl+z:放大F:整图居中显示c:复制m:移动shift+x:进入下一层版图ctrl+x:还回上一层版图i:插入模块R:画矩形Shift+P:多边形工具PolygonP:插入PathK:标尺工具shift+K:清除所有标尺L:标签工具,标签要加在特定的text层上,这个有些人总忘记。

Shift+C:裁切(Chop),首先调用命令,选中要裁切的图形,后画矩形裁切。

在用P快捷键画了一条Path后,如果需要调整线宽,就需要用到这个快捷键。

Ctrl+Z视图放大两倍Zoom In by 2Shift+Z视图缩小两倍Zoom Out by 2Z键视图放大。

Shift+O旋转工具。

RotateCtrl+P插入引脚。

PinCadence Virtuoso Layout Editor快捷键归纳右键点击拖放用来放大。

放大后经常配合F键使用,恢复到全部显示。

配合Tab键使用,平移视图。

u:撤销上一次操作Esc:清楚刚键入的命令Ctrl +D:取消选择,这个也可用鼠标点击空白区域实现。

经常使用这个快捷键可以防止误操作。

q:显示属性Delete:删除S:拉伸工具Stretch,要求是框选要拉伸图形,再拉伸。

O键插入接触孔。

Create ContactShift+左键加选图形,Ctrl+左键减选图形。

F2保存。

F3这个快捷键很有用,是控制在选取相应工具后是否显示相应属性对话框的。

cadence中元器件编号问题经验小结

cadence中元器件编号问题经验小结2012-09-10 11:44:44| 分类:pcb制作 | 标签:cadence学习|字号订阅当今社会,大部分的IT公司已经有自己的产品,研发人员都是在已有的产品的基础上进行修改,增加新的功能、使用新的技术……研发出新一代的产品,使其产品更加具备竞争力。

在这里我想谈一下成型产品在修改过程中的元器件编号问题。

成型的产品在电路原理图设计的过程中,各个元器件的编号已经确定,如果我们在这个过程中增加某种元器件的数量,对于这些元器件的编号就不知道从何编起,稍有不慎就会出错。

这个时候我们就会想起给这些元器件进行自动编号。

那么如何这些新增加的元器件进行编号呢?我从自己修改原理图的体验中提出了以下几种方案:1. 增加少量的元器件。

增加一些少量的元器件的过程中,我们在放置这些元器件的过程中把这些元器件的编号更改为“?”的形式,由于在原理图的设计过程中,工程制图软件会把一些关键字之后的?进行自动编号,否则自动编号将无法进行。

自动编号的操作指令如下:点击菜单栏中的”Tools” →“Annotate”弹出如下的对话框:这个默认的选项基本上就能够实现,元器件的自动编号,(注意:这个对话框的弹出必须是在工程菜单中点击Tools才会有Annotate)下面对上述的对话框进行说明:a,Scope中的:Update entire design是更新整个设计Update selection 更新选择的部分电路b,ActionIncremental reference update 在现有的基础上进行增加排序Unconditional reference update 无条件进行排序Reset part reference to “?” 把所有的序号都变成“?”Add intersheet reference 在分页图纸间的端口的序号加上图纸编号Delete intersheet references 删除分页图纸间的端口的序号上的图纸编号c,Combined property 网络表中要包含的属性d,Reset reference numbers to begin at 1 in each page编号时每张图纸都从1开始e,Do not change the page number不要改变图纸编号解释完这些,估计朋友们都能看出我们应该选择哪个选项以及不应该选择哪个选项。

Cadence 使用参考手册

Cadence 使用参考手册邓海飞微电子学研究所设计室2000年7月目录概述 (1)1.1 Cadence概述 (1)1.2 ASIC设计流程 (1)第一章Cadence 使用基础 (5)2.1 Cadence 软件的环境设置 (5)2.2 Cadence软件的启动方法 (10)2.3库文件的管理 (12)2.4文件格式的转化 (14)2.5 怎样使用在线帮助 (14)2.6 本手册的组成 (15)第二章Verilog-XL 的介绍 (16)3. 1 环境设置 (16)3.2 Verilog-XL的启动 (16)3.3 Verilog-XL的界面 (18)3.4 Verilog-XL的使用示例 (19)3.5 Verilog-XL的有关帮助文件 (20)第四章电路图设计及电路模拟 (22)4.1 电路图设计工具Composer (22)4.1.1 设置 (22)4.1.2 启动 (23)4.1.3 用户界面及使用方法 (23)4.1.4 使用示例 (25)4.1.5 相关在线帮助文档 (25)4.2 电路模拟工具Analog Artist (25)4.2.1 设置 (25)4.2.2 启动 (26)4.2.3 用户界面及使用方法 (26)4.2.5 相关在线帮助文档 (26)第五章自动布局布线 (28)5.1 Cadence中的自动布局布线流程 (28)5.2 用AutoAbgen进行自动布局布线库设计 (29)第六章版图设计及其验证 (31)6.1 版图设计大师Virtuoso Layout Editor (31)6.1.1 设置 (31)6.1.2 启动 (31)6.1.3 用户界面及使用方法 (31)6.1.4 使用示例 (32)6.1.5 相关在线帮助文档 (32)6.2 版图验证工具Dracula (32)6.2.1 Dracula使用介绍 (32)6.2.2 相关在线帮助文档 (33)第七章skill语言程序设计.................... 错误!未定义书签。

asp ckeditor 分页

Asp里实现分页真的是很麻烦,利用控制字数分页很大概率网页显示的文章会出现html 代码,在网上搜了很多天的解决办法,都不如意。

我用的编辑器是ckeditor,里面有个按钮是可以插入分页符的,分页符的源代码:<div style="page-break-after: always;"><span style="display: none;"> </span></div>,但是这么大一串代码里,有换行符,有双引号,有空格的,利用它做分页,实现起来是真的困难,还在网上找了asp的正则表达式也弄了好久,最终还是没实现。

所以最后想到自己给ckeditor添加一个插件按钮,相应的给文章添加一个特殊的代码,然后asp利用此代码作为标记来分页,其实也可以添加文章的时候自己手写那个特殊的代码,但是可能文章也不是由本人编辑,所以还是添加一个按钮比较合适。

呵呵,说了这么一大堆,只是为了和你分享我的成果,解决你们的困扰,希望橙子的小发现能给你们带来帮助。

以下为我实现的步骤:一、首先说明下,要想把ckeditor里的分页符源码改为得简单些,是在是太难了,可能是我对js不熟悉吧,所以就自己添加插件按钮来插入分页符:1.在ckeditor的plugins目录新建文件夹nextpage,在nextpage下新建文件:plugin.js 内容如下:(function(){var a= {exec:function(editor){editor.insertHtml("[[page]]");}},b="nextpage";CKEDITOR.plugins.add(b,{init:function(editor){editor.addCommand(b,a);editor.ui.addButton("nextpage",{label:"nextpage",icon: this.path + "nextpage.gif",command:b});}});})();还要在文件夹nextpage下,添加一个图标nextpage.gif大小差不多是16*16的2.在toolbar中加一项nextpage,并在配置中声明添加扩展插件config.extraPlugins =‘nextpage’;有两种方法实现,方法一是直接在config.js中添加;方法二:在引用CKEditor的地方加配置参数,我是用方法一配置的:CKEDITOR.editorConfig = function( config ){config.font_names = '宋体/宋体;黑体/黑体;仿宋/仿宋_GB2312;楷体/楷体_GB2312;隶书/隶书;幼圆/幼圆;雅黑/雅黑;'+ config.font_names ;nguage = 'zh-cn';config.skin = 'v2';config.width = 650;config.height = 300;config.removePlugins = 'elementspath';config.extraPlugins = "nextpage";//新建插件config.toolbar=[['Source','unlink','-','Save','unlink','Preview','-','Templates'],['Cut','Copy','Paste','PasteText','PasteFromWord','-','Print','SpellChecker','Scayt'],['Undo','Redo','-','Find','Replace','-','SelectAll','RemoveFormat'],'/',['Bold','Italic','Underline','Strike','-','Subscript','Superscript'],['NumberedList','BulletedList','-','Outdent','Indent','Blockquote'],['JustifyLeft','JustifyCenter','JustifyRight','JustifyBlock'],['Link','Unlink','Anchor'],['Image','Flash','Table','HorizontalRule','Smiley','SpecialChar','PageBreak','nextpage'], //我的按钮'/',['Styles','Format','Font','FontSize'],['TextColor','BGColor'],['Maximize','ShowBlocks','-','About','-']];};这样就在ckeditor编辑器里添加了一个nextpage按钮插件,在文章需要分页的地方按下这个按钮,就会在文章中添加一个[[page]]代码。

Cadence下原理图绘制,单页与多页图的处理

复杂多页图层次式连接

这种复杂多页图层次式连接 并不常用,只有在重复模块 较多时才能用得到,目前大 家只需要了解一下处理方式 即可。 首先建立一个新工程,在新 的图面上用 PlaceHierarchical Block菜单命令来绘制该层 次图的方框。如右图反色部 分。

复杂多页图拼接式的连接处理

为完成复杂多页,我们还需要再绘制几页图,我们 把以上绘制的图放在了第二页,在第一页中加入了 CPU部分和FLASH元件。第三页中加了CPU的第二个部 分和复位电路及UART电路。 同一图页,没有涉及外连的网络只放置网络标号, 这样就可以看出此网络是在本图页上。

放置图页间连接端口符号的,表明该网络还在其它 图面上存在。这是多图拼接式主要连接处理方式。

绘图工具栏中“《C”图标是放 置图纸页与页之间的连接符号, 在约定情况下只有两种进与出, 即“》”、“《”。 该两种标号不能满足总线间的 连接,但依然可用。 如依然采用该两种符号进行页 与页之间的连接,则总线将不 存在。就是说总线将被打散并 只以这两种符号来表示。 解决办法,COPY,再次点击《C 图标就可以在其中找到该COPY 的连接图标。 为方便和统一我们找来三种共 六个符号的图与图之间连接的 端口连接图标。如右上图所示

进行总线连接

先放置进行总线连接的线, 用绘图工具栏中电源图标 上面的图标命令。 在所需要汇总的总线线路 上都放置该种图线。 有放置该图线前用鼠标点 击右键可在弹出的菜单中 有Rotate命令可实现翻转。 用Z字型图标来绘制总线就 是把放有总线连接线的斜 线段都用该总线连接上。

Cadence常用技巧、网表导入PADS、CAD板框导入PADS

在进行中等以上规模电路设计的时候,一般都是专人负责原理图原理图,专人负责layout,orCAD因为他的输出网表种类相当丰富,操作方便深受原理设计人员青睐,orCAD可以输出目前市面上大部分PCB设计软件的网表,包括protel、AltiumDesigner、PADS、Alegrro等等,下面介绍一下两者交互设计时候网表导入和更新问题。

1、生成网表。

首先在rocad中选中要生成网表的原理图文件夹,之后执行Tool/Creat Netlist命令,之后弹出下面的对话框:在other页面中Formatter中选择orPadspc.dll,之后点击确定,便会生成PDAS所使用.asc格式的网表,如下图所示:2、导入网表。

新建一个PADS PCB文件,在此假设名字为Demo.pcb.如下图所示:新建文件之后,首先要有自己的PCB封装库,并且设置好自己的PCB封装库路径,设置PCB封装库路径发方法如下:工具/选项之后弹出来如下界面:点击右侧的库列表文件夹,如下图所示,之后选择自己的PCB封装库所在位置:这样自己的封装库路径设置完成了。

之后可以在PADS layout软件中导入网表了。

打开刚才创建的Demo.pcb文件,执行"文件/导入"命令,打开刚才用orcad生成的.asc文件。

之后会弹出一个检验文本,提示所有的错误和警告,如下图所示:之后还会弹出一个警告对话框,可以忽略之。

之后所有的原件就导入进来了,如下图所示,此时元件是堆放在一起的:执行命令:“工具/分散元器件”,之后元器件被分散开来,如下图所示:这样,就完成了PCB的导入,之后可以进行布线工作。

3、更新原理图中修改的网表。

在PCB布线的时候可能会修改原理图中的部分器件或者连线,这时候就要进行网表更新。

步骤如下:a、更改好原理图之后,重新生成网表,然后新建一个空的PCB文件,给这个pcb文件起一个名字(名字随便起),这里就叫做temp.pcb.b、打开temp.pcb文件,执行"文件/导入"命令,导入新生成的.asc网表,之后关闭temp.pcb。

cadence按分页编号

cadence按分页编号

Cadence按照分页进行元器件编号

如果没有分裂元件直接按照分组来做就可以了(已在16.5版本验证,测试通过),注意红色框的地方,如果没有分裂元件第3,5个框不用管(从上往下数,备注:16.5无第五个框),如果有分裂元件,则编号后手动改一下即可。

2. 如果有分裂元件则上面的步骤会提示出错

ERROR(ORCAP-1376): Cannot perform annotation of heterogeneous part

'U?A(Value MCP6004) at location (4.00, 5.30) on page

alternating_current_filter', part has not been uniquely grouped (using a common User Property with differing Values) or the device designation has not been chosen

INFO(ORCAP-1379): Done updating part references

这种情况下需要给元件添加一个额外的属性来让cadence知道哪几个分裂元件是同一个器件

打开这个分裂元件的库文件,双击器件出现下面的对话框,然后点“new”新建一个package,值填1即可

3. 在原理图里设置package

把属于一个器件上的分裂器件的部分设置成同样的标号,同时注意上面第一步里的第3,5个红框也要修改,第三个红框是刚才加的这个属性:package,第五个框勾选就可以了

现在应该可以正确的按页编号显示标号了。

在OrcadCadence中修改原理图页码

我直接在要修改的原理图上右键——Schematic Page Properties,出来的窗口选择Miscellaneous,出现了Page Number,但是这里并不能修改。

在网上搜索一番以后,出现的大都是在off-page connector后面添加导向页码的方法,而且可以看出,大都是相互复制粘贴的。

-----------------------------------------题外话----------------------------------------在这里插一句题外话,如果要复制别人的文章,拜托在题目前面加上【转载】嘛!尊重一下别人的知识产权。

再不济,实在不好意思的话,请把图片也复制过来好吗??发了一大堆见下图,如图1.2所示,结果完全没有图片。

发这样没有意义的文章简直是侮辱自己的智商。

----------------------------------------------------------------------------------------好了言归正传,既然在网上找不到办法,那只好去请教经理了。

经理教我:先选择要修改的原理图工程,点Edit菜单,选Browse——Titleblocks,在弹出的对话框上如图选择,点OK。

看到下图的表格了吗?Page Number在向我们招手咯,但这里还不能修改,选中所有的原理图,点Edit——Properties,弹出下下图的表格,在这里我们就可以修改啦。

先不要急!在这里我们会看到四组数据,分别是Schematic Page Number、Schematic PageCount、Page Number和Page Count,都要按照实际修改才可以,否则会报错。

修改完毕,点击左下角的OK,现在所有的页码就都设置完毕了。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

Cadence按照分页进行元器件编号

如果没有分裂元件直接按照分组来做就可以了(已在16.5版本验证,测试通过),注意红色框的地方,如果没有分裂元件第3,5个框不用管(从上往下数,备注:16.5无第五个框),如果有分裂元件,则编号后手动改一下即可。

2. 如果有分裂元件则上面的步骤会提示出错

ERROR(ORCAP-1376): Cannot perform annotation of heterogeneous part

'U?A(Value MCP6004) at location (4.00, 5.30) on page

alternating_current_filter', part has not been uniquely grouped (using a common User Property with differing Values) or the device designation has not been chosen

INFO(ORCAP-1379): Done updating part references

这种情况下需要给元件添加一个额外的属性来让cadence知道哪几个分裂元件是同一个器件

打开这个分裂元件的库文件,双击器件出现下面的对话框,然后点“new”新建一个package,值填1即可

3. 在原理图里设置package

把属于一个器件上的分裂器件的部分设置成同样的标号,同时注意上面第一步里的第3,5个红框也要修改,第三个红框是刚才加的这个属性:package,第五个框勾选就可以了

现在应该可以正确的按页编号显示标号了。