USB 2.0 硬件设计

基于DSP和Slave FIFO的USB2.0接口硬件电路设计

将数据 发送至接收端 , 这种方式传输时间长, 传输速度 低, 传输过程 中 大 量 占 用 D P 源 , 低 了DS S 资 降 P运 算 效 率 。 接 口设 计 中 , 用 本 利 DP S 片上资源采用直接存储器访 问( MA) D 方式 , 直接将数据在D P S 片外存储器与接 收端 之间传输 , 有效地解 决了传输瓶颈 问题 , 提高 了数 据 传 输 速 度 , 时 数据 传 输 过 程 中无 需 占用 D P 同 S 资源 , 高 了 提 D P 运算 能力 。 S的 本 接 口 中D P 其 周 边 电路 主 要 包 括 D P、 DRAM存 储 器 、 S 及 S S Fah ls 存储器及D P S 电源监控芯片 、 式配置 电路等 。 模 在设 计中使用 DP S 信号线 C [:】 E3 0将片外存储器 分为多个存储 空 间, 分别对 应不 同存储器 , 并通过片上E F 口( MI接 外部存储器接 口) 实现 电气连接 。

应 用 研 究

基于 DS P和 Sa eF F lv I O 的 U B . 接 口硬件电路设计 S 20

廉 平 平

( 台工程 职 业技 术 学 院 山 东烟 台 240) 烟 606

摘要 : 文介 绍 了一 种基 TDS 和S v I O的US 2 0 口硬 件 电路设 计 。 对数 据传 输瓶 颈 f 题 , 计采 用DS 直接 存 储 器访 问( 本 P l eFF a B .接 针 " 设 - I P DMA ) 数 据 传输 方 式 , 实现 了一个 T -作 于 实 时信 号处理 系统 中,US 20 口。 V - g B .接 / 该接 口 用SaeFF 使 l IO ̄ 口进 行 通信 , v 可以有 效 利 用us 协议 带 宽 , B 提 高数 据 传 输 速 率 , 有较 高 的 实 用价 值 。 具

USB2.0接口中固件、软件的设计

USB2.0接口中固件、软件的设计摘要:本文介绍了一种usb2.0接口中的微控制器固件和pc机软件设计。

根据usb2.0协议特点,本文在固件设计中采用usb批量传输方式,在实现usb2.0协议通信的同时,有效地利用了usb协议带宽;同时在软件设计中采用多线程编程技术,较好地实现了界面显示和程序数据交互,具有较高的实用价值。

关键词:usb2.0接口批量传输多线程中图分类号:tp313 文献标识码:a 文章编号:1007-9416(2012)02-0084-021、引言usb2.0接口是一种实现usb2.0协议通信的计算机外围接口设备,具有支持热插拔、即插即用、通信可靠、数据传输速率高等优点,在实际生产生活中得到了广泛应用,一般由固件、软件和硬件电路组成。

其中的固件是固化在集成电路内部的“软件”,通常存储于eprom或flash存储器中,负责usb2.0接口最基础、最底层的工作。

它和负责上层工作的软件一起构成了接口的灵魂,很大程度上决定了接口的功能和性能。

因此固件和软件的设计一直是usb2.0接口开发中的重点与难点。

2、usb2.0协议usb,即通用串行总线,是一种标准的连接接口,支持pc主机同时连接多个外部接口设备。

其最初于1995年由compaq、ibm、intel、microsoft等七个计算机与通信工业领先的公司所组成的联盟定义和加以推广。

相比较旧的usb1.1标准,usb2.0标准在兼容1.1规范中的低速设备和全速设备的基础上新加入了高速设备,最大传输速度可达到480mbps。

usb的总线结构采用阶梯式星形的拓扑结构,包括usb host(主机)与usb设备。

其中,usb设备包含usb hub(集线器)与usb node (功能设备)两种类型。

在总线结构中,任何usb系统中只能有一个usb主机,位于总线结构最顶端。

usb主机往下可连接usb集线器,再由集线器按阶梯式的方式往下扩展出去,连接到下一层,总线结构允许的最大阶梯层数是7层。

USB2.0中物理层接口的设计

USB2.0中物理层接口的设计

USB(Universal Serial Bus)是一种用于连接计算机和外部设备的通用接口标准。

USB接口的设计包括物理层、数据链路层、网络层和传输层等多个方面,其中物理层接口设计是USB通信的基础。

USB2.0是USB接口的一种版本,具有更高的传输速度和更好的兼容性。

在USB2.0中,物理层接口的设计是为了提供可靠的数据传输和稳定的电力传输。

该设计的目标是在不增加成本和复杂性的情况下,提供更高的传输速度和更好的性能。

USB2.0物理层接口的设计使用了差分信号传输技术。

差分信号传输技术通过同时传输正负两个相等但反相的电信号来传输数据。

这种设计可以有效地抵抗电磁干扰和噪声,提高数据传输的可靠性和稳定性。

在物理层接口设计中,USB2.0还使用了多级信号放大器和等化器等技术来增强信号的强度和稳定性。

多级信号放大器可以增加信号的幅度,提高传输距离和速度。

而等化器可以对信号进行补偿,消除传输过程中的失真和衰减,确保数据的完整性和准确性。

此外,USB2.0物理层接口的设计还考虑了功耗和供电问题。

USB2.0接口提供了两个供电线路,分别用于传输数据和提供电力。

这样可以避免数据传输对供电造成的干扰,保证设备的正常工作。

USB2.0中物理层接口的设计不仅仅关注了传输速度和性能,还考虑了可靠性、稳定性和兼容性等方面。

通过使用差分信号传输技术、多级信号放大器和等化器等技术,USB2.0接口能够在不增加成本和复杂性的情况下提供更好的数据传输和电力传输能力。

这些设计的应用使得USB2.0成为一种被广泛应用于计算机和外部设备连接的通用接口。

USB2.0摄像头微处理器硬件设计,USB2.0,摄像头,微概要

USB2.0摄像头微处理器硬件设计,USB2.0,摄像头,微处理器,图像后处理单元1.引言USB2.0摄像头微处理器支持高速USB2.0接口,内嵌强劲的图像后处理单元,JPEG高速编译码器,支持高达200万像素的CMOS传感器接口和CCD传感器接口,处理器设计的产品可以实现独特的运动监测功能与脸部追踪功能,这不仅大大加强了显示效果,提高了画面的品质,更拓展了PC摄像头的应用领域,如增强的实时视频聊天功能和门禁监测系统。

主要功能:USB2.0高速传输并兼容USB1.1;高速图像后处理单元;JPEG高速编译码器;VGA下30帧/秒1.引言USB2.0摄像头微处理器支持高速USB2.0接口,内嵌强劲的图像后处理单元,JPEG高速编译码器,支持高达200万像素的CMOS传感器接口和CCD传感器接口,处理器设计的产品可以实现独特的运动监测功能与脸部追踪功能,这不仅大大加强了显示效果,提高了画面的品质,更拓展了PC摄像头的应用领域,如增强的实时视频聊天功能和门禁监测系统。

主要功能:USB2.0高速传输并兼容USB1.1;高速图像后处理单元;JPEG高速编译码器;VGA下30帧/秒高速传输;CMOS/CCD接口;内置8比特微控制器。

不仪具备以上的先进特性,还拥有以下多种可扩展性:多个GPIO接口为增加连拍、LED指示灯、快捷键等功能提供了无限可能;USB2.0兼容USB1.1,为摄像头的广泛的使用增加了保障;支持多种操作系统,如64-bit Window,Windows XP,Linux,Mac,VxWorks,WinCE等等。

以下就是对USB2.0摄像头微处理器的硬件设计方法及外围电路分布的介绍。

2.系统硬件设计2.1 振荡器USB2.0摄像头微处理器的钟频是12MHz,外部时钟频率稳定性必须小于±50ppm。

图1是振荡器电路的设计参考图。

2.2 复位上电后,复位信号必须在低设置处停上最少10ms,才能使来自振荡器的信号稳定。

USB2.0接口EMC设计方案

USB2。

0接口EMC设计方案一、接口概述USB 通用串行总线(英文:Universal Serial Bus,简称USB)是连接外部装置的一个串口汇流排标准,在计算机上使用广泛,但也可以用在机顶盒和游戏机上,补充标准On—The—Go ( OTG)使其能够用于在便携装置之间直接交换资料。

USB接口的电磁兼容性能关系到设备稳定行与数据传输的准确性,赛盛技术应用电磁兼容设计平台(EDP)软件从接口原理图、结构设计,线缆设计三个方面来设计USB2.0接口的EMC设计方案二、接口电路原理图的EMC设计本方案由电磁兼容设计平台(EDP)软件自动生成1. USB2.0接口防静电设计图1 USB 2。

0接口防静电设计接口电路设计概述:本方案从EMC原理上,进行了相关的抑制干扰和抗敏感度的设计;从设计层次解决EMC 问题。

电路EMC设计说明:(1)电路滤波设计要点:L1为共模滤波电感,用于滤除差分信号上的共模干扰;L2为滤波磁珠,用于滤除为电源上的干扰;C1、C2为电源滤波电容,滤除电源上的干扰。

L1共模电感阻抗选择范围为60Ω/100MHz ~120Ω/100MHz,典型值选取90Ω/100MHz;L2磁珠阻抗范围为100Ω/100MHz ~1000Ω/100MHz,典型值选取600Ω/100MHz ;磁珠在选取时通流量应符合电路电流的要求,磁珠推荐使用电源用磁珠;C1、C2两个电容在取值时要相差100倍,典型值为10uF、0。

1uF;小电容用滤除电源上的高频干扰,大电容用于滤除电源线上的纹波干扰;C3为接口地和数字地之间的跨接电容,典型取值为1000pF,耐压要求达到2KV以上,C3容值可根据测试情况进行调整;(2)电路防护设计要点D1、D2和D3组成USB接口防护电路,能快速泄放静电干扰,防止在热拔插过程中产生的大量干扰能量对电路进行冲击,导致内部电路工作异常.D1、D2、D3选用TVS,TVS反向关断电压为5V;TVS管的结电容对信号传输频率有一定的影响,USB2。

USB2.0主机端控制器协议层的设计及实现

USB2.0主机端控制器协议层的设计及实现摘要:本文简要介绍了USB 2.0协议层的通信原理,描述了USB 2.0主机端控制器核心部分的划分、设计及实现。

通过Cadence公司的NCSim 进行了软件仿真,最后在XILINX公司的FPGA上加以了验证,结果符合USB 2.0协议要求。

关键词:USB2.0;协议层;状态机引言USB(Universal Serial Bus)是当今流行的一种PC外围设备接口标准[1]。

它具有即插即用、可热插拔等的优点,在实际应用中连接简单、使用方便。

本文简要介绍了USB 2.0协议层的通信原理,并根据USB 2.0协议规范,利用Verilog硬件描述语言完成了主机端控制器协议层的设计,通过Cadence公司的NCSim进行软件仿真之后,在XILINX公司的Virtex xcv300efg456-6芯片上进行了验证。

1 协议层通信原理USB接口是以令牌包(token-based) 为主的总线协议,PC主机掌握着总线的一切主控权[1],除令牌包外,还有数据封包、握手封包、特殊封包等。

令牌包还可细分为OUT、IN、SETUP、SOF等4种封包格式,其他几个封包也同样可以细分为多种封包格式。

在USB的传输中,每一个传输包含一笔或多笔事务,每一笔事务包含一到三个封包[2]。

USB有4种传输类型:控制传输、批量传输、中断传输和实时传输,每种传输类型用以处理不同的需求。

具体来讲,批量传输类型用于对时间要求不严格的数据传输,可以发送大量数据而不会阻塞总线,并能通过错误检测和重试的方式保证主机和功能部件之间数据的无错发送。

控制传输模块用以发送与设备的能力和配置有关的请求和数据,也可传输任何其他用途的信息块。

中断传输类型适用于在一个规定的时间里传输一个中等数量的数据,通常应用在键盘、鼠标、其他指针设备和集线器的状态报告中,中断传输令设备引起硬件中断,将使计算机产生一个快速响应。

实时传输类型是对数据以一个恒定的速率或在规定时间内完成的传输,仅包含令牌和数据两个时相,而不包含握手时相,因此不具备错误校正的能力,所接收的信息偶尔会包含少量的错误。

基于USB2.0的高性能移动存储设备的设计

基于USB2.0的高性能移动存储设备的设计

1.引言

闪存盘(FLASH MEMORY)是USB 接口的一种典型应用,1999 年朗科研发出全球第一款USB 闪存盘,成功启动了全球闪存盘行业。

由于闪存是

一种基于半导体的存储器,信息在断电后可以保存,并且还具有低功耗、速度快、可擦写性、高可靠性、低成本等特点,是高数据存储密度的最佳选择,在

外部存储领域、嵌入式系统、工控行业和信息家电业得到广泛使用,如手机、

数码相机、MP3 等。

市场上的FLASH 有多种技术来实现,其中最常用的有NAND(与非)和NOR(异或)两种。

武汉电离层观象台的高频多普勒与到达角探测分析系统在投入实际观测后,获得了一些很重要的观测数据[1],该系统的数据采集单元采用闪存作为数

据移动存储设备,实现与计算机的信息交互,完成数据的分析与处理。

本文所

讨论的NAND FLASH 存储器与USB2.0 控制器的硬件连接和软件编程方法,在研究开发USB 移动存储器使其更稳定安全地工作,具有重要的价值。

本文

首先介绍移动存储设备的硬件设计部分,重点讨论了该移动存储设备的硬件接

口设计,继而给出固件程序的编程方法。

其中设备固件的编写是本设计的重点。

2.硬件实现

本移动存储设备的USB2.0 控制器采用ATMEL 公司的AT89C5131 芯片,数据存储介质采用SAMSUNG 公司的NAND FLASH 芯片K9K2G08U0A。

2.1 AT89C5131 芯片特点

AT89C5131 是ATMEL 公司生产的基于80C52 内核的高性能内置全速USB 控制器的8 位单CPU 微处理芯片[2],直接与MCS-51 系列兼容,其内部。

USB 2.0 板载设计及布线指南

应用报告ZHCA059–2007 年 12 月USB 2.0 板载设计及布线指南DSP 应用摘要本文档探讨了通用串行总线(USB)系统原理图设计的若干指导方针。

背景在 USB 设计中,时钟频率提供了主要的信号源。

USB 差分 DP/DM 对可工作于 480Mbps 的高速模式,系统时钟可工作于 12 MHz 、48 MHz 及 60 MHz 。

由于 USB 电缆扮演了单极天线的角色,因此必须小心设计以防止 RF 电流耦合至缆线上。

设计 USB 板载时,最关注的信号有:器件接口信号:时钟及其他信号/数据,通过走线在器件与 PCB 之间传输。

缆线输入/输出供电:USB 连接器插槽的引脚 1(VBUS)可能被严重滤波,仅可通过低于 100 KHz 的低频信号。

USB 插槽的引脚 4(模拟地)必须能够返还(return)数据传输期间的电流,且必须进行基本的滤波。

通过缆线、DP 及 DM 输出出的差分双铰线对信号:依据数据传输率的不同,这些器件的终端引脚上可给出带 240MHz (高速)、6MHz (全速)、750kHz (低速)基频的信号。

外部晶振电路(器件终端引脚 XI 及 X0):12MHz 、19.2MHz 、24MHz 、48MHz 基频。

如果使用外接晶体作为参考时钟,强烈推荐采用 24MHz 及 更高基频的晶振。

••••1目录1 背景12 USB 物理层(PHY)布线指南 23 静电放电(ESD) 84参考文献10图表目录1 推荐的电容及铁氧体磁珠阵列,以实现电磁干扰的最小化 22 四层板堆叠 33 USB 连接器 44 3W 间隔规则45 至 USB 物理层的电源及时钟连接 56 USB 物理层连接器及缆线连接器 67 避免跨层边界走线 78 避免层交叠 79避免损坏镜像层8separated by a groundSignal�1GND�PlanePower�PlaneSignal�2USB物理层布线指南U2Ferrite�BeadVBUSU1USB�Socket543216SHIELD_GND GND DP DM+5�VSHIELD_GNDFerrite�Bead2.2.5Clock Routings Trace3W3WWUSB PHY Layout GuideFigure B ConnectorTo address the system clock emissions between devices,place a ~10to 130Ωresistor in series with the clock e a trial and error method of looking at the shape of the clock waveform on a high-speedoscilloscope and of tuning the value of the resistance to minimize waveform distortion.The value on this resistor should be as small as possible to get the desired effect.Place the resistor close to the device generating the clock signal.If an external crystal is used,follow the guidelines detailed in the Selection and Specification of Crystals for Texas Instruments USB 2.0Devices (SLLA122).When routing the clock traces from one device to another,try to use the 3W spacing rule.The distance from the center of the clock trace to the center of any adjacent signal trace should be at least three times width of the clock trace.Many clocks,including slow frequency clocks,can have fast rise and falling the 3W rule cuts down on crosstalk between traces.In general,leave space between each of the traces running parallel between the devices.Avoid using right angles when routing traces to minimize the routingdistance and impedance discontinuities.For further protection from crosstalk,run guard traces beside the clock signals (GND pin to GND pin),if possible.This lessens clock signal coupling,as shown in Figure 4.Figure 4.3W Spacing RuleU2Ferrite�BeadVBUSU1USB�Socket543216SHIELD_GNDGNDDP DM +5�V SHIELD_GND Ferrite�Bead2.2.5Clock RoutingsTrace 3W 3W WUSB PHY Layout Guide Figure B Connector To address the system clock emissions between devices,place a ~10to 130Ωresistor in series with theclock e a trial and error method of looking at the shape of the clock waveform on a high-speed oscilloscope and of tuning the value of the resistance to minimize waveform distortion.The value on this resistor should be as small as possible to get the desired effect.Place the resistor close to the device generating the clock signal.If an external crystal is used,follow the guidelines detailed in the Selection and Specification of Crystals for Texas Instruments USB 2.0Devices (SLLA122).When routing the clock traces from one device to another,try to use the 3W spacing rule.The distance from the center of the clock trace to the center of any adjacent signal trace should be at least three times the width of the clock trace.Many clocks,including slow frequency clocks,can have fast rise and fall ing the 3W rule cuts down on crosstalk between traces.In general,leave space between each of the traces running parallel between the devices.Avoid using right angles when routing traces to minimize the routing distance and impedance discontinuities.For further protection from crosstalk,run guard traces beside the clock signals (GND pin to GND pin),if possible.This lessens clock signal coupling,as shown in Figure 4.Figure 4.3W Spacing Rule时钟走线为满足系统器件间时钟辐射的需求,须安置约 10 至 130 W 的电阻与时钟信号串联。

USB2.0摄像头微处理器硬件设计及外围电路分布

U B 3. V i { a P w r S 3 D g t I o e L 1 8 1 L P w r ' SB . V ) i a1 o e

L B D gi aj r u d 。 j G o n S t

P P

P

l 8 l g

2 0 2

U B VD A S D

U B .接 口; E R M接 口; S2 0 EPO 传感器接 口; 其它功能

类 型 引脚 ( J) I\

J 3 I

2J

信 号描述

U I . V A aI g o r S3 3 3 n o P we

PN接 口和 U B . C I S 20P B排版 。

2 系 统硬 件 设 计 .

2 1 振 荡 器 .

U B. S 20摄像 头微 处 理器 的钟频 是 1MH , 外 2 z 部时 钟频 率稳 定性 必须小 于 ±5p m。 图 1 0p 是振 荡

图 2 复位 电路

k ● ●^

,^ …

^…

: …

…

维普资讯

I0 g o n / rud

P

3 0 7

E P O 接 口如表 3所示 。 ER M

如需要添加新 的 V D和 PD或 传感器配置, I I 则

需用 一个 2 一线 串行 E P O E R M。 图 5是 E P O E R M

DD V Dl

C r p w r o e o e

J 7 UB V S S S A [S r o ( o n B A aI g ; u d i r l

2 2

3 1 S2 0 接 口 . U B .

U B . 口如表 2 示 。 S 2B D). S V I !

硬件设计:接口--USB2.0电路设计

硬件设计:接⼝--USB2.0电路设计参考资料:⼀、USB2.0物理特性 1.1、USB接⼝ USB连接器包含4条线,其中VBUS、GND⽤于提供5V电源,电流可达500mA;⽽D+、D-⽤于USB数据传输。

D+、D-是⼀组差分信号,差分阻抗为90欧,具有极强的抗⼲扰性;若遭受外界强烈⼲扰,两条线路对应的电平会同时出现⼤幅度提升或降低的情况,但⼆者的电平改变⽅向和幅度⼏乎相同,所以两者之间的电压差值可始终保持相对稳定。

扩展:USB OTG(即USB On-The-Go)技术在完全兼容USB2.0标准的基础上,增添了电源管理(节省功耗)功能,它允许设备既可作为主机,也可作为外设操作,实现了在没有主机的情况下,设备与设备之间的数据传输。

例如数码相机直接连接到打印机上,通过OTG技术,连接两台设备间的USB⼝,将拍出的相⽚⽴即打印出来。

USB OTG接⼝中有5条线: 2条⽤来传送数据D+ 、D-; 2条是电源线VBUS、GND; 1条是ID线,⽤于识别不同的电缆端点,mini-A插头(即A外设)中的ID引脚接地,mini-B插头(即B外设)中的ID引脚浮空。

当OTG设备检测到接地的ID引脚时,表⽰默认的是A设备(主机),⽽检测到ID引脚浮空的设备则认为是B设备(外设)。

1.2、反向不归零编码(NRZI) 反向不归零编码(Non Return Zero Inverted Code)的编码⽅式⾮常简单,即⽤信号电平的翻转代表“0”,信号电平保持代表“1”。

这种编码⽅式既可以保证数据传输的完整性,还不需要传输过程中包含独⽴的时钟信号,从⽽可以减少信号线的数量。

但是当数据流中出现长“1”电平时,就会造成数据流长时间⽆法翻转,从⽽导致接收器丢失同步信号,使得读取的时序发⽣严重的错误;所以在反向不归零编码中需要执⾏位填充的⼯作,当数据流中出现连续6个“1”电平就要进⾏强制翻转(即⾃动添加⼀位“0”电平),这样接收器在反向不归零编码中最多每七位就会出现⼀次数据翻转,从⽽保证了接收器的时钟同步,同时接收器端会扔掉⾃动填充的“0”电平,保证了数据的正确性(即使连续6个“1”电平后为“0”电平,NRZI仍然会填充⼀位“0”电平); USB的数据包就是采⽤反向不归零编码⽅式,所以在总线中不需要时钟信号。

USB2.0主控器软硬件协同仿真系统设计

( 中国 海 洋 大 学 信 息科 学 与 工程 学 院 ,山东 青 岛 2 60 ) 6 1 0

摘 要 :为 了能 够 充 分 、 速 验 证 US . 快 B2 0主 控 器 的 功 能 , 计 了一 个软 硬 件 协 同仿 真 平 台 。其 中 , P 模 型 部 分 采 用 设 CU

使 软 件 人 员 能在 I P的硬 件 验 证 阶段 就 能 完成 软 件 的设 计 测 试 工 作 , 缩短 软 硬 件 接 口整 合 时 间 , 快 开发 进 度 。 加 关 键 词 : 硬 协 同 ; 合 仿 真 引 擎 ; P 模 型 ;通 用 串行 总线 ;主控 器 ;片上 系统 软 联 C U 中 图 分 类 号 : N9 93 T 1—4 文献标识码 : A 文 章 编 号 :043 3 2 1 ) 20 6—3 1 0 -7X(0 2 0 —100

21 年 1 l 02 月 5日 第 3 第 2期 5卷

现 代电 子技术

M o e n Elc r n c c n q e d r e to isTe h iu

J n 2 1 a . 0 2 Vo . 5 No 2 13 .

U B2 0主控器软硬件协 同仿真 系统设计 S .

to l r n t i p a f r ,a fiin y t mC mo e s a o td f r C r l .I h s lto m e n e f e tS s e d li d p e o PU d li s e d o h n tu t n s t b s d c mp e c mo e n t a ft e i s r c i e a e o lx o C PU d 1 Te tc s s a e wr e t h i h ra s r c in lv l a g a e mo e. s a e r i n wih t e h g e b t a to e e ln u g ,wh c e f r h t t C i h p ro ms t e s i l s g n r t n a d mu u e e a i n o r s o s h c i g t r u h c l n h Ip o i e y t esm ua in p a f r e p n e c e k n h o g a l g t e AP r vd d b h i l t l to m.Th i u a in r s l s o h tt i t o i o esm l t e u t h ws t a h sme h d o c n e f c ie y rd c h c u a i n o i lt n r s u c n h i l t n t . M e n a fe t l e u et e o c p to fsmu a i e o r e a d t e smu a i i v o o me a wh l ,i e a ls t e s f wa e d — i e t n be h o t r e sg e s t u f h o t r e u g n a d r e i c t n p a e O a o s o t n t e i t g a i n t f h r wa e a d i n r o f li t e s fwa e d b g i g i h r wa e v rf a i h s ,S s t h r e h n e r t i o a d r n l n i o o me

USB2.0整体框架的设计

一、usb系统的组成1、硬件2、软件1.1、硬件usb主机控制器usb设备控制器root hub普通usb hubusb设备(U盘,usb鼠标,usb摄像头等)usb线(四根线,VBUS,GND,D+,D-)上面的这些硬件设备组成了usb的拓扑结构,usb树。

下面简要的说下这些硬件的关系:usb主机控制器:就是usb host,典型的就是PC机上的usb控制器,有三大类包括OHCI,UHCI,EHCI,XHCI等.Usb设备控制器:一般运行Linux系统的设备,要想作为一个usb外设(比如你的手机插入到PC上作为一个U盘),就要有一个usb设备控制器。

OTG控制器:在支持OTG设备的系统中决定是启动主机控制器还是设备控制器。

Root hub:通常usb主机控制器和root hub集成到一起。

usb设备:就是咱们通常用的U盘,usb鼠标,usb摄像头等。

usb线:通常usb线是四根,VBUS,GND,D+,D-,但支持OTG的设备还有第五根ID 引脚。

四根线的颜色分别为:红色为VBUS,黑色GND,白色为D-,绿色为D+,,D+和D-是差分输入线,它使用的是3.3V的电压(注与CMOS的5V电平不同),而电源线和地线可向设备提供5V 电压,在没有配置的时候最大能提供100mA的电流,在配置完成时最大提供500mA的电流。

下面看下普通的usb线:下面是普通的usb集线器的图:其中包含了状态变化端点和用于控制的端点0下面是高通的8x60芯片中的USB模块,该usb模块是在嵌入式soc内部的:对于普通的PC 机,usb 控制器在在主板上单独的一个芯片:Usb主机控制器就挂到pci总线上.下面看下usb主机控制器和你的usb设备的什么器件通讯,也就是他们之间的通信管道。

不管任何usb设备在设备硬件上都有叫端点的东西,可以理解为usb设备通讯的buffer,并且这些端点都有地址编号。

实际的通信就是主机控制器和usb设备的这些端点通讯,这些端点的寻址是通过usb设备地址+端点地址唯一确定通讯地址的。

基于USB2.0的虚拟数字存储示波器硬件系统设计

签名:

日期:

年

月

日

关于论文使用授权的说明

本学位论文作者完全了解电子科技大学有关保留、 使用学位论文 的规定,有权保留并向国家有关部门或机构送交论文的复印件和磁 盘,允许论文被查阅和借阅。本人授权电子科技大学可以将学位论文 的全部或部分内容编入有关数据库进行检索,可以采用影印、缩印或 扫描等复制手段保存、汇编学位论文。 (保密的学位论文在解密后应遵守此规定) 签名:

II

目 录

目 录

第一章 引言 ............................................................................................................ 1 1.1 虚拟仪器概述.............................................................................................. 1 1.2 虚拟仪器发展状况...................................................................................... 2 1.3 选题背景及选题意义.................................................................................. 3 1.4 课题目标及论文主要研究内容.................................................................. 3 第二章 虚拟数字存储示波器硬件系统总体方案 ................................................ 5 2.1 总体设计方案.............................................................................................. 5 2.2 系统结构...................................................................................................... 6 2.2.1 模拟通道 ........................................................................................... 6 2.2.2 数据采集 ........................................................................................... 7 2.2.3 数据处理及存储 ............................................................................... 7 2.2.4 通用串行总线 ................................................................................... 7 2.2.5 电源模块 ........................................................................................... 8 第三章 硬件系统设计 ............................................................................................ 9 3.1 模拟通道电路设计...................................................................................... 9 3.2 数据采集及处理系统设计........................................................................ 16 3.2.1 关键器件的选型 ............................................................................. 16 3.2.2 并行采集电路 ................................................................................. 20 3.2.3 高速采样时钟 .................................................................................. 25 3.2.4 数据并行存储 ................................................................................. 28 3.3 FPGA 及外围电路 ..................................................................................... 36 3.4 DSP 处理电路设计 .................................................................................... 38 3.4.1 存储器扩展电路 ............................................................................. 38 3.4.2 JTAG 接口电路 ............................................................................. 40 3.5 USB2.0 硬件设计....................................................................................... 41 3.5.1 USB 总线特性 ................................................................................. 41 3.5.2 USB 接口芯片 ................................................................................. 42 3.5.3 USB 接口电路的实现 ..................................................................... 44

USB2.0设备控制器IP核的设计与FPGA验证的开题报告

USB2.0设备控制器IP核的设计与FPGA验证的开题报告一、研究背景USB(Universal Serial Bus)是一种外部总线接口,广泛用于现代电子设备之中,其使用方便、传输速度快、供电充足等特点,使其成为现代设备的标配之一。

USB接口的发展也在不断推进,USB2.0与USB3.0的出现更是实现了更高的传输速度。

本课题将重点研究USB2.0设备控制器IP核的设计与FPGA验证,旨在实现USB2.0接口的稳定、高效、可靠使用。

二、研究意义USB接口是现代电子设备中十分重要的一部分,与各类外设的连接都需要通过USB接口实现。

因此,一个稳定、高效、可靠的USB接口以及其相应的控制器至关重要。

而实现一个符合标准的USB控制器需要经过复杂的设计和验证,涉及到硬件电路和软件编码两个方面,同时需要对该控制器的功能、性能、稳定性等进行综合评估与测试。

因此,本课题的研究意义在于探索如何设计一种符合USB2.0标准的设备控制器IP 核,并进行FPGA验证,以便为现代电子设备的设计工作提供参考。

三、研究方法本课题将采用以下研究方法:1、深入学习USB2.0的标准及其相关协议,明确USB2.0接口和设备控制器的设计要求与规范。

2、了解现有的USB2.0设备控制器设计方案,分析其优缺点。

3、针对设计方案中存在的问题,提出自己的改进建议,并设计USB2.0设备控制器IP核。

4、进行IP核的仿真测试,在保证其符合USB2.0标准的基础上,优化其性能和稳定性。

5、将IP核与FPGA相结合进行验证实验,验证其在实际应用中的性能和可靠性。

四、研究内容和进展计划本课题的研究内容主要包括以下几个方面:1、USB2.0标准及协议的学习;2、现有USB2.0设备控制器设计方案的分析;3、USB2.0设备控制器IP核的设计;4、IP核的仿真测试和性能优化;5、IP核与FPGA相结合的验证实验。

本课题的进展计划如下:第一阶段:对USB2.0标准及协议进行深入学习,并研究现有的USB2.0设备控制器设计方案,制定解决问题的初步方案,计划在1个月内完成。

usb2.0通道设计标准

usb2.0通道设计标准USB 2.0是一种通信接口标准,下面我将从多个角度全面回答有关USB 2.0通道设计标准的问题。

USB 2.0通道设计标准涉及以下几个方面:1. 传输速度,USB2.0标准支持最高传输速度为480 Mbps(兆位每秒),相比USB 1.1的12 Mbps有了显著提升。

这种高速传输速度使得USB 2.0适用于大容量数据传输,如高清视频、音频和图像文件。

2. 物理接口,USB 2.0采用了四根线缆进行数据传输,包括两根用于数据传输(D+和D-),一根用于电源(VCC),以及一根用于地线(GND)。

这种物理接口设计使得USB 2.0在连接性方面更加稳定可靠。

3. 协议规范,USB 2.0通道设计标准定义了一套协议规范,用于控制和管理数据传输。

这些协议规范包括传输层协议(如传输控制协议和传输数据协议)、设备层协议(如设备描述符和配置描述符)以及应用层协议(如通信设备类协议和存储设备类协议)。

这些协议规范确保了USB 2.0设备之间的互操作性。

4. 电源管理,USB 2.0通道设计标准还包括了对电源管理的支持。

USB 2.0接口可以通过向设备提供电源来充电或供电。

此外,USB 2.0还支持挂起和恢复功能,可以在设备不使用时进入低功耗模式,以节省能源。

5. 兼容性,USB 2.0通道设计标准与之前的USB 1.1标准向下兼容,这意味着USB 2.0设备可以与USB 1.1设备进行通信。

然而,由于传输速度的差异,USB 2.0设备与USB 1.1设备之间的数据传输速度将受到限制。

总结起来,USB 2.0通道设计标准包括传输速度、物理接口、协议规范、电源管理和兼容性等方面。

这些标准的制定旨在提供高速、可靠的数据传输和设备互操作性。

通过遵循这些标准,USB 2.0设备可以在各种应用中广泛使用,如计算机、外部存储设备、打印机、数码相机等。

基于DSP和SlaveFIFO的USB2.0接口硬件电路设计

基于DSP和Slave FIFO的USB2.0接口硬件电路设计摘要:本文介绍了一种基于dsp和slave fifo的usb2.0接口硬件电路设计。

针对数据传输瓶颈问题,设计采用dsp直接存储器访问(dma)数据传输方式,实现了一个可工作于实时信号处理系统中的usb2.0接口。

该接口使用slave fifo端口进行通信,可以有效利用usb协议带宽,提高数据传输速率,具有较高的实用价值。

关键词:dsp slave fifo usb2.0接口中图分类号:tp334 文献标识码:b 文章编号:1007-9416(2012)01-0046-021、引言usb(通用串行总线)是一种电缆总线,支持主计算机与许多可同时访问的外设之间进行数据交换。

其相比传统的串口、并口,具有灵活方便、成本低、通信可靠、支持热插拔、即插即用等优点,在近些年得到了很大的发展,广泛应用于个人电脑及消费电子产品中,具有很高的实用价值。

尤其自usb2.0协议面世以来,其传输速率大幅提高到480mbps,特别适合应用于实时信号处理系统等高数率大容量场合。

由于目前实时信号处理系统在通信、图像、电力、雷达、控制等诸多领域得到了广泛应用,因此面向实时信号处理系统应用设计一种适应其应用特点的usb2.0接口具有比较重要的意义。

2、usb2.0接口硬件结构基于dsp和slave fifo本文设计了一种usb2.0接口,其硬件结构如图1所示。

该接口主要包括dsp、usb微控制器两部分。

在接口中,dsp实时处理前端输入信号,与pc机通过usb微控制器中的slave fifo实现双向usb2.0协议通信,并根据接收到的主机命令将需要的实时数据处理结果传送至pc机。

usb2.0接口硬件电路设计包括dsp、usb微控制器两部分,主要完成dsp、usb微控制器的配置及与其周边电子元件的电气互联。

3、dsp及其周边电路设计在实时信号处理系统中,dsp凭借丰富的寻址方式、内部资源及算法支持,主要应用于高速实时数据处理等场合。

USB 2.0的EMI和ESD设计

USB 2.0的EMI和ESD设计提供双向、实时数据传输的USB接口,以其即插即用、可热插拔和价格低廉等优点,目前已成为计算机和信息电子产品连接外围设备的首选接口。

时下流行的USB2.0具有高达480Mbps的传输速率,并与传输速率为12Mbps的全速USB1.1和传输速率为1.5Mbps的低速USB1.0完全兼容。

这使得数字图像器、扫描仪、视频会议摄像机等消费类产品可以与计算机进行高速、高性能的数据传输。

另外值得一提的是,USB2.0的加强版USB OTG可以实现没有主机时设备与设备之间的数据传输。

例如。

数码相机可以直接与打印机连接并打印照片,PDA可以与其它品牌的PDA进行数据传输或文件交换。

USB接口的传输速率很高,因此如何提高USB信号的传输质量、减小电磁干扰(EMI)和静电放电(ESD)成为USB设计的关键。

本文以USB2.0为例,从电路设计和PCB设计两个方面对此进行分析。

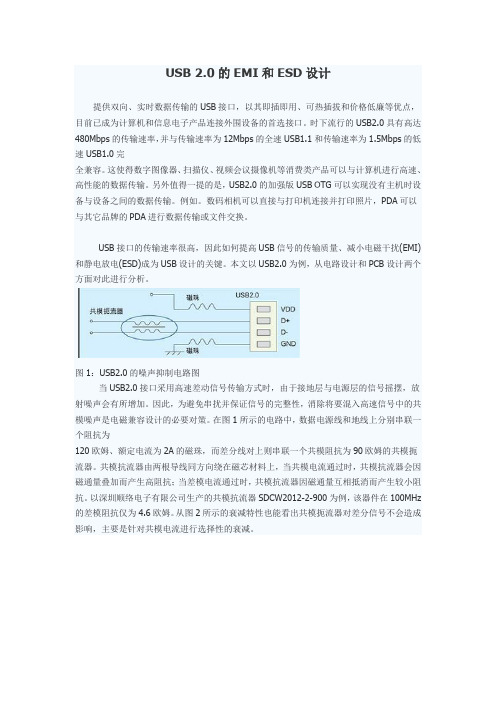

图1:USB2.0的噪声抑制电路图当USB2.0接口采用高速差动信号传输方式时,由于接地层与电源层的信号摇摆,放射噪声会有所增加。

因此,为避免串扰并保证信号的完整性,消除将要混入高速信号中的共模噪声是电磁兼容设计的必要对策。

在图1所示的电路中,数据电源线和地线上分别串联一个阻抗为120欧姆、额定电流为2A的磁珠,而差分线对上则串联一个共模阻抗为90欧姆的共模扼流器。

共模抗流器由两根导线同方向绕在磁芯材料上,当共模电流通过时,共模抗流器会因磁通量叠加而产生高阻抗;当差模电流通过时,共模抗流器因磁通量互相抵消而产生较小阻抗。

以深圳顺络电子有限公司生产的共模抗流器SDCW2012-2-900为例,该器件在100MHz 的差模阻抗仅为4.6欧姆。

从图2所示的衰减特性也能看出共模扼流器对差分信号不会造成影响,主要是针对共模电流进行选择性的衰减。

图2:SDCW2012-2-900的衰减频谱由于USB接口具有可热插拔性,USB接口很容易因不可避免的人为因素而导致静电损坏器件,比如死机、烧板等。

基于TMS320C32的USB2.0接口的软硬件设计

关键 词 : 用 串行 总线 ; 点 ; 举 ; D ( i d w 设 备驱 动 ) 通 端 枚 W M W o s n 中 图分 类 号 : P 0 T 32 文 献标 志码 : B

S fwa e a a d r sg f US . n e f c s d o TM S 2 C3 o t r nd H r wa e De i n o B20 I t r a e Ba e n 30 2

L U L. n, HA Ja - n I imi Z 0 in mig

( c o l f co lcrnc a d oi sae lcrnc , iest o e t nc ce c a d e h oo y Ch n d S h o o Miree t is n S l o d— tt E eto isUnvri f Elcr i S in e n T c n lg , e g u y o 6 0 5 C ia 1 0 4, hn )

收 稿 日期 : 0 6 1 — 4 修 订 日期 :0 7 0 — 20—20 : 20 — 6 0 4

摘 要 :在 讨 论 了通 用 US 2 器 件 C 7 8 0 主 要 特 征 的 基 础 上 ,详 细 阐 述 了 一 种 B. 0 Y C6 0 1 T 3 0 3 与C C 8 0 接 口的 软硬 件方 案 .并 对T 3 0 2 MS 2 C 2 Y7 6 0 1 MS 2 C3 与US 20 件接 口进 行 了 B. 硬 重 点 的论 述 , 出 了具 体 接 口电路 原理 图和 程 序 流 程 图 。 同时 , P 给 对 C端 驱动 程 序 框 架 以及 驱动 程 序 与 客 户 程 序 的接 口也 进 行 了论 述 。该 方 案 已经在 多款 虚 拟 仪 器 项 目得 到 应 用 , 取

USB2.0接口芯片系统架构设计与数字部分实现的开题报告

USB2.0接口芯片系统架构设计与数字部分实现的开题报告一、设计背景和目的随着人们对于高速、大容量数据存储需求的不断增加,USB2.0接口作为一种标准接口得到了广泛的应用。

本设计旨在设计一套完整的USB2.0接口芯片系统,包括了数字、模拟、射频等多个模块,以满足高速数据传输和稳定性的要求。

二、设计方法和步骤1. 系统架构设计本设计采用了分层设计的方式,将整个系统分为三个模块:数字模块、模拟模块和射频模块。

其中,数字模块包括控制器、缓存控制器、存储器等,模拟模块包括电源管理、时钟管理等,射频模块包括天线、射频前端等。

2. 数字部分实现数字部分大致包括控制器、缓存控制器、存储器等。

具体实现步骤如下:(1)控制器的设计控制器作为USB2.0接口芯片的核心,负责USB传输的整个控制和管理。

其主要包括以下功能:USB协议的解析、端点的管理和数据的收发控制等。

在设计时,需要考虑到控制器的复杂性和实时性,同时根据相关的规范和标准进行设计。

(2)缓存控制器的设计缓存控制器用于解决CPU与存储器之间速度不匹配的瓶颈,提高系统的整体效率。

其设计重点在于通过预读和缓存技术,有效地提高读写数据的速度和效率。

(3)存储器的设计存储器主要用于存储各种传输数据,在设计时需要考虑到数据容量和传输速度等因素。

一般采用高速SRAM或者SDRAM作为存储器。

三、预期结果和意义本设计旨在设计一套完整的USB2.0接口芯片系统,使之能够在高速数据传输和稳定性方面满足要求。

预期结果为:(1)实现一个稳定高效的USB2.0接口芯片系统;(2)提高USB数据传输的速度和效率;(3)降低USB接口芯片系统的成本。

本设计的意义在于,能够提高USB2.0的传输速度和效率,满足高速、大容量数据存储的需求。

同时,也能够为其他数字集成电路的设计提供借鉴和参考。

USB2.0接口EMC设计方案

电磁兼容设计平台(EDP)应用案例——以太网口USB2.0 接口 EMC 设计方案一、接口概述USB 通用串行总线(英文:Universal Serial Bus,简称 USB)是连接外部装置的一个串口汇流排标准,在计算机上使用广泛,但也可以用在机顶盒和游戏机上,补充标准On-The-Go ( OTG)使其能够用于在便携装置之间直接交换资料。

USB 接口的电磁兼容性能关系到设备稳定行与数据传输的准确性,赛盛技术应用电磁兼容设计平台(EDP)软件从接口原理图、结构设计,线缆设计三个方面来设计USB2.0 接口的 EMC 设计方案二、接口电路原理图的EMC设计本方案由电磁兼容设计平台(EDP)软件自动生成B2.0 接口防静电设计图1 USB 2.0接口防静电设计接口电路设计概述:本方案从 EMC 原理上,进行了相关的抑制干扰和抗敏感度的设计;从设计层次解决 EMC 问题。

电路 EMC 设计说明:(1)电路滤波设计要点:L1 为共模滤波电感,用于滤除差分信号上的共模干扰;L2 为滤波磁珠,用于滤除为电源上的干扰;C1、C2 为电源滤波电容,滤除电源上的干扰。

L1共模电感阻抗选择范围为60Ω/100MHz ~120 Ω /100MHz ,典型值选取90Ω/100MHz ;L2 磁珠阻抗范围为 100Ω /100MHz ~1000Ω /100MHz ,典型值选取 600Ω /100MHz ;磁珠在选取时通流量应符合电路电流的要求,磁珠推荐使用电源用磁珠;C1、C2 两个电容在取值时要相差 100 倍,典型值为 10uF、0.1uF;小电容用滤除电源上的高频干扰,大电容用于滤除电源线上的纹波干扰;C3 为接口地和数字地之间的跨接电容,典型取值为1000pF,耐压要求达到2KV 以上,C3 容值可根据测试情况进行调整;( 2)电路防护设计要点D1、 D2 和 D3 组成 USB 接口防护电路,能快速泄放静电干扰,防止在热拔插过程中产生的大量干扰能量对电路进行冲击,导致内部电路工作异常。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

作者:萧世文

出版社:清华大学出版社

ISBN:7-302-05937-3/TP.3528

出版时间:2002-10-1

内容提要

USB 是外围设备与计算机进行连接的快速且灵活的新式接口。本书介绍最新的 USB 2.0标准,从 USB 的基础开始介绍,包括实际的硬件与软件设计,并且使用汇编语言、Visual C++、Visual Basic 等来示范程序代码的编写。另外还有各种 USB 芯片介绍,帮助读者快速设计自己的 USB 设备。

目录

第1章 USB简介

第2章 SB传输

第3章 检测设备

第4章 控制传输

第5章 USB控制器芯片

第6章 Cypress enCoRe 控制器芯片

第7章 驱动程序

第8章 设备类别

第9章 设备测试

第10章 电源管理和信号编码

第11章 电路接口

第12章 集线器

第13章 HID设备

第14章 HID程序设计

附录 USB参考资料

本书共14章和1个附录,内容包括: USB 简介、 USB 传输、检测设备、控制传输、 USB 控制器芯片、Cypress enCoRe控制芯片、驱动程序、设备类别、设备测试、电源管理与信号编码、电路接口、集线器、HID设备、HID程序设计、HID设备开发实例以及 USB 参考资料等。

本书适合从事 USB 硬件、软件设计的程序员和其他相关技术人员使用或参考。