大规模集成电路一二章作业

集成电路设计与制造技术作业指导书

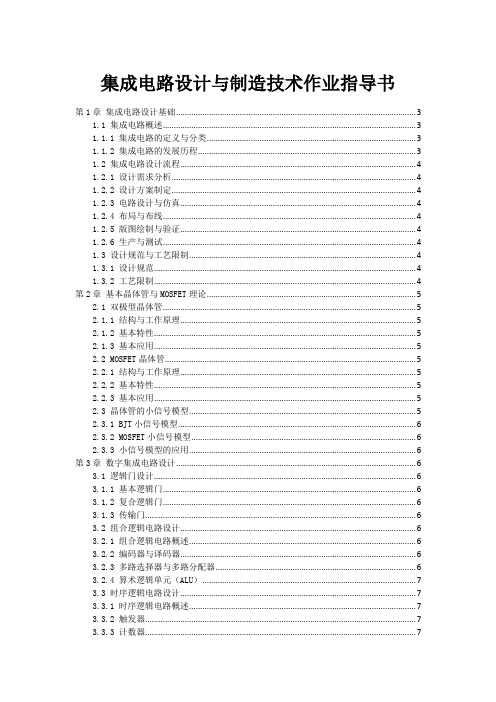

集成电路设计与制造技术作业指导书第1章集成电路设计基础 (3)1.1 集成电路概述 (3)1.1.1 集成电路的定义与分类 (3)1.1.2 集成电路的发展历程 (3)1.2 集成电路设计流程 (4)1.2.1 设计需求分析 (4)1.2.2 设计方案制定 (4)1.2.3 电路设计与仿真 (4)1.2.4 布局与布线 (4)1.2.5 版图绘制与验证 (4)1.2.6 生产与测试 (4)1.3 设计规范与工艺限制 (4)1.3.1 设计规范 (4)1.3.2 工艺限制 (4)第2章基本晶体管与MOSFET理论 (5)2.1 双极型晶体管 (5)2.1.1 结构与工作原理 (5)2.1.2 基本特性 (5)2.1.3 基本应用 (5)2.2 MOSFET晶体管 (5)2.2.1 结构与工作原理 (5)2.2.2 基本特性 (5)2.2.3 基本应用 (5)2.3 晶体管的小信号模型 (5)2.3.1 BJT小信号模型 (6)2.3.2 MOSFET小信号模型 (6)2.3.3 小信号模型的应用 (6)第3章数字集成电路设计 (6)3.1 逻辑门设计 (6)3.1.1 基本逻辑门 (6)3.1.2 复合逻辑门 (6)3.1.3 传输门 (6)3.2 组合逻辑电路设计 (6)3.2.1 组合逻辑电路概述 (6)3.2.2 编码器与译码器 (6)3.2.3 多路选择器与多路分配器 (6)3.2.4 算术逻辑单元(ALU) (7)3.3 时序逻辑电路设计 (7)3.3.1 时序逻辑电路概述 (7)3.3.2 触发器 (7)3.3.3 计数器 (7)3.3.5 数字时钟管理电路 (7)第4章集成电路模拟设计 (7)4.1 放大器设计 (7)4.1.1 放大器原理 (7)4.1.2 放大器电路拓扑 (7)4.1.3 放大器设计方法 (8)4.1.4 放大器设计实例 (8)4.2 滤波器设计 (8)4.2.1 滤波器原理 (8)4.2.2 滤波器电路拓扑 (8)4.2.3 滤波器设计方法 (8)4.2.4 滤波器设计实例 (8)4.3 模拟集成电路设计实例 (8)4.3.1 集成运算放大器设计 (8)4.3.2 集成电压比较器设计 (8)4.3.3 集成模拟开关设计 (8)4.3.4 集成模拟信号处理电路设计 (8)第5章集成电路制造工艺 (9)5.1 制造工艺概述 (9)5.2 光刻工艺 (9)5.3 蚀刻工艺与清洗技术 (9)第6章硅衬底制备技术 (10)6.1 硅材料的制备 (10)6.1.1 硅的提取与净化 (10)6.1.2 高纯硅的制备 (10)6.2 外延生长技术 (10)6.2.1 外延生长原理 (10)6.2.2 外延生长设备与工艺 (10)6.2.3 外延生长硅衬底的应用 (10)6.3 硅片加工技术 (10)6.3.1 硅片切割技术 (10)6.3.2 硅片研磨与抛光技术 (10)6.3.3 硅片清洗与检验 (10)6.3.4 硅片加工技术的发展趋势 (11)第7章集成电路中的互连技术 (11)7.1 金属互连 (11)7.1.1 金属互连的基本原理 (11)7.1.2 金属互连的制备工艺 (11)7.1.3 金属互连的功能评价 (11)7.2 多层互连技术 (11)7.2.1 多层互连的原理与结构 (11)7.2.2 多层互连的制备工艺 (11)7.2.3 多层互连技术的挑战与发展 (11)7.3.1 铜互连技术 (12)7.3.2 低电阻率金属互连技术 (12)7.3.3 低电阻互连技术的发展趋势 (12)第8章集成电路封装与测试 (12)8.1 封装技术概述 (12)8.1.1 封装技术发展 (12)8.1.2 封装技术分类 (12)8.2 常见封装类型 (12)8.2.1 DIP封装 (12)8.2.2 QFP封装 (13)8.2.3 BGA封装 (13)8.3 集成电路测试方法 (13)8.3.1 功能测试 (13)8.3.2 参数测试 (13)8.3.3 可靠性测试 (13)8.3.4 系统级测试 (13)第9章集成电路可靠性分析 (13)9.1 失效机制 (13)9.2 热可靠性分析 (14)9.3 电可靠性分析 (14)第10章集成电路发展趋势与展望 (14)10.1 先进工艺技术 (14)10.2 封装技术的创新与发展 (14)10.3 集成电路设计方法学的进展 (15)10.4 未来集成电路的发展趋势与挑战 (15)第1章集成电路设计基础1.1 集成电路概述1.1.1 集成电路的定义与分类集成电路(Integrated Circuit,IC)是指在一个半导体衬底上,采用一定的工艺技术,将一个或多个电子电路的组成部分集成在一起,以实现电子器件和电路的功能。

《超大规模集成电路设计》考试习题(含答案)完整版分析

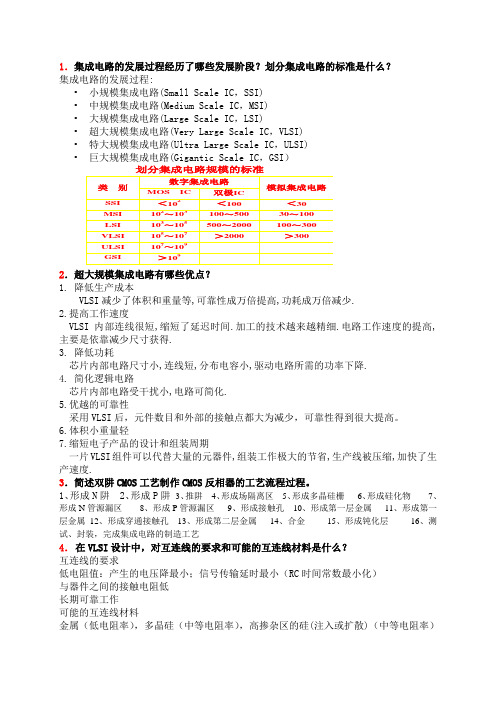

1.集成电路的发展过程经历了哪些发展阶段?划分集成电路的标准是什么?集成电路的发展过程:•小规模集成电路(Small Scale IC,SSI)•中规模集成电路(Medium Scale IC,MSI)•大规模集成电路(Large Scale IC,LSI)•超大规模集成电路(Very Large Scale IC,VLSI)•特大规模集成电路(Ultra Large Scale IC,ULSI)•巨大规模集成电路(Gigantic Scale IC,GSI)划分集成电路规模的标准2.超大规模集成电路有哪些优点?1. 降低生产成本VLSI减少了体积和重量等,可靠性成万倍提高,功耗成万倍减少.2.提高工作速度VLSI内部连线很短,缩短了延迟时间.加工的技术越来越精细.电路工作速度的提高,主要是依靠减少尺寸获得.3. 降低功耗芯片内部电路尺寸小,连线短,分布电容小,驱动电路所需的功率下降.4. 简化逻辑电路芯片内部电路受干扰小,电路可简化.5.优越的可靠性采用VLSI后,元件数目和外部的接触点都大为减少,可靠性得到很大提高。

6.体积小重量轻7.缩短电子产品的设计和组装周期一片VLSI组件可以代替大量的元器件,组装工作极大的节省,生产线被压缩,加快了生产速度.3.简述双阱CMOS工艺制作CMOS反相器的工艺流程过程。

1、形成N阱2、形成P阱3、推阱4、形成场隔离区5、形成多晶硅栅6、形成硅化物7、形成N管源漏区8、形成P管源漏区9、形成接触孔10、形成第一层金属11、形成第一层金属12、形成穿通接触孔13、形成第二层金属14、合金15、形成钝化层16、测试、封装,完成集成电路的制造工艺4.在VLSI设计中,对互连线的要求和可能的互连线材料是什么?互连线的要求低电阻值:产生的电压降最小;信号传输延时最小(RC时间常数最小化)与器件之间的接触电阻低长期可靠工作可能的互连线材料金属(低电阻率),多晶硅(中等电阻率),高掺杂区的硅(注入或扩散)(中等电阻率)5.在进行版图设计时为什么要制定版图设计规则?—片集成电路上有成千上万个晶体管和电阻等元件以及大量的连线。

超大规模集成电路第一章

人们总是需要更复杂的系统

S S I M S I

L S I

V L S I U L S I G S I

晶 体 管 数< 102 102~103 103~105 105~107 107~109 > 109

门 数 < 10 10~102 102~104 104~106 106~108 > 108

利用率高、速度快、功耗低的最优性能的芯片,但这种设计周期长、成本高,适用于要 求性能高或批量很大的芯片。 半定制设计:

半定制设计又可分为门阵列设计、标准单元设计、可编程逻辑器件设计。都是约束性 的设计方法,其主要目的就是简化设计,以牺牲芯片性能为代价来缩短开发时间

53

集成电路半定制设计方法+

门阵列设计 又称“母片”(Master Slice)法,是早期开发并得到广泛应用的ASIC技术,母片是IC工厂

EDA工具 ★ 电路分析、原理图设计、仿真、综合(可测性设计、功耗)、版图、时序分析等。

50

未来VLSI工艺已从深亚微米到超深亚微米迈进,对于功耗与速度提出了更高的要求。 互联——延迟,交扰,寄生等问题 功耗 复杂度——系统芯片,软硬件协同设计等

51

连线参数-

工艺特征等比改变时,连线的延迟基本不变。 ★ 沟道长度按等比因子缩小,因此晶体管开关延迟按因子减小。 ★ 电阻的长度按因子减小,但截面积按2减小,因此电阻按增大。 ★ 电容的平板面积按2减小,但中间绝缘层也按因子减小,因此电容按减小。

双极型RTL

nMOS

CMOS

26

VLSI中的低功耗

CMOS门电路需要的功耗比其它门电路小 尺寸是低功耗的本质因素

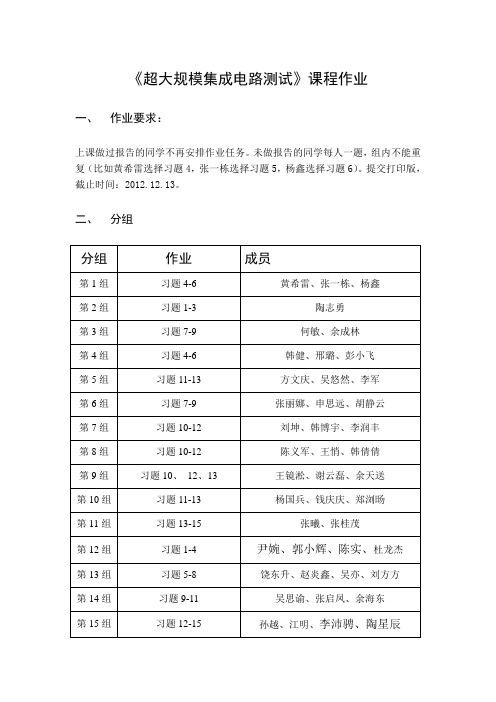

《超大规模集成电路测试》课程作业

《超大规模集成电路测试》课程作业一、作业要求:上课做过报告的同学不再安排作业任务。

未做报告的同学每人一题,组内不能重复(比如黄希雷选择习题4,张一栋选择习题5,杨鑫选择习题6)。

提交打印版,截止时间:2012.12.13。

二、分组三、《超大规模集成电路测试》课程习题1、对于图1的电路,计算组合SCOAP可测试性度量(可控制性和可观测性)图12、对于图2的电路,计算组合SCOAP可测试性度量(可控制性和可观测性)图23、对于图3的电路,计算组合SCOAP可测试性度量(可控制性和可观测性)图34、采用Roth的D_ALG,对修改的Schneider电路中扇出分支h s-a-1故障进行ATPG,如图4所示。

图45、对于图5电路中的h1 s-a-1故障,采用D算法进行ATPG。

图56、对于图6中的r s-a-0故障,采用FAN A TPG算法生成测试矢量。

图67、对于图7中的NOT门输出的s-a-1故障导出一个测试码。

图78、对于图8中的NAND门的C输入上的s-a-1故障的测试码,并说明这是一个振荡故障。

将无故障的功能重新设计成组合电路。

图89、导出图9电路中A s-a-1故障的一个测试码,并对该故障设计一个多重观察测试。

图910、考虑图10电路中的路径C-F-G:1)导出C处上升转变的测试矢量;2)如果在B出施加下降转变,上述测试矢量可以工作吗?3)当所有门具有一个延迟单元时,画出2)情况的所有信号波形。

4)如何诊断有故障路径。

图1011、假定芯片有100 000个门和2000个触发器。

一个组合A TPG程序为完全测试这个逻辑生成了500个矢量。

单个扫描链设计将需要大约106个时钟周期进行测试。

如果实现20条扫描链,计算扫描测试的长度。

假定电路有20个原始输入数据管脚和20个原始输出数据管脚,而且对测试只能增加一个额外的管脚,对新设计需要多少额外的门开销?12、计算有特征多项式为872()1=+++的标准LFSR生成的前8个测f x x x x试矢量,其初始值是“00000001”,其中1在最低位。

大规模集成电路

9.1.2.1 RAM旳构造

经典旳RAM构造框图如图9-4所示,由地址译码器、存储 矩阵和读写控制电路部分构成。

大规模集成电路

图9-4 RAM旳构造

大规模集成电路

(1)存储矩阵 它是由大量存储单元构成旳,每个存储 单元能存储着由若干位二进制数码构成旳一组信息,存储容 量用(字线数)×(位线数)表达。存储单元在存储矩阵中排 列成若干行、若干列。例如,存储容量为1024×1旳存储器, 其存储单元可排列成32行×32列旳矩阵。基本存储电路主要 由RS触发器构成,其两个稳态分别表达存储内容为“1”或 “0”。

只读存储器(ROM)由“与矩阵”形式旳地址译码器和 “或矩阵”形式旳存储体构成,所以ROM电路旳输出能够用 来表达组合逻辑电路旳最小项“与或”体现式。利用这种措 施构成旳逻辑电路,不但节省了门电路数目,而且还具有一 定旳保密性。目前,在ROM 基础上已开发出了多种层次旳 PLD产品,以满足产品开发旳需要,尤其在多输入多输出变 量场合取得广泛应用。表9-5列出了四种PLD器件旳构造比较。

因为,任一逻辑电路旳功能均可用最小项之和体现式 (与或体现式)表达,所以,能够利用PROM实现组合逻辑电 路旳设计。

大规模集成电路

例9-1 用PROM设计一种将四位8421BCD代码转换为格雷码 旳逻辑电路。

解:首先可列出代码转换表(真值表),如表9-6所示。 根据表9-6可写出用最小项表达旳格雷码输出逻辑体现式:

2114静态RAM旳存储容量为1K×4位,其外引线端子如图 9-5所示,外形为18脚双列直插式构造,地址线为A9~A0,在 片选信号CS 和读写控制信号R /W 旳控制下,信息由四条双 向传播线I/O4~I/O1进行写入或读出操作。

大规模集成电路一二章作业

郭小明2011060100010 大规模集成电路一二章作业第一章作业1、集成电路是哪一年有谁发明的?答:1958年的Texas Instruments(美国德州仪器)公司的Jack Kilby 发明的,基于锗材料采用单管互连方法制作了一个简单的振荡器,可以使认为第一块雏形集成电路,1959年申请小型化电子电路的专利,并于2000年获得诺贝尔物理学奖。

2、诺伊斯对集成电路的主要贡献是什么?答:1959年提出的发明平面工艺技术和PN结隔离技术奠定了半导体集成电路的基础,美国仙童公司的Robert Noyce结合其同事Jean Hoerni发明的刻蚀氧化工艺,在电路上淀积金属薄层进行电路连接,使得复杂集成电路成为可能,并在1959年突出平面型晶体管之后,1961年推出用平面工艺制造出的第一块双极型集成电路,从此旋开了集成电路的新篇章。

1968年7月,Robert Noyce和Gordon Moore,离开Fairchild公司,建立Intel。

2000年,Jack Kilby,Robert Noyce获得Nobel物理奖。

3、MOS场效应管是哪年出现的?1960年Jhon Atalla和Dawon Kahng发明了MOS场效应晶体管,1962年美国的RCA 公司研制出MOS场效应晶体管,并于1963年研制出第一块MOS集成电路。

4、集成电路的发展规律是由谁总结提出来的,具体规律是什么摩尔定律是由英特尔(Intel)创始人之一戈登·摩尔(Gordon Moore)提出来的。

其内容为:当价格不变时,集成电路上可容纳的晶体管数目,约每隔18个月便会增加一倍,性能也将提升一倍。

换言之,每一美元所能买到的电脑性能,将每隔18个月翻两倍以上。

这一定律揭示了信息技术进步的速度。

5、叙述集成电路的层次设计步骤层次化设计是大规模集成电路设计中最广泛使用的方法,可以简化设计的复杂性。

层次化设计分为自顶向下和自底向上两种方法。

第一 二章作业题(参考答案)汇总

第一章引论(Introduction)1.知识要点数字电路的发展及其在信息技术领域中的地位;数字信号与模拟信号之间的关系及数字信号的基本特点;数字系统输入/输出特性及其逻辑特点,数字逻辑电路(Digital Logic Circuit)的主要内容。

重点:1.数字信号(Digital Signal)与模拟信号(Analog Signal)之间的关系;2.数字信号的基本特点;3.数字系统(Digital System)输入/输出特性及其逻辑特点。

难点:1.数字信号的基本特点;2.数字系统的特点。

数字信号只在离散时刻(观测时刻)变化;其取值也是离散的,即数字信号只能取有限种不同的值,为方便电路中处理,这些数值可以用二进制(Binary Number)表达(0,1)。

数字系统的特点:(1)只需考虑观测时刻的输入/输出关系,无须考虑其连续的变化;(2)只需考虑有限的信号取值,不考虑其中间值;(3)任何时刻一根输入/输出线上的状态只能为0或1,所以输入/输出具有有限状态,输入-输出的关系可以采用有限表格进行表达;(4)对于输出的讨论只是考虑在哪些输入条件下输出会等于0,哪些条件下会等于1,于是输入-输出关系体现为逻辑关系。

2.Exercises1.1 Define the following acronyms:ASIC, CAD, CD, CO, CPLD, DIP, DVD, FPGA, HDL, IC, IP, LSI, MCM, MSI, NRE, PBX, PCB, PLD, PWB, SMT, SSI, VHDL, VLSI.ASIC: Application Specific Integrated Circuit,专用集成电路CAD: Computer Aided Design,计算机辅助设计CD: Compact Disc,原意: 紧凑型小唱片,即CD光盘CO: Central Office,中央局,中心站,交换机(也可作Carry Out,进位输出)CPLD: Complex Programmable Logic Device,复杂可编程逻辑器件DIP: Dual Inline-pin Package,双列直插式封装DVD: Digital Versatile Disc,数字通用光盘FPGA: Field Programmable Gate Array,现场可编程门阵列HDL: Hardware Description Language,硬件描述语言IC: Integrated Circuit,集成电路IP: Internet Protocol,因特网协议(也可作Intellectual Property,知识产权)LSI: Large Scale Integration,大规模集成电路MCM: MultiChip Module,多芯片模块MSI: Medium Scale Integration,中规模集成电路NRE: Nonrecurring Engineering,非再现工程,一次性工程PBX: Private Branch Exchange,专用用户交换机PCB: Printed Circuit Board,印制电路板PLD: Programmable Logic Device,可编程逻辑器件PWB: Printed-Wiring Board,印刷线路板SMT: Surface Mount Technology,表面贴装技术SSI: Small Scale Integration,小规模集成电路VHDL: Very High-speed-integrated-circuit Hardware Description Language,超高速集成电路硬件描述语言VLSI: Very Large Scale Integration,超大规模集成电路1.2 Research the definitions of the following acronyms:ABEL, CMOS, DDPP, JPEG, MPEG, OK, PERL (Is OK really an acronym?).ABEL: Advanced Boolean Equation Language,高级布尔方程语言(一种硬件描述语言)CMOS: Complementary Metal-Oxide Semiconductor,互补金属氧化物半导体DDPP: Digital Design Principles and Practices,数字设计原理和实践(英文教材名)JPEG: Joint Photographic Experts Group,联合图像专家组MPEG: Moving Picture Experts Group,运动图像专家组OK: OkayPERL: Practical Extraction and Report Language,实用报表提取语言1.3 Draw a digital circuit consisting of a 2-input AND gate and three inverters,where an inverter is connected to each of the AND gate’s inputs and its output for each of the four possible combinations of inputs applied to the two primary inputs of this circuit determine the value produced at the primary output. Is there a simpler circuit that gives the same input/output behavior?F第二章 信息的二进制表达 (Binary Expression of Information )1.知识要点十进制、二进制、八进制和十六进制数的表示方法以及它们之间的相互转换、二进制数的运算;符号-数值码,二进制补码、二进制反码表示以及它们之间的相互转换;符号数的运算;溢出的概念。

全版《数字电子技术基础》课后习题答案.docx

00

01

11

10

0

0

1

0

1

1

1

0

1

0

另有开关S,只有S=1时,Y才有效,所以

4.14、解:根据题意,画卡诺图如下:

BC

A

00

01

11

10

0

0

0

0

0

1

0

1

1

1

所以逻辑表达式为:Y=AC+AB

(1)使用与非门设计:

逻辑电路如下:

(2)使用或非门设计:

4.15、

(2)解:

1、写出逻辑函数的最小项表达式

2、将逻辑函数Y和CT74LS138的输出表达式进行比较

(45.36)10=(0100 0101.0011 0110)8421BCD=(0111 1000.0110 1001)余3BCD

(136.45)10=(0001 0011 0110.0100 0101)8421BCD=(0100 0110 1001.0111 1000)余3BCD

(374.51)10=(0011 0111 0100.0101 0001)8421BCD=(0110 1010 0111.1000 0100)余3BCD

二、

3、√

4、√

三、

5、A

7、C

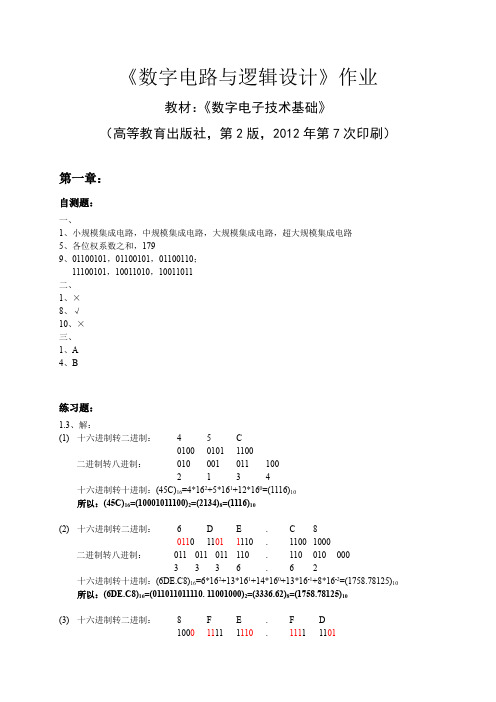

练习题:

4.1;解:(a) ,所以电路为与门。

(b) ,所以电路为同或门

4.5、解:当M=0时, ,同理可推:

,

所以此时电路输出反码。

当M=1时, ,同理可推:

,

所以此时电路输出原码。

4.7、

4.9、解:设三个开关分别对应变量A、B、C,输出Y’,列出卡诺图如下:

2004年数字大规模集成电路作业答案

+…+Y 0 )

=X×((Y −1 +Y 0 +2×Y 1 -4×Y 2 )+…

+(Y n −1 +Y n +2×Y n +1 -4×Y n+ 2 )×2 )n=3K 时, +(Y n −2 +Y n −1 +2×Y n -4×Y n +1 )×2 )n=3K+1 时, +(Y n −3 +Y n −2 +2×Y n −1 -4×Y n )×2 )n=3K+2 时, 2. Yi+2 0 0 0 0 0 0 0 0 1 1 1 1 1 1 1 1 Yi+1 0 0 0 0 1 1 1 1 0 0 0 0 1 1 1 1 Yi 0 0 1 1 0 0 1 1 0 0 1 1 0 0 1 1 Yi-1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 Pi 0 X X 2X 2X 3X 3X 4X -4X -3X -3X -2X -2X -X -X 0 Yi+3 0 0 0 0 0 0 0 0 1 1 1 1 1 1 1 1 Yi+2 0 0 0 0 0 0 0 1 -1 0 0 0 0 0 0 0 Yi+1 0 0 0 1 1 1 1 0 0 -1 -1 -1 -1 0 0 0 Yi 0 1 1 0 0 1 1 0 0 -1 -1 0 0 -1 -1 0 Yi-1 0 -1 0 -1 0 -1 0 -1 0 -1 0 -1 0 -1 0 -1

µ pξ ox W 1 1 2 2 (Vin-Vdd-Vtp) = × Kp × (VM-Vdd-Vtp) ,其中Kp= × Ip= − × Kp × 2 2 t ox L

Vdd + VTp + VTn

由于 Ip+In=0 可以得出 VM =

Kn Kp

大规模集成电路设计题目及答案

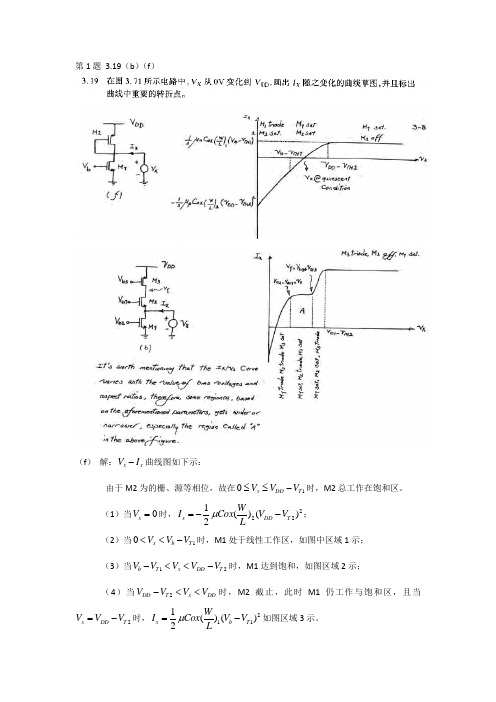

第1题 3.19(b )(f )(f ) 解:x x V I -曲线图如下示:由于M2为的栅、源等相位,故在10x DD T V V V ≤≤-时,M2总工作在饱和区。

(1)当0x V =时,2221()()2x DD T WI Cox V V Lμ=--; (2)当10x b T V V V <<-时,M1处于线性工作区,如图中区域1示; (3)当12b T x DD T V V V V V -<<-时,M1达到饱和,如图区域2示;(4)当2DD T x DD V V V V -<<时,M2截止,此时M1仍工作与饱和区,且当2x DD T V V V =-时,2111()()2x b T WI Cox V V Lμ=-如图区域3示。

(b )解:x x V I -曲线图如下示:(1)当0x V =时,此时M3接DD V 使其饱和,而M1、M2漏源所加电压为零,工作于线性工作区。

当x V 上升至21b T V V -时,M1达到饱和,故当210x b T V V V <<-时,M1、M2工作于线性工作区,M3处于饱和状态,电流变化曲线如区域1所示;(2)随着x V 的继续升高,Y V 也将升高,且当其等于33b T V V +时,此时的M3将由饱和区转为线性工作区,设此时对应的x V 记为xY V ,因此当21b T x xY V V V V -<<时,M1、M3工作于饱和区,M2工作与线性放大区,如图中区域2示。

由于Y V 的变化幅度各个MOS 管的参数有很大的关系,因此此区域的面积有很大的可变性;(3)M3工作于饱和的临界条件为12x b T V V V =-,因此当12xY x b T V V V V <<-时,M1、M2工作于饱和区,M3处于线性工作区,如图中区域3示;(4)当12b T x DD V V V V -<<时,M2关断,M1处于饱和,M3工作于线性放大区,如图中区域4示。

《大学计算机基础课程》作业(1)

第一、二章计算机基础知识一、填空题1.世界上首先实现存储程序的电子数字计算机是 ENIAC 。

2.计算机所具有的存储程序和程序原理是•诺依曼提出的。

3.1946年世界上有了第一台电子数字计算机,奠定了至今仍然在使用的计算机体系结构体系结构。

4.1946年第一台计算机问世以来,计算机的发展经历了4个时代,它们是电子管计算机、晶体管计算机、小规模集成电路计算机、大规模及超大规模集成电路计算机。

5.计算机能够自动、准确、快速地按照人们的意图进行运行的最基本思想是存储程序和程序控制。

6.计算机之所以能实现自动连续运算,是由于采用了存储程序原理。

7.结构化程序设计的三种基本控制结构是顺序、循环和选择。

8.目前计算机应用领域可大致分为三个方面,实时控制、科学计算、数据处理。

9.计算机能直接执行的指令包括两部分,它们是操作码与操作数。

10.计算机中的所有信息都是以二进制编码的形式存储在机器部的。

11.在微机中,bit 的中文含义是二进制位, 8 位二进制为一个字节,用一个字节最多能编出 256个不同的码。

12.计算机硬件系统结构主要分为运算器、控制器、存储器、输入设备、输出设备五大组成。

13.计算机的三类总线是指数据总线DB(Data Bus)、地址总线AB(Address Bus)和控制总线CB(Control Bus) 。

14.计算机中存储信息的最小单位是位。

15.计算机的通用性使其可以求解不同的算术和逻辑运算,这主要取决于计算机的指令系统。

二、单项选择题1.从1946年世界上第一台计算机的产生至今,计算机的发展已经经历了四代,而划分成四代的主要依据是计算机的( C )。

A.运算徽墨 B.主要性能C.构成元件 D.主要功能2.用计算机进行资料检索工作,是属于计算机应用中的( B )。

A.科学计算B.数据处理C.实时控制D.人工智能3.计算机软件系统由( B )组成。

A.程序和程序说明文档 B.硬件系统和软件系统C.指令和程序 D.系统软件和应用软件。

形考作业一(第1-2章,权重30%)测验

试题顺序会变化,请查找具体的题目一、单选题试题1在Windows中,排列桌面项目图标的第一步操作是____。

正确答案是:按鼠标右键单击桌面空白区试题2计算机的硬件系统由五大部分组成,下列各项中不属于这五大部分的是______。

正确答案是:语言处理试题3第一台电子计算机是1946年在美国研制成功的,该机的英文缩写名称是______。

正确答案是:ENIAC试题4在Windows操作环境下,将整个屏幕画面全部复制到剪贴板中使用的键是____。

正确答案是:Print Screen试题5要移动窗口,可以将鼠标指针移到窗口的____。

正确答案是:标题栏位置上拖曳试题6当前的计算机一般被认为是第四代计算机,它所采用的逻辑元件是______。

正确答案是:大规模集成电路试题7冯·诺依曼结构计算机的五大基本构件包括运算器、存储器、输入设备、输出设备和______。

正确答案是:控制器试题8在Windows中,Alt+Tab键的作用是____。

正确答案是:应用程序之间相互切换试题98个字节含二进制位______。

正确答案是:64个试题10Windows的任务栏可用于____。

正确答案是:切换当前应用程序试题11二进制数10110001相对应的十进制数应是______。

正确答案是:177试题12在Windows中,为了查找文件名以"A"字母打头的所有文件,应当在查找名称框内输入____。

正确答案是:A*二、多选题试题13关于Windows窗口,以下叙述错误的是____。

正确答案是:屏幕上只能出现一个窗口,这就是活动窗口,屏幕上可以出现多个窗口,但不止一个活动窗口,当屏幕上出现多个窗口时,就没有了活动窗口试题14下列四个计算机存储容量的换算公式中,正确的是______。

正确答案是:1TB=1024GB, 1KB=1024B, 1MB=1024KB试题15在Windows中,关于文件夹的描述正确的是____。

《超大规模集成电路设计》习题(含答案)

《超大规模集成电路设计》习题1.集成电路的发展过程经历了哪些发展阶段?划分集成电路的标准是什么?集成电路的发展过程:•小规模集成电路(Small Scale IC,SSI)•中规模集成电路(Medium Scale IC,MSI)•大规模集成电路(Large Scale IC,LSI)•超大规模集成电路(Very Large Scale IC,VLSI)•特大规模集成电路(Ultra Large Scale IC,ULSI)•巨大规模集成电路(Gigantic Scale IC,GSI)划分集成电路规模的标准2.超大规模集成电路有哪些优点?1. 降低生产成本VLSI减少了体积和重量等,可靠性成万倍提高,功耗成万倍减少.2.提高工作速度VLSI内部连线很短,缩短了延迟时间.加工的技术越来越精细.电路工作速度的提高,主要是依靠减少尺寸获得.3. 降低功耗芯片内部电路尺寸小,连线短,分布电容小,驱动电路所需的功率下降.4. 简化逻辑电路芯片内部电路受干扰小,电路可简化.5.优越的可靠性采用VLSI后,元件数目和外部的接触点都大为减少,可靠性得到很大提高。

6.体积小重量轻7.缩短电子产品的设计和组装周期一片VLSI组件可以代替大量的元器件,组装工作极大的节省,生产线被压缩,加快了生产速度.3.简述双阱CMOS工艺制作CMOS反相器的工艺流程过程。

4.在VLSI设计中,对互连线的要求和可能的互连线材料是什么?5.在进行版图设计时为什么要制定版图设计规则?在芯片尺寸尽可能小的前提下,使得即使存在工艺偏差也可以正确的制造出IC,尽可能地提高电路制备的成品率6.版图验证和检查主要包括哪些方面?◆DRC(Design Rule Check):几何设计规则检查;对IC的版图做几何空间检查,保证能在特定的工艺条件下实现所设计的电路,并保证一定的成品率;◆ ERC(Electrical Rule Check):电学规则检查;检查电源(power)/地(ground)的短路,浮空的器件和浮空的连线等指定的电气特性;◆ LVS(Loyout versus Schematic):网表一致性检查;将版图提出的网表和原理图的网表进行比较,检查电路连接关系是否正确,MOS晶体管的长/宽尺寸是否匹配,电阻/电容值是否正确等;◆LPE(Layout Parameter Extraction):版图寄生参数提取;从版图中提取晶体管的尺寸、结点的寄生电容、连线的寄生电阻等参数,并产生SPICE 格式的网表,用于后仿真验证;◆ POSTSIM:后仿真,检查版图寄生参数对设计的影响;提取实际版图参数、电阻、电容,生成带寄生量的器件级网表,进行开关级逻辑模拟或电路模拟,以验证设计出的电路功能的正确性和时序性能等,并产生测试向量。

大规模集成电路设计技术手册

大规模集成电路设计技术手册随着科技的飞速发展,电子产品的更新换代速度越来越快,而这些电子产品都需要使用集成电路。

在这个大背景下,大规模集成电路的发展催生了很多技术手册,本文就是其中之一。

本手册旨在向大家介绍大规模集成电路设计技术的相关知识和常用工具,帮助初学者快速掌握相关技能。

第一章基本概念1.1 集成电路的概念与发展集成电路是指将多个电子元器件,如晶体管、二极管、电容器等集成在一个晶片上。

这种技术的出现,大大提高了电子产品的功能、性能和可靠性。

随着技术的进步,集成度越来越高,晶片上集成的元器件越来越多,从而催生了大规模集成电路的发展。

大规模集成电路是指集成了上千、上万个元器件的电路。

1.2 大规模集成电路设计的分类大规模集成电路设计一般分为数字电路设计和模拟电路设计两类。

其中,数字电路设计以逻辑门、触发器等数字元器件为主,主要应用于数字电子产品中;而模拟电路设计则以模拟器件为主,主要应用于模拟电子产品中。

第二章设计流程大规模集成电路设计一般由前端设计和后端设计两部分构成。

2.1 前端设计前端设计主要包括芯片设计、电路设计、逻辑设计、高层次综合、低功耗设计等环节。

常用的设计软件有Cadence、Mentor Graphics、Synopsys等。

2.2 后端设计后端设计主要包括版图设计、布局布线、仿真验证、物理验证等环节。

常用的设计软件有Calibre、Spectre、HSPICE等。

第三章常用工具3.1 设计软件前端设计软件:Cadence、Mentor Graphics、Synopsys后端设计软件:Calibre、Spectre、HSPICE3.2 设计验证工具模拟仿真:Spectre、HSPICE物理仿真:Calibre逻辑仿真:ModelSim、VCS、NC-Verilog3.3 特殊工具FPGA设计:Xilinx、Altera芯片封装:Synopsys Cover-Extend第四章硬件描述语言硬件描述语言(Hardware Description Language,HDL)是一种用于描述数字电路或系统的语言。

微机课后习题答案

第1章作业答案微处理器、微型计算机和微型计算机系统三者之间有什么不同把CPU(运算器和控制器)用大规模集成电路技术做在一个芯片上,即为微处理器。

微处理器加上一定数量的存储器和外部设备(或外部设备的接口)构成了微型计算机。

微型计算机与管理、维护计算机硬件以及支持应用的软件相结合就形成了微型计算机系统。

CP U在内部结构上由哪几部分组成CPU应该具备哪些主要功能CPU主要由起运算器作用的算术逻辑单元、起控制器作用的指令寄存器、指令译码器、可编程逻辑阵列和标志寄存器等一些寄存器组成。

其主要功能是进行算术和逻辑运算以及控制计算机按照程序的规定自动运行。

微型计算机采用总线结构有什么优点采用总线结构,扩大了数据传送的灵活性、减少了连线。

而且总线可以标准化,易于兼容和工业化生产。

数据总线和地址总线在结构上有什么不同之处如果一个系统的数据和地址合用一套总线或者合用部分总线,那么要靠什么来区分地址和数据数据总线是双向的(数据既可以读也可以写),而地址总线是单向的。

8086CPU为了减少芯片的引脚数量,采用数据与地址线复用,既作数据总线也作为地址总线。

它们主要靠信号的时序来区分。

通常在读写数据时,总是先输出地址(指定要读或写数据的单元),过一段时间再读或写数据。

第 2章作业答案IA-32结构微处理器直至Pentillm4,有哪几种80386、30486、Pentium、Pentium Pro、PeruiumII、PentiumIII、Pentium4。

IA-32结构微处理器有哪几种操作模式IA一32结构支持3种操作模式:保护模式、实地址模式和系统管理模式。

操作模式确定哪些指令和结构特性是可以访问的。

IA-32结构微处理器的地址空间如何形成由段寄存器确定的段基地址与各种寻址方式确定的有效地址相加形成了线性地址。

若末启用分页机制,线性地址即为物理地址;若启用分页机制,则它把线性地址转为物理地址。

8086微处理器的总线接口部件由哪几部分组成8086微处理器中的总线接口单元(BIU)负责CPU与存储器之间的信息传送。

微机原理与接口技术(第二版)课后习题答案

微机原理与接口技术(第二版)课后习题答案第1章作业答案1.1 微处理器、微型计算机和微型计算机系统三者之间有什么不同?解:把CPU(运算器和控制器)用大规模集成电路技术做在一个芯片上,即为微处理器。

微处理器加上一定数量的存储器和外部设备(或外部设备的接口)构成了微型计算机。

微型计算机与管理、维护计算机硬件以及支持应用的软件相结合就形成了微型计算机系统。

1.2 CPU在内部结构上由哪几部分组成?CPU应该具备哪些主要功能? 解:CPU主要由起运算器作用的算术逻辑单元、起控制器作用的指令寄存器、指令译码器、可编程逻辑阵列和标志寄存器等一些寄存器组成。

其主要功能是进行算术和逻辑运算以及控制计算机按照程序的规定自动运行。

1.3 微型计算机采用总线结构有什么优点?解:采用总线结构,扩大了数据传送的灵活性、减少了连线。

而且总线可以标准化,易于兼容和工业化生产。

1.4 数据总线和地址总线在结构上有什么不同之处?如果一个系统的数据和地址合用一套总线或者合用部分总线,那么要靠什么来区分地址和数据?解:数据总线是双向的(数据既可以读也可以写),而地址总线是单向的。

8086CPU为了减少芯片的引脚数量,采用数据与地址线复用,既作数据总线也作为地址总线。

它们主要靠信号的时序来区分。

通常在读写数据时,总是先输出地址(指定要读或写数据的单元),过一段时间再读或写数据。

1.8在给定的模型中,写出用累加器的办法实现15×15的程序。

解: LD A, 0LD H, 15LOOP:ADD A, 15DEC HJP NZ, LOOPHALT第 2 章作业答案2.1 IA-32结构微处理器直至Pentillm4,有哪几种?解:80386、30486、Pentium、Pentium Pro、Peruium II 、PentiumIII、Pentium4。

2.6 IA-32结构微处理器有哪几种操作模式?解:IA一32结构支持3种操作模式:保护模式、实地址模式和系统管理模式。

中国科学院大学-超大规模集成电路基础第二次作业答案

1·NMOS的饱和电流更高

因为饱和电流的大小与载流子有关系,P管为空穴导电,N管为电子导电,电子的迁移率大于空穴。

同样的电场下,N管电流大于P管,因此要增大P管的宽长比使之对称,这样才能使得二者上升时间和下降时间相等、高低电平的噪声容限一样、充放电时间相等。

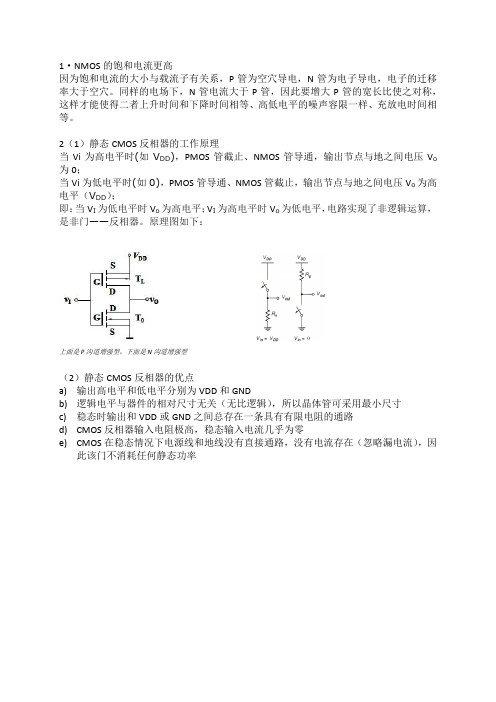

2(1)静态CMOS反相器的工作原理

当Vi为高电平时(如V DD),PMOS管截止、NMOS管导通,输出节点与地之间电压V o 为0;

当Vi为低电平时(如0),PMOS管导通、NMOS管截止,输出节点与地之间电压V o为高电平(V DD);

即:当V I为低电平时V o为高电平;V I为高电平时V o为低电平,电路实现了非逻辑运算,是非门——反相器。

原理图如下:

上面是P沟道增强型,下面是N沟道增强型

(2)静态CMOS反相器的优点

a)输出高电平和低电平分别为VDD和GND

b)逻辑电平与器件的相对尺寸无关(无比逻辑),所以晶体管可采用最小尺寸

c)稳态时输出和VDD或GND之间总存在一条具有有限电阻的通路

d)CMOS反相器输入电阻极高,稳态输入电流几乎为零

e)CMOS在稳态情况下电源线和地线没有直接通路,没有电流存在(忽略漏电流),因

此该门不消耗任何静态功率。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

郭小明2011060100010 大规模集成电路一二章作业

第一章作业

1、集成电路是哪一年有谁发明的?

答:1958年的Texas Instruments(美国德州仪器)公司的Jack Kilby 发明的,基于锗材料采用单管互连方法制作了一个简单的振荡器,可以使认为第一块雏形集成电路,1959年申请小型化电子电路的专利,并于2000年获得诺贝尔物理学奖。

2、诺伊斯对集成电路的主要贡献是什么?

答:

1959年提出的发明平面工艺技术和PN结隔离技术奠定了半导体集成电路的基础,美国仙童公司的Robert Noyce结合其同事Jean Hoerni发明的刻蚀氧化工艺,在电路上淀积金属薄层进行电路连接,使得复杂集成电路成为可能,并在1959年突出平面型晶体管之后,1961年推出用平面工艺制造出的第一块双极型集成电路,从此旋开了集成电路的新篇章。

1968年7月,Robert Noyce和Gordon Moore,离开Fairchild公司,建立Intel。

2000年,Jack Kilby,Robert Noyce获得Nobel物理奖。

3、MOS场效应管是哪年出现的?

1960年Jhon Atalla和Dawon Kahng发明了MOS场效应晶体管,1962年美国的RCA 公司研制出MOS场效应晶体管,并于1963年研制出第一块MOS集成电路。

4、集成电路的发展规律是由谁总结提出来的,具体规律是什么

摩尔定律是由英特尔(Intel)创始人之一戈登·摩尔(Gordon Moore)提出来的。

其内容为:当价格不变时,集成电路上可容纳的晶体管数目,约每隔18个月便会增加一倍,性能也将提升一倍。

换言之,每一美元所能买到的电脑性能,将每隔18个月翻两倍以上。

这一定律揭示了信息技术进步的速度。

5、叙述集成电路的层次设计步骤

层次化设计是大规模集成电路设计中最广泛使用的方法,可以简化设计的复杂性。

层次化设计分为自顶向下和自底向上两种方法。

层次设计奖设计目标分为不同的层次级别,针对设计对象的不同,划分为不同的设计区域,如器件(版图级)、电路级、门级、模块(寄存器级)、系统级。

设计域的划分时针对不同的设计描述方式确定的,相当于抽象设计表示方法,整个层次分为行为域、结构域和几何域。

对于一个复杂的数字IC来说,自顶向下的设计方法,可以分成如下几个步骤完成(1)系统描述(行为级设计):讲用户需求转换为胸膛呢设计说明的过程,给出电路系统的具体要求,如速度、功耗、可靠性、采用的工艺、开发费用和开发周期等,作为电路系统设计过程的约束条件。

(2)抽取高层模型:先借助于硬件描述语言进行算法设计和描述,依据高度抽象的模型库,讲系统划分为子系统或模块的集合,各子系统之间通过数据流和控制流相互连接。

然后通过寄存器传输机设计奖系统设计算法实体化,将子系统或模块的算法描述转换成实现其功能所采用的实际硬件,如寄存器、组合逻辑、多路转换器等,同时进行系统综合优化。

(3)逻辑组合:就是将门、触发器等功能进一步细化,转化成只包含基本门与触发器的逻辑电路

(4)电路设计:将门、触发器转换成晶体管、电阻、电容等基本的元件及连线,可以同时考虑电学及电路性能,并行进行电路分析

(5)物理设计:将晶体管、电阻、电容及连线转换成几何图形,进行电路参数提取及验证。

自底向上的设计过程是系统划分和分解的基础上,先进行单元(门级)的电路和版图设计,在单元精心设计后逐步向上进寄存器传输级功能模块、子系统设计直至最终的系统集成。

自底向上的优点是可以保准局部最优,对单元的精心设计能够为更高层次的系统设计提供良好的基础,但是自底向上的设计过程缺乏全局观点的问题,没有考虑整个系统的设计要求。

第二章作业

1、集成电路的加工有哪些基本工艺?

答:平面工艺基础:热氧化工艺、扩散工艺、淀积工艺和光刻工艺

2、简述光刻工艺过程及作用

答:光刻工艺作用:掩膜版图形通过曝光复制到硅片表面光刻胶上,形成光刻图像,刻蚀未被光刻胶覆盖的部分并去胶。

光刻机:接触式光刻机、接近式光刻机和投影式光刻机。

掩膜版制备:制版系统分为图形处理系统和图形发生器。

光刻过程:在涂上光刻胶之前先进行热氧化处理,淀积一层绝缘的氮化硅薄膜,增加光刻胶与硅片之间的粘附性,以及防止湿法腐蚀时产生。

光刻胶用甩胶机涂覆在硅片上。

由于光刻胶中有溶剂,需要在80度左右的烘箱中进行烘干。

因为集成电路制造是逐层加工的,每次光刻时都要将掩膜版与硅片上的对中记号,保证掩膜版上的图形与硅片上已加工的各层图形套准。

将高压银灯G线或I线痛过掩膜版照射硅片上的感光胶,使光刻胶获得与掩膜图形相同的感光图形。

将曝光后的硅片浸泡到特定的显影液中,控制时间使光刻胶的曝光部

分被溶解掉。

掩膜上的图形就被复制到光刻胶上。

在120度-200度的温度下烘干残留在光刻胶中的有机溶液,提高光刻胶和硅片的粘接性及光刻胶的耐腐蚀性。

以复制到光刻胶上的图形作为掩膜,下层材料进行腐蚀,图形被复制到下层材料商。

最后去除光刻胶。

3、简述双阱CMOS集成电路工艺加工过程?

双阱CMOS工艺主要步骤如下。

1、衬底准备:衬底氧化,生长Si3N4。

2、光刻P阱,形成阶版:在P阱区腐蚀Si3N4,P阱注入。

3、去光刻胶,P阱扩散并牛长SiO2。

4、腐蚀Si3N4,N阱注入并扩散:。

5、有源区衬底氧化:生长Si3N4,有源区光刻和腐蚀,形成有源区版。

6、N管场注入光到:N管场注入。

7、场区氧化:肯源区Si3N4和SiO2腐蚀,栅氧化,沟通掺杂(闭值电压调节注入)。

8、多晶硅淀积、掺杂、光刻和腐蚀,形成多晶硅版。

9、NMOS管光刻和注入硼,形成N+版。

10、PMOS管光刻和注入磷,形成P+版。

11、硅片表面生长SiO2薄膜。

12、接触孔光到,接触孔腐蚀。

13、淀积铝,反刻铝.形成铝连线。

4、MOS晶体管什么类型?

MOS晶体管分为PMOS、NMOS、二极管。

5、版图设计的过程分为那几步?

通常情况下,整个版图设计可分为划分(Partition)、布图规划(Floor-planning)、布局(Placement)、布线(Routing)和压缩(Compaction)。

1、划分:对于一个大的电路系统,其芯片上将会包含上一亿个晶体管,为了降低设计复杂

性,通常把整个电路划分成若干个模块(5-25个左右),将处理问题的规模缩小。

划分时要考虑的因素包括模块的大小、模块的数目和模块之间的连线数等。

2、布图规划:布图规划的任务是要为每一个模块和整个芯片选择一个好的布图方案。

据模

块包含的器件数估计其面积,再根据该模块和其它模块的连接关系以及上一层模块或芯片的形状估计该模块的形状和相对位置。

其优化目标是:电路性能,包括时延,噪声、串扰等,同时考虑P/G、Clock、Bus、Interconnect的可布性。

布图规划中的模块为软模

块。

由于它比较复杂,常常由设计者手工完成。

3、布局:布局的任务是要确定模块在芯片上的准确位置,其目标是在满足时延要求的前提

下,尽量减小布线拥挤度、连线总长、芯片面积等。

布局完成通常分为初始布局和改进布局。

一般情况下,在初试布局时用构造方法给出布局问题的初始解;然后,通过迭代改进优化布局的结果。

由于布局时还未做实际布线,无法评价布局的质量。

如果布线区分配不合理,可能造成布线的失败,使得重新布局。

另外,随着深亚微米工艺的发展,作为主要约束条件,在布局阶段还需要估计关键路径的时延。

目前实用的布局算法大都属于时延驱动的布局算法。

4、布线:该阶段的首要目标就是百分百地完成模块间的互联,其次是完成布线的前提下进

行优化布线结果。

如提高电性能,减少通孔数等。

对于布线区非预先设置的布图模式,如积木块和门海模式等,首先要划分和定义布线区域,有时候要对布线区域进行排序。

目前定义多边形布线区域。

布线分为:总体布线和详细布线,前者完成合理线网的分配,后者最终确定连线的具体位置。

采用两步布线总体上简化布线问题,提供布线成功率。

5、压缩:压缩是布线完成后的优化处理过程,它试图进一步减少芯片的面积,目前常用的

有一维和二维压缩,较为成熟的是一维压缩技术。

在压缩过程中必须保证单元相对位置不变、线网连接性不变、版图几何图形间不违反设计规则。

6、设MOS电路中某层的电阻率ρ=1Ω·cm,该层厚度是1μm,试计算:

(1)有这层材料制作的长度为55μm、宽度为5μm的电阻值

(2)若使用方块电阻的概念,计算该材料的方块电阻值?

答:R=ρ*(L / W*d )=(ρ/ d )*(L/W )

其中,ρ为电阻率,L,W,和d分别为导体的长,宽和厚度(薄层的厚度)。

如果W=L,则R =ρ/ d,称为方块电阻。

R=ρ*(L / W*d )=(ρ/ d )*(L/W ) = 1Ω·cm/1 μm* 55μm/5μm = 11*10^4Ω

R = ρ/ d = 1Ω·c m/1 μm = 1*10^4Ω。