集成电路作业

2023年继续教育集成电路作业(八)

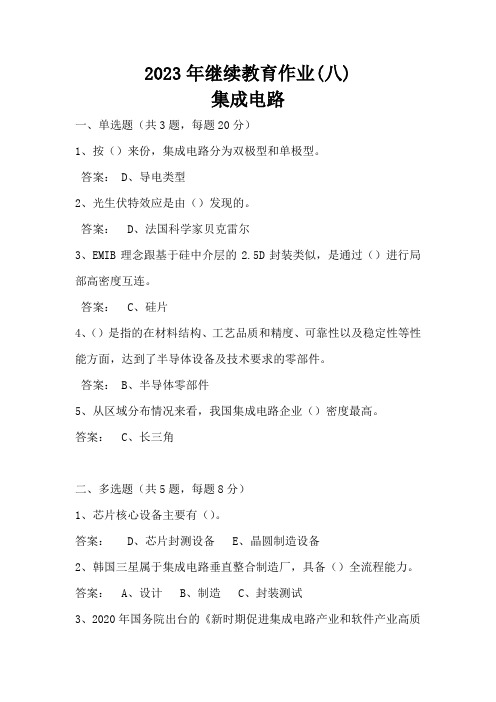

2023年继续教育作业(八)集成电路一、单选题(共3题,每题20分)1、按()来份,集成电路分为双极型和单极型。

答案: D、导电类型2、光生伏特效应是由()发现的。

答案: D、法国科学家贝克雷尔3、EMIB理念跟基于硅中介层的2.5D封装类似,是通过()进行局部高密度互连。

答案: C、硅片4、()是指的在材料结构、工艺品质和精度、可靠性以及稳定性等性能方面,达到了半导体设备及技术要求的零部件。

答案: B、半导体零部件5、从区域分布情况来看,我国集成电路企业()密度最高。

答案: C、长三角二、多选题(共5题,每题8分)1、芯片核心设备主要有()。

答案: D、芯片封测设备 E、晶圆制造设备2、韩国三星属于集成电路垂直整合制造厂,具备()全流程能力。

答案: A、设计 B、制造 C、封装测试3、2020年国务院出台的《新时期促进集成电路产业和软件产业高质量发展的若干政策》中明确提出,进一步优化集成电路产业和软件产业发展环境,深化产业国际合作,提升产业()。

答案: A、创新能力 C、发展质量4、在加工芯片的过程中,光刻机通过一系列的光源能量、形状控制手段,将光束透射过画着线路图的(),经物镜补偿各种光学误差,将线路图成比例()后映射到硅片上,然后使用()方法显影,得到刻在硅片上的电路图。

答案: A、掩模 B、缩小 C、化学5、就半导体工艺整体而言,()和()两个环节的技术壁垒极高。

答案: A、硅片制造 B、芯片制造三、判断题(共5题,每题6分)1、硬核是用硬件描述语言或软件编程语言描述的功能块。

答案:错误2、据掺杂杂质不同,我们把半导体可以分为N型半导体与P型半导体,P型半导体主要掺杂的是五价元素,如磷、砷等。

答案:错误3、集成电路产业在国民经济中的关键性和战略性作用日益凸显。

答案:正确4、整体来看,汽车芯片产业链的重点企业基本为国内企业,国外的领先企业数量不多。

答案:错误5、社会各界对维权援助机构的了解度较高。

拉扎维模拟CMOS集成电路设计第二章作业答案详解完整版中文

IX

1 2

nCOX

W L

[2 0.2(VX

1) (VX

1)

2

]

1 2

nCOX

W L

(1.4 VX )(VX

1)

gm

nCOX

W L

VDS

nCOX

W L

(Vx

1)

Copyright for zhouqn

③ 当VX≥1.2V时,MOS管工作在饱和区

IX

+

IX

1 2

nCOX

IX

1 2

PCox

W L

(0.1)2

gm

PCox

W L

(0.1)

+ 1.9V

-

② 当1.8V<VX≤1.9V时,MOS管工作在线性区

IX

1 2

PCox

W L

[2 (0.1) (VX

1.9) (VX

1.9)2 ]

gm

PCox

W L

(VX

1.9)

Copyright for zhouqn

第二章 作业答案

Copyright for zhouqn

2.1、W/L=50/0.5,假设|VDS|=3V,当|VGS|从0上升到 3V时,画出NFET和PFET的漏电流VGS变化曲线

解:

a) NMOS管: 假设阈值电压VTH=0.7V,不考虑亚 阈值导电

① 当VGS<0.7V时,NMOS管工作在截止区,则ID=0 ② 当VGS>0.7V时, NMOS管工作在饱和区,NMOS管

0 8.854 1012 F / m sio2 3.9

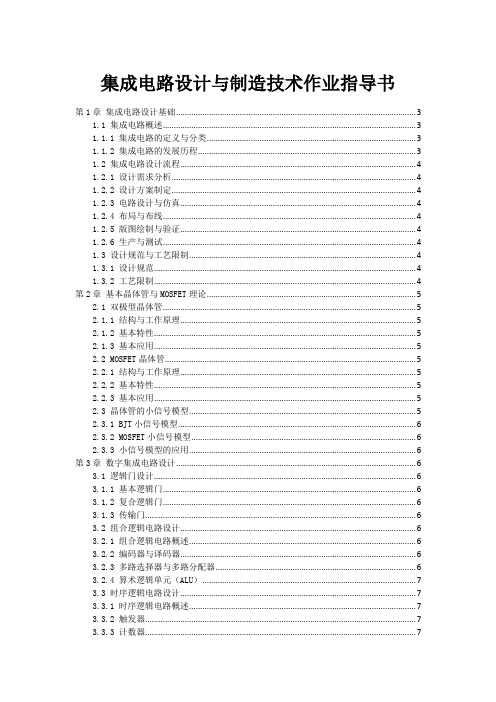

集成电路设计与制造技术作业指导书

集成电路设计与制造技术作业指导书第1章集成电路设计基础 (3)1.1 集成电路概述 (3)1.1.1 集成电路的定义与分类 (3)1.1.2 集成电路的发展历程 (3)1.2 集成电路设计流程 (4)1.2.1 设计需求分析 (4)1.2.2 设计方案制定 (4)1.2.3 电路设计与仿真 (4)1.2.4 布局与布线 (4)1.2.5 版图绘制与验证 (4)1.2.6 生产与测试 (4)1.3 设计规范与工艺限制 (4)1.3.1 设计规范 (4)1.3.2 工艺限制 (4)第2章基本晶体管与MOSFET理论 (5)2.1 双极型晶体管 (5)2.1.1 结构与工作原理 (5)2.1.2 基本特性 (5)2.1.3 基本应用 (5)2.2 MOSFET晶体管 (5)2.2.1 结构与工作原理 (5)2.2.2 基本特性 (5)2.2.3 基本应用 (5)2.3 晶体管的小信号模型 (5)2.3.1 BJT小信号模型 (6)2.3.2 MOSFET小信号模型 (6)2.3.3 小信号模型的应用 (6)第3章数字集成电路设计 (6)3.1 逻辑门设计 (6)3.1.1 基本逻辑门 (6)3.1.2 复合逻辑门 (6)3.1.3 传输门 (6)3.2 组合逻辑电路设计 (6)3.2.1 组合逻辑电路概述 (6)3.2.2 编码器与译码器 (6)3.2.3 多路选择器与多路分配器 (6)3.2.4 算术逻辑单元(ALU) (7)3.3 时序逻辑电路设计 (7)3.3.1 时序逻辑电路概述 (7)3.3.2 触发器 (7)3.3.3 计数器 (7)3.3.5 数字时钟管理电路 (7)第4章集成电路模拟设计 (7)4.1 放大器设计 (7)4.1.1 放大器原理 (7)4.1.2 放大器电路拓扑 (7)4.1.3 放大器设计方法 (8)4.1.4 放大器设计实例 (8)4.2 滤波器设计 (8)4.2.1 滤波器原理 (8)4.2.2 滤波器电路拓扑 (8)4.2.3 滤波器设计方法 (8)4.2.4 滤波器设计实例 (8)4.3 模拟集成电路设计实例 (8)4.3.1 集成运算放大器设计 (8)4.3.2 集成电压比较器设计 (8)4.3.3 集成模拟开关设计 (8)4.3.4 集成模拟信号处理电路设计 (8)第5章集成电路制造工艺 (9)5.1 制造工艺概述 (9)5.2 光刻工艺 (9)5.3 蚀刻工艺与清洗技术 (9)第6章硅衬底制备技术 (10)6.1 硅材料的制备 (10)6.1.1 硅的提取与净化 (10)6.1.2 高纯硅的制备 (10)6.2 外延生长技术 (10)6.2.1 外延生长原理 (10)6.2.2 外延生长设备与工艺 (10)6.2.3 外延生长硅衬底的应用 (10)6.3 硅片加工技术 (10)6.3.1 硅片切割技术 (10)6.3.2 硅片研磨与抛光技术 (10)6.3.3 硅片清洗与检验 (10)6.3.4 硅片加工技术的发展趋势 (11)第7章集成电路中的互连技术 (11)7.1 金属互连 (11)7.1.1 金属互连的基本原理 (11)7.1.2 金属互连的制备工艺 (11)7.1.3 金属互连的功能评价 (11)7.2 多层互连技术 (11)7.2.1 多层互连的原理与结构 (11)7.2.2 多层互连的制备工艺 (11)7.2.3 多层互连技术的挑战与发展 (11)7.3.1 铜互连技术 (12)7.3.2 低电阻率金属互连技术 (12)7.3.3 低电阻互连技术的发展趋势 (12)第8章集成电路封装与测试 (12)8.1 封装技术概述 (12)8.1.1 封装技术发展 (12)8.1.2 封装技术分类 (12)8.2 常见封装类型 (12)8.2.1 DIP封装 (12)8.2.2 QFP封装 (13)8.2.3 BGA封装 (13)8.3 集成电路测试方法 (13)8.3.1 功能测试 (13)8.3.2 参数测试 (13)8.3.3 可靠性测试 (13)8.3.4 系统级测试 (13)第9章集成电路可靠性分析 (13)9.1 失效机制 (13)9.2 热可靠性分析 (14)9.3 电可靠性分析 (14)第10章集成电路发展趋势与展望 (14)10.1 先进工艺技术 (14)10.2 封装技术的创新与发展 (14)10.3 集成电路设计方法学的进展 (15)10.4 未来集成电路的发展趋势与挑战 (15)第1章集成电路设计基础1.1 集成电路概述1.1.1 集成电路的定义与分类集成电路(Integrated Circuit,IC)是指在一个半导体衬底上,采用一定的工艺技术,将一个或多个电子电路的组成部分集成在一起,以实现电子器件和电路的功能。

集成电路设计EDA工具应用作业指导书

集成电路设计EDA工具应用作业指导书第1章 EDA工具概述 (5)1.1 EDA工具发展历程 (5)1.2 EDA工具在集成电路设计中的作用 (5)1.3 常用EDA工具简介 (6)第2章集成电路设计流程 (6)2.1 设计准备阶段 (6)2.1.1 需求分析 (6)2.1.2 技术选型 (6)2.1.3 设计规划 (6)2.1.4 电路架构设计 (6)2.2 设计实现阶段 (6)2.2.1 电路设计 (7)2.2.2 仿真验证 (7)2.2.3 布局布线 (7)2.2.4 版图设计 (7)2.3 设计验证阶段 (7)2.3.1 功能验证 (7)2.3.2 时序验证 (7)2.3.3 电源完整性分析 (7)2.3.4 热分析 (7)2.4 设计后处理阶段 (7)2.4.1 版图检查 (7)2.4.2 后仿真分析 (7)2.4.3 生产数据 (7)2.4.4 文档编写 (7)第3章数字集成电路设计 (7)3.1 数字电路设计基础 (8)3.1.1 数字逻辑元件 (8)3.1.2 组合逻辑电路设计 (8)3.1.3 硬件描述语言(HDL) (8)3.2 逻辑合成与优化 (8)3.2.1 逻辑合成 (8)3.2.2 逻辑优化 (8)3.2.3 EDA工具在逻辑合成与优化中的应用 (8)3.3 时序分析 (8)3.3.1 时序分析基础 (9)3.3.2 时序约束与优化 (9)3.3.3 EDA工具在时序分析中的应用 (9)3.4 电源网络设计 (9)3.4.1 电源网络设计基础 (9)3.4.2 电源网络设计方法 (9)3.4.3 EDA工具在电源网络设计中的应用 (9)第4章模拟集成电路设计 (9)4.1 模拟电路设计基础 (9)4.1.1 模拟电路概述 (9)4.1.2 模拟电路设计流程 (9)4.1.3 模拟电路设计方法 (9)4.2 模拟电路仿真 (9)4.2.1 仿真概述 (10)4.2.2 仿真工具与流程 (10)4.2.3 仿真参数设置与优化 (10)4.3 模拟电路布局与布线 (10)4.3.1 布局与布线概述 (10)4.3.2 布局设计 (10)4.3.3 布线设计 (10)4.4 模拟电路后处理 (10)4.4.1 后处理概述 (10)4.4.2 版图检查与修正 (10)4.4.3 后仿真与功能验证 (10)4.4.4 生产工艺与封装 (10)第5章混合信号集成电路设计 (10)5.1 混合信号电路设计基础 (10)5.1.1 混合信号电路概述 (11)5.1.2 混合信号电路设计流程 (11)5.1.3 混合信号电路关键功能指标 (11)5.2 混合信号电路仿真 (11)5.2.1 仿真方法 (11)5.2.2 仿真工具 (11)5.2.3 仿真步骤 (12)5.3 混合信号电路布局与布线 (12)5.3.1 布局与布线概述 (12)5.3.2 布局与布线原则 (12)5.3.3 布局与布线工具 (12)5.4 混合信号电路后处理 (12)5.4.1 后处理概述 (12)5.4.2 后处理流程 (12)5.4.3 后处理工具 (13)第6章射频集成电路设计 (13)6.1 射频电路设计基础 (13)6.1.1 射频信号特性 (13)6.1.2 射频电路元件 (13)6.1.3 射频电路拓扑 (13)6.2 射频电路仿真 (13)6.2.1 电路仿真原理 (13)6.2.2 仿真工具及参数设置 (13)6.2.3 仿真结果分析 (14)6.3 射频电路布局与布线 (14)6.3.1 布局原则 (14)6.3.2 布线技巧 (14)6.3.3 射频电路版图设计 (14)6.4 射频电路后处理 (14)6.4.1 参数提取 (14)6.4.2 功能评估 (14)6.4.3 优化策略 (14)第7章系统级集成电路设计 (14)7.1 系统级电路设计基础 (14)7.1.1 设计流程概述 (15)7.1.2 设计规范与要求 (15)7.1.3 顶层模块划分 (15)7.1.4 通信协议与接口设计 (15)7.2 系统级电路仿真 (15)7.2.1 仿真工具与流程 (15)7.2.2 仿真模型与参数设置 (15)7.2.3 功能仿真与功能仿真 (15)7.2.4 仿真结果分析 (15)7.3 系统级电路布局与布线 (15)7.3.1 布局布线概述 (15)7.3.2 布局布线策略与方法 (15)7.3.3 布局布线工具与流程 (16)7.3.4 布局布线优化与后处理 (16)7.4 系统级电路后处理 (16)7.4.1 后处理概述 (16)7.4.2 版图检查与修正 (16)7.4.3 参数提取与后仿真 (16)7.4.4 设计交付与生产 (16)第8章设计验证与测试 (16)8.1 功能验证 (16)8.1.1 验证目的 (16)8.1.2 验证方法 (16)8.1.3 验证步骤 (16)8.2 时序验证 (17)8.2.1 验证目的 (17)8.2.2 验证方法 (17)8.2.3 验证步骤 (17)8.3 功耗验证 (17)8.3.1 验证目的 (17)8.3.2 验证方法 (17)8.3.3 验证步骤 (17)8.4 DFT与测试 (18)8.4.1 DFT(Design for Testability)设计 (18)8.4.2 测试方法 (18)8.4.3 测试步骤 (18)第9章设计收敛与优化 (18)9.1 设计收敛策略 (18)9.1.1 确定设计目标 (18)9.1.2 分阶段收敛 (18)9.1.3 迭代优化 (18)9.1.4 设计收敛监控 (19)9.2 逻辑合成优化 (19)9.2.1 逻辑简化 (19)9.2.2 逻辑层次优化 (19)9.2.3 时序优化 (19)9.2.4 功耗优化 (19)9.3 布局与布线优化 (19)9.3.1 布局优化 (19)9.3.2 布线优化 (19)9.3.3 热点分析与优化 (19)9.4 电源网络优化 (19)9.4.1 电源规划 (19)9.4.2 电源网络分割 (19)9.4.3 电源网络优化算法 (20)9.4.4 电源噪声分析与控制 (20)第10章 EDA工具在特定领域应用 (20)10.1 EDA工具在嵌入式系统设计中的应用 (20)10.1.1 硬件描述语言(HDL)设计 (20)10.1.2 仿真验证 (20)10.1.3 逻辑综合 (20)10.1.4 布局布线 (20)10.2 EDA工具在人工智能芯片设计中的应用 (20)10.2.1 高层次综合 (21)10.2.2 基于FPGA的加速 (21)10.2.3 数据流优化 (21)10.3 EDA工具在物联网芯片设计中的应用 (21)10.3.1 低功耗设计 (21)10.3.2 射频设计 (21)10.3.3 系统集成 (21)10.4 EDA工具在汽车电子设计中的应用 (21)10.4.1 功能安全 (21)10.4.2 硬件在环仿真 (21)10.4.3 系统级设计 (22)第1章 EDA工具概述1.1 EDA工具发展历程电子设计自动化(Electronic Design Automation,EDA)工具起源于20世纪60年代,集成电路(Integrated Circuit,IC)技术的飞速发展,EDA工具逐渐成为集成电路设计领域不可或缺的辅助工具。

(整理)集成电路工艺原理作业王蔚1

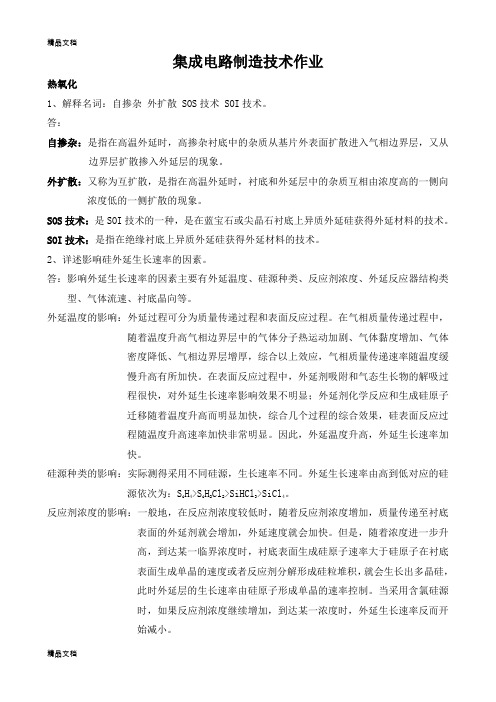

集成电路制造技术作业热氧化1、解释名词:自掺杂外扩散 SOS技术 SOI技术。

答:自掺杂:是指在高温外延时,高掺杂衬底中的杂质从基片外表面扩散进入气相边界层,又从边界层扩散掺入外延层的现象。

外扩散:又称为互扩散,是指在高温外延时,衬底和外延层中的杂质互相由浓度高的一侧向浓度低的一侧扩散的现象。

SOS技术:是SOI技术的一种,是在蓝宝石或尖晶石衬底上异质外延硅获得外延材料的技术。

SOI技术:是指在绝缘衬底上异质外延硅获得外延材料的技术。

2、详述影响硅外延生长速率的因素。

答:影响外延生长速率的因素主要有外延温度、硅源种类、反应剂浓度、外延反应器结构类型、气体流速、衬底晶向等。

外延温度的影响:外延过程可分为质量传递过程和表面反应过程。

在气相质量传递过程中,随着温度升高气相边界层中的气体分子热运动加剧、气体黏度增加、气体密度降低、气相边界层增厚,综合以上效应,气相质量传递速率随温度缓慢升高有所加快。

在表面反应过程中,外延剂吸附和气态生长物的解吸过程很快,对外延生长速率影响效果不明显;外延剂化学反应和生成硅原子迁移随着温度升高而明显加快,综合几个过程的综合效果,硅表面反应过程随温度升高速率加快非常明显。

因此,外延温度升高,外延生长速率加快。

硅源种类的影响:实际测得采用不同硅源,生长速率不同。

外延生长速率由高到低对应的硅源依次为:Si H4>SiH2Cl2>SiHCl3>SiCl4。

反应剂浓度的影响:一般地,在反应剂浓度较低时,随着反应剂浓度增加,质量传递至衬底表面的外延剂就会增加,外延速度就会加快。

但是,随着浓度进一步升高,到达某一临界浓度时,衬底表面生成硅原子速率大于硅原子在衬底表面生成单晶的速度或者反应剂分解形成硅粒堆积,就会生长出多晶硅,此时外延层的生长速率由硅原子形成单晶的速率控制。

当采用含氯硅源时,如果反应剂浓度继续增加,到达某一浓度时,外延生长速率反而开始减小。

其他影响因素:外延器的结构类型、气体流速的因素对气相质量传递快慢造成影响。

复旦大学集成电路工艺原理作业03

作业3:光刻1

1. 对于NA =0.6的曝光系统,设k 1=0.6,k 2=0.5。

考虑100 nm

到1000 nm 之间的波长(DUV 至可见光),计算其在不同的曝光波长下的理论分辨率和焦深,并作图。

在图中标示出常用的光刻波长(i 线,g 线,KrF 和ArF )。

根据计算和图,请说明ArF 对于0.13 μm 和0.1 μm 技术是否足够?

2、 计算有9块掩模工艺的的最终成品率。

掩膜中有4块平均致命

缺陷密度为0.1cm -2, 4块为0.25 cm -2,还有一块为1.0 cm -2,芯片面积为50mm 2.

3、 一个X 光接近式曝光系统,使用的光子能量为1 keV ,如果版

和硅片的间距为20 μm ,估算该系统所能达到的理论衍射分辨率。

(注:λ/hC E =)。

4、 假定某种光刻胶可以MTF =0.3分辨图形,如果曝光系统的

NA =0.4,S =0.5。

则采用i 线光源时光刻分辨的最小尺寸为多少?(选做)。

清华大学数字集成电路作业一

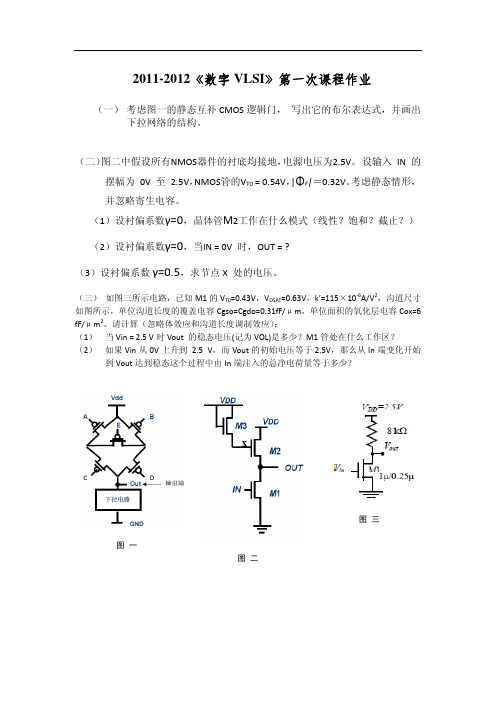

2011-2012《数字VLSI》第一次课程作业

(一) 考虑图一的静态互补CMOS逻辑门, 写出它的布尔表达式,并画出下拉网络的结构。

(二)图二中假设所有NMOS器件的衬底均接地,电源电压为2.5V。

设输入 IN 的摆幅为 0V 至 2.5V,NMOS管的V T0 = 0.54V,|ΦF|=0.32V。

考虑静态情形,并忽略寄生电容。

(1)设衬偏系数γ=0,晶体管M2工作在什么模式(线性?饱和?截止?) (2)设衬偏系数γ=0,当IN = 0V 时,OUT = ?

(3)设衬偏系数γ=0.5,求节点X 处的电压。

(三) 如图三所示电路,已知M1的V T0=0.43V,V DSAT=0.63V,k’=115×10‐6A/V2,沟道尺寸如图所示,单位沟道长度的覆盖电容Cgso=Cgdo=0.31fF/μm,单位面积的氧化层电容Cox=6 fF/μm2。

请计算(忽略体效应和沟道长度调制效应):

(1) 当Vin = 2.5 V时Vout 的稳态电压(记为VOL)是多少?M1管处在什么工作区? (2) 如果Vin从0V上升到 2.5 V,而Vout的初始电压等于2.5V,那么从In端变化开始到Vout达到稳态这个过程中由In端注入的总净电荷量等于多少?

图 一

图 二

图 三。

电子技术相关 《数字集成电路基础》作业答案

《数字集成电路基础》作业答案第一次作业1、查询典型的TTL与CMOS系列标准电路各自的VIH、VIL、VOH和VOL,注明资料出处。

2、简述摩尔定律的内涵,如何引领国际半导体工艺的发展。

第二次作业1、说明CMOS电路的Latch Up效应;请画出示意图并简要说明其产生原因;并简述消除“Latch-up”效应的方法。

答:在单阱工艺的MOS器件中(P阱为例),由于NMOS管源与衬底组成PN结,而PMOS 管的源与衬底也构成一个PN结,两个PN结串联组成PNPN结构,即两个寄生三极管(NPN 和PNP),一旦有因素使得寄生三极管有一个微弱导通,两者的正反馈使得电流积聚增加,产生自锁现象。

影响:产生自锁后,如果电源能提供足够大的电流,则由于电流过大,电路将被烧毁。

消除“Latch-up”效应的方法:版图设计时:为减小寄生电阻Rs和Rw,版图设计时采用双阱工艺、多增加电源和地接触孔数目,加粗电源线和地线,对接触进行合理规划布局,减小有害的电位梯度;工艺设计时:降低寄生三极管的电流放大倍数:以N阱CMOS为例,为降低两晶体管的放大倍数,有效提高抗自锁的能力,注意扩散浓度的控制。

为减小寄生PNP管的寄生电阻Rs,可在高浓度硅上外延低浓度硅作为衬底,抑制自锁效应。

工艺上采用深阱扩散增加基区宽度可以有效降低寄生NPN管的放大倍数;具体应用时:使用时尽量避免各种串扰的引入,注意输出电流不易过大。

2、什么是器件的亚阈值特性,对器件有什么影响?答:器件的亚阈值特性是指在分析MOSFET时,当Vgs<Vth时MOS器件仍然有一个弱的反型层存在,漏源电流Id并非是无限小,而是与Vgs呈现指数关系,这种效应称作亚阈值效应。

影响:亚阈值导电会导致较大的功率损耗,在大型电路中,如内存中,其信息能量损耗可能使存储信息改变,使电路不能正常工作。

3、什么叫做亚阈值导电效应?并简单画出logI D-V GS特性曲线。

答:GS在分析MOSFET时,我们一直假设:当V GS下降到低于V TH时器件会突然关断。

集成电路设计基础作业解答(8~12)

集成电路设计基础作业解答(8~12)1、求N +硅NMOS 晶体管的阈值电压和体因⼦K 。

设t OX =0.1um , N A =3×1018/cm 3。

多晶硅栅掺杂浓度N D =1020/cm 3。

氧化层和硅界⾯处单位⾯积的正离⼦电荷为1010cm -3 解答:(1)P 型衬底体因⼦OXA S C N q K ε2=,其中C q cm F cm N S A 1914318106.1/10854.89.11/103--?=??=?=,,εmT C OXOXOX µεε1.09.30==。

计算可得V K 13.29=(2)V T 有三部分组成:a 、平带电压V FB ;由两部分组成OXOXbulk poly FB C Q V -=-φ。

其中bulk poly -φ为栅多晶硅和体硅的功函数差;)ln(DA bulk poly N N q kT⽶势=多晶硅费⽶势-硅体费=-φ Q ox 为界⾯电荷;b 、降落在栅氧上的电压OXA OX n A OX C QC Q Q V ≈+=;其中F S A S S A F A qN qN Q φεφεφ42)2(≈=c 、半导体表⾯势)ln(2iA F F F n N q kT=是衬底费⽶势,其中φφφ。

所以得到F OXA OX OX bulk poly F OX FB thC QC Q V V V φφφ22+--=++=- 带⼊相应数值得到当没有衬底偏置效应时(V SB =0)阈值电压为V th =28.9V 阈值电压的通式为:)22(),(00F SB F th th SB th V K V V V V φφ-++=评注:这个的数字很不正常,⼀般电路中MOS 器件的阈值电压只有0.7~0.8V 左右。

体效应系数只有0.3左右。

产⽣这些偏差的原因是衬底浓度太⾼(3e1018)。

⼀般的衬底浓度只有1015~1016量级7.1 已知⼀⾃举反相器如图题7.1所⽰,其负载管的W/L =2,设其他参数委V T =0.7,V DD =5V ,k ’=1×10-5A/V 2, 忽略衬底偏置效应。

2004年数字大规模集成电路作业答案

+…+Y 0 )

=X×((Y −1 +Y 0 +2×Y 1 -4×Y 2 )+…

+(Y n −1 +Y n +2×Y n +1 -4×Y n+ 2 )×2 )n=3K 时, +(Y n −2 +Y n −1 +2×Y n -4×Y n +1 )×2 )n=3K+1 时, +(Y n −3 +Y n −2 +2×Y n −1 -4×Y n )×2 )n=3K+2 时, 2. Yi+2 0 0 0 0 0 0 0 0 1 1 1 1 1 1 1 1 Yi+1 0 0 0 0 1 1 1 1 0 0 0 0 1 1 1 1 Yi 0 0 1 1 0 0 1 1 0 0 1 1 0 0 1 1 Yi-1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 Pi 0 X X 2X 2X 3X 3X 4X -4X -3X -3X -2X -2X -X -X 0 Yi+3 0 0 0 0 0 0 0 0 1 1 1 1 1 1 1 1 Yi+2 0 0 0 0 0 0 0 1 -1 0 0 0 0 0 0 0 Yi+1 0 0 0 1 1 1 1 0 0 -1 -1 -1 -1 0 0 0 Yi 0 1 1 0 0 1 1 0 0 -1 -1 0 0 -1 -1 0 Yi-1 0 -1 0 -1 0 -1 0 -1 0 -1 0 -1 0 -1 0 -1

µ pξ ox W 1 1 2 2 (Vin-Vdd-Vtp) = × Kp × (VM-Vdd-Vtp) ,其中Kp= × Ip= − × Kp × 2 2 t ox L

Vdd + VTp + VTn

由于 Ip+In=0 可以得出 VM =

Kn Kp

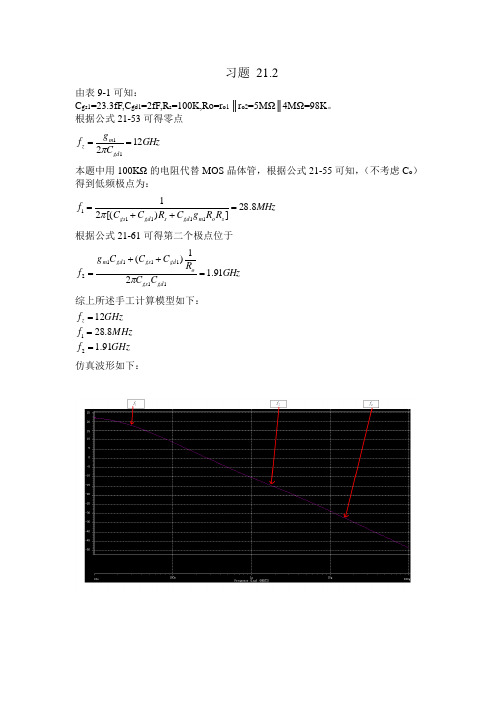

cmos模拟集成电路作业习题21-2

习 21.2由表9-1可知:C gs1=23.3fF,C gd1=2fF,R s =100K,Ro=r o1 ║r o2=5M Ω║4M Ω=98K 。

根据公式21-53可得零点GHz C g f gd m z 12211==π本题中用100K Ω的电阻代替MOS 晶体管,根据公式21-55可知,(不考虑C o ) 得到低频极点为:MHz R R g C R C C f s o m gd s gd gs 8.28])[(2111111=++=π根据公式21-61可得第二个极点位于GHz C C R C C C g f gd gs o gd gs gd m 91.121)(1111112=++=π综上所述手工计算模型如下:GHz f MHzf GHzf z 91.18.281221===仿真波形如下:从仿真结果中可以看到:GHz f GHzf MHzf z 1223021===通过比较仿真结果与手工计算结果差别不大.Sp 文件描述如下:.TITLE MY_analog*------------------------------------------------------------------------*参数、模型定义部分*------------------------------------------------------------------------.include 'hua05.sp'.temp 25.option scale=1u* #destroy all* #run* #plot 20*log(mag(V out/Vs))* #set units=degrees* #plot ph(vout/vs)*------------------------------------------------------------------------*电路网表*------------------------------------------------------------------------.subckt bias VDD Vbias1 Vbias2 Vbias3 Vbias4 Vhigh Vlow Vncas VpcasMN1 Vbias2 Vbiasn 0 0 NMOS L=2 W=10MN2 Vbias1 Vbiasn 0 0 NMOS L=2 W=10MN3 Vncas Vncas vn1 0 NMOS L=2 W=10MN4 vn1 Vbias3 vn2 0 NMOS L=2 W=10MN5 vn2 vn1 0 0 NMOS L=2 W=10MN6 Vbias3 Vbias3 0 0 NMOS L=10 W=10MN7 Vbias4 Vbias3 Vlow 0 NMOS L=2 W=10MN8 Vlow Vbias4 0 0 NMOS L=2 W=10MN9 Vpcas Vbias3 vn3 0 NMOS L=2 W=10MN10 vn3 Vbias4 0 0 NMOS L=2 W=10MP1 Vbias2 Vbias2 VDD VDD PMOS L=10 W=30MP2 Vhigh Vbias1 VDD VDD PMOS L=2 W=30MP3 Vbias1 Vbias2 Vhigh VDD PMOS L=2 W=30MP4 vp1 Vbias1 VDD VDD PMOS L=2 W=30MP5 Vncas Vbias2 vp1 VDD PMOS L=2 W=30MP6 vp2 Vbias1 VDD VDD PMOS L=2 W=30MP7 Vbias3 Vbias2 vp2 VDD PMOS L=2 W=30MP8 vp3 Vbias1 VDD VDD PMOS L=2 W=30MP9 Vbias4 Vbias2 vp3 VDD PMOS L=2 W=30MP10 vp4 vp5 VDD VDD PMOS L=2 W=30MP11 vp5 Vbias2 vp4 VDD PMOS L=2 W=30MP12 Vpcas Vpcas vp5 VDD PMOS L=2 W=30MBM1 Vbiasn Vbiasn 0 0 NMOS L=2 W=10MBM2 Vbiasp Vbiasn Vr 0 NMOS L=2 W=40MBM3 Vbiasn Vbiasp VDD VDD PMOS L=2 W=30MBM4 Vbiasp Vbiasp VDD VDD PMOS L=2 W=30Rbias Vr 0 6.5kMSU1 Vsur Vbiasn 0 0 NMOS L=2 W=10MSU2 Vsur Vsur VDD VDD PMOS L=100 W=10MSU3 Vbiasp Vsur Vbiasn 0 NMOS L=1 W=10.ends biasXbias VDD Vbias1 Vbias2 Vbias3 Vbias4 Vhigh Vlow Vncas Vpcas bias Rs Vs Vss 100kM1 V out Vin 0 0 NMOS L=2 W=10Rp vdd vout 100kRbig Vbias4 Vin 10GCbig Vss Vin 10*------------------------------------------------------------------------*电源描述语句*------------------------------------------------------------------------VDD VDD 0 DC 5Vs Vs 0 DC 0 AC 1*------------------------------------------------------------------------*分析控制语句*------------------------------------------------------------------------.AC DEC 100 1MEG 100G.end习题21-6如果例21-6中的放大器驱动100fF 的负载,估算其传输函数。

拉扎维模拟CMOS集成电路设计第二章作业答案详解完整版

gmnC O XW LV D SnC O XW L(1 V x)

② 当1V<VX<1.2V时,MOS管工作在线性区

I X 1 2 n C O X W L [ 2 0 . 2 ( V X 1 ) ( V X 1 ) 2 ] 1 2 n C O X W L ( 1 . 4 V X ) ( V X 1 )

W

W

gmnC O XLV D SnC O XL(V x 1 )

精品课件

③ 当VX≥1.2V时,MOS管工作在饱和区

IX

+

IX 1 2n C O X W L ( V G S V T H )2 1 2n C O X W L (0 .2 )2

1.9V

VX

M1

-

+

g mn C O XW L(V G S V T H )0 .2n C O XW L

1

ID2

pC oxL W eff (V G SV TH)2(1p3)

ID4 .8 1 0 3(V S G0 .8 )2

08.8541012F/msio2 3.9

Cox

0 sio2 tox

3.837103F/m2

精品课件

2.2 W/L=50/0.5, |ID|=0.5mA,计算NMOS和PMOS的跨导 和输出阻抗,以及本证增益gmro

解:

gm

2Cox

W L

ID

ro

1 ID

gmro

2CoxW LID1 IDA

W L ID

精品课件

2.4 分别画出MOS晶体管的ID~VGS曲线。a) 以VDS作为参

数;b)以VBS为参数,并在特性曲线中标出夹断点

解:以NMOS为例

+

(参考资料)数字集成电路课后习题1-4章作业解析

QB0 =−3×10−7 C / cm××1100−−76

=−0.188 V

= QOX COX

6= ×1011.16××11.60−×610−19

0.06 V

VT0 =−0.99 − (−0.88) − (−0.188) − 0.060 =+0.018 V

计算 PMOS 器件的阈值电压:

VGS −VT + EC L

(1.2 − 0.4)(6)(0.2) 1.2 − = 0.4 + (6)(0.2)

0.48V

VDS = 0.2V

∴ VDS < VDSAT

d. 饱和

VGS>VT,VD > VG 肯定工作在饱和区。对于长沟道器件,如果满足这个关系 就工作在饱和区。而发生速度饱和的短沟道器件的 VDSAT 比长沟道器件的要 小,如果电压偏置能使长沟道器件饱和,那么肯定能使速度饱和的短沟道器件 饱和。

VGS = VG −VS = 1.2 −1.1 = 0.1V V=T V= T 0 0.4V ∴ VGS < VT

c. 线性

VGS = VG −VS = 1.2 − 0 = 1.2V V=T V= T 0 0.4V ∴ VGS > VT

不在饱和区的判断依据:

= VDSAT

(= VGS −VT ) EC L

(N 型)

对于(b)中的 PMOS 器件:

NI

= − QI q

= − (1.6

×10−6 )(1.24 1.6 ×10−19

−

0.4)

= 8.4 ×1012 ions / cm2

(P 型)

d) 从上面的计算可以看到,NMOS 用 N 型多晶硅栅和 PMOS 用 P 型多晶硅栅算得的阈值 电压比较小,在沟道区使用与衬底相同的离子掺杂即可调整到期望值(NMOS:P 型注 入;PMOS:N 型注入)。如果我们在 MOS 管的栅极中采用跟衬底相同类型的离子注 入,得到的阈值电压很大,偏离期望值很多,调整起来比较困难。另外,源极和漏极 的制作过程采用自对准工艺,如果栅极的注入类型和源漏一致,一步即可完成离子注 入,简化了器件制作的工艺流程。

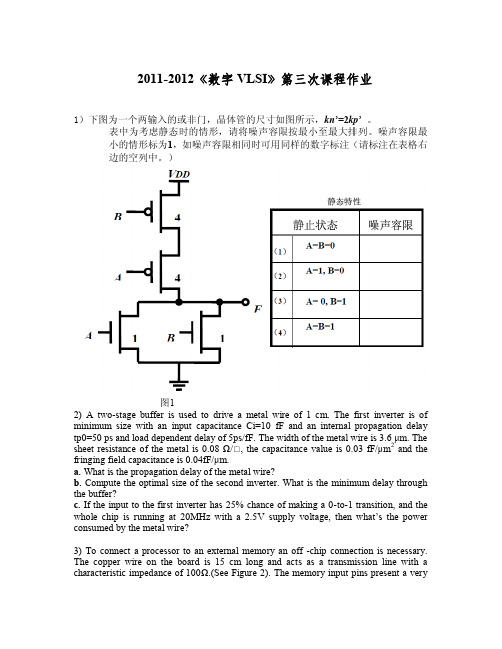

清华大学数字集成电路作业三

2011-2012《数字VLSI》第三次课程作业1)下图为一个两输入的或非门,晶体管的尺寸如图所示,kn’=2kp’ 。

表中为考虑静态时的情形,请将噪声容限按最小至最大排列。

噪声容限最小的情形标为1,如噪声容限相同时可用同样的数字标注(请标注在表格右边的空列中。

)图12) A two-stage buffer is used to drive a metal wire of 1 cm. The first inverter is of minimum size with an input capacitance Ci=10 fF and an internal propagation delay tp0=50 ps and load dependent delay of 5ps/fF. The width of the metal wire is 3.6 μm. The sheet resistance of the metal is 0.08 Ω/□, the capacitance value is 0.03 fF/μm2 and the fringing field ca pacitance is 0.04fF/μm.a. What is the propagation delay of the metal wire?b. Compute the optimal size of the second inverter. What is the minimum delay through the buffer?c. If the input to the first inverter has 25% chance of making a 0-to-1 transition, and the whole chip is running at 20MHz with a 2.5V supply voltage, then what’s the power consumed by the metal wire?3) To connect a processor to an external memory an off -chip connection is necessary. The copper wire on the board is 15 cm long and acts as a transmission line with a characteristic impedance of 100Ω.(See Figure 2). The memory input pins present a veryhigh impedance which can be considered infinite. The bus driver is a CMOS inverter consisting of very large devices: (50/0.25) for the NMOS and (150/0.25) for the PMOS, where all sizes are in μm. The m inimum size device, (0.25/0.25) for NMOS and(0.75/0.25) for PMOS, has the on resistance 35 kΩ.a. Determine the time it takes for a change in the signal to propagate from source to destination (time of flight). The wire inductance per unit length equals 75*10-8 H/m.b. Determine how long it will take the output signal to stay within 10% of its final value. You can model the driver as a voltage source with the driving device acting as a series resistance. Assume a supply and step voltage of 2.5V. Hint: draw the lattice diagram for the transmission line.c. Resize the dimensions of the driver to minimize the total delay.Figure 2. The driver, the connecting copper wire and the memory block being accessed.。

拉扎维模拟CMOS集成电路设计第二章作业答案详解完整版中文全

1.8)(Vin

Vout ) (Vin

Vout )2 ]R1

第十九页,共38页。

2.9 对于图2.46的每个电路,画出IX和VX关于时间的函数曲线

图。C1的初始电压等于3V。

Ix

Vx

(a) λ=γ=0 , VTH=0.7V,Vb>VTH 当Vb-0.7 ≤ VX≤3V时,M1工作在饱和区

Vb

` C1

M1

Ix

1 2

nCOX

W L

(Vb

0.7)2

dQ Ixdt CdVX

dV Vx (t )

3V

X

t

0 I xdt

VX

(t)

3

1 2

nCOX

W L

(Vb

0.7)2

t

当VX< Vb-0.7时,M1工作在线性区,则

Ix

1 2

nCOX

W L

[2(Vb

0.7) VX

VX2 ]

第二十页,共38页。

当VX< Vb-0.7时,M1工作在线性区,则

1 2

nCox

WLVSBV=0GS

-

VVSB>0 TH

+

VBS

-

2

VDS

-

当VGS>VDS+VTH时,MOS工作在三极管区(线性区)

ID

nCox

W L

VGS

VTH

VDS

1 2

VD2S

VTH

VGS

VTH0 VTH1

VGS

VDS+VTH1 VDS+VTH0

VDS3+VTH VDS2+VTH VDS1+VTH

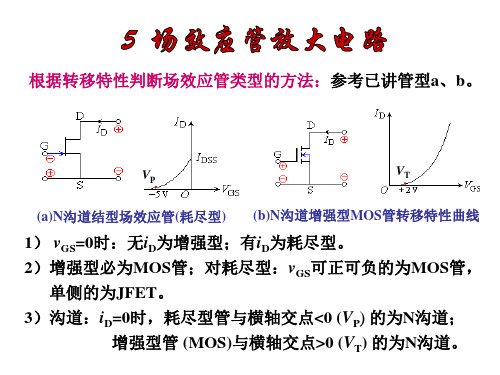

作业参考答案4-场效应管 集成电路 负反馈

VP

VT

(a)N沟道结型场效应管(耗尽型)

(b)N沟道增强型MOS管转移特性曲线

1) vGS=0时:无iD为增强型;有iD为耗尽型。 2)增强型必为MOS管;对耗尽型:vGS可正可负的为MOS管, 单侧的为JFET。 3)沟道:iD=0时,耗尽型管与横轴交点<0 (VP) 的为N沟道; 增强型管 (MOS)与横轴交点>0 (VT) 的为N沟道。

Rd

(1) 画小信号等效电路:共源组态

(2)Av vo gm Rd 1 10 3.3 vi 1 gm R1 1 1 2

R1

R1

Rd

(3)Ri Rg 3 ( Rg1 || Rg2 ) 2075 Ω k

回顾:中频电压增益计算

RL

AVm

gm ( Rd || RL ) Vo 1 gm R Vi

Rc1 5.6kΩ

T1

+ vo - vO1 vO2

Re1 e Re2

vi2

IO

2mA

-VEE

vo Avd (vi1 vi2 ) -43.3 [0.01 (-0.01)] -0.866V

(-=5.6kΩ时,求v’o (3) 单端输出,RL=∞ 时,vO2=? 求Avd2、Avc2和KCMR2的值;

v v

oc2 ic

βRc2 rbe2 (1 β )(2ro Re2 )

Rc1 5.6kΩ

vic

Re1 2rO

T1

+

+

voc -

+

T2

Rc2 5.6kΩ vic

Re2

数字集成电路作业(翻译)

15.2使用稳定窗口定时检查这些定时检查本节讨论:设置保持设置和保持恢复移除$recrem这些检查接受两个信号,该参照事件和数据的事件,并相对于一个信号定义一个时间窗口,而检查其它信号的转换的时间相对于该窗口。

一般来说他们都请执行下列步骤:a)确定一个时间窗口就使用指定的限制或限制的参考信号;b)请与对于时间窗口中的数据信号的过渡时间;c)报告的时序违规,如果数据的时间窗口内的信号转换。

15.2.1设置设置定时检查语法语法15-3所示。

setup_timing_check::=(从附件- A.7.5.1)设置(data_event、reference_event timing_check_limit[[notify_reg]]);data_event::=(从附件- A.7.5.2)timing_check_eventnotify_reg::=variable_identifierreference_event::=timing_check_eventtiming_check_limit::=表达式语法15-3-Syntax设置表定义了49设置定时检查。

表49-setup参数参数描述data_event时间戳事件reference_event timecheck事件限制非负常数表达式通知(可选)注册事件通常是一个数据信号的数据,而引用事件通常是一个时钟信号。

时间窗的端点确定如下: (开始时间窗口)=(timecheck时间)-极限(结束时间窗)=(timecheck时间)设置定时检查报告时间违反在下列情况下:(开始时间窗口)<(时间戳时间)<(结束时间窗口)时间窗的端点不违反地区的一部分。

限制为0时,设置检查永远不会违反。

15.2.2保持所示的持有时间检查语法语法审查费。

hold_timing_check::=(从附件- A.7.5.1)持有(reference_event、data_event timing_check_limit[[notify_reg]]);data_event::=(从附件- A.7.5.2)timing_check_eventnotify_reg::=variable_identifierreference_event::=timing_check_eventtiming_check_limit::=表达式语法15-4-Syntax举行表50定义保存定时检查。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

b.IC产业进入了以客户为导向的阶段。

c.EDA工具的发展,使IC设计工程可以独立于生产工艺。

第三次变革以设计、制造、封装和测试四业分离为标志

a.集成电路产业的又一次大分工。

b.IC产业进入了以竞争为导向的高级阶段。

c.系统设计与IP核设计逐渐开始分工。

4、1个门相当于几个晶体管?以门的数量来划分集成电路有哪些分类?

15、何谓薄膜沉积技术?其主要作用是什么?

集成电路是由数层材质厚度不同的薄膜组成。而将这些薄膜置于硅晶圆片上所需要的技术就是薄膜沉积技术。

主要作用:在硅片表面上淀积一层材料,如金属铝、多晶硅及磷硅玻璃PSG等。在薄膜形成过程中,并不消耗晶片或底材的材质。

11、请简述集成电路生产制造的基本流程。

拉单晶切片与抛光硅圆晶片工艺裸片测试芯片切割芯片粘贴压焊键合线封装和测试

12、简单分析离子注入的优点和局限性。

离子注入的优点:各种杂质浓度分布与注入浓度可通过控制掺杂剂量(1011-1016cm-2)和能量(10-200KeV)来达到;横向分布非常均匀(1% variation across 8’’wafer);表面浓度不受固溶度限制,可做到浅结低浓度或深结高浓度;注入元素可以非常纯,杂质单一性;可用多种材料作掩膜(如金属/光刻胶/介质),可防止沾污,自由度大;低温过程(因此可用光刻胶作掩膜),避免高温过程引起的热扩散。

8、简述新型EDA工具的发展趋势。

a.评价一个EDA软件工具的优劣有以下一些重要指标:

>设计可包含的“门”的数量;

>仿真的速度和仿真时对0.35um以下(深亚微米)COMS工艺中“门”延迟和“线”延迟的估算精度;

>逻辑综合器的性能;(主要是反映硬件描述语言的使用深度)

>版图验证工具的正确性;

b.对EDA工具新要求

光刻的质量要求:刻蚀的图形完整性好,尺寸准确,边缘整齐,线条陡直;图形内无针孔,图形外无小岛,不染色;硅片表面清洁,无底膜;图形套刻准确。

14、目前有哪两种掺杂方式?并请简述这两种掺杂方式。

扩散和离子注入

扩散:扩散炉与氧化炉基本相同,只是将要掺入的杂质如P或B的源放入炉管内。

离子注入:将某种元素的原子经离化变成带电的离子;在强电场中加速,获得较高的动能;射入材料表层(靶);以改变这种材料表层的物理或化学性质。

1个门相当于4个晶体管,等效于一个二输入与非门

a.小规模集成电路(SSI:Small Scale Integrated Circuit)>1-10个门,基本的与非和或非逻辑。

b.中规模集成电路(MSI: Middle Scale Integrated Circuit)>1万门以内,含有计数器和逻辑功能块等电路。

EDA工具的使用

Verilog-HDL和VHDL等硬件描述语言

系统电路设计原理

可测性设计方法和原理

版图设计、验证方法和相关原理等。

7、简述自底向上(Bottom-Up)和自顶向下(Top-Down)设计方法的设计流程,及各自的不足或优点。

自底向上(Bottom-Up)设计方法

a.设计流程:

>确定系统总的功能和指标;

f.巨大规模集成电路(GSI:Giga Scale Integrated Circuit)>千万门以上,如SoC等电路。

5、集成电路系统设计需具备哪些要素?

人才、工具、库和资金。

6、一个集成电路系统设计设计)

集成电路设计、制造生产和测试流程

c.大规模集成电路(LSI:Large Scale Integrated Circuit)>几万门,含有更多更大逻辑功能块,如4位CPU等。

d.超大规模集成电路(VLSI:Very Large Scale Integrated Circuit)>近十万门,如64位CPU等电路。

e.特大规模集成电路(ULSI:Ultra Large Scale Integrated Circuit)>几百万门以上,如DSP、CPU等电路。

MOS/CMOS:结构简单、功耗低、电流电压适应范围大;面积是对应Bipolar的1/5;速度不快、负载能力不强和抗静电能力差等。CMOS相较于MOS工艺又具有超高速、高密度潜力和高增益;低静态功耗、低噪声和低电流驱动;宽的电源电压范围、宽的输出电压幅度(无阈值损失),可与TTL电路兼容;适合各种规模数字集成电路和模拟集成电路;是MOS工艺中最常用的工艺

>系统级仿真和验证数据要到最后才能得到,设计的反复性大。

自顶向下(Top-Down)设计方法

a.设计流程:

系统规范确定及分析建立行为级模型、确定时序要求

↓

RTL级模型建立与模拟建立可综合的VHDL模型,进行功能验证

↓

逻辑综合及测试综合生成门级模型与测试向量

↓

预布局时序验证Timing验证

↓

版图设计及验证布局和布线

b.集成电路朝着两个方向发展。

c.从另一个角度来说,进入90年代以来,电子信息类产品的开发明显地出现了两个特点。

3、简述集成电路产业结构经历的三次重大变革。

第一次变革是以加工制造为主导的初级阶段

a.这一时期半导体制造在IC产业中充当主角。

b.这一时期IC设计和半导体工艺密切相关且主要以人工为主。

第二次变革以Foundry和IC设计公司的崛起为标志

>前端设计时,图形输入法和HDL编程的混合使用EDA工具;

>数字、模拟混合电路的EDA设计工具;

>将系统级设计自动生成门级电路的逻辑综合器EDA工具;

>可测试设计EDA工具(引脚多达200~500个)。

9、简述以硅材料为基础的集成电路制造工艺划分。

>在硅工艺下一般可分出两支:双极(Bipolar)工艺、MOS(金属-氧化物-半导体)场效应工艺。

离子注入的局限:会产生缺陷,甚至非晶层,必须经高温退火加以改进;产量不高、设备复杂;有不安全因素(如高压、有毒气体)。

13、何谓光刻技术?请简述光刻技术的目的和质量要求。并请绘出基于负胶的光刻步骤。

光刻是一种图形复印和化学腐蚀相结合的精密表面加工技术。

光刻的目的:在SiO2或金属薄膜上刻蚀出与掩膜版完全对应的几何窗口图形。实现选择性掺杂和金属薄膜布线等目的。

↓

版图后仿真版图设计后的分布参数提取及时序验证

↓

系统级验证系统验证

b. Top-Down设计的优点:

>它是满足设计指标要求的自然设计方法,克服了设计反复的问题;

>可以采用行为级模型进行系统结构设计,自动综合产生门级电路,而不必理会设计细节,且每一步都可进行设计验证;

>提高了一次设计的成功率;

>提高了设计效率,缩短了IC产品开发周期,也降低了开发费用。

>近年来为了适应高速大驱动和高密度低功耗ASIC与SoC设计的需要,在双极工艺与MOS工艺之间又衍生出BiCMOS工艺。

10、请简述Bipolar、MOS/CMOS等集成电路制造工艺的各自特性。

Bipolar:高速、高增益、低噪声、负载能力强和功耗大,适合中、小规模集成电路和模拟集成电路(如运放、ADC和DAC等);

1、集成电路制造工艺发展水平的衡量指标是什么?

a.在设计和生产中可达到的最小线宽(或称特征尺寸L)。

b.所使用的硅晶圆片的直径。

c. DRAM的储存容量。

2、简述电路制造工艺的发展趋势。

a.趋势性的变化越来越明显,速度越来越快。

特征尺寸越来越小,电源电压越来越低,芯片尺寸越来越大,布线层数越来越多,单片上的晶体管数越来越多,I/O引线越来越多,时钟速度越来越快

>系统划分,并确定各功能的指标;

>设计出各功能块的结构化原理图(框图),并逐层细化直到门级原理图;

>采用逻辑模拟和时序分析自底向上逐级进行验证;

>生成相应的测试向量;

>版图设计和验证;

>版图后仿真。

b.自底向上(Bottom-Up)设计方法不足之处:

>设计周期长,设计规模小;

>设计面积较难有效控制;