synopsys dc中文教程(比较详细)

Synopsys软件安装步骤及说明

5、环境配置………………………………..…………………..…..11

6、说明……………………………………………………………..…..12

7、附录……………………………………………………………..…..13

Synopsys公司的软件都不用破解文件,图形安装流程几乎一样,关键在于license的制作,安装配置都较为简单,在制作license时需要细心。

Unable to obtain feature 'Design-Analyzer ' because:

Error: Can't communicate with the license server. (பைடு நூலகம்EC-12)

Pleasecontact atroot@(none), who isyour local Synopsys license administrator for Synopsys site 000.

aliassnps=“./<SCL安装目录>/linux/bin/lmgrd–c<license所在目录>/<license名称> -l <log文件名称及其路径>”

Cshell设置:

aliassnps“./<SCL安装目录>/linux/bin/lmgrd–c<license所在目录>/<license名称> -l <log文件名称及其路径>”

exportPATH=$SYNOPSYSDC/bin:$PATH

aliasdv=$SYNOPSYSDC/bin/design_vision

DC简单使用

综合概述综合主要包括三个阶段:转换(translation)、优化(optimization)与映射(mapping)。

转换阶段综合工具将高层语言描述的电路用门级的逻辑来实现,对于Synopsys的综合工具DC来说,就是使用gtech.db1库中的门级单元来组成HDL语言描述的电路,从而构成初始的未优化的电路。

优化与映射是综合工具对已有的初始电路进行分析,去掉电路中的冗余单元,并对不满足限制条件的路径进行优化,然后将优化之后的电路映射到由制造商提供的工艺库上。

必须的限制条件1)电路中需要有时钟的定义.2)保留时钟网络,不对时钟网络做综合.3)综合的时候需要指定线负载模型,用于估计连线延迟.4)限制模块中组合路径的输入输出延迟.5)限制输出的带负载能力(Loading budget)以及输入的驱动单元(drivingcell)6)模块同步输出的输出延迟(output delay)的限制,以及同步输入的输入延迟(input delay)的限制.7)多周期路径(multicycle path)以及非法路径(false path)的限制8)工作环境的给定综合的准备设计文件自下而上式的编译目录结构综合划分(Partitioning for Synthesis)采取的策略:z方便设计重用(Partition for design reuse)z保证相关的组合逻辑一起(Keep related combinational logic together)z确保块输出为寄存器(Registering block outputs)z按设计目标划分(Partition by design goal)z按编译技术划分(Partition by compile technique)z保证共享的资源在一起(Keep sharable resources together)z Keep user-defined resources with the logic they drive.z隔离特殊的功能,例如pads,时钟,边界扫描和异步逻辑(Isolate special functions,such as pads,clocks,boundary scans,and asynchronous logic)综合划分技术库技术库包含了半导体厂商提供的每个单元的特征和功能的信息。

SynopsysDesignCompiler使用

SynopsysDesignCompiler使⽤Synopsys Design Compiler使⽤⼀、介绍:美国Synopsys公司发布的“Design Compiler”软件,简称“DC”,是⼀种逻辑合成⼯具。

通过改进电路延迟时间的计算⽅法,缩⼩了逻辑合成时的时序与布局完成后的最终时序之间的偏差。

DC得到全球60多个半导体⼚商、380多个⼯艺库的⽀持。

据最新Dataquest的统计,Synopsys的逻辑综合⼯具占据91%的市场份额。

DC是⼗⼆年来⼯业界标准的逻辑综合⼯具,也是Synopsys最核⼼的产品。

它使IC设计者在最短的时间内最佳的利⽤硅⽚完成设计。

它根据设计描述和约束条件并针对特定的⼯艺库⾃动综合出⼀个优化的门级电路。

它可以接受多种输⼊格式,如硬件描述语⾔、原理图和⽹表等,并产⽣多种性能报告,在缩短设计时间的同时提⾼设计性能。

⼆、要求:由于实训没有硬性要求VHDL⽂件,本⼈挑选了已经预先做好的洗⾐机时控电路,利⽤Synopsys Design Compiler⼯具,进⾏优化分析,通过这⼀过程熟悉软件的使⽤。

三、过程:设置优化运⾏库,鉴于⽼师在练习⼿册上⾯提供的例⼦,我们使⽤库LSI-10K,因此在打开VHDL⽂件前,需要作以下设置Setup->Defaults,填⼊以下信息。

在File->read打开要分析优化的VHDL⽂件,这⾥我选择⼀个洗⾐机时控电路NewWasher.vhd 如下所⽰(分别为不同层次的视图:顶层、器件、门级电路)在Tools->Design Optimization中设置好兼顾平衡的约束条件(左图),确定编译后,产⽣了右边经过优化的门级电路图。

接下来,把优化过的图形转换为VHDL⽂件和DB⽂件输出,另存到指定位置File->Save As如右图,⽣成了新的DB⽂件和vhd⽂件。

接下来,是要设定CLK的周期,根据分析、优化、编译出来的Slack Time 松弛数值和Area⾯积数值,选取最合适的平衡点。

synopsys-dc中文教程(比较详细)

ASIC design flow

IP and Library Models

Verified RTL

Design Constraints

Logic Synthesis optimization&scan insertion Static Timing Analysis

no Time ok?

Floorplan placement, CT Insertion&Global routing

-output active_design+”.sdf” write_constraints –format sdf –cover_design\

-output constraints.sdf

ASIC design flow

Verification

利用SDF文件进行动态时序仿真:利用功能仿真时。用verilog 编写的test_bench 文件 形式验证:利用数学算法检查设计的逻辑的等效性,静态验证,需要的时间比动态仿真少,

方案。我们就以下几个方面对DC做以介绍:

script文件:由DC的命令构成,可使DC自动完成综合的整个过程。 DC支持的对象、变量、属性 DC支持的文件格式及类型 DC在HDL代码中的编译开关,控制综合过程

Translate_off/translate_on:指示DC终止或开始verilog 源代码转换的位置。 full_case:阻止case语句在不完全条件下生成latch。

பைடு நூலகம்

ASIC design flow

Compile and scan insert的scripts,采用bottom_up的编译方法

set_fix_multiple_port_net –buffer_constants –all compile –scan check_test create_test_pattern –sample 10 preview_scan insert_scan check_test 如果模块内的子模块具有dont_touch 属性需添加如下命令,因要插入扫描 remove_attribute find(-hierarchy design,”*”)dont_touch

DC使用说明

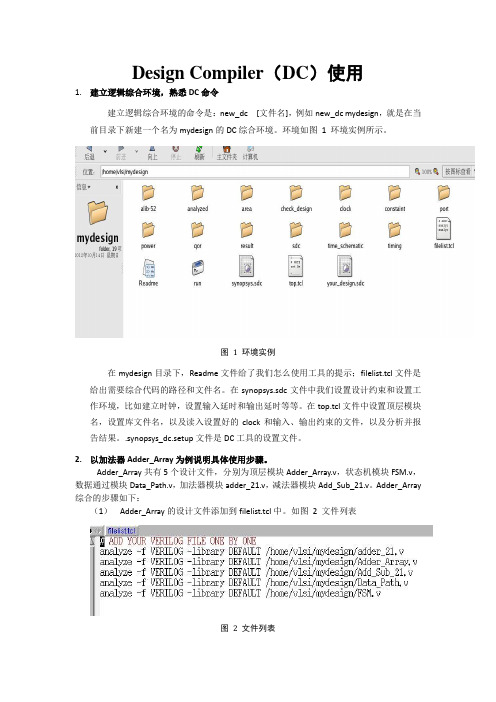

Design Compiler(DC)使用1.建立逻辑综合环境,熟悉DC命令建立逻辑综合环境的命令是:new_dc [文件名],例如new_dc mydesign,就是在当前目录下新建一个名为mydesign的DC综合环境。

环境如图1 环境实例所示。

图1 环境实例在mydesign目录下,Readme文件给了我们怎么使用工具的提示;filelist.tcl文件是给出需要综合代码的路径和文件名。

在synopsys.sdc文件中我们设置设计约束和设置工作环境,比如建立时钟,设置输入延时和输出延时等等。

在top.tcl文件中设置顶层模块名,设置库文件名,以及读入设置好的clock和输入、输出约束的文件,以及分析并报告结果。

.synopsys_dc.setup文件是DC工具的设置文件。

2.以加法器Adder_Array为例说明具体使用步骤。

Adder_Array共有5个设计文件,分别为顶层模块Adder_Array.v,状态机模块FSM.v,数据通过模块Data_Path.v,加法器模块adder_21.v,减法器模块Add_Sub_21.v。

Adder_Array 综合的步骤如下:(1)Adder_Array的设计文件添加到filelist.tcl中。

如图2 文件列表图2 文件列表(2)在top.tcl中将顶层模块设置为Adder_Array。

如图3修改顶层模块名图3 修改顶层模块名(3)修改synopsys.sdc实现以下设计约束:时钟周期1.2ns,input_delay设置为0.5ns,output_delay设置为0.5ns。

如果使用者想增加其他的设计约束可以在此文件中增添。

(4)进入刚才建好的综合环境,在终端中执行run命令,调用Design Compiler执行逻辑综合。

打开终端:cd [建好的环境路径],进入后输入run,即可。

(5)等逻辑综合执行完毕后,查看123.log,对其中的error和warning进行确认,如果有问题修改设计或综合脚本后重新综合,直至没有问题。

DC仿真教程

DC仿真教程DC的使⽤⼀、实验⽬的1、掌握DC软件的基本使⽤流程;2、熟悉基本的DC命令,并理解其意义;3、对DC综合后的结果进⾏分析。

⼆、实验⼯具Synopsys 公司电路综合⼯具Design Complier,即DC。

三、实验内容概述1、利⽤DC图形界⾯进⾏电路综合;2、使⽤DC脚本⽂件进⾏电路综合;3、查看综合报告,根据报告分析电路性能。

四、实验步骤(⽂件说明:为了演⽰⽅便,在进⾏下⾯的实验时需要⽤到两个⽂件,⼀个是example1.v,它是描述⼀个电路的verilog代码,我们的⽬标就是⽤DC综合这个代码得到满⾜约束条件的电路⽹表;另⼀个是dc.scr,它是综合example1.v 的脚本⽂件。

)DC既可使⽤图形界⾯,也可不使⽤图形界⾯⽽直接运⾏脚本来综合电路。

当然,它们⼆者功能是⼀样的,在图形界⾯的每步操作都有相应的命令。

我们先以较为直观的图形界⾯来演⽰各个操作步骤,并给出相应的tcl命令,再⽤DC 脚本来对电路进⾏综合。

准备好需要综合的⽂件和相应的脚本⽂件后,下⾯就开始我们的实验:⼀、DC图形界⾯的使⽤。

1.DC图形界⾯的启动打开⼀个终端窗⼝,键⼊命令dv –db_mode,回车:则DC图形界⾯启动,如下图所⽰:红框处是DC的命令输⼊框,所有以下在图形界⾯上的操作都可以在这个命令输⼊框中输⼊相应的命令来完成。

选择Help-----→Man Pages可以查看DC的联机帮助。

相应指令:man。

例:man man表⽰查看man命令的帮助。

man create_clock表⽰查看creat_clock命令的帮助。

2.设置库⽂件选择File----→Setup打开如下界⾯:接下来就要在这设置库⽂件了,在设置之前我们有必要对这些库做个简单说明:●search_path是要指定综合⼯具的搜索路径。

●target_library为综合的⽬标库,它⼀般是由⽣产线提供的⼯艺相关的库。

●synthetic_library是综合库,它包含了⼀些可综合的与⼯艺⽆关的IP。

DC使用说明

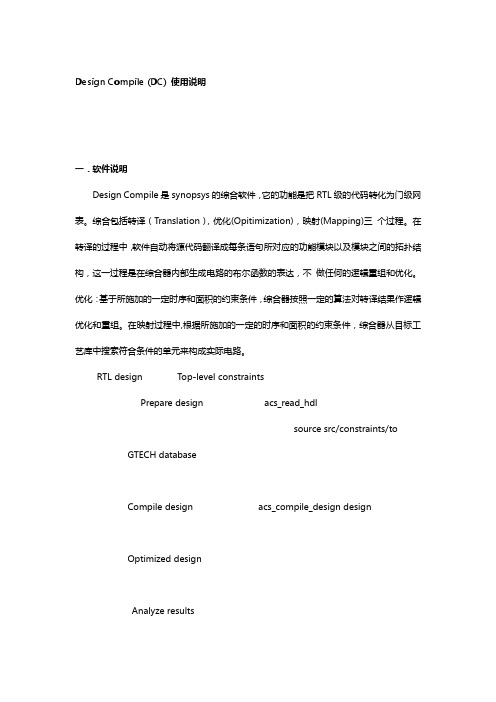

Design Compiler使用说明一.软件说明Design Compiler是synopsys的综合软件,它的功能是把RTL级的代码转化为门级网表。

综合包括转译(Translation),优化(Opitimization),映射(Mapping)三个过程。

在转译的过程中,软件自动将源代码翻译成每条语句所对应的功能模块以及模块之间的拓扑结构,这一过程是在综合器内部生成电路的布尔函数的表达,不做任何的逻辑重组和优化。

优化:基于所施加的一定时序和面积的约束条件,综合器按照一定的算法对转译结果作逻辑优化和重组。

在映射过程中,根据所施加的一定的时序和面积的约束条件,综合器从目标工艺库中搜索符合条件的单元来构成实际电路。

DC有两种界面,图形界面通过敲入design vision&调用出来,另一种命令行界面通过dc_shell-t调用。

建议初学者使用图形界面,因为图形界面比较容易上手;业界的人士比较青睐命令行界面,因为其所耗的资源少,并且将所用的命令写成综合脚本的形式,便于查阅。

因为门级和代码级不同,代码级考虑的是理想情况,但是实际电路不是这样的,它有门级的延时,线的延时,信号的转换时间,甚至时钟信号到达各个触发器的时间不相等。

基于这些考虑,DC通过施加约束,模拟实际环境,根据实际情况得出门级网表。

因此如何适当的施加约束是DC的关键所在。

二.库的配置通过上述说明可知,DC需要通用库和工艺库的支持,DC用到的工艺库是.db或者是.lib格式的,其中.lib格式的文件是可读得,通过此文件可以了解库的详细信息,比如说工作电压,操作温度,工艺偏差等等。

.db格式的库是二进制的,不可读。

.db格式的库由.lib格式的库通过命令read_lib生成。

目标工艺库(Target_library):是指将RTL级的HDL描述到门级时所需的标准单元综合库,它是由芯片制造商(Foundry)提供的,包含了物理信息的单元模型。

Synopsys软件安装步骤及说明

之后可一直“NEXT”到如图(三)所示。

图 (三)

在该界面勾选需要选择所想要的安装包,如果系统是64bit,可将linux和amd64均选上,继续下一步到如图(四)所示。选择安装路径后继续下一步直到结束。

图 (四)

至此DC安装结束。

3

在Synopsys软件的安装目录下没有管理License的工具,故需要安装SCL这一License管理工具。

exportSYNOPSYSFM=/eda_tools/synopsys/fm_vD_2010.03_SP5

exportPATH=$SYNOPSYSFM/bin:$PATH

################################HSPICE12.06#############################

此安装与D处略过。

4

License的制作是在windows下进行的。

1)、打开EFALicGen0.4b文件夹运行LicGen.exe程序出现如图(五)所示界面。

图 (五)

点击“OPEN”选择Synopsys.lpd文件,“打开”。回到图(五)所示界面。勾选上Custon、Use Daemon及最后一个Custon,在两个“Custon”后输入Linux系统的MAC。填好以上内容后点击“Generade”出现license内容界面,取名ynopsys.dat保存(例:保存到D:/Synopsys SSS FeatureKeygen)。

exportPATH=$SYNOPSYSDC/bin:$PATH

aliasdv=$SYNOPSYSDC/bin/design_vision

aliasdc=$SYNOPSYSDC/bin/dc_shell

Design Compiler Lab Guide自学笔记——快速入门DC

Design Compiler Lab Guide自学笔记——快速入门DCfrom Monchy(蒙奇)在2020年秋招前根据Synopsys的Design Compiler Lab Guide2012自学综合工具Synplify,在此分享第一章章详细的学习笔记,几乎是指南的中文翻译,大量的过程截图对初学者很友好。

虽然只有一章,但是对于掌握DC流程的初学者特别重要,共10个任务,很多的设置一旦出错了就卡那了。

本笔记可以帮你避免走弯路。

Design Compiler Lab Guide2012是Synopsys给出的DC综合官方入门指南,里面包涵源码和实验指导,可以在网上自行下载。

1Setup and Synthesis Flow1学习内容描述本实验中使用的三个DC 设置文件中每个文件的内容。

更新common_setup.tcl 文件完全指定逻辑和物理库以及工艺文件在Design Vision 中探索符号和原理图视图通过地形模式下的基本综合步骤进行设计并生成报告访问SolvNet 以浏览《Design Vision 》用户手册2实验指导任务1检查并修改setup 文件1将1ab1目录作为工作目录并列出以下内容文件:#cd /home/IC/Desktop/DC/lab1#ls -al.synopsys*查看所有前面以”.synopsys”开头的关键字的隐藏文件#ls -al *setup*查看所有只要包含有关键字”setup”的文件.synopsys_dc.setup 文件(.开头为隐藏文件)定义别名,source 另外两个设置文件:common_setup.tcl 和dc_setup.tcl 。

(source 报错,不知道怎么弄)common_setup.tcl 文件包含用户自定义的变量,用于指定工艺文件和目录名。

这些变量在dc_setup.tcl 中使用。

在终端中显示echo 打印的内容dc_setup.tcl文件使用common_setup.tcl中的变量执行命令以加载必要的逻辑和物理工艺数据。

Synopsys综合工具DesignCompiler(DC)

Synopsys综合工具DesignCompiler(DC)Synopsys 综合工具Design Compiler(DC)简介一.约束的基本概念:约束就是对用户的设计中可度量的电路参数(如时序、面积以及电容等)进行声明。

没有约束,工具(本文为DC)就不能有效地优化电路,以满足要求。

当DC对设计进行优化时,使用了两类约束:1)设计规则约束(Design Rule Constraints,DRC):此类约束是工具固有的,由工艺库(technology library)来定义。

此类约束是设计功能正确的必要条件,通过库应用于所有设计上。

当然,你可以将它们定义的更紧。

2)优化约束(Optimization Constraints):它们是由用户定义的,前提是可实现的。

用户在使用DC时,可以通过命令行或编写约束文件(.scr)来定义约束。

下图给出DC 主要的DRC及优化约束,以及相关的DC命令(dc_shell接口命令)。

DRC:最大转换时间(Max Transition Time):对于一条连线(net)来说,是其驱动pin逻辑值转化的最长时间。

最大扇出(Max Fanout):对于驱动pin来讲。

最大/最小电容(Max/Min Capacitance):用来控制连线的电容值。

器件退化(Cell Degradation):某些工艺库包括器件退化表,它列举了某一器件可驱动的最大电容,是该器件输入pin最大转换时间的函数。

优化约束:时序约束:包括输入/输出延迟(Input/Output Delay):同步路径最大/最小延迟(Minimum/Maximum Delay):异步路径最大面积(门数):最小孔隙度(Min porosity):可布线性二.约束报告约束报告提供了设计规则和优化约束的信息。

可采用如下命令产生相应报告:report_constraintreport_portreport_clockreport_attributereport_timing_requirements用户可通过输出相应报告,来分析设计是否满足了约束。

DC综合教程

DC综合教程启动dc的三种方法:DCSH:dc_shellTCL:dc_shell-t //注意:-t前没有空格图形化界面:design_visiontip1. 综合主要包括三个阶段:转换(translation)、优化(optimization)与映射(mapping)。

1. 转换阶段:综合工具将高层语言描述的电路用门级的逻辑来实现,对于Synopsys 的综合工具DC 来说,就是使用gtech.db库中的门级单元来组成HDL 语言描述的电路,从而构成初始的未优化的电路。

2. 优化与映射:是综合工具对已有的初始电路进行分析,去掉电路中的冗余单元,并对不满足限制条件的路径进行优化,然后将优化之后的电路映射到由制造商提供的工艺库上。

tip2DesignWare 是集成在DC综合环境中的可重用电路的集合DesignWare 分为DesignWare Basic 与DesignWare Foundation,DesignWare Basic 提供基本的电路,DesignWare Foundation提供性能较高的电路结构。

如果需要Foundation的DesignWare,需要在综合的时候设置synthetic_library3。

tip3 日志文件Design Analyzer 在启动时自动在启动目录下面创建两个日志文件:command.log 和view_command.log,用于记录用户在使用Design Compiler 时所执行的命令以及设置的参数,在运行过程中同时还产生filenames.log的文件,用于记录design compiler访问过的目录,包括库、源文件等,filenames.log文件在退出design compiler 时会被自动删除。

启动dc_shell时则只产生command.log 的日志文件。

tip4Propagation Delay传播延时Transition Time转变延时Setup Time建立时间The setup time for a sequential cell is theminimumlength of time the data-inputsignal must remain stable before the active edge of the clockHold Time保持时间The hold time for a sequential cell is the minimum length of time the data-inputsignal must remain stable after the active edge of the clock脚本:################################# Read design file #//read –format verilog[db、vhdl] file //dcsh的工作模式read_db file.db //TCL工作模式读取DB格式read_verilog file.v //TCL工作模式读取verilog格式read_vhdl file.vhd //TCL工作模式读取VHDL格式//设定时钟create_clock -name "clock" -period 20 -waveform { 0.000 10.000 } { clk }//输出文件write -f verilog -out output/count.v //输出网表write -f ddc -out output/count.ddc//综合数据文件write_sdf mapped/count.sdf //标准延时文件//综合compile -map_effort medium -incremental_mappingtip6设置设计环境Define the Design Environment1. Defining the Operating Conditions设置操作环境查看有哪些操作环境dc_shell> read_file my_lib.dbdc_shell> report_lib my_lib指定操作环境dc_shell> set_operating_conditions WCCOM -lib my_lib 2.设置线负载模型set_wire_load_mode Top/Enclosed/Segmentedset_wire_load_model "10x10"3. Modeling the System Interface设置系统接口The set_drive and set_input_transition Commands:dc_shell> current_design top_level_designdc_shell> set_drive 1.5 {I1 I2}dc_shell> current_design sub_design2dc_shell> set_driving_cell -lib_cell IV {I3}dc_shell> set_driving_cell -lib_cell AN2 -pin Z -from_pin B {I4} Defining Loads on Input and Output PortsDefining Fanout Loads on Output Ports4. Setting Logic Constraints on Portsset_equal port1 port2set_oppositeset_logic_dcset_logic_oneset_logic_zeroset_unconnectedtip7设定设计约束When Design Compiler optimizes your design, it uses two types of constraints:Design rule constraintsOptimization constraints用于组成逻辑1. Maximum Transition Timedc_shell> set_max_transition 5 [current design]2. Maximum FanoutYou can set a maximum fanout constraint on every driving pin and input port as follows:dc_shell> set_max_fanout 8 [get_designs ADDER]计算Fanout值:Maximum Fanout>=Total Fanout Load注意:取出某些约束用:dc_shell> remove_attribute [get_designs adder] max_transitiondc_shell> remove_attribute [get_ports port_name] max_fanoutdc_shell> remove_attribute [get_designs design_name]max_fanoutdc_shell> remove_attribute port_name fanout_load3. The set_fanout_load command sets the expected fanout load value for listed output ports.To find the fanout load on the input pin of library cell AND2 in library libA, enterdc_shell> get_attribute "libA/AND2/i" fanout_loadTo find the default fanout load set on technology library libA, enterdc_shell> get_attribute libA default_fanout_load用于综合出可以驱动的最大扇出的引脚4. Maximum CapacitanceMaximum capacitance is a design rule constraint. It is set as a pin-level attribute that definesthe maximum total capacitive load that an output pin can drive. That is, the pin cannot connect to a net that has a total capacitance greater than or equal to the maximum capacitance defined at the pin.dc_shell> set_max_capacitance 3 [get_designs adder]5. Minimum CapacitanceThe min_capacitance design rule specifies the minimum load a cell can drive.设计规则的优先权1. Minimum capacitance2. Maximum transition3. Maximum fanout4. Maximum capacitance5. Cell degradationtip8设定优化约束Optimization ConstraintsTiming Constraints对于同步pashscreate_clockset_input_delayset_output_delay对于异步pashsset_max_delayset_min_delayMaximum Areadc_shell> set_max_area 0.0dc_shell> set_max_area 14.0Managing Constraint Prioritiesset_cost_priority [-default] [-delay] cost_listReporting Constraints:dc_shell >report_constraint写脚本tip9:在终端中启动DC用脚本综合dc_shell-t -f ./scripts/seg_drive.tcl > 1将报告写入1文件tip10:设计中有多个模块时,如果用top_down策略,则在脚本中得把所有的模块读入:set active_design seg_drive //注意:相等于一个宏定义,用active_design代替seg_drive read_verilog {encode_seg.v number_mod.v scan.v seg_drive.v} //read_file也可以,它可以读多种格式文件,包括.db#analyze -format verilog {encode_seg.v number_mod.v scan.v seg_drive.v}#elaborate $active_design //注意这里是$active_designcurrent_design $active_design //将顶层设置成当前设计link//read_verilog命令与后面的analyze、elaborate功能相同,可以选择其中一个;参看《ASIC综合与DC使用》:set_svf ./mapped/svf/$active_design.svf //没查############################################# ##1# Define the Design Environment#1############################################# ##113Modeling the SystemInterface设置系统接口21)set_operating_conditions slow //设定一个库的环境,库内包含使用温度、电压、电路特征线宽等2)set_wire_load_model –name model_name –lib_name library –max –min//设定线负载模型set_wire_load_model -name tsmc090_wl40 -library slow //表示使用库slow里的tsmc090_wl40线模型如果没有wire_load_model,可以将auto_wire_load_selection 参数设置为 true,则 DC自动根据综合之后的面积来选择一个统计的线负载模型用于估计连线延迟。

Design Compile (DC) 使用说明

Design Compile (DC) 使用说明一.软件说明Design Compile是synopsys的综合软件,它的功能是把RTL级的代码转化为门级网表。

综合包括转译(Translation),优化(Opitimization),映射(Mapping)三个过程。

在转译的过程中,软件自动将源代码翻译成每条语句所对应的功能模块以及模块之间的拓扑结构,这一过程是在综合器内部生成电路的布尔函数的表达,不做任何的逻辑重组和优化。

优化:基于所施加的一定时序和面积的约束条件,综合器按照一定的算法对转译结果作逻辑优化和重组。

在映射过程中,根据所施加的一定的时序和面积的约束条件,综合器从目标工艺库中搜索符合条件的单元来构成实际电路。

RTL design Top-level constraintsPrepare design acs_read_hdlsource src/constraints/to GTECH databaseCompile design acs_compile_design designOptimized designAnalyze resultsConstraints met ? DoneNoRefine design acs_refine_design designRefined designDC有两种界面,图形界面通过敲入design vision&调用出来,另一种命令行界面通过dc_shell-t调用。

建议初学者使用图形界面,因为图形界面比较容易上手;业界的人士比较青睐命令行界面,因为其所耗的资源少,并且将所用的命令写成综合脚本的形式,便于查阅。

因为门级和代码级不同,代码级考虑的是理想情况,但是实际电路不是这样的,它有门级的延时,线的延时,信号的转换时间,甚至时钟信号到达各个触发器的时间不相等。

基于这些考虑,DC通过施加约束,模拟实际环境,根据实际情况得出门级网表。

因此如何适当的施加约束是DC的关键所在。

EDA技术_Synopsys公司逻辑综合工具DC 介绍 part2

2013-7-9

21

Synopsys工艺库—功能、时序等 属性信息

2013-7-9

22

Synopsys工艺库——逻辑库

EDA技术实验

延时计算 Synopsys支持的延迟模型有:

CMOS通用的延迟模型 CMOS分段的线性延迟模型 非线性的查找表延迟模型

DSM的设计,前两种延迟模型不常用, 非线性延迟模型以输入的跃迁时间和输出 的容性负载为参变量计算延迟的时间值, 其结果以表格的形式列出供DC查找。

2013-7-9

12

Design Compiler Interfaces

EDA技术实验

1) dc_shell-t(DC-Tcl)

2) dc_shell(DCSH)

3) Design Analyzer

4) Design vision

in 2000.11 release

2013-7-9

13

CONTENTS

2013-7-9

18

Synopsys工艺库——逻辑库

EDA技术实验

环境描述:用于对PVT的偏差建模。

工作条件(operating conditions) 线负载模型(WLM, wire load model) 时序范围模型

2013-7-9

19

Synopsys工艺库——逻辑库

EDA技术实验

工作条件(operating conditions):指 定了工艺、温度、电压以及RC树模型, 用于设计的综合和时序分析。例如:

2013-7-9 23

Synopsys工艺库——逻辑库

EDA技术实验

设计人员了解工艺库,在于正确使用和 理解逻辑库,而不在于与库设计者相关的 细节上。

dc使用教程

DC使用说明文件说明:在进行下面的演示时需要用到两个文件,一个是example1.v,它是描述一个电路的verilog代码,我们的目标就是用DC综合这个代码得到满足约束条件的电路网表;另一个是dc.scr,它是综合example1.v的脚本文件。

这两个文件都在/home/student1000目录下,大家把它们拷贝到自己的目录下,以备使用。

DC既可使用图形界面,也可不使用图形界面而直接运行脚本来综合电路。

一、DC图形界面的使用。

1.DC图形界面的启动1.1 打开一个终端窗口,写入命令dv –db_mode,敲入回车。

则DC图形界面启动,如下图所示红框处是DC的命令输入框,以下在图形界面上的操作都可以在命令输入框中输入相应的命令来完成。

选择Help----- Man Pages可以查看DC的联机帮助。

相应指令:man。

例:man man表示查看man命令的帮助。

man create_clock表示查看creat_clock命令的帮助。

2.设置库文件选择File---- Setup需要设置以下库文件,如下图。

相应指令:set search_path [list /tools/lib/smic25/feview_s/version1/STD/Synopsys \/tools/lib/smic25/feview_s/version1/STD/Symbol/synopsys] set target_library { smic25_ff.db }set link_library { smic25_ff.db smic25_ss.db }set symbol_library { smic25.sdb }点OK,设置完成。

3.读入verilog文件选择File--- Read在打开文件对话框中选中要打开的文件,在这里我们选中example1.v文件。

在Log框中出现successfully字样表明读入文件成功。

SynopsysDC中文培训实验

SYNOPSYSLab1Setup and Synthesis Flow缩略词:Design Compile =DC;备注:UNIX%代表在linux终端下进行操作,其余的代表在DC下进行DC命令输入前言:DC(Design Compiler)是Synopsys的logical synthesis优化工具,它根据design description 和constraints自动综合出一个优化了的门级电路。

它可以接受多种输入格式,如硬件描述语言、原理图和netlist等,并产生多种性能报告,在缩短设计时间的同时提高读者设计性能。

基本的综合流程:该基本综合流程包含下列步骤:1. 发展HDL文件输入Design Compiler的设计文件通常都是用诸如VHDL和Verilog HDL等硬件描述语言编写。

这些设计描述必须小心地编写以获得可能的最好的综合结果。

在编写HDL代码时,你需要考虑设计数据的管理、设计划分和HDL编码风格。

划分和编码风格直接影响综合和优化过程。

虽然流程中包含该步骤,但实际上它并不是Design Compiler的一个步骤。

你不能用Design Compiler工具来编写HDL文件。

2. 指定库通过link_,target_,symbol_,和synthetic_library命令为Design Compiler指定链接库、对象库、符合库和综合库。

链接库和对象库是工艺库,详细说明了半导体厂家提供的单元和相关信息,象单元名称、单元管脚名称、管脚负载、延迟、设计规则和操作环境等。

符号库定义了设计电路图所调用的符号。

如果你想应用Design Analyzer图形用户界面,就需要这个库。

另外,你必须通过synthetic_library命令来指定任何一种特殊的有许可的设计工具库(你不需要指定标准设计工具库)。

3. 读入设计Design Compiler使用HDL Compiler将RTL级设计和门级网表作为设计输入文件读入。

DC简明教程

DC简明教程(转)1.1 什么是DC?DC(Design Compiler)是Synopsys的logical synthesis优化工具,它根据design description和constraints自动综合出一个优化了的门级电路。

它可以接受多种输入格式,如硬件描述语言、原理图和netlist等,并产生多种性能报告,在缩短设计时间的同时提高读者设计性能。

1.2 DC能接受多少种输入格式?支持.db, .v, .vhd , edif, .vgh等等,以及.lib等相关格式。

1.3 DC提供多少种输出格式?提供.db, .v, .vhd, edif, .vgh等,并可以输出sdc, .sdf等相关格式文件。

1.4 DC的主要功能或者主要作用是什么?DC是把HDL描述的电路综合为跟工艺相关的门级电路。

并且根据用户的设计要求,在timing和area,timing和power上取得最佳的效果。

在floorplanning和placement和插入时钟树后返回DC进行时序验证1.5 如何寻找帮助?帮助可以用3种求助方式:1. 使用SOLD,到文档中寻求答案2. 在命令行中用man+ DC命令3. 在命令行中用info+ DC命令1.6 如何找到SOLD文档?SOLD文档可以在teminal中输入sold&执行。

$> sold&或者用命令 which dc_shell找到dc的安装目录。

找到online目录。

1.7 如何配置DC?综合设置提供必要的参数给DC,使工具能够知道进行综合时所需要的必要的信息,即重要参数:工艺库,目标库,标志库等等。

要在.synopsys_dc.setup上设置好这些参数。

而.synopsys_dc.setup要在三个目录下有说明,一个是synopsys的安装目录,一个是用户文件夹,最后一个是工程目录。

由后一个设置覆盖前一个文件。

参数包括:search_path, target_library, link_library, symbol_library1.8 target_library 是指什么?target_library是在synthesis的map时需要的实际的工艺库1.9 link_library如何指定?链接时需要的库,通常与library相同,设置时,需要加“*”,表示内存中的所有库。

SynopsysDesignCompiler完整中文讲义

DC学习----第一章基本概念1.1 启动文件启动文件用来指定综合工具所需要的一些初始化信息。

DC使用名为“.synopsys_dc.setup”的启动文件,启动时,DC会以下述顺序搜索并装载相应目录下的启动文件:1)、DC的安装目录;2)、用户的home目录;3)、当前启动目录。

注意:后装载的启动文件中的设置将覆盖先装载的启动文件中的相同设置。

下面是一个DC启动文件的实例,它包含了几乎所有重要的设置,下文将结合该实例解释启动文件中各项设置的具体含义。

例1-1(一个DC启动文件):search_path= search_path + {“.”, synopsys_root + “/dw/sim_ver” }search_path= search_path + { “~/risc32/synthesis/libraries” }target_library={ tcb773stc.db }synthetic_library={dw_foundation.sldb}link_library = { “*”, dw_foundation.sldb, tcb773stc.db }symbol_library = { tcb773s.sdb }synlib_wait_for_design_license = {"DesignWare-Foundation"}alias rt “report_timing”designer= XXXXXcompany= “ASIC Lab, Fudan Univ.”search_path指定了综合工具的搜索路径。

target_library为综合的目标库,它一般是由生产线提供的工艺相关的库。

synthetic_library是综合库,它包含了一些可综合的与工艺无关的IP。

dw_foundation.sldb是Synopsys提供的名为Design Ware的综合库,它包含了基本的算术运算逻辑、控制逻辑、可综合存储器等IP,在综合是调用这些IP有助于提高电路性能和减少综合时间。

集成电路可测性设计软件DC安装教程

第一次上课:安装所需文件:EFALicGen0.4b dc.tar DC_LAB synkey查找网卡序列号:打开终端,按如下命令输入。

(000C29F7CA04即是网卡号,将其保存到新建记事本中)打开文件夹EFALicGen0.4b,将文件夹Synopsys SSS Feature Keygen粘贴到C盘根目录下,打开EFALicGen0.4b\EFA LicGen 0.4b\LicGen 0.4bLicGen.exe,打开后如下图:点击Open,选择EFALicGen0.4b\EFA LicGen 0.4b\packs\Synopsys.lpd,勾选Select Host ID下Custom,在其后输入网卡号(不输入冒号),勾选Use Daemon勾选Select Daemon ID下Custom,在其后输入网卡号,点击Generate,将生成文件保存在目录EFALicGen0.4b\EFA LicGen 0.4b 下,文件名为synopsys,找到文件synopsys.dat(在目录EFALicGen0.4b\EFA LicGen 0.4b\synopsys.dat),将之复制到目录C:\Synopsys SSS Feature Keygen下(如该目录下已有相同名称文件,直接替换),将该目录下已有的license.dat文件删除,输入cmd,打开任务窗口,依次按照下图命令输入,按回车,在生成的数据中寻找SECRET DATA = **** **** **** ****(序列号),将序列号复制到新建记事本中,关闭任务窗口,打开C:\Synopsys SSS Feature Keygen\KeyGen.exe,在打开的界面中分别在SECRET DATA和HOSTID下输入相应的序列号,然后点击Generate,在目录C:\Synopsys SSS Feature Keygen下会生成license.dat文件,打开文件license.dat,将(FEATURE SSS snpslmd 1.0 31-dec-2020 uncounted 9E80059D521B299B0E54 \ VENDOR_STRING="69656 d1d88 34cc3 3a463 8792e 5c9fb 7bf43 8258f \ecc22fcf" HOSTID=000c29057ce5 ISSUER="Team ZWT 2006" \NOTICE="Licensed to mammoth//ZWT 2006 [PLEASE DO NOT DELETE THIS \SSS KEY]" SN=RK:1978-0:001224:0 START=1-jan-2006)复制,打开文件synopsys.dat,将之前所复制内容粘贴到本文档最后,然后保存、关闭,保存后的将保存后的文件synopsys.dat粘贴到虚拟机桌面,打开虚拟机在目录/home/fxwang下新建文件夹eda,将文件dc.tar DC_LAB synkey粘贴到其下;解压目录/home/fxwang/eda下的dc.tar压缩包(cd eda;tar –xvf dc.tar),将桌面上的synopsys.dat文件重命名为key,将重命名后的key文件粘贴到目录/home/fxwang/eda/dcadmin/license下(将已有的key文件删除),打开终端,运行如下命令即可。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

ASIC design flow

Pre_layout 的 STA :用DC的静态时序分析引擎做block的STA,用PrimeTime做 full_chip的STA。 Setup_time分析 Hold_time分析 其时序约束和提供给DC做逻辑综合的约束相同。静态时序分析同综合一样,是 一个迭代的过程,和cell的位置及布线关系密切,通常都执行多次,直到满 足需要。

综合的定义

逻辑综合:决定设计电路逻辑门的相互连接。

逻辑综合的目的:决定电路门级结构、寻求时序和与面积的平衡、 寻求功耗与时序的平衡、增强电路的测试性。 逻辑综合的过程:首先,综合工具分析HDL代码,用一种模型 (GTECH) ,对HDL进行映射,这个模型是与技术库无关的;然后, 在设计者的控制下,对这个模型进行逻辑优化;最后一步,进行 逻辑映射和门级优化,将逻辑根据约束,映射为专门的技术目标 单元库(target cell library)中的cell,形成了综合后的网表。

Floorolanning and global Routing; Estimated 寄生电容和RC delay的抽取; 利用抽取的参数静态时序分析,若时序不满足要求,生成custom wire_load 做 incremental synthesis即post_layout的优化,采用reoptimize_design – in_place命令,其script文件需反标抽取的参数到设计; Detail routing; real寄生电容和RC delay的抽取; 利用抽取的参数静态时序分析,修正hold_time如需要做post_layout的优化; 生成post_layout的SDF文件,做gate_level仿真验证;

DC介绍

Synopsys Design Compiler,是一个基于UNIX系统,通过命令行进行交互的综合工具, 除了综合之外,它还含有一个静态时序分析引擎及FPGA和LTL(links-to-layout)的解决 方案。我们就以下几个方面对DC做以介绍: script文件:由DC的命令构成,可使DC自动完成综合的整个过程。 DC支持的对象、变量、属性 DC支持的文件格式及类型 DC在HDL代码中的编译开关,控制综合过程

}

ASIC design flow

Constrain scripts(续) /* Apply default drive strengths and typical loads for I/O ports */ set_load 1.5 all_outputs() set_driving_cell -cell IV all_inputs() /* If real clock, set infinite drive strength */ if (find(port, clk) == {"clk"}) { set_drive 0 clk } /* Apply default timing constraints for modules */ set_input_delay 1.2 all_inputs() -clock clk_name set_output_delay 1.5 all_outputs() -clock clk_name set_clock_skew -minus_uncertainty 0.45 clk_name /* Set operating conditions */ set_operating_conditions WCCOM /* Turn on Auto Wireload selection Library must support this feature */ auto_wire_load_selection = true

Translate_off/translate_on:指示DC终止或开始verilog 源代码转换的位置。 full_case:阻止case语句在不完全条件下生成latch。

Script 文件

Script 文件

Script 文件的构成 DC综合环境设置(.synopsys_dc.setup); 属性和约束信息; 综合命令(read,compile); 控制流命令;

ASIC design flow

Compile and scan insert的scripts,采用bottom_up的编译方法

set_fix_multiple_port_net –buffer_constants –all compile –scan check_test create_test_pattern –sample 10 preview_scan insert_scan check_test 如果模块内的子模块具有dont_touch 属性需添加如下命令,因要插入扫描 remove_attribute find(-hierarchy design,‖*‖)dont_touch

ASIC design flow

IP and Library Models Verified RTL Design Constraints Logic Synthesis optimization&scan insertion Static Timing Analysis no Post global route Static Timing Analysis Time ok? no

ASIC design flow

Verification

利用SDF文件进行动态时序仿真:利用功能仿真时。用verilog 编写的test_bench 文件 形式验证:利用数学算法检查设计的逻辑的等效性,静态验证,需要的时间比动态仿真少, 验证全面。在这里验证RTL描述与gate_level网表的逻辑等效性。

ASIC design flow

Initial Setup :建立设计环境,技术库文件及其它设计环境设置。 DC .synopsys_dc.setup 文件 company =―zte corporation‖; designer =―name‖; technology=―0.25 micron‖ search_path=search_path+{―.‖ ―/usr/golden/library/std_cells‖\ ―/usr/golden /library/pads‖} target_library ={std_cells_lib.db} link_library ={―*‖,std_cells_lib.db,pad_lib.db} symbol_library ={std_cells.sdb,pad_lib.sdb}

Write netlist

remove_unconnected_ports find(-hierarchy cell,‖*‖) change_names –hierarchy –rules BORG set_dont_touch current_design write –herarchy –output active_design+‖.db‖ write –format verilog –hierarchy –output active_design+‖.sv‖

ASIC design flow

ECO

Engineering change order,不属于正常的ASIC流程,一般只有在ASIC设计的 后期,需要改变网表,可利用ECO,例如,在tape-out(sign-off)以后,遇见设 计的硬件bug。采用ECO可仅对设计的一小部分重新布线不影响chip其他部分 的位置及时序,通常,修改不能大于10%。 最新版本的DC提供由ECO compiler, 可使设计者手工修改网表,节省时间。 一些layout工具也具有ECO功能。

ASIC design flow

设计举例,tap控制器,已完成代码ntroller.v Tap_bypass.v Tap_instruction.v Tap_state.v 完成全部设计还需经过如下几个步骤:

Pre_layout Synthesis STA using PrimeTime SDF generation Verification Floorolanning and Routing Post_layout 反标来自layout tool的信息, STA using PrimeTime Post-layout Optimization Fix Hold-Time Violation

ASIC design flow

SDF generation,pre_layout的SDF文件,用于pre_layout timing仿真,同时还需 提供时序约束文件(SDF格式)给layout tool做布局布线。script文件如下:

active_design=tap_controller read active_design current_design active_design link Create_clock –period 33 –waveform {0 16.5} tck Set_dont_touch_network {tck trst} set_clock_skew –delay 2.0 –minus_uncertainty 3.0 tck set_driving_cell –cell BUFF1X –pin Z all_inputs() set_drive 0 {tck trst} set_input_delay 20.0 –clock tck –max all_inputs() set_output_delay 10.0 –clock tck –max all_outputs() write_timing –format sdf-v2.1 \ -output active_design+‖.sdf‖ write_constraints –format sdf –cover_design\ -output constraints.sdf