一种中速高精度模拟电压比较器的设计

一种新型高精度比较器电路

专利名称:一种新型高精度比较器电路专利类型:实用新型专利

发明人:梁会锋,林茂,于涛,沈怿皓

申请号:CN202121619285.9

申请日:20210716

公开号:CN215728408U

公开日:

20220201

专利内容由知识产权出版社提供

摘要:本实用新型公开了一种新型高精度比较器电路,包括模拟比较器,所述模拟比较器内包括内部参考电压生成电路和内部电阻分压电路,所述内部参考电压生成电路分别连接正端比较器和内部电阻分压电路,所述内部电阻分压电路连接负端比较器,所述正端比较器和负端比较器的输出端共同连接使能比较器。

本实用新型通过内部参考电压生成电路和内部电阻分压电路既可以实现两路外部输入电压EVN0与CMPN之间的比较,也可以实现VDD或外部输入的电压检测功能,且通过配置电阻分压网络寄存器实现比较器配置判断,增加比较和检测精度。

申请人:上海中基国威电子股份有限公司

地址:200000 上海市浦东新区中国(上海)自由贸易试验区芳春路400号1幢3层

国籍:CN

代理机构:上海汇齐专利代理事务所(普通合伙)

代理人:朱明福

更多信息请下载全文后查看。

【CN209731200U】一种高精度绝对电压比较器的实现电路【专利】

(19)中华人民共和国国家知识产权局(12)实用新型专利(10)授权公告号 (45)授权公告日 (21)申请号 201920489655.8(22)申请日 2019.04.09(73)专利权人 深圳市万微微电子技术有限公司地址 518000 广东省深圳市龙岗区宝龙街道宝龙社区宝龙四路2号安博科技宝龙厂区2号厂房1406(72)发明人 刘磊 熊力嘉 (74)专利代理机构 深圳市远航专利商标事务所(普通合伙) 44276代理人 田志远 张朝阳(51)Int.Cl.H03K 5/24(2006.01)(ESM)同样的发明创造已同日申请发明专利(54)实用新型名称一种高精度绝对电压比较器的实现电路(57)摘要本实用新型公开了集成电路设计技术领域中的一种高精度绝对电压比较器的实现电路,包括比较器,输入电压信号及基准电压,比较器的一个输入端经过第一分压电阻串接地,第一分压电阻串包括第一分压电阻和至少一个第一修调电阻;比较器的该输入端还经过第二分压电阻串与输入电压信号连接,第二分压电阻串包括第二分压电阻和至少一个第二修调电阻;每个第一修调电阻和每个第二修调电阻均与对应的金属熔丝并联。

本实用新型可以对单一电阻匹配误差/放大器输入随机匹配误差/参考源电压随机误差进行修调,得到所需的绝对精度的电压比较器,且可修调的精度高,整个修调操作简单,节省了修调所需时间和工艺成本,具有广泛适用性。

权利要求书1页 说明书6页 附图2页CN 209731200 U 2019.12.03C N 209731200U权 利 要 求 书1/1页CN 209731200 U1.一种高精度绝对电压比较器的实现电路,包括比较器,输入电压信号及基准电压,所述比较器的一个输入端与所述基准电压连接,其特征在于,所述比较器的另一输入端经过第一分压电阻串接地,所述第一分压电阻串包括第一分压电阻和第一修调电阻串,所述第一修调电阻串包括至少一个第一修调电阻;所述比较器的该另一输入端还经过第二分压电阻串与所述输入电压信号连接,所述第二分压电阻串包括第二分压电阻和第二修调电阻串,所述第二修调电阻串包括至少一个第二修调电阻;每个所述第一修调电阻和每个所述第二修调电阻均与对应的金属熔丝并联。

一种高性能的CMOS电压比较器设计

一 种 高性能 的 CMOS电压 匕较器 设计

文 /苟欣 杨 鸣

设 计 一 种 高性 能 的 电压 比 较 器 , 该 比较 器 采 用 两 级 放 大 电 路 和推 挽输 出级 电路,应 用 差分 放 大 电路 减 少 共 模 干 扰 , 应 用 共 源共 栅 电路 减 少失调 电压,应 用 推 挽 输 出 级 电路 提 高 输 出驱 动 能 力 。 在 Cadence环 境 下 基 于 TSMC 0.18 m CMOS工 艺 下 完 成 电压 比较 器 的设 计 。仿真 得 到 比较 器 的增 益 为 92.12 3dB,带 宽 为 10MHz, 上 升 延 时 为 91 3ps, 下 降延 时 为 7 54ps,失 调 电压 为 1 50 u V, 功 耗 为 0.289mW,版 图 面 积 为 29.56 gtm x 2 5.68 um。 它 具 有 高增 益、低 失调 电压、低 功耗 等特 点 ,可用 于 高精度 测 时 电路 中。

大 器提供 偏置 电压。通 过调 节 M 管 和 M,管 的宽长 比,让差分放大器和共源放大器得到合 适 的工作 电流 ,合理设计差分放大器和共源放 大器 ,主要考虑输入失调 电压、输入共模范 围、

可能低 ,该 电路 选取Vos5=O.2V,Vr,=0.8V。 因 此 , Vas5 Vos5+ VrN=lV。 选 取 VGs5 = IV。Vas5= 2= Vas2=IV, 可 以得 到 : VDSI= VGS1: D—Vvs2=2V

调 存储技术 (OOS)对失调 电压进行消 除,增 个推挽输 出级 电路 ,提升输 出信号的驱动 能力 , 电流 为 20gA。由式 (1)就 可 以得 出( /L)I

一种0_2_mV20_MHz600_W比较器

GHz[1] ,一般采用锁存器 (latch) 结构 ,但是失调比 果 ,第四部分给出了该比较器的版图。

较大 ,精度在 8 位以下 ,用于闪烁 ( Flash) 、流水线 ( Pipeline) 等高速 A/ D 转换器[224] 。高精度比较器 可以分辨较小的电压 ,但是速度相对比较慢 ,一般采

2 比较器结构

PMOS 作负载的差分运放结构 ,如图 2 所示 。M1 、 M2 是输入对管 ,与 M3 、M4 构成 Casco de 结构 ,可以

将回程噪声 (kickback

noi

se[

7

]

)

减小

g g

m3 m5

. .

4 6

倍

,

这在比

较器一端固定电位 , 另一端作输入应用的情况下尤

其重要 。M5 、M6 是 连 接 成 二 极 管 形 式 的 PMOS 管 ,作为 Cascode 输入级的负载 。整个电路的增益

图 4 小信号模型 Fig. 4 Small2signal model

图 4 中 , Gm1 、Gm2 分别是 M1 与 M3 、M2 与 M4 组成 的 Cascode 结构的等效跨导 ,忽略衬底调制效应 ,有

Gm1

=

g ml ro1 (

r o1 ( gm3 ro3 gm3 ro3 + 1)

假设比较器 1 ~ 3 、锁存器的输入失调分别为 V OS1 、V OS2 、V OS3 、V OSL , 比较器 1 ~ 3 的增益分别为 A1 、A2 、A3 ,开关 S3 与 S4 、S5 与 S6 注入到电容上的 电荷失配量分别为ΔQ3 ,4 、ΔQ5 ,6 , C1 = C2 = C3 = C4 = C ,那么 ,使用失调校准技术后 , 比较器的残余输入 失调为

电压比较器的设计陈磊

电压比较器的设计陈磊 崔丹 辛颖 宋毅彬(物理与电气信息工程学院 09应用物理 大庆师范学院)摘 要:电压比较器是集成运放在非线性状态下的具体应用,它源自于集成运放优良的性能,即趋于无穷大的电压放大倍数,使之两输入端谁的电位高输出反映谁的特征来完成比较功能. 深刻理解这一本质问题,对我们学习电子线路是十分重要的.关键词:集成运放;电压比较器;非线性应用0 引言电压比较器是一种常用的模拟信号处理电路,功能是将一个模拟电压与一个参考电压进行比较。

在自动控制及自动测量系统中,常常将比较器应用于报警、模/数转换以及各种非正弦波的产生和变换等。

由于比较器的输出只有高电位或低电位两种状态,所以其中的集成运放常常工作在非线性区域。

从电路结构来看,运放经常处于开环或正反馈状态。

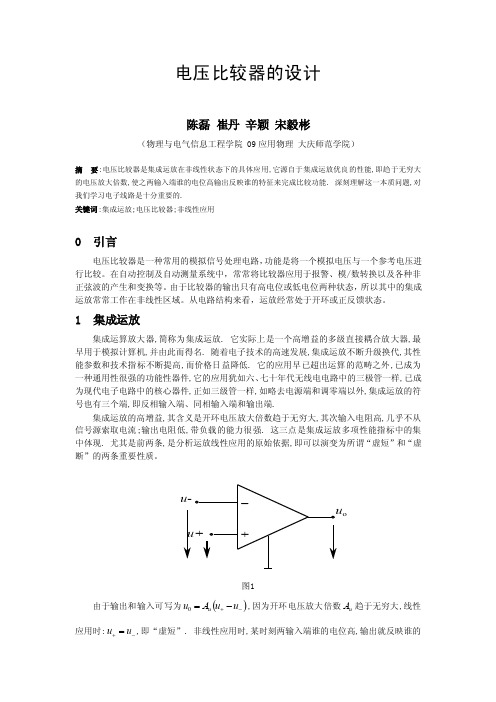

1 集成运放集成运算放大器,简称为集成运放. 它实际上是一个高增益的多级直接耦合放大器,最早用于模拟计算机,并由此而得名. 随着电子技术的高速发展,集成运放不断升级换代,其性能参数和技术指标不断提高,而价格日益降低. 它的应用早已超出运算的范畴之外,已成为一种通用性很强的功能性器件,它的应用犹如六、七十年代无线电电路中的三极管一样,已成为现代电子电路中的核心器件,正如三级管一样,如略去电源端和调零端以外,集成运放的符号也有三个端,即反相输入端、同相输入端和输出端.集成运放的高增益,其含义是开环电压放大倍数趋于无穷大,其次输入电阻高,几乎不从信号源索取电流;输出电阻低,带负载的能力很强. 这三点是集成运放多项性能指标中的集中体现. 尤其是前两条,是分析运放线性应用的原始依据,即可以演变为所谓“虚短”和“虚断”的两条重要性质。

u-u- _ u o + u+ u+ _图5-1 运放的符号+_+_ 图1 由于输出和输入可写为0u ()-+-=u u A u ,因为开环电压放大倍数u A 趋于无穷大,线性应用时:-+=u u ,即“虚短”. 非线性应用时,某时刻两输入端谁的电位高,输出就反映谁的特征,即:当-+>u u ,输出0u 趋于正向饱和;当-+<u u ,输出0u 趋于负向饱和. 这是集成运放运用于非线性状态的本质特征。

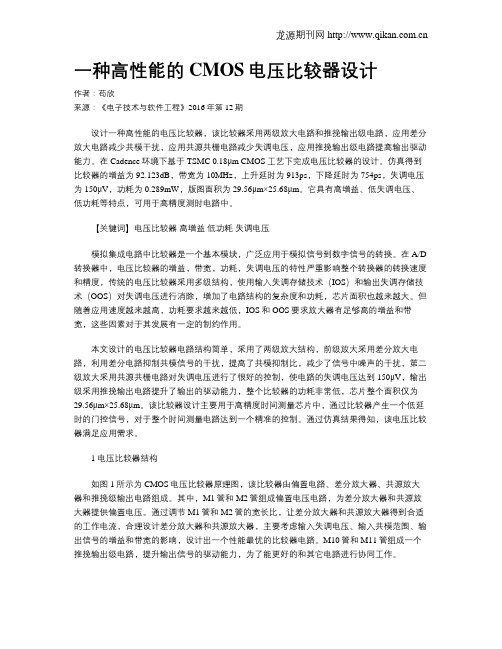

一种高性能的CMOS电压比较器设计

一种高性能的CMOS电压比较器设计作者:苟欣来源:《电子技术与软件工程》2016年第12期设计一种高性能的电压比较器,该比较器采用两级放大电路和推挽输出级电路,应用差分放大电路减少共模干扰,应用共源共栅电路减少失调电压,应用推挽输出级电路提高输出驱动能力。

在Cadence环境下基于TSMC 0.18μm CMOS工艺下完成电压比较器的设计。

仿真得到比较器的增益为92.123dB,带宽为10MHz,上升延时为913ps,下降延时为754ps,失调电压为150μV,功耗为0.289mW,版图面积为29.56μm×25.68μm。

它具有高增益、低失调电压、低功耗等特点,可用于高精度测时电路中。

【关键词】电压比较器高增益低功耗失调电压模拟集成电路中比较器是一个基本模块,广泛应用于模拟信号到数字信号的转换。

在A/D 转换器中,电压比较器的增益,带宽,功耗,失调电压的特性严重影响整个转换器的转换速度和精度,传统的电压比较器采用多级结构,使用输入失调存储技术(IOS)和输出失调存储技术(OOS)对失调电压进行消除,增加了电路结构的复杂度和功耗,芯片面积也越来越大。

但随着应用速度越来越高,功耗要求越来越低,IOS和OOS要求放大器有足够高的增益和带宽,这些因素对于其发展有一定的制约作用。

本文设计的电压比较器电路结构简单,采用了两级放大结构,前级放大采用差分放大电路,利用差分电路抑制共模信号的干扰,提高了共模抑制比,减少了信号中噪声的干扰,第二级放大采用共源共栅电路对失调电压进行了很好的控制,使电路的失调电压达到150μV,输出级采用推挽输出电路提升了输出的驱动能力,整个比较器的功耗非常低,芯片整个面积仅为29.56μm×25.68μm。

该比较器设计主要用于高精度时间测量芯片中,通过比较器产生一个低延时的门控信号,对于整个时间测量电路达到一个精准的控制。

通过仿真结果得知,该电压比较器满足应用需求。

一种中速高精度模拟电压比较器的设计

一种中速高精度模拟电压比较器的设计1引言在A/D转换器中,比较器重要性能指标是工作速度、精度、功耗、输入失调电压、正反馈时产生的回程噪声等,这些指标影响和制约着整个A/D转换器的性能。

高速比较器速度较快,一般采用锁存器(Latch)结构,但是失调和回程噪声较大,精度在8位以下,用于闪烁(Flash)、流水线(Pipeline)型等高速A/D转换器。

高精度比较器可分辨小电压,但速度相对较慢,一般采用多级结构,且较高的精度决定失调校准的必要性。

这里设计的比较器是用于输入范围2.5V、速度1MS/s、精度12位的逐次逼近型A/D转换器,为了满足A/D转换器的性能指标,则需采用中速高精度的比较器。

2比较器的设计由于该比较器用于输入电压2.5V、速度1MS/s、精度12位的逐次逼近型A/D转换器,因此比较器的精度至少应达到1/2LSB,即0.3mV的电压,速度高于12MHz,并且需要考虑一定的设计余量,所以暂定指标为精度O.2mV、速度20MHz。

该中速高精度的比较器通常采用多级结构实现。

在利用锁存器速度高、功耗小等优点的基础上,采用3级前置放大器组成的预放大级提高精度;采用输入失调储存与输出失调储存技术相结合的办法降低甚至抵消失调的影响;采用共源共栅、源随器结构的前置放大器和锁存器的时钟控制来抑制回程噪声的影响;采用数字触发电路获得高性能的数字输出信号。

需要注意的是必须准确处理好比较器的各个工作阶段,使其各部分协调工作,降低相互之间的干扰,以达到最优的性能。

2.1总体结构与失调校准技术图1为比较器电路的总体结构框图。

采用3级电容耦合的前置放大器加锁存比较器的结构,其中耦合电容可用于失调储存,开关用于控制比较器工作。

暂不考虑锁存比较器的时钟控制以及整个电路的复位工作,该比较器工作大致分为2阶段:首先是失调校准阶段,S1断开,S2闭合,使预放级1的正负输入端连接在中间电压Vcm上,同时,S3~S6闭合,这样预放级1的输出失调电压就存储在C1、C2上,预放级2和预放级3的输入失调电压则分别存储于C1、C2和C3、C4;然后是比较阶段,S1闭合,S2~S6断开,比较器开始比较Vcm和Vin,由于预放级1~3的失调电压绝大部分存储在电容C1~C4上,因此失调电压相互抵消,同时由于3级前置放大器增益的存在,锁存比较器失调电压的影响也减小相应倍数。

电压比较器的设计

一、实验目的

1.通过实验,熟悉电压比较器的原理;

2.掌握电压比较器的设计步骤和方法;

二、实验内容及原理

1.搭建求和型比较电路,分析比较电路的门限电平,

1)仿真观察输入为三角波的比较器输出信号,记录门限电平;

2)输入为三角波上叠加小幅值的高频正弦波信号时,记录电平比较器的“振铃”现象。

2.搭建滞回比较器,分析滞回比较电路的高低两个门限电平

1)仿真观察输入为三角波的比较器输出信号,记录门限电平;

2)输入为三角波上叠加小幅值的高频正弦波信号时,记录是否会出现“振铃”现象。

3.搭建窗口比较电路,分析输入为三角波信号时,输出信号的波形,并调整比较窗口门限电平,观察记录输出信号的波形变化。

三、实验步骤

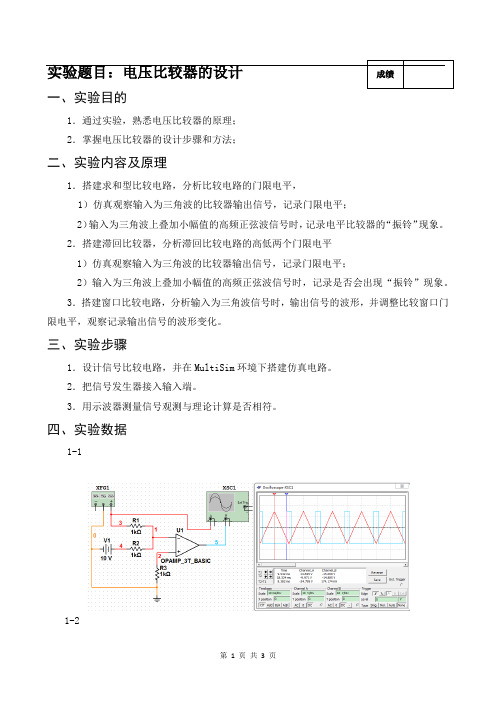

1.设计信号比较电路,并在MultiSim环境下搭建仿真电路。

2.把信号发生器接入输入端。

3.用示波器测量信号观测与理论计算是否相符。

四、实验数据

1-1

1-2

2-1

2-2

3-1

五、实验结论与感悟

熟悉了电压比较器的原理,掌握了电压比较器的设计步骤和方法。

相比于求和比较器,滞回比较器可以有效地消除振铃现象。

一种高性能的CMOS电压比较器设计

【关键词】电压比较器高增益低功耗失调电压模拟集成电路中比较器是一个基本模块,广泛应用于模拟信号到数字信号的转换。

在a/d 转换器中,电压比较器的增益,带宽,功耗,失调电压的特性严重影响整个转换器的转换速度和精度,传统的电压比较器采用多级结构,使用输入失调存储技术(ios)和输出失调存储技术(oos)对失调电压进行消除,增加了电路结构的复杂度和功耗,芯片面积也越来越大。

但随着应用速度越来越高,功耗要求越来越低,ios和oos要求放大器有足够高的增益和带宽,这些因素对于其发展有一定的制约作用。

本文设计的电压比较器电路结构简单,采用了两级放大结构,前级放大采用差分放大电路,利用差分电路抑制共模信号的干扰,提高了共模抑制比,减少了信号中噪声的干扰,第二级放大采用共源共栅电路对失调电压进行了很好的控制,使电路的失调电压达到150μv,输出级采用推挽输出电路提升了输出的驱动能力,整个比较器的功耗非常低,芯片整个面积仅为29.56μm×25.68μm。

该比较器设计主要用于高精度时间测量芯片中,通过比较器产生一个低延时的门控信号,对于整个时间测量电路达到一个精准的控制。

通过仿真结果得知,该电压比较器满足应用需求。

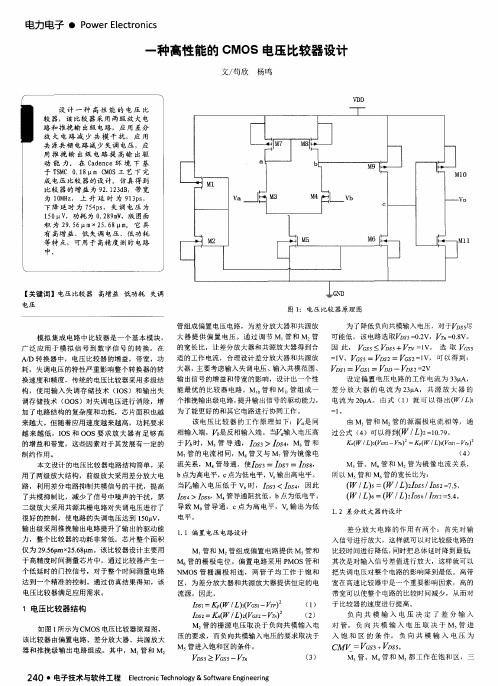

1 电压比较器结构如图1所示为cmos电压比较器原理图,该比较器由偏置电路、差分放大器、共源放大器和推挽级输出电路组成。

其中,m1管和m2管组成偏置电压电路,为差分放大器和共源放大器提供偏置电压。

通过调节m1管和m2管的宽长比,让差分放大器和共源放大器得到合适的工作电流,合理设计差分放大器和共源放大器,主要考虑输入失调电压、输入共模范围、输出信号的增益和带宽的影响,设计出一个性能最优的比较器电路。

m10管和m11管组成一个推挽输出级电路,提升输出信号的驱动能力,为了能更好的和其它电路进行协同工作。

该电压比较器的工作原理如下:是同相输入端,是反相输入端。

当输入电压高于时,m3管导通,,m3管和m7管的电流相同,m8管又与m7管为镜像电流关系,m8管导通,使,b点为高电平,c点为低电平,vo输出高电平。

模拟电路比较器设计

模拟电路比较器设计一、引言在电子电路设计领域,比较器是一种重要的元件,常用于比较两个电压的大小。

本文将介绍模拟电路比较器的设计原理和方法,以及一些常见的比较器电路。

二、比较器的工作原理比较器是一种高增益放大器,其输出电压取决于输入电压与参考电压的差异。

一般情况下,比较器的输入电压包括正输入和负输入两个端口,输出则取决于两个输入端口之间的电压差。

三、设计要点1. 选择比较器类型常见的比较器类型有开环比较器和闭环比较器,根据设计要求选择合适的比较器类型。

2. 输入电压范围根据实际应用需求确定输入电压的范围,并选择合适的比较器能够满足这一范围。

3. 参考电压选择根据比较器的输入电压范围选择合适的参考电压,确保比较器能够正确工作。

4. 输出逻辑电平确定比较器的输出逻辑电平,一般为高电平和低电平,并根据需要进一步设计输出电路。

四、常见比较器电路1. 基准电平比较器基准电平比较器使用一个恒定的参考电压作为基准,将输入电压与此参考电压进行比较。

当输入电压高于基准电平时,输出高电平;当输入电压低于基准电平时,输出低电平。

2. 连续比较器连续比较器常用于模拟信号处理电路中,通过连续比较输入信号与多个参考电平之间的差异,实现高精度的信号处理。

3. 比较器与其他电路的结合比较器可以与其他电路元件结合,如反馈电路、滤波电路等,以实现更复杂的功能。

五、实例:基准电平比较器设计以下是一个基准电平比较器的设计示例:1. 确定输入电压范围为0-5V。

2. 选择一个比较器,满足输入电压范围,并具有良好的响应速度。

3. 选择一个适当的基准电压,例如2.5V。

4. 连接输入电压和基准电压至比较器的正负输入端口。

5. 设计输出电路,将比较器的输出转换为需要的逻辑电平。

六、总结比较器作为电子电路设计中的重要元件,可以在很多应用中起到关键作用。

通过对比较器的设计原理和方法的了解,并使用适当的电路结构,可以实现各种复杂的电路功能。

综上所述,本文介绍了模拟电路比较器的设计原理和方法,以及一些常见的比较器电路。

模拟电路电压比较器设计

模拟电路电压比较器设计电压比较器是模拟电路中一种常用的电子元件,它可以将输入的电压与参考电压进行比较,并输出一个高或低电平来表示两者的关系。

在电路设计中,电压比较器扮演着重要的角色,尤其在模拟信号处理、自动控制以及传感器应用等领域。

一、电压比较器原理电压比较器的原理很简单,它通过将输入电压与参考电压进行比较,然后输出一个高电平或低电平来表示两者的关系。

通常情况下,当输入电压高于参考电压时,输出为高电平;当输入电压低于参考电压时,输出为低电平。

电压比较器可以看作是一个电压开关,当输入电压满足比较条件时,开关闭合,输出电平跃变,否则保持不变。

二、基本电路结构电压比较器的基本电路结构包括一个比较器和一个参考电压源。

比较器通常是一个高增益的差分放大器,它会放大输入电压的微小变化,并产生一个高或低电平输出信号。

参考电压源则用来设定比较的基准电压,可以通过电位器或其他电子元件来调节。

三、设计要点1. 确定比较器类型:在实际应用中,根据需求可以选用不同类型的比较器,包括共集电极比较器、差动比较器、窗口比较器等。

需要根据具体情况选择合适的比较器类型。

2. 确定参考电压:根据应用需求,确定参考电压的大小。

通常情况下,参考电压应该在输入信号的变化范围内,并且要考虑噪声、干扰等因素的影响。

3. 设置输出极性:根据实际需要,确定输出信号的极性,即输入电压高于参考电压时输出高电平还是低电平。

4. 考虑输出电压的稳定性:在设计过程中,需要注意输出电压的稳定性,尽量避免输出电压的抖动或漂移现象。

5. 调节器件参数:根据具体的比较器型号和应用需求,调节器件的参数,例如工作电流、电源电压、共模抑制比等,以保证电压比较器的性能和可靠性。

四、实例应用以温度控制为例,设计一个模拟电路电压比较器用于控制温度在一定范围内。

首先,选择一个合适的差动比较器作为比较器类型,因为差动比较器具有高精度和稳定性。

然后,确定参考电压为温度上限的2/3,以防止温度超过设定范围。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

一种中速高精度模拟电压比较器的设计

1引言

在A/D转换器中,比较器重要性能指标是工作速度、精度、功耗、输入失调电压、正反馈时产生的回程噪声等,这些指标影响和制约着整个A/D转换器的性能。

高速比较器速度较快,一般采用锁存器(Latch)结构,但是失调和回程噪声较大,精度在8位以下,用于闪烁(Flash)、流水线(Pipeline)型等高速A/D转换器。

高精度比较器可分辨小电压,但速度相对较慢,一般采用多级结构,且较高的精度决定失调校准的必要性。

这里设计的比较器是用于输入范围2.5V、速度1MS/s、精度12位的逐次逼近型A/D转换器,为了满足A/D转换器的性能指标,则需采用中速高精度的比较器。

2比较器的设计

由于该比较器用于输入电压2.5V、速度1MS/s、精度12位的逐次逼近型A/D转换器,因此比较器的精度至少应达到1/2LSB,即0.3mV的电压,速度高于12MHz,并且需要考虑一定的设计余量,所以暂定指标为精度O.2mV、速度20MHz。

该中速高精度的比较器通常采用多级结构实现。

在利用锁存器速度高、功耗小等优点的基础上,采用3级前置放大器组成的预放大级提高精度;采用输入失调储存与输出失调储存技术相结合的办法降低甚至抵消失调的影响;采用共源共栅、源随器结构的前置放大器和锁存器的时钟控制来抑制回程噪声的影响;采用数字触发电路获得高性能的数字输出信号。

需要注意的是必须准确处理好比较器的各个工作阶段,使其各部分协调工作,降低相互之间的干扰,以达到最优的性能。

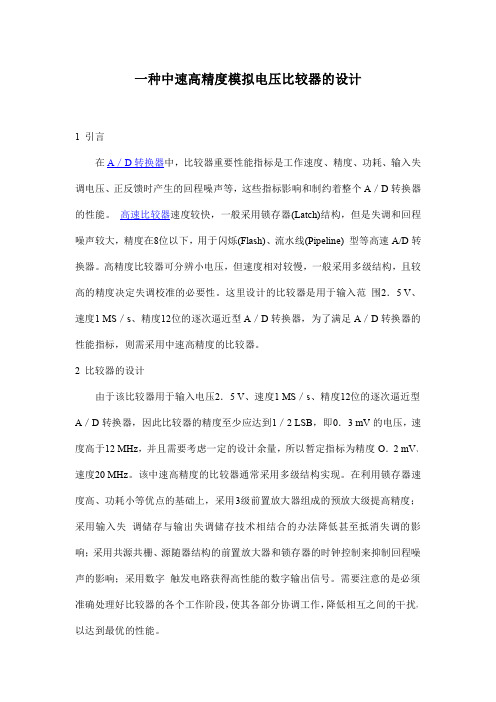

2.1总体结构与失调校准技术

图1为比较器电路的总体结构框图。

采用3级电容耦合的前置放大器加锁存比较器的结构,其中耦合电容可用于失调储存,开关用于控制比较器工作。

暂不考虑锁存比较器的时钟控制以及整个电路的复位工作,该比较器工作大致分为2阶段:首先是失调校准阶段,S1断开,S2闭合,使预放级1的正负输入端连接在中间电压Vcm上,同时,S3~S6闭合,这样预放级1的输出失调电压就存储在C1、C2上,预放级2和预放级3的输入失调电压则分别存储于C1、C2和C3、C4;然后是比较阶段,S1闭合,S2~S6断开,比较器开始比较Vcm和Vin,由于预放级1~3的失调电压绝大部分存储在电容C1~C4上,因此失调电压相互抵消,同时由于3级前置放大器增益的存在,锁存比较器失调电压的影响也减小相应倍数。

假设预放级1~3和锁存比较器的失调电压分别是Vos1、Vos2、Vos3、VosL,预放级1~3的增益分别为A1、A2、A3,开关S3、S4和S5、S6注入到电容上的电荷失配量分别为△Q3,4、△Q5,6电容C1~C4的电容量都为C,则使用失调校准技术后,比较器的残余输入失调将为:

从式(1)看出,要达到0.2mV的分辨率,还应根据锁存器的失调电压确定

前置放大器的增益。

由于锁存器的失调电压通常不会超过100mV,因此总增益可确定为500。

然后再来考虑增益分配问题。

预放级1需要将0.2mV的小信号输入迅速放大,所以预放级1的带宽要大。

在一定增益带宽积的前提下。

意味着增益要小,同时预放级1采用输出失调存储的失调校准技术,也要求预放级1增益要小,以避免因放大后的输入失调在电容C1、C2上饱和而达不到消除失调的效果。

同时,预放级2、3采用输出失调存储的失调校准技术,输入的信号幅度也较大,因此可采用较大的增益。

最终确定预放级1的增益约为5,预放级2、3的增益约为10。

2.2比较器第一级的结构

由于第一级前置放大器需将0.2mV的小信号输入迅速放大,同时采用输出失调存储的失调校准技术,这就要求它具有高带宽和低增益特点。

因此,预放级1可以采用二极管连接成PMOS作负载的差分运放结构,同时考虑本级也是整个高精度模拟电压比较器的输入极,它的噪声性能也对比较器的精度有影响,因此输入则采用共源共栅(Cascode)的结构,这可将回程噪声减小gm3,4/gm5,6倍,这在比较器一端固定电位,另一端作输入应用的情况下尤其重要,最后再加入一个源随器作为输出级,既可调节后级放大器的输入直流电平达到最佳值,又可起到隔离的效果改善噪声性能。

预放级1的电路如图2所示(后接的源随器未画出)。

假设电路是完全对称的结构,则整个电路的增益A1约为:

该值一般都在10以下,考虑到带宽要求和电容上失调电压饱和的问题,最终确定其取值约为5。

同时,在输出端Out+与Out-之间加入复位开关,在每个比较

周期的最初,由复位信号控制开关闭合。

将预放级1复位,加快比较速度。

2.3比较器第二、三级的结构

预放级2与预放级3采用相同的电路结构,为了增加放大器的增益,它在预放级1的电路基础上加入了2个交叉的PMOS管VM7、VM8,在电路中引人了弱正反馈机制,但缩减了带宽。

由于预放级2的输入信号比预放级3小。

设计时也可适当增大预放级2的电流,有助于提高比较速度。

其电路如图3所示(后接的源随器未画出)。

同样假设电路是完全对称的,则通过弱反馈补偿后,电路的增益约为:

需要注意的是,迟滞比较器也是采用如图3所示的电路结构,所不同的是迟滞比较器使用了强正反馈机制。

两者的区别就在于交叉的PMOS管VM7、VM8引入的电流相对于PMOS管VM5、VM6的电流的大小不同。

当PMOS管VM7、VM8的电流大于PMOS管VM5、VM6的电流时,整个电路呈正反馈状态;反之,电路中的正反馈不足以抵消负反馈,整个电路呈负反馈状态。

由于电路在大信号分析中PMOS管VM5~VM8的过载电压是相同的,因此它们的电流和宽长比成正比,故VM5的宽长比一定要大于VM7的宽长比才能实现弱正反馈。

2.4锁存比较器与数字触发电路

锁存器实际上就是2个反相器首尾互连,由于利用反相器的正反馈的机制,输出信号与时间呈正指数关系变化,因此可将输入的小信号差量迅速放大到数字可识别的电平。

同时,锁存器具有低功耗特点,因为它在一段时间内是不工作的,此时干路的开关被切断,因此无电流,功耗降低。

然而,正是由于这样的工作特点。

使锁存器工作时的输出状态并未持续一个时钟周期,为了串行数字输出正确以及给D/A转换器提供正确的置位信号,再生放大器后面应加适当的触发电路,以便在再生放大器工作期间正确输出持续时间为一个周期的比较结果。

因此,设计出如图4所示的电路。

当φ为低电平时,输入信号In+和In-与锁存器接通,而锁存器与电源、地相连的开关均断开,锁存器处于感应输入信号阶段;同时,在数字触发电路中,高电平φ/使得开关管VMN7、VMN8导通接地,此时,低电平φ//分别通过VMP4、VMN4组成的反向器和VMP6、VMN6组成的反向器分别到达2个与非门的输入端并将其值置为高电平1,使得后级的数字RS触发器呈保持状态,持续保持输出不变。

当φ为高电平时,输入信号In+和In-与锁存器断开,而锁存器与电源、地相连的

开关接通,锁存器处于正反馈工作段,输出信号Out+、Out-与时间呈正指数关系变化,使输出迅速达到电源电压或低电平,直接满足数字输出要求;同时,在数字触发电路中,低电平φ/使得开关管VMN7、VMN8关断,高电平φ//别使VMP4、VMP6关断和VMN4、VMN6导通,因此,此时2个与非门的输入端便分别成为了由VMP3、VMN3组成的反向器和VMP5、VMN5组成的反向器的输出端,其取值直接由反向器的输入Out+、Out-决定.使得后级的数字RS触发器根据输入的变化而变化,得到正确输出。

3比较器的工作时序与仿真

考虑到要最大限度降低锁存器和数字触发电路部分对前面的模拟电路部分产生的干扰,以及使比较器在每个比较周期完成后迅速复位,必须使用复位控制。

该比较器工作过程依次分为失调校准和比较两个阶段。

比较阶段由数个比较周期组成,在每个比较周期开始时(除了失调校准结束后的第一个比较周期),预放级1~3和锁存器在复位信号rst的作用下进行复位操作;在每个比较周期结束时,锁存器在锁存信号西作用下锁存放大信号。

仿真中使用Hspice进行瞬态仿真验证,为了降低比较器功耗和干扰,设定锁存信号φ的有效信号占空比为1:8,要达到20MHz的速度,则锁存信号的周期应为50ns。

为此。

设定Vcm=1.2V,而Vin每50ns变化一次,从0ns到250ns 分别为1.2V,1.2002V,1.1998V,2V,1.1998V,其中,0~50ns期间,比较器处于失调校准阶段,之后每个比较周期为50ns。

当预放级1~3无输入失调,存在20mV输入失调时,比较器的仿真结果分别如图5和图6所示,其中西为锁存信号,rst为复位信号,Out为比较器输出,Vo3+、Vo3-为预放级3的输出信号。

由仿真结果知,比较器在上述的Vcm和Vin的输

入下,能够在20MHz的输人信号频率下准确输出结果。

因此,该比较器既能够准确的识别0.2mV的小信号,也能在0.8V的大信号输入下具有很强恢复能力。

而当预放级1~3都有20mV输入失调时,从图5看出,预放级3的输出会在复位信号后产生波动,但由于使用了恰当的失调校准技术,波动后的信号依然能够快速复位,比较器依然能够准确有效地辨别电压。

也就是说,20mV输入失调并没有淹没小至0.2mV的小信号输入差值,失调校准技术取得预期效果。

4结束语

在传统的多级结构的基础上,实现中速高精度模拟电压比较器。

通过仿真,比较器达到各项预定指标,在20mV输入失调下精度达到0.2mV,速度20MHz,功耗约1mW。