十进制可逆加减计数器

Proteus十进制加减可逆计数器的设计

课程设计任务书学生姓名:专业班级:指导教师:工作单位:题目: 十进制加/减可逆计数器设计初始条件:电脑一台、Proteus软件、数模电相关基础要求完成的要紧任务:(包括课程设计工作量及其技术要求,和说明书撰写等具体要求)1、技术要求:设计M=125或给定值的十进制加/减可逆计数器,要求如下:A、给定元件为74LS00,74LS76,74LS192,74LS48及数码管等;B、进行电路仿真,并说明其工作原理;2、要紧任务:(1)温习有关课程,如数字电路、模拟电路等;(2)自学Proteus软件,能够熟练地进行仿真;(3)依照设计指标设计电路的框图;(4)依照要求设计出电路图;(5)查阅资料,确信所需各元器件型号和参数;(6)自拟调整测试方式,并调试电路使其达到仿真要求;(7)撰写设计说明书,进行答辩。

3、撰写课程设计说明书:装订顺序要求:封面→任务书→目录→正文→参考文献。

正文:一、技术指标;二、设计方案及其比较;3、实现方案;4、调试进程及结论;五、心得体会;六、参考文献时刻安排:课程设计时刻:19周-20周19周:明确任务,查阅资料,初步设计电路原理图;20周:依照电路原理图布线,并调试通过。

依照要求撰写课程设计说明书。

指导教师签名:年月日系主任(或责任教师)签名:年月日目录摘要 (I)1技术指标 (1)2设计方案及其比较 (2)设计方案 (2)设计思路 (2)手控方式计数器设计思路 (2)自控方式计数器设计思路 (4)集成电路及元件选择 (5)3实现方案 (6)手动操纵计数器实现方案 (6)计数单元的设计 (6)译码显示单元电路设计 (7).1译码器74LS48 (7)显示器LG5011AH (9).3译码显示电路 (10)加/减计数操纵电路的设计 (10)总原理图的设计 (12)自动操纵计数器实现方案 (13)4 Proteus仿真 (14)Proteus简介 (14)电路仿真 (15)放置元件 (15)参数设置 (18)布线与调整 (20)仿真 (21)5课程设计心得体会 (22)参考文献 (23)摘要计数器是数字电路中最为大体的一个单元电路。

欧姆龙plc计数器指令的功能详述

欧姆龙plc计数器指令的功能详述欧姆龙plc计数器指令CNT是单向计数器,CNTR是可逆计数器。

这两种计数器在编程时都需要设定计数值。

设定值用4位十进制数表示,范围0~9999。

设定值既可表示成立即数形式(设定值前加“#”),也可以放在通道中(设定值前无“#”即表示通道号)。

(1)单向计数器CNT。

单向计数器的计数输入端CP每接通1次(从OFF到ON),计数值减1。

当计数值减到0时,计数器的触点动作。

当计数器的复位端R接通时,计数器被复位,其常开触点断开,常闭触点闭合,且计数值恢复到设定值。

单向计数器的使用如图3-30。

计数器CNT0001的计数设定值是3,输入继电器触点000005每接通1次,计数值减1。

当触点000005接通3次时,CNT0001计数到,其常开触点C0001闭合,使输出继电器000101接通。

当输入继电器触点000000接通时,计数器CNT0001被复位,其常开触点断开,输出继电器000101断开。

图3-30梯形图对应的指令助记符程序如下所示。

图3-30 CNT指令梯形图图3-30梯形图的波形图如图3-31所示,由图可见,在输入继电器触点000000接通期间,触点000005有两次接通,但此时计数器不计数,因为当计数逻辑CP与复位逻辑R同时接通时,复位优先。

只有触点000000断开后,计数器才开始计数,输入继电器触点000005每接通1次,计数器计数值减1,当接通3次时,计数器计数值减到0,其常开触点动作,使输出继电器000101产生输出。

此后,000005再接通,计数器仍然是计数到,其常开触点C0001一直保持闭合,直到被复位。

波形图中000005脉冲上方数字表示该脉冲到来时,计数器的当前值。

图3-31 图3-30梯形图的波形图(2)可逆计数器CNTR。

可逆计数器既可递增计数,又可递减计数。

它有3个输入端:加计数端II、减计数端DI和复位端R。

加计数端每接通1次,可逆计数器的值加1;减计数端每接通1次,可逆计数器的值就减1;无论何时复位端接通,可逆计数器均被复位成0。

两位同步十进制可逆计数器的设计综述

湖北师范学院文理学院信息工程系2010级电子信息工程专业综合课程设计(一)文理学院综合课程设计(一)Integrated Curriculum Design(1)两位同步十进制可逆计数器的设计1 设计目的(1)熟悉各种触发器的使用及时序逻辑电路的设计方法;(2)掌握中规模集成十进制可逆计数器74LS192的逻辑功能和使用方法;(3)了解计数器的功能扩展及显示器的应用和它们的运行过程中是如何实现相关功能的。

2 设计思路第一步:将两片74LS192进行级联,用“反馈清零法”设计一个两位十进制加法计数器,反馈清零信号取自输出端Q0 ~Q3 ;第二步:将两片74LS192进行级联,用“反馈置数法”设计一个两位十进制减法计数器,反馈置数信号取自计数器最高位的借位端TCD;第三步:将上述加、减计数器电路结合起来,即初步构成一个加/减两位十进制可逆计数器。

余下的问题就是在加/减可逆计数条件下,如何切换计数器最低位的计数脉冲输入端CPD、CPU的信号。

经过分析,这一功能通过单刀双掷开关即可实现。

整个可逆计数器电路(不包括数字显示部分)的设计框图如下图图1(可逆计数器设计框图)3 设计过程整个设计可分为三个部分,具体如下:第一部分:提供持续的脉冲信号;第二部分:计数单元的设计;第三部分:用两个74LS192组成两位十进制可逆计数器。

其中第二部分由74LS192双十钟方式的可逆计数器组成,其引脚图如下图2所示,功能表如下表1所示:图2(74LS192的引脚图)表1(74LS192的功能表)第三部分的设计框图如下图3所示:图3(两个74LS192组成十进制可逆计数器)低位计数器的CPU 端与计数脉冲输入端相连,进位输出端与高一位计数器的CPU 端相连3.1方案论证通过仿真软件进行实际验证,改变脉冲信号进行计数,通过开关控制,看是否能实现相关功能,论证方案:将线路处于工作状态,调节开关置零,然后进行置数,将输入端置为0111,拨动开关使电路进行加计数,当加到99时自动置零,然后将开关调置另一边进行减计数。

一位十进制数加减法器

一位十进制数加减法器引言在计算机领域中,数字加减法是最基础且常见的算术运算。

为了实现有效的数字加减法运算,我们需要使用加减法器。

本文将介绍一位十进制数加减法器的设计和功能。

一位十进制数加减法器的原理一位十进制数加减法器是用来对两个十进制数进行加法或减法运算的电路。

它包含三个输入端和两个输出端:•输入端:两个十进制数(A和B)和一个控制输入(Cin)。

•输出端:一个和输出(Sum)和一个进位输出(Cout)。

一位十进制数加减法器根据控制输入的不同来执行不同的操作,具体原理如下:1. 加法操作•输入:A、B和Cin。

•输出:Sum和Cout。

加法操作的实现可以采用如下步骤:1.将A、B和Cin输入到加法器电路中。

2.对A和B进行加法运算,得到结果与进位。

3.Sum输出运算结果,Cout输出进位。

2. 减法操作•输入:A、B和Cin。

•输出:Sum和Cout。

减法操作的实现可以采用如下步骤:1.将A、B和Cin输入到减法器电路中。

2.对A和B进行减法运算,得到结果与借位。

3.Sum输出运算结果,Cout输出借位。

一位十进制数加减法器的设计一位十进制数加减法器的设计需要考虑以下几个方面:1.加法器和减法器电路的设计。

2.输入和输出信号的处理和传输。

3.控制输入的处理和判断。

1. 加法器和减法器电路的设计加法器和减法器电路的设计可以采用逻辑门电路来实现。

对于加法操作,可以通过使用XOR门和AND门来实现加法运算和进位计算。

对于减法操作,可以通过使用补码变换和与非门来实现减法运算和借位计算。

2. 输入和输出信号的处理和传输输入和输出信号的处理和传输可以通过触发器来实现。

触发器是一种存储器件,可以存储和传输信号。

输入信号可以存储在输入触发器中,通过触发器传输到加减法器电路中进行运算。

运算结果可以存储在输出触发器中,通过触发器输出到外部。

3. 控制输入的处理和判断控制输入的处理和判断可以通过逻辑电路来实现。

根据控制输入的不同值,可以判断是执行加法操作还是减法操作,并将相应的输入信号传递给加减法器电路。

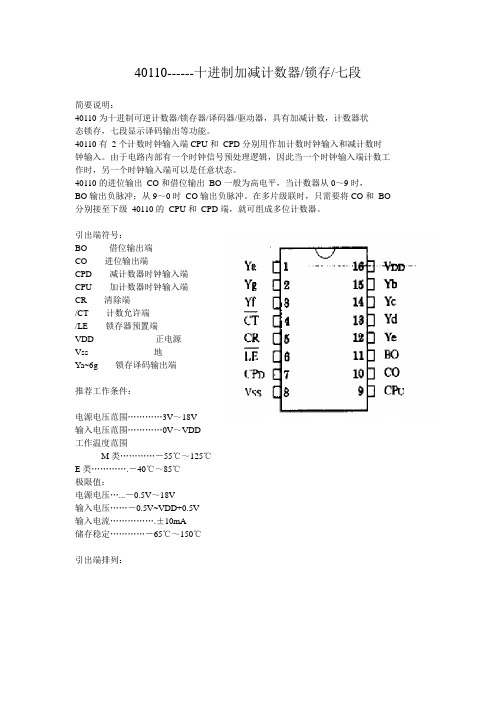

CD40110简洁中文资料

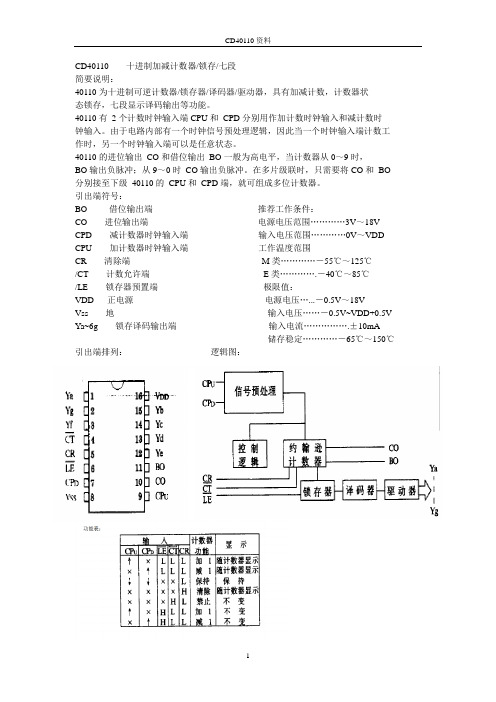

40110------十进制加减计数器/锁存/七段简要说明:40110为十进制可逆计数器/锁存器/译码器/驱动器,具有加减计数,计数器状态锁存,七段显示译码输出等功能。

40110有2个计数时钟输入端CPU和CPD分别用作加计数时钟输入和减计数时钟输入。

由于电路内部有一个时钟信号预处理逻辑,因此当一个时钟输入端计数工作时,另一个时钟输入端可以是任意状态。

40110的进位输出CO和借位输出BO一般为高电平,当计数器从0~9时,BO输出负脉冲;从9~0时CO输出负脉冲。

在多片级联时,只需要将CO和BO 分别接至下级40110的CPU和CPD端,就可组成多位计数器。

引出端符号:BO 借位输出端CO 进位输出端CPD 减计数器时钟输入端CPU 加计数器时钟输入端CR 清除端/CT 计数允许端/LE 锁存器预置端VDD 正电源Vss 地Y a~6g 锁存译码输出端推荐工作条件:电源电压范围…………3V~18V输入电压范围…………0V~VDD工作温度范围M类…………-55℃~125℃E类………….-40℃~85℃极限值:电源电压…...-0.5V~18V输入电压……-0.5V~VDD+0.5V输入电流…………….±10mA储存稳定…………-65℃~150℃引出端排列:12本设计主要基于CD40110,设计的秒、分时钟电路CD40110 内部集成了计数、译码、锁存器的功能,因此可以省去一些译码芯片,内部有加法器与减法器两种功能,都是十进制的图中的1Hz的信号,可经过555多谐振荡产生,也可以通过晶振32768经过分频得到,也可以通过把市电经过50分频得到还可以加入时间调整,报时模块。

十进制加法计数器

在数字系统中,常需要对时钟脉冲的个数进行计数,以实现测量、运算和控制等功能。

具有计数功能的电路,称为计数器。

计数器是一种非常典型、应用很广的时序电路,计数器不仅能统计输入时钟脉冲的个数,还能用于分频、定时、产生节拍脉冲等。

计数器的类型很多,按计数器时钟脉冲引入方式和触发器翻转时序的异同,可分为同步计数器和异步计数器;按计数体制的异同,可分为二进制计数器、二—十进制计数器和任意进制计数器;按计数器中的变化规律的异同,可分为加法计数器、减法计数器和可逆计数器。

二进制加法计数器运用起来比较简洁方便,结构图和原理图也比其它进制的简单明了,但二进制表示一个数时,位数一般比较长。

十进制是我们日常生活中经常用到的,不用转换,所以设计十进制加法计数器比设计二进制加法计数器应用广泛,加法器是以数据的累加过程,日常生活中,数据的累加普遍存在,有时候需要一种计数器对累加过程进行运算处理,所以设计十进制加法计数器应广大人们生活的需要,对我们的生活有一个积极地促进作用,解决了生活中许多问题,所以会设计十进制加法计数器使我们对数字电路的理论和实践知识的充分结合,也使我们对电子技术基础有了深刻的了解,而且增强了我们对电子技术基础产生了浓厚的兴趣,这次课程设计使我受益匪浅!一、设计题目 (3)二、设计目的 (3)三、设计依据 (3)四、设计内容 (3)五、设计思路 (4)六、设计方案 (7)七、改进意见 (10)八、设计总结 (11)九、参考文献 (12)一、设计题目十进制加法计数器二、设计目的1.学习电子电路设计任务。

2.通过课程设计培养学生自学能力和分析问题、解决问题的能力。

3.通过设计使学生具有一定的计算能力、制图能力以及查阅手册、使用国家技术标准的能力和一定的文字表达能力。

三、设计依据1.用JK触发器组成。

2.实现同步或异步加法计数。

四、设计内容1.复习课本,收集查阅资料,选定设计方案;2.绘制电气框图、电气原理图;3.对主要元器件进行计算选择,列写元器件的规格及明细表;4.设计总结及改进意见;5.参考资料;6.编写说明书。

课程设计—分频器的制作

电子技术课程设计报告学院:专业班级:学生姓名:学号:指导教师:完成时间:成绩:分频器的制作设计报告一. 设计要求把1000HZ的信号分成500Hz,100Hz的信号,用拨动开关控制。

发挥部分:1、200Hz信号的产生 2、倍频信号的产生。

二. 设计的作用、目的1、掌握运用中规模集成芯片设计分频器的方法。

2、掌握使用与非门、555单稳态产生倍频信号的方法。

三.设计的具体实现1、单元电路设计(或仿真)与分析1、分频信号的产生:电路图如下74ls192是同步十进制可逆计数器,具有双时钟输入,并具有异步清零等功能。

在此电路中,计数器处于加计数状态,输入脉冲1000Hz由5脚输入,用清零法组成进制可变的计数器,并通过单刀双掷开关控制。

仿真结果图如下:①当开关拨到1档时,上面频率计数器计输入信号频率为1000Hz,下面频率计数器计数频率为500Hz信号。

②当开关拨到2档时,上面频率计数器计输入信号频率为1000Hz,下面输出频率计数器显示100Hz信号。

2、200Hz信号的产生:电路图如下74ls192是同步十进制可逆计数器,具有双时钟输入,并具有异步清零等功能。

仿真结果图如下:在此电路中,计数器处于加计数状态,输入脉冲1000Hz由5脚输入,用清零法组成进制可变的计数器,2脚即输出200Hz信号。

2、倍频信号的产生:倍频信号原理图如下,输入信号由最左端输入方波(频率大于1000Hz并且峰峰值大于3v小于5v效果好)其中第一个与非门连接成非门使用,起着对输入信号倒相的作用。

这样,当有一个方波脉冲信号输入时,由C1、R1组成的微分电路将在脉冲信号的前沿产生一个正向微分脉冲信号,同时在方波下降沿处产生负向脉冲,另一路经过反相后,C2、R2微分电路产生负向脉冲(另一路产生正向脉冲同时)和负向脉冲,经过二极管滤除正向脉冲作为555单稳态的2脚触发端输入信号,而555单稳态3脚输出倍频后的方波。

仿真结果图如下:左端频率计数器显示的是输入的1000Hz的信号,右端频率计数器显示的是倍频后输出的2000Hz的信号示波器显示:号2000Hz。

汇编语言实现十进制加减计算器资料

课程设计题目十进制数加减计算器学院计算机科学与技术专业计算机科学与技术班级计算机0808班姓名何爽指导教师袁小玲2010 年12 月31 日课程设计任务书学生姓名:何爽专业班级:计算机0808班指导教师:袁小玲工作单位:计算机科学与技术学院题目: 十进制数加减计算器的设计初始条件:理论:学完“汇编语言程序设计”、“课程计算机概论”、“高级语言程序设计”和“数字逻辑”。

实践:计算机学院科学系实验中心提供计算机和软件平台。

如果自己有计算机可以在其上进行设计。

要求完成的主要任务:(包括课程设计工作量及其技术要求,以及说明书撰写等具体要求)(1)十进制数加减计算器的设计。

(2)程序应有操作提示、输入和输出,界面追求友好,最好是菜单式的界面。

(3)设计若干用例(测试数据),上机测试程序并分析(评价)所设计的程序。

(4)设计报告格式按附件要求书写。

课程设计报告书正文的内容应包括:在正文第一行写课程设计题目;1.需求说明(要求、功能简述)或问题描述;2.设计说明(简要的分析与概要设计);3.详细的算法描述;4.源程序与执行结果(含测试方法和测试结果);5.使用说明;6.总结,包括设计心得(设计的特点、不足、收获与体会)和展望(该程序进一步改进扩展的设想)。

时间安排:设计时间一周:周1:查阅相关资料。

周2:系统分析,设计。

周3~4:编程并上机调试。

周5:撰写课程设计报告。

设计验收安排:20周星期五8:00起到计算机学院科学系实验中心进行上机验收。

设计报告书收取时间:20周的星期五下午5:00之前。

指导教师签名: 2010年12月31日系主任(或责任教师)签名: 2010年12月31日目录1.需求说明 (4)2.设计说明 (4)2.1 简要分析 (4)2.2 概要设计 (4)2.2.1 主要模块 (4)2.2.2 主函数结构 (5)3.详细的算法描述 (6)3.1 详细的算法描述 (6)3.2 算法流程图 (11)3.2.1 程序流程图 (11)3.2.2 输入函数(inputdec)流程图 (12)3.2.3 输出函数(outputdec)流程图 (12)3.2.4 输出算术表达式函数(show)流程图 (13)4.源程序与执行结果 (13)4.1 源程序 (13)4.2 执行结果 (19)4.2.1 测试方法 (19)4.2.2 测试结果 (19)5.使用说明 (20)6.总结 (21)十进制数加减计算器的设计1.需求说明十进制数加减计算器的设计,要求完成:(1)用汇编语言正确编写程序,完成简单的十进制数的加减运算,(2)求能正确进行输入和输出操作,界面追求友好,尽量实现菜单操作(3)用若干测试用例来测试程序的正确性2.设计说明2.1 简要分析要正确、友好地完成用汇编语言设计十进制数的加减计算器,我们应该完成以下几个功能:(1)相关菜单及字符输出的设计(2)十进制数的输入(3)十进制数的输出(4)加法运算(5)减法运算(6)输出运算表达式(7)回车换行功能(因为为了控制格式,经常要用到)2.2 概要设计2.2.1 主要模块(1)菜单及字符menu db ‘|--------------------------------------|’0dh,0ahdb ‘| 1.Add |’0dh,0ahdb ‘| 2.Sub |’0dh,0ahdb ‘| 0.Exit |’0dh,0ahdb ‘|--------------------------------------|’0dh,0ahdb ‘Please input your choice:$’mess1 db 'Please input the first number: $'mess2 db 'Please input the second number: $'mess3 db 'The result is : $'mess4 db '-$'mess5 db '+$'mess6 db '=$'(2)十进制数的输入inputdec proc实现代码retinputdec endp(3)十进制数的输出outputdec proc实现代码retoutputdec endp(4)加法运算addfun proc显示mess1 ;提示输入第一个数call inputdec ;输入第一个数显示 mess2 ;提示输入第二个数call inputdec ;输入第二个数做加法运算显示mess3 ;提示输入第一个数call show ;输出运算表达式retaddfun endp(5)减法运算subtract proc显示mess1 ;提示输入第一个数call inputdec ;输入第一个数显示 mess2 ;提示输入第二个数call inputdec ;输入第二个数做减法运算显示mess3 ;提示输入第一个数call show ;输出运算表达式retsubtract endp(6)输出运表达算式函数show proccall outputdec ;输出第一个数输出运算符号call outputdec ;输出第二个数输出等号call outputdec ;输出运算结果retshow endp(7)回车换行crlf proc实现代码retcrlf endp2.2.2 主函数结构main proc显示menu ;供选择输入选项判断选项Case 1: call addfunCase 2: call subtractCase 3: 退出程序main endp3.详细的算法描述3.1详细的算法描述(1)main函数main procpush dsxor ax,axpush axmov ax,datamov ds,axks:lea dx,menu ;输出菜单项mov ah,09hint 21hmov al,0mov ah,01h ;输入选择项int 21hsub al,30hcmp al,2 ;判断选择项jz l2 ;如果输入为2 ,则跳转到l2cmp al,1jz l1 ;如果输入为1,则跳转到l1mov ah,4ch ;这两句为正常返回dos界面int 21hl1:call addfun ;调用加法函数jmp ks ;返回到菜单l2: call subtract;调用减法操作jmp ks ;返回到菜单main endp(2)addfun函数(加法运算函数)addfun proccall crlfmov bp,1 ;给下面的show输出中间的运算符做标记,1为加号 lea dx,mess1 ;给出输入第一个数的提示信息mov ah,09hint 21hcall inputdec;调用输入函数,输入第一个数mov si,bx ;第一个数保存在si中lea dx,mess2 ;给出输入第二个数的提示信息mov ah,09hint 21hcall inputdec;调用输入函数,输入第二个数mov di,bx ;第二个数保存在di中mov bx,si ;将第一个数保存到bx中,再进行操作,以免影响到的输出 add bx,di ;第一个数和第二个数相加,结果保存在bx中lea dx,mess3 ;给出输出结果的提示信息mov ah,09hint 21hcall show ;调用show函数,输出算术表达式ret ;返回函数调用处addfun endp(3)subtract函数(减法运算函数)subtract proccall crlfmov bp,2 ;给下面的show输出中间的运算符做标记,2为减号lea dx,mess1;给出输入第一个数的提示信息mov ah,09hint 21hcall inputdec;调用输入函数,输入第一个数mov si,bx ;第一个数保存在si中lea dx,mess2 ;给出输入第一个数的提示信息mov ah,09hint 21hcall inputdec;调用输入函数,输入第一个数mov di,bx ;第二个数保存在di中mov bx,sicmp bx,di ;比较第一个数和第二人数的大小js subl1 ;如果为负(第一个数小一些)则跳转sub bx,di ;否则直接进行计算,结果保存在bx中jmp subl2subl1:mov bp,3 ;为show里面是否输出负号作准备,3的时候要输出负号push di ;先将第二个操作数进栈,否则下面的减法操作会将其值改变 sub di,bxmov bx,dipop di ;第二个操作数出栈,再赋给di寄存器subl2:lea dx,mess3 ;输出运算表达式的提示mov ah,09hint 21hcall show ;调用show函数,输出运算表达式retsubtract endp(4)inputdec函数(十进制输入函数)inputdec procmov bx,0il0:mov ah,01h ;输入数字int 21hcmp al,0dh ;判断是否为回车jz iexit ;如果是回车,则返回到函数调用处sub al,30h ;得到输入数字的真实大小mov ah,0xchg bx,ax ;将bx值与ax值交换,因为下面乘以10是将ax中的值乘10 mov cx,10 ;注意,这里不能用CL,否则数较大时就会出现问题mul cx ;将ax中的值乘以10,也就是将bx中原来的值乘以10add bx,axjmp il0 ;进行输入下一数值位iexit:call crlfretinputdec endp(5)outputdec函数(十进制输出函数)outputdec procpush bpmov bp,0 ;前导0输出与否的标志,0时不输出,1时输出mov ax,bxmov dx,0 ;在进行除法之前,要对dx赋0,否则结果出错mov cx,10000div cx ;除法,字操作,商在ax中,余数在dx中mov bx,dx ;保存余数,作为下一次裤除数mov dl,alcmp dl,0 ;将万位同0比较jz ol0 ;如果万位为0则不输出万位mov bp,1 ;如果万位不为0,则应将bp设为1,以后的0都要输出or dl,30hmov ah,02hint 21h ;输出万位ol0:mov ax,bx ;输出千位的方法与万位相同mov dx,0mov cx,1000div cx ;字操作,商在ax中,余数在dx中mov bx,dx ;保存余数,作为下一次裤除数mov dl,alcmp bp,0jz ol1or dl,30hmov ah,02hint 21h ;输出千位jmp ol2ol1:cmp dl,0jz ol2mov bp,1or dl,30hmov ah,02hint 21h ;输出千位ol2:mov ax,bx ;输出百位与千位、万位方法相同mov dx,0mov cx,100div cx ;字操作,商在ax中,余数在dx中mov bx,dx ;保存余数,作为下一次裤除数mov dl,alcmp bp,0jz ol3mov bp,1or dl,30hmov ah,02hint 21h ;输出百位jmp ol4ol3:cmp dl,0jz ol4or dl,30hmov ah,02hint 21h ;输出百位ol4:mov ax,bx ;输出十位的方法与前面几位方法相同mov cl,10div cl ;字节操作,商在al中,余数在ah中mov bl,ah ;保存余数,作为下一次裤除数,也就是个位数mov dl,alcmp bp,0jz ol5mov bp,1or dl,30hmov ah,02hint 21h ;输出十位jmp ol6ol5:cmp dl,0jz ol6or dl,30hmov ah,02hint 21h ;输出十位ol6:mov dl,bl ;在上面,bl中的数直接就应该为个位,所以直接输出or dl,30hmov ah,02hint 21hpop bp ;恢复bpretoutputdec endp(6)show函数(输出运算表达式函数)show procpush bx ;把运算结果保存起来mov bx,si ;第一个数放在si中call outputdec;输出第一个数cmp bp,3 ;是否为减号jz sl0cmp bp,2 ;判断是否为减号jz sl0lea dx,mess5 ;输出加号mov ah,09hint 21hjmp sl1sl0:lea dx,mess4 ;输出减号mov ah,09hint 21hsl1:mov bx,di ;第二个数放在di中call outputdec ;输出第二个数lea dx,mess6 ;输出等号mov ah,09hint 21hcmp bp,3 ;判断是否需要输出负号 jnz sl2lea dx,mess4 ;输出负号mov ah,09hint 21hsl2:pop bx ;得到运算结果call outputdec;输出运算结果call crlfretshow endp(7)crlf函数(输出回车换行函数)crlf procpush axpush dxmov ah,02hmov dl,0dh ;输出回车int 21hmov dl,0ah ;输出换行int 21h ;ah值被改变 pop dxpop axretcrlf endp3.2 算法流程图3.2.2 十进制输入(inputdec)流程图3.2.3 十进制输出3.2.4 输出算术表达式(show)流程图4.4.1 源程序assume cs:code,ds:datadata segment ;定义数据段menu db ‘|--------------------------------------|’0dh,0ah db ‘| 1.Add |’0dh,0ah db ‘| 2.Sub |’0dh,0ah db ‘| 0.Exit |’0dh,0ahdb ‘|--------------------------------------|’0dh,0ahdb ‘Please input your choice:$’mess1 db 'Please input the first number: $'mess2 db 'Please input the second number: $'mess3 db 'The result is : $'mess4 db '-$'mess5 db '+$'mess6 db '=$'data ends ;数据段结束code segment ;定义代码段main proc ;主函数push dsxor ax,axpush axmov ax,datamov ds,axks:lea dx,menumov ah,09hint 21hmov al,0mov ah,01hint 21hsub al,30hcmp al,2jz l2cmp al,1jz l1mov ah,4chint 21hl1:call addfunjmp ksl2: call subtractjmp ksmain endp ;主函数结束addfun proc ;加法运算函数call crlfmov bp,1 ;给下面的show输出中间的运算符做标记 lea dx,mess1mov ah,09hint 21hcall inputdecmov si,bx ;第一个数保存在si中lea dx,mess2int 21hcall inputdecmov di,bx ;第二个数保存在di中mov bx,siadd bx,dilea dx,mess3mov ah,09hint 21hcall show ;输出结果retaddfun endp ;加法运算函数结束subtract proc ;减法运算函数call crlfmov bp,2 ;给下面的show输出中间的运算符做标记 lea dx,mess1mov ah,09hint 21hcall inputdecmov si,bx ;第一个数保存在si中lea dx,mess2mov ah,09hint 21hcall inputdecmov di,bx ;第二个数保存在di中mov bx,sicmp bx,dijs subl1 ;如果为负则跳转sub bx,dijmp subl2subl1:mov bp,3 ;为show里面是否输出负号作准备push disub di,bxmov bx,dipop disubl2:lea dx,mess3mov ah,09hint 21hcall showretsubtract endp ;减法运算函数结束inputdec proc ;十进制输入函数il0:mov ah,01hint 21hcmp al,0dh ;判断是否为回车jz iexitsub al,30hmov ah,0xchg bx,axmov cl,10mul cladd bx,axjmp il0iexit:call crlfretinputdec endp ;十进制输入函数结束outputdec proc ;十进制输出函数push bp ;用来做前导0的标记mov bp,0mov ax,bxmov dx,0 ;在进行除法之前,要对dx赋0,否则结果over devide mov cx,10000div cx ;字操作,商在ax中,余数在dx中mov bx,dx ;保存余数,作为下一次裤除数mov dl,alcmp dl,0jz ol0mov bp,1or dl,30hmov ah,02hint 21h ;输出万位ol0:mov ax,bxmov dx,0mov cx,1000div cx ;字操作,商在ax中,余数在dx中mov bx,dx ;保存余数,作为下一次裤除数mov dl,alcmp bp,0jz ol1or dl,30hmov ah,02hint 21h ;输出千位jmp ol2ol1:cmp dl,0jz ol2mov bp,1or dl,30hmov ah,02hint 21h ;输出千位ol2:mov ax,bxmov dx,0mov cx,100div cx ;字操作,商在ax中,余数在dx中 mov bx,dx ;保存余数,作为下一次裤除数mov dl,alcmp bp,0jz ol3or dl,30hmov ah,02hint 21h ;输出百位jmp ol4ol3:cmp dl,0jz ol4mov bp,1or dl,30hmov ah,02hint 21h ;输出百位ol4:mov ax,bxmov cl,10div cl ;字节操作,商在al中,余数在ah中 mov bl,ah ;保存余数,作为下一次裤除数mov dl,alcmp bp,0jz ol5or dl,30hmov ah,02hint 21h ;输出十位jmp ol6ol5:cmp dl,0jz ol6mov bp,1or dl,30hmov ah,02hint 21h ;输出十位ol6:mov dl,blor dl,30hmov ah,02hint 21hpop bp ;恢复bpretoutputdec endp ;十进制输出函数结show proc ;输出运算式函数push bx ;把运算结果保存起来 mov bx,si ;第一个数放在si中 call outputdeccmp bp,3 ;是否为减号jz sl0cmp bp,2jz sl0lea dx,mess5mov ah,09hint 21hjmp sl1sl0:lea dx,mess4mov ah,09hint 21hsl1:mov bx,di ;第二个数放在di中 call outputdeclea dx,mess6mov ah,09hint 21hcmp bp,3jnz sl2lea dx,mess4mov ah,09hint 21hsl2:pop bx ;得到运算结果call outputdeccall crlfretshow endp ;输出运算式函数结束crlf proc ;回车换行函数push axpush dxmov ah,02hmov dl,0dhint 21hmov dl,0ahint 21h ;ah值被改变pop dxpop axretcrlf endp ;回车换行函数结束code ends ;代码段结束end main ;程序结束4.2 执行结果4.2.1 测试方法本次测试我们采用的是通过菜单形式,输出选择项,然后根据提示信息,输入相关数字,进行举例测试。

十进制可逆加减计数器

时序电路逻辑设计实验人:周铮班级:中法1202班学号:U201215676一实验目的1.掌握用SSI实现简单组合逻辑电路的方法。

2.掌握简单数字电路的安装与测试技术。

3.熟悉使用Verilog HDL描述组合逻辑电路的方法,以及EDA仿真技术。

二实验器件计算机,可编程实验板三实验内容十进制加减可逆计数器设计功能要求:拨码开关键SW1为自动可逆加减功能键,当SW1为HIGH时,计数器实现自动可逆模十加减计数功能,即4个七段数码管上几乎同步显示0—1—2—3—4—...9—8—7—...0—1...的模十自动可逆加减计数结果;当SW1为LOW时,计数器按拨码开关键SW0的选择分别执行加减计数功能。

即当SW0为HIGH时,计数器实现模十加计数功能,即4个七段数码管上几乎同步显示0—1—2—3—4—...9——0—1...的模十加计数结果;当SW0为LOW时,计数器实现模十减计数功能,即4个七段数码管上几乎同步显示9—8—7—...—1—0— (9)—8—7…的模十减计数结果。

四实验设计1.原理设计脉冲发生电路采用555定时器组成的多谐振荡器振荡产生周期为1s的矩形脉冲,从而为计数器提供触发信号。

其中,可以通过R1,R2,C来控制充放电的时间。

加/减计数控制电路主要由74LS138构成。

74LS138芯片是常用的3-8线译码器,常用在单片机和数字电路的译码电路中,74LS138的引脚排列及真值表如图计数单元电路主要由十进制计数器74LS192构成。

74LS192是同步十进制可逆计数器,它具有双时钟输入,并具有清除和置数等功能,其引脚排列图如图功能表如图2.模拟仿真用Verilog HDL语言设计二通道数据选择器实验程序如下:①实验代码module a(input clk,input SW1,input SW0,input clear,input reset,output reg[3:0] s1_reg,output reg[6:0] segdat_reg);reg[26:0] counter;reg[3:0]q;reg x;always@(posedge clk)beginif(clear) begins1_reg<=0;counter<=0;endelsecounter<=counter+1;endalways@(posedge counter[26])beginif (reset) beginq<=0;x<=0;endelsebegincase(SW1)1'd1:begincase(x)1'd0: beginif(q==4'd8)x<=1;q<=q+1;end1'd1: beginif(q==4'd1)x<=0;q<=q-1;endendcaseend1'd0:begincase(SW0)1'd0:beginif(q==4'd0)q<=4'd9;elseq<=q-1;end1'd1:beginif(q==4'd9)q<=4'd0;elseq<=q+1;endendcaseendendcaseendendalways@(q) // 数码管显示处理begincase(q)4'h0:segdat_reg = 7'b0000001; //04'h1:segdat_reg = 7'b1001111; //14'h2:segdat_reg = 7'b0010010; //24'h3:segdat_reg = 7'b0000110; //34'h4:segdat_reg = 7'b1001100; //44'h5:segdat_reg = 7'b0100100; //54'h6:segdat_reg = 7'b0100000; //64'h7:segdat_reg = 7'b0001111; //74'h8:segdat_reg = 7'b0000000; //84'h9:segdat_reg = 7'b0000100; //9default:segdat_reg=7'b0111000; //Fendcaseendendmodule②测试文件test代码module test;// Inputsreg clk;reg SW1;reg SW0;reg clear;reg reset;// Outputswire [3:0] s1_reg;wire [6:0] segdat_reg;// Instantiate the Unit Under Test (UUT)a uut (.clk(clk),.SW1(SW1),.SW0(SW0),.clear(clear),.reset(reset),.s1_reg(s1_reg),.segdat_reg(segdat_reg));initial begin// Initialize Inputsclk = 0;SW1 = 0;SW0 = 1;clear = 1;reset = 1;// Wait 100 ns for global reset to finish#100;// Add stimulus hereendendmodule③管脚设置ucf文件代码# PlanAhead Generated physical constraintsNET "SW0" LOC = P11;NET "SW1" LOC = L3;NET "clear" LOC = K3;NET "clk" LOC = B8;NET "reset" LOC = B4;NET "segdat_reg[0]" LOC = M12;NET "segdat_reg[1]" LOC = L13;NET "segdat_reg[2]" LOC = P12;NET "segdat_reg[3]" LOC = N11;NET "segdat_reg[4]" LOC = N14;NET "segdat_reg[5]" LOC = H12;NET "segdat_reg[6]" LOC = L14;NET "s1_reg[0]" LOC = F12;NET "s1_reg[1]" LOC = J12;NET "s1_reg[2]" LOC = M13;NET "s1_reg[3]" LOC = K14;# PlanAhead Generated IO constraintsNET "clk" SLEW = FAST;④模拟仿真顶层原理图⑤模拟仿真波形图五实验心得本次实验要求用Verilog HDL语言做出十进制可逆加减计数器并进行模拟仿真,其中在代码部分出现多次bug,后经过仔细检查发现是测试文件未加限制的原因,最终做出了模拟仿真。

CD40110中文资料

CD40110------十进制加减计数器/锁存/七段

简要说明:

40110为十进制可逆计数器/锁存器/译码器/驱动器,具有加减计数,计数器状

态锁存,七段显示译码输出等功能。

40110有2个计数时钟输入端CPU和CPD分别用作加计数时钟输入和减计数时

钟输入。

由于电路内部有一个时钟信号预处理逻辑,因此当一个时钟输入端计数工作时,另一个时钟输入端可以是任意状态。

40110的进位输出CO和借位输出BO一般为高电平,当计数器从0~9时,

BO输出负脉冲;从9~0时CO输出负脉冲。

在多片级联时,只需要将CO和BO 分别接至下级40110的CPU和CPD端,就可组成多位计数器。

引出端符号:

BO 借位输出端推荐工作条件:

CO 进位输出端电源电压范围…………3V~18V CPD 减计数器时钟输入端输入电压范围…………0V~VDD CPU 加计数器时钟输入端工作温度范围

CR 清除端M类…………-55℃~125℃

/CT 计数允许端E类………….-40℃~85℃

/LE 锁存器预置端极限值:

VDD 正电源电源电压…...-0.5V~18V

Vss 地输入电压……-0.5V~VDD+0.5V Ya~6g 锁存译码输出端输入电流…………….±10mA

储存稳定…………-65℃~150℃引出端排列:逻辑图:。

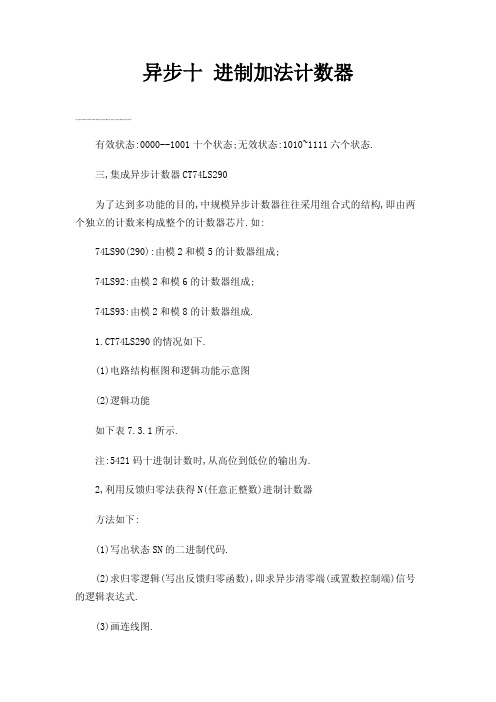

异步十进制加法计数器

异步十进制加法计数器000有效状态:0000--1001十个状态;无效状态:1010~1111六个状态.三,集成异步计数器CT74LS290为了达到多功能的目的,中规模异步计数器往往采用组合式的结构,即由两个独立的计数来构成整个的计数器芯片.如:74LS90(290):由模2和模5的计数器组成;74LS92:由模2和模6的计数器组成;74LS93:由模2和模8的计数器组成.1.CT74LS290的情况如下.(1)电路结构框图和逻辑功能示意图(2)逻辑功能如下表7.3.1所示.注:5421码十进制计数时,从高位到低位的输出为.2,利用反馈归零法获得N(任意正整数)进制计数器方法如下:(1)写出状态SN的二进制代码.(2)求归零逻辑(写出反馈归零函数),即求异步清零端(或置数控制端)信号的逻辑表达式.(3)画连线图.举例:试用CT74LS290构成模小于十的N进制计数器.CT74LS290则具有异步清零和异步置9功能.讲解教材P215的[例7.3.1].注:CT74LS90的功能与CT74LS290基本相同.7.3.2同步计数器一,同步二进制计数器1.同步二进制加法计数器2,同步二进制减法计数器3,集成同步二进制计数器CT74LS161(1)CT74LS161的引脚排列和逻辑功能示意图注:74LS163的引脚排列和74LS161相同,不同之处是74LS163采用同步清零方式.(2)CT74LS161的逻辑功能①=0时异步清零.C0=0②=1,=0时同步并行置数.③==1且CPT=CPP=1时,按照4位自然二进制码进行同步二进制计数.④==1且CPT·CPP=0时,计数器状态保持不变.4,反馈置数法获得N进制计数器方法如下:·写出状态SN-1的二进制代码.·求归零逻辑,即求置数控制端的逻辑表达式.·画连线图.(集成计数器中,清零,置数均采用同步方式的有74LS163;均采用异步方式的有74LS193,74LS197,74LS192;清零采用异步方式,置数采用同步方式的有74LS161,74LS160;有的只具有异步清零功能,如CC4520,74LS190,74LS191;74LS90则具有异步清零和异步置9功能.等等) 试用CT74LS161构成模小于16的N进制计数器5,同步二进制加/减计数器二,同步十进制加法计数器8421BCD码同步十进制加法计数器电路分析三,集成同计数器1,集成十进制同步加法计数器CT74LS160(1)CT74LS160的引脚排列和逻辑功能示意图图7.3.3CT74LS160的引脚排列图和逻辑功能示意图(2)CT74LS160的逻辑功能①=0时异步清零.C0=0②=1,=0时同步并行置数.③==1且CPT=CPP=1时,按照BCD码进行同步十进制计数.④==1且CPT·CPP=0时,计数器状态保持不变.2.集成十进制同步加/减计数器CT74LS190其逻辑功能示意图如教材图7.3.15所示.功能如教材表7.3.10所示.集成计数器小结:集成十进制同步加法计数器74160,74162的引脚排列图,逻辑功能示意图与74161,74163相同,不同的是,74160和74162是十进制同步加法计数器,而74161和74163是4位二进制(16进制)同步加法计数器.此外,74160和74162的区别是,74160采用的是异步清零方式,而74162采用的是同步清零方式.74190是单时钟集成十进制同步可逆计数器,其引脚排列图和逻辑功能示意图与74191相同.74192是双时钟集成十进制同步可逆计数器,其引脚排列图和逻辑功能示意图与74193相同.7.3.3利用计数器的级联获得大容量N进制计数器计数器的级联是将多个计数器串接起来,以获得计数容量更大的N进制计数器.1,异步计数器一般没有专门的进位信号输出端,通常可以用本级的高位输出信号驱动下一级计数器计数,即采用串行进位方式来扩展容量.举例:74LS290(1)100进制计数器(2)64进制计数器2,同步计数器有进位或借位输出端,可以选择合适的进位或借位输出信号来驱动下一级计数器计数.同步计数器级联的方式有两种,一种级间采用串行进位方式,即异步方式,这种方式是将低位计数器的进位输出直接作为高位计数器的时钟脉冲,异步方式的速度较慢.另一种级间采用并行进位方式,即同步方式,这种方式一般是把各计数器的CP端连在一起接统一的时钟脉冲,而低位计数器的进位输出送高位计数器的计数控制端.举例:74161(1)60进制(2)12位二进制计数器(慢速计数方式)12位二进制计数器(快速计数方式)7.4寄存器和移位寄存器寄存器是由具有存储功能的触发器组合起来构成的.一个触发器可以存储1位二进制代码,存放n位二进制代码的寄存器,需用n个触发器来构成.按照功能的不同,可将寄存器分为基本寄存器和移位寄存器两大类.基本寄存器只能并行送入数据,需要时也只能并行输出.移位寄存器中的数据可以在移位脉冲作用下依次逐位右移或左移,数据既可以并行输入,并行输出,也可以串行输入,串行输出,还可以并行输入,串行输出,串行输入,并行输出,十分灵活,用途也很广.7.4.1基本寄存器概念:在数字电路中,用来存放二进制数据或代码的电路称为寄存器.1,单拍工作方式基本寄存器无论寄存器中原来的内容是什么,只要送数控制时钟脉冲CP上升沿到来,加在并行数据输入端的数据D0~D3,就立即被送入进寄存器中,即有:2.双拍工作方式基本寄存器(1)清零.CR=0,异步清零.即有:(2)送数.CR=1时,CP上升沿送数.即有:(3)保持.在CR=1,CP上升沿以外时间,寄存器内容将保持不变.7.4.2移位寄存器1.单向移位寄存器四位右移寄存器:时钟方程:驱动方程:状态方程:右移位寄存器的状态表: 输入现态次态说明DiCP1↑1↑1↑1↑00001000110011101000110011101111连续输入4个1单向移位寄存器具有以下主要特点:单向移位寄存器中的数码,在CP脉冲操作下,可以依次右移或左移.n位单向移位寄存器可以寄存n位二进制代码.n个CP脉冲即可完成串行输入工作,此后可从Q0~Qn-1端获得并行的n位二进制数码,再用n个CP脉冲又可实现串行输出操作.若串行输入端状态为0,则n个CP脉冲后,寄存器便被清零.2.双向移位寄存器M=0时右移M=1时左移3.集成双向移位寄存器74LS194CT74LS194的引脚排列图和逻辑功能示意图:CT74LS194的功能表:工作状态0×××100×101↑110↑111×异步清零保持右移左移并行输入7.4.3移位寄存器的应用一,环形计数器1,环形计数器是将单向移位寄存器的串行输入端和串行输出端相连,构成一个闭合的环.结构特点:,即将FFn-1的输出Qn-1接到FF0的输入端D0.工作原理:根据起始状态设置的不同,在输入计数脉冲CP的作用下,环形计数器的有效状态可以循环移位一个1,也可以循环移位一个0.即当连续输入CP 脉冲时,环形计数器中各个触发器的Q端或端,将轮流地出现矩形脉冲.实现环形计数器时,必须设置适当的初态,且输出Q3Q2Q1Q0端初始状态不能完全一致(即不能全为"1"或"0"),这样电路才能实现计数,环形计数器的进制数N与移位寄存器内的触发器个数n相等,即N=n2,能自启动的4位环形计数器状态图:由74LS194构成的能自启动的4位环形计数器时序图二,扭环形计数器1,扭环形计数器是将单向移位寄存器的串行输入端和串行反相输出端相连,构成一个闭合的环.实现扭环形计数器时,不必设置初态.扭环形计数器的进制数N与移位寄存器内的触发器个数n满足N=2n的关系结构特点为:,即将FFn-1的输出接到FF0的输入端D0.状态图:2,能自启动的4位扭环形计数器7.4.4顺序脉冲发生器在数字电路中,能按一定时间,一定顺序轮流输出脉冲波形的电路称为顺序脉冲发生器.顺序脉冲发生器也称脉冲分配器或节拍脉冲发生器,一般由计数器(包括移位寄存器型计数器)和译码器组成.作为时间基准的计数脉冲由计数器的输入端送入,译码器即将计数器状态译成输出端上的顺序脉冲,使输出端上的状态按一定时间,一定顺序轮流为1,或者轮流为0.前面介绍过的环形计数器的输出就是顺序脉冲,故可不加译码电路即可直接作为顺序脉冲发生器.一,计数器型顺序脉冲发生器计数器型顺序脉冲发生器一般用按自然态序计数的二进制计数器和译码器构成.举例:用集成计数器74LS163和集成3线-8线译码器74LS138构成的8输出顺序脉冲发生器.二,移位型顺序脉冲发生器◎移位型顺序脉冲发生器由移位寄存器型计数器加译码电路构成.其中环形计数器的输出就是顺序脉冲,故可不加译码电路就可直接作为顺序脉冲发生器.◎时序图:◎由CT74LS194构成的顺序脉冲发生器见教材P233的图7.4.6和图7.4.77.5同步时序电路的设计(略)7.6数字系统一般故障的检查和排除(略)本章小结计数器是一种应用十分广泛的时序电路,除用于计数,分频外,还广泛用于数字测量,运算和控制,从小型数字仪表,到大型数字电子计算机,几乎无所不在,是任何现代数字系统中不可缺少的组成部分.计数器可利用触发器和门电路构成.但在实际工作中,主要是利用集成计数器来构成.在用集成计数器构成N进制计数器时,需要利用清零端或置数控制端,让电路跳过某些状态来获得N进制计数器.寄存器是用来存放二进制数据或代码的电路,是一种基本时序电路.任何现代数字系统都必须把需要处理的数据和代码先寄存起来,以便随时取用.寄存器分为基本寄存器和移位寄存器两大类.基本寄存器的数据只能并行输入,并行输出.移位寄存器中的数据可以在移位脉冲作用下依次逐位右移或左移,数据可以并行输入,并行输出,串行输入,串行输出,并行输入,串行输出,串行输入,并行输出.寄存器的应用很广,特别是移位寄存器,不仅可将串行数码转换成并行数码,或将并行数码转换成串行数码,还可以很方便地构成移位寄存器型计数器和顺序脉冲发生器等电路.在数控装置和数字计算机中,往往需要机器按照人们事先规定的顺序进行运算或操作,这就要求机器的控制部分不仅能正确地发出各种控制信号,而且要求这些控制信号在时间上有一定的先后顺序.通常采取的方法是,用一个顺序脉冲发生器来产生时间上有先后顺序的脉冲,以控制系统各部分协调地工作.顺序脉冲发生器分计数型和移位型两类.计数型顺序脉冲发生器状态利用率高,但由于每次CP信号到来时,可能有两个或两个以上的触发器翻转,因此会产生竞争冒险,需要采取措施消除.移位型顺序脉冲发生器没有竞争冒险问题,但状态利用率低.参考资料:第七章%20时序逻辑电路.doc。

模块七 十进制可逆计数器

模快七十进制可逆计数器的设计课时安排:理论2课时,实训14课时(电路设计仿真2课时,电路装配调试12课时)8.1 教学目的要求8.1.1 掌握十进制可逆计数器设计方案和方案论证的方法;8.1.2 掌握十进制可逆计数器的设计方法;8.1.3 熟悉编码器、译码器、数码管的使用;8.1.4 学会电路的安装、焊接和调试方法。

8.2教学重点十进制可逆计数器的方案设计及方案论证。

8.3 教学难点十进制可逆计数器的设计及参数计算。

8.4教学内容8.4.1十进制可逆计数器的方案设计及方案论证。

;8.4.2十进制可逆计数器的设计及参数计算;8.4.3编码器、译码器、数码管的使用;8.4.4 十进制可逆计数器的组装及功能调试。

新课引入:模块题目:十进制可逆计数器的设计设计要求:1、可实现十进制计数的功能。

2、可逆计数器:计数规律可按加法计数规律计数,也可按减法计数规律计数,由控制端决定。

设计思路计数器是用来累计时钟脉冲(CP脉冲)个数的时序逻辑部件。

它是数字系统中用途最广泛的基本部件之一,几乎在各种数字系统中都有计数器。

它不仅可以计数,还可以对CP脉冲分频,以及构成时间分配器或时序发生器,对数字系统进行定时、程序控制操作。

此外,还能用它执行数字运算。

1、计数器的特点:在数字电路中,把记忆输入CP脉冲个数的操作叫做计数,能实现计数状态的电子电路称为计数器。

特点为(1)该电路一般为Moore型电路,输入端只有CP信号。

(2)从电路组成看,其主要组成单元是时钟触发器。

2、计数器分类1)按CP脉冲输入方式分类按CP脉冲输入方式,计数器分为同步计数器和异步计数器两种。

同步计数器:计数脉冲引到所有触发器的时钟脉冲输入端,使应翻转的触发器在外接的CP脉冲作用下同时翻转。

异步计数器:计数脉冲并不引到所有触发器的时钟脉冲输入端,有的触发器的时钟脉冲输入端是其它触发器的输出,因此,触发器不是同时动作。

2)按计数增减趋势分类按计数增减趋势,计数器分为加法计数器、减法计数器和可逆计数器三种。

十进制计数器码十进制加法计数器的状态表

举例

将二进制数1010转换为十进制数,可以表示为1×2^3 + 0×2^2 + 1×2^1 + 0×2^0 = 8 + 0 + 2 + 0 = 10。

十进制计数器的原理

法运算。

它具有十个不同的状态,可 以表示从0到9的十个不同的

十进制数。

在每个时钟周期内,计数器的 状态会根据输入的二进制数进 行更新,从而实现二进制数的

加法运算。

02

十进制计数器码

二进制到十进制的转换

总结词

二进制到十进制的转换是将二进制数转换为十进制数的过程,可以通过逐位乘以权值并求 和得到。

详细描述

故障排除效率。

05

总结

计数器的发展历程

手动计数器

早期计数器采用机械或手动方式,主 要用于简单的计数和计测。

电子ห้องสมุดไป่ตู้数器

随着电子技术的发展,电子计数器开 始出现,具有更高的精度和可靠性。

集成电路计数器

随着集成电路的普及,计数器被集成 到芯片中,实现了更小体积、更低功 耗和更高性能。

智能计数器

现代智能计数器结合了传感器、微处 理器和通信技术,具有自动识别、数 据处理和远程控制等功能。

计数速度 十进制加法计数器的计数速度较 快,适用于需要高速计数的应用 场景,而十进制计数器码的计数 速度较慢。

未来计数器的发展趋势

集成化

智能化

未来计数器将进一步向集成化发展,实现 更小体积、更低功耗和更高性能。

结合传感器、微处理器和通信技术,实现 自动识别、数据处理和远程控制等功能。

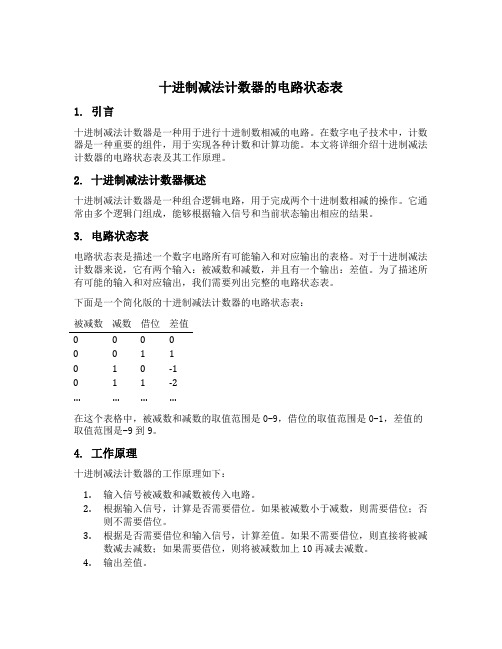

十进制减法计数器的电路状态表

十进制减法计数器的电路状态表1. 引言十进制减法计数器是一种用于进行十进制数相减的电路。

在数字电子技术中,计数器是一种重要的组件,用于实现各种计数和计算功能。

本文将详细介绍十进制减法计数器的电路状态表及其工作原理。

2. 十进制减法计数器概述十进制减法计数器是一种组合逻辑电路,用于完成两个十进制数相减的操作。

它通常由多个逻辑门组成,能够根据输入信号和当前状态输出相应的结果。

3. 电路状态表电路状态表是描述一个数字电路所有可能输入和对应输出的表格。

对于十进制减法计数器来说,它有两个输入:被减数和减数,并且有一个输出:差值。

为了描述所有可能的输入和对应输出,我们需要列出完整的电路状态表。

下面是一个简化版的十进制减法计数器的电路状态表:被减数减数借位差值0 0 0 00 0 1 10 1 0 -10 1 1 -2…………在这个表格中,被减数和减数的取值范围是0-9,借位的取值范围是0-1,差值的取值范围是-9到9。

4. 工作原理十进制减法计数器的工作原理如下:1.输入信号被减数和减数被传入电路。

2.根据输入信号,计算是否需要借位。

如果被减数小于减数,则需要借位;否则不需要借位。

3.根据是否需要借位和输入信号,计算差值。

如果不需要借位,则直接将被减数减去减数;如果需要借位,则将被减数加上10再减去减数。

4.输出差值。

5. 示例为了更好地理解十进制减法计数器的工作原理,我们来看一个简单的示例。

假设我们要计算8-3的差值。

根据电路状态表,我们可以得到以下信息:被减数减数借位差值8 3 0 5根据输入信号8和3,计算得到不需要借位,并且差值为5。

因此,8-3的结果是5。

6. 总结十进制减法计数器是一种用于进行十进制数相减的电路。

它通过多个逻辑门实现了输入信号的处理和输出结果的产生。

本文介绍了十进制减法计数器的电路状态表及其工作原理,并通过示例说明了其应用。

希望本文能够帮助读者更好地理解十进制减法计数器的原理和功能,以及在数字电子技术中的应用。

十进制数加减计算器的设计

十进制数加减计算器的设计在计算机科学中,十进制数加减计算器是一种用于执行加法和减法运算的算术设备或程序。

普通的十进制计算器是我们日常生活中经常使用的工具,它们用于执行各种计算任务,例如做家庭预算、计算商品价格、统计和分析数据等。

一个十进制数加减计算器的设计需要考虑以下几个方面:界面设计、输入和输出处理、运算逻辑和错误处理。

下面将分别对这些方面进行详细阐述。

其次,输入和输出处理是一个重要的设计考虑因素。

计算器应该能够接受用户输入的数字,并将计算结果以可读性良好的方式输出给用户。

输入可以通过按键、虚拟键盘、语音识别等方式完成。

输出可以以图形界面、文本显示或语音输出的形式实现。

对于输入错误或超出了计算能力范围的操作,计算器应给出明确的错误提示,以帮助用户进行修正。

接下来是运算逻辑的设计。

十进制数的加减运算是基本的算术运算,它要求对两个数字进行对齐,并按位相加(减)。

设计一个高效的运算逻辑需要考虑以下几个方面:处理进位(或退位)、对齐和补位、处理小数部分、实现数字运算的正确性和一致性等。

计算器应能够正确地处理各种情况,例如负数加减、小数加减、连续多位数加减等。

最后是错误处理的设计。

计算器应该能够检测和处理用户输入中的各种错误,例如无效数字、超出范围、除以零等。

错误处理可以通过在界面上显示错误消息、发出声音提示或弹出对话框来完成。

此外,为确保计算器的稳定性和安全性,还需要进行输入验证和运行时错误处理,以防止恶意输入和运行时错误导致计算器崩溃或伤害用户的设备。

总结起来,设计一个十进制数加减计算器需要综合考虑界面设计、输入和输出处理、运算逻辑和错误处理等方面。

一个好的十进制数加减计算器应该具有易于使用和直观的界面,能够接受各种形式的用户输入,并能够对输入进行验证和处理。

它应能够正确地执行加法和减法运算,同时能够检测和处理各种错误情况。

通过合理的设计和实现,一个易用、高效和可靠的十进制数加减计算器将成为用户的得力助手,为用户提供准确和方便的计算服务。

十进制计数器

十进制计数器十进制计数器是在计数脉冲作用下各触发器状态的转换按十进制数的编码规律进行计数的数字电路。

十进制计数器由哪些部分组成?它是如何工作的?8421BCD编码表十进制数有0~9共10个数码,至少要用4位二进制数。

十进制计数器分类同步十进制加法计数器同步十进制减法计数器异步十进制加法计数器异步十进制减法计数器一 、异步十进制加法计数器电路组成由4位二进制计数器和一个用于计数器清0的与非门组成。

与二进制加法计数器的主要差异是跳过了二进制数码1010~1111这6个状态。

二 、异步十进制加法计数器工作过程计数器输入0~9个计数脉冲时,工作过程与4位二进制异步计数器完全相同,第9个计数脉冲后Q 3Q 2Q 1Q 0=1001。

当第10个计数脉冲到来后,计数器状态为Q 3Q 2Q 1Q 0=1010:101000000 Q 3=Q 1=l ,与非门输入全1,输出为0,使各触发器复位,即Q 3Q 2Q 1Q 0=0000。

同时,使与非门输出又变为1,计数器重新开始工作。

11000011111异步十进制加法计数器能实现按8421BCD码的十进制计数,但在工作过程中有一个复位过渡状态,即计数器要在1010状态下使各触发器同步复位。

虽然复位过渡状态只是短暂的一瞬间,但若各触发器的翻转速度不一致,便会产生误动作。

十进制计数器一、电路组成二、工作过程异步十进制加法计数器由4位二进制计数器和一个用于计数器清0的与非门组成。

跳过了二进制数码1010~1111这6个状态。

计数器输入0~9个计数脉冲时,工作过程与4位二进制异步计数器完全相同,第9个计数脉冲后Q 3Q 2Q 1Q 0=1001。

当第10个计数脉冲到来后,各触发器复位,计数器重新开始工作。

谢谢!。

CMOS异步十进制可逆计数器的优化设计

题目:基于李码的模9递减计数器CMOS 异步十进制可逆计数器的设计与优化摘要详细论述了一个CMOS 异步十进制可逆计数器的原理和设计过程,以及仿真结果。

本电路的逻辑部分通过软件MAXPLUS2设计仿真验证正确后,再通过集成电路设计软件CANDENCE 在给定的0.5μm CMOS工艺下,设计出一个高速计数器,具有加法和减法计数的功能,并且可以一键切换,该电路同时具有一键清零的功能。

该设计更加简化可逆十进制的逻辑,可以省去更多电路,对于设计更为复杂的集成电路可以直接使用,提供了方便。

通过实验得出了NMOS 和PMOS 的最优化宽长比,当MOS 管为最优宽长比时,通过波形分析,得出上升时间为3.5 ns,下降时间为2.5 ns,从而提高了该计数器的计数频率,该计数器的最高频率为166 MHz, 并通过优化设计,提高了电路工作的稳定性。

附录是异步十进制可逆计数器的SPICE 语言的程序。

关键词:异步十进制可逆计数器仿真集成电路高速计数器版图Design and Optimization of CMOS AsynchronousMetricReversible CounterABSTRACTThe paper describes the principle, design process and simulation results on a CMOS asynchronous decimal reversible counter. In detail, the logical part of circuit is designed and simulated by the software of MAX PLUS2, On the given 0.5μm micron CMOS process ,design a high-speed counter , which with the function of addition and subtraction ,by using the integrated circuit design software CANDENCE. The layout make the logical of asynchronous metricationreversible counter more simple, so that the work has more advantages. Experimental results show that the NMOS and PMOSoptimize the width-length ratio, waveform analysis, come up time 3.5 ns and fall time 2.5 ns, thus increasing the frequency of the counting. The counter frequency of 166MHz,improve the stabilization of circuit by optimizing the design. The supplement is the SPICE procedure of the Asynchronous MetricReversible Counter.Keywords:asynchronous metricationreversible countersimulation IC high speedcounter territory目录一引论 (1)1.1课题的来源及意义 (1)1.2 计数器简介 (1)1.3 CMOS集成电路的性能及特点 ····················· 4 二异步十进制可逆计数器原理与设计 ·····错误!未定义书签。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

时序电路逻辑设计

实验人:周铮班级:中法1202班学号:U201215676

一实验目的

1.掌握用SSI实现简单组合逻辑电路的方法。

2.掌握简单数字电路的安装与测试技术。

3.熟悉使用Verilog HDL描述组合逻辑电路的方法,以及EDA仿真技术。

二实验器件

计算机,可编程实验板

三实验内容

十进制加减可逆计数器设计

功能要求:

拨码开关键SW1为自动可逆加减功能键,当SW1为HIGH时,计数器实现自动可逆模十加减计数功能,即4个七段数码管上几乎同步显示0—1—2—3—4—...9—8—7—...0—1...的模十自动可逆加减计数结果;当SW1为LOW时,计数器按拨码开关键SW0的选择分别执行加减计数功能。

即当SW0为HIGH时,计数器实现模十加计数功能,即4个七段数码管上几乎同步显示0—1—2—3—4—...9——0—1...的模十加计数结果;当SW0为LOW时,计数器实现模十减计数功能,即4个七段数码管上几乎同步显示9—8—7—...—1—0— (9)

—8—7…的模十减计数结果。

四实验设计

1.原理设计

脉冲发生电路采用555定时器组成的多谐振荡器振荡产生周期为1s的矩形脉冲,从而为计数器提供触发信号。

其中,可以通过R1,R2,C来控制充放电的时间。

加/减计数控制电路主要由74LS138构成。

74LS138芯片是常用的3-8线译码器,常用在单片机和数字电路的译码电路中,74LS138的引脚排列及

真值表如图

计数单元电路主要由十进制计数器74LS192构成。

74LS192是同步十进制可逆计数器,它具有双时钟输入,并具有清除和置数等功能,其引脚排列图如图

功能表如图

2.模拟仿真

用Verilog HDL语言设计二通道数据选择器实验程序如下:

①实验代码

module a(

input clk,

input SW1,

input SW0,

input clear,

input reset,

output reg[3:0] s1_reg,

output reg[6:0] segdat_reg

);

reg[26:0] counter;

reg[3:0]q;

reg x;

always@(posedge clk)

begin

if(clear) begin

s1_reg<=0;

counter<=0;

end

else

counter<=counter+1;

end

always@(posedge counter[26])

begin

if (reset) begin

q<=0;

x<=0;

end

else

begin

case(SW1)

1'd1:begin

case(x)

1'd0: begin

if(q==4'd8)

x<=1;

q<=q+1;

end

1'd1: begin

if(q==4'd1)

x<=0;

q<=q-1;

end

endcase

end

1'd0:begin

case(SW0)

1'd0:begin

if(q==4'd0)

q<=4'd9;

else

q<=q-1;

end

1'd1:begin

if(q==4'd9)

q<=4'd0;

else

q<=q+1;

end

endcase

end

endcase

end

end

always@(q) // 数码管显示处理

begin

case(q)

4'h0:segdat_reg = 7'b0000001; //0

4'h1:segdat_reg = 7'b1001111; //1

4'h2:segdat_reg = 7'b0010010; //2

4'h3:segdat_reg = 7'b0000110; //3

4'h4:segdat_reg = 7'b1001100; //4

4'h5:segdat_reg = 7'b0100100; //5

4'h6:segdat_reg = 7'b0100000; //6

4'h7:segdat_reg = 7'b0001111; //7

4'h8:segdat_reg = 7'b0000000; //8

4'h9:segdat_reg = 7'b0000100; //9

default:segdat_reg=7'b0111000; //F

endcase

end

endmodule

②测试文件test代码

module test;

// Inputs

reg clk;

reg SW1;

reg SW0;

reg clear;

reg reset;

// Outputs

wire [3:0] s1_reg;

wire [6:0] segdat_reg;

// Instantiate the Unit Under Test (UUT)

a uut (

.clk(clk),

.SW1(SW1),

.SW0(SW0),

.clear(clear),

.reset(reset),

.s1_reg(s1_reg),

.segdat_reg(segdat_reg)

);

initial begin

// Initialize Inputs

clk = 0;

SW1 = 0;

SW0 = 1;

clear = 1;

reset = 1;

// Wait 100 ns for global reset to finish

#100;

// Add stimulus here

end

endmodule

③管脚设置ucf文件代码

# PlanAhead Generated physical constraints

NET "SW0" LOC = P11;

NET "SW1" LOC = L3;

NET "clear" LOC = K3;

NET "clk" LOC = B8;

NET "reset" LOC = B4;

NET "segdat_reg[0]" LOC = M12;

NET "segdat_reg[1]" LOC = L13;

NET "segdat_reg[2]" LOC = P12;

NET "segdat_reg[3]" LOC = N11;

NET "segdat_reg[4]" LOC = N14;

NET "segdat_reg[5]" LOC = H12;

NET "segdat_reg[6]" LOC = L14;

NET "s1_reg[0]" LOC = F12;

NET "s1_reg[1]" LOC = J12;

NET "s1_reg[2]" LOC = M13;

NET "s1_reg[3]" LOC = K14;

# PlanAhead Generated IO constraints

NET "clk" SLEW = FAST;

④模拟仿真顶层原理图

⑤模拟仿真波形图

五实验心得

本次实验要求用Verilog HDL语言做出十进制可逆加减计数器并进行模拟仿真,其中在代码部分出现多次bug,后经过仔细检查发现是测试文件未加限制的原因,最终做出了模拟仿真。