版图绘制时如何进行LVS验证

LVS验证的实验指导

第五章物理验证(一)教学内容1.物理验证的概念;2.主流物理验证工具介绍;Calibre 是Mentor Graphics 的IC版图验证软件,此软件包括设计规则检查(DRC )、版图与原理图一致性检查(LVS)、电气规则检查(ERC)、及版图寄生参数萃取(LPE)等验证功能。

其操作界面主要分为图形模式(GUI)(graphical user interface) Calibre Interactive与指令模式(Command Line),其中图形模式可以单独启动,亦可与Virtuoso 等软件相连接,其操作界面皆相同。

本章我们主要研究图形模式。

3.主要术语⏹SVRF---Standard Verification Rule Format(标准的检查文件)⏹RVE---Results Viewing Environment(显示结果用的环境窗口)⏹SVDB---Standard Verification Database (LVS results)⏹DRC---Design Rule Check(设计规则检查)⏹ERC---Electrical Rule Checking(电气规则检查)⏹LVS---Layout Versus Schematic(版图原理图一致性检查)⏹LPE---Layout Parasitic Extraction(版图寄生参数萃取)第二节LVS版图与原理图的一致性4.Calibre LVS 简介Calibre LVS 是一个出色的版图与线路图对比检查工具,具有高效率、高准确度和大容量等优点。

Calibre LVS 不仅可以对所有的“元件”进行验证,而且还能在不影响性能的条件下,处理无效数据。

主要表现在以下几个方面:(1) 运行模式快捷方便:Calibre LVS 有两种运行模式,即命令行模式和界面模式(Calibre Interactive-LVS)。

采用命令行模式可以快速输入控制命令,快速运行,其结果精确稳定。

lvs

1、LVS规则检查。

以aoi21逻辑门为例,做它的逻辑图与版图的LVS规则检查。

一、建立LVS规则,它是应该根据特定的工艺来编写的。

这里LVS 文件保存在/home1/design/lvs下面。

二、a、逻辑图的建立。

建立逻辑cell,选择Composer-Schematic 工具,进入绘制窗口后,按I键调用元件库,这里可以供选择的有2个库,basic 和sample,之后进行逻辑图绘制。

b、版图绘制。

建立版图cell,选择Virtuoso工具进入绘制窗口进行相应的绘制。

三、建立netlist和.gds文件。

其中netlist对应于逻辑图,而.gds 文件对应于版图。

a、netlist生成:选择File—Export—CDL…进入Virtuoso CDL out 窗口。

接着选择Library Browser来选择aoi21逻辑图所在的位置并选择。

此时,Top Cell Name 为aoi21;View Name 为schematic;Library Name为 yjh(逻辑图所在的文件夹);Output File为netlist;最后要在Run Directory里填写上输出文件的路径,这里为/home1/design/lvs,这样在lvs中就会生成一个netlist文件。

b、.gds文件的生成:选择File—Export—Steream...进入的窗口为Virtuoso Stream Out,同样在Library Browser中调取版图文件,这时在Qutput File中文件为aoi.gds,在Run Directory里填写保存路径/home1/design/lvs;接着选择User—Defined Data连接,在Layer Map Table中写入exe.map,设置好后,就会在lvs中出现一个新文件aoi21.gds。

四、LVS.ruls文件的编写。

这个文件在/home1/design/lvs之下,使用Vi LVS.ruls可以打开这个文件。

版图的物理验证

版图的物理验证版图的物理验证主要有DRC,ERC(电气规则检查)和LVS三种方法。

DRC 表示设计规则检查,是Design Rule Checking的缩写,LVS是Layout Versus Schematic的缩写,ERC是Electrical Rule Checking。

DRC用来检查版图的几何图形符合工艺规则要求,以便芯片能在工艺线上生产出来;LVS把设计得到的版图和逻辑网表进行比较,检查各器件大小和连接关系是否完全一致;ERC主要是检查版图电性能(如衬底是否正确接电源或地,又无栅极悬空等)以保证各器件能正常工作。

物理验证成功则可以出带(Tapeout),或生成macro cell 做作为整个设计的一部份来使用,数据格式一般采用GDSII。

下面以Mentor公司的物理验证Calibre来说明版图的验证过程。

1.ANT流程2.DRC流程DRC验证需要输入版图文件(GDSII格式)和规则文件,规则文件一般由厂商提供。

Mentor 公司的Calibre软件是DRC方面的主流工具。

其规则文件的语法简单,但规则较繁杂。

规则文件通常包括描述模块(Description Block)、输入层模块(Inputlayer Block)、操作模块(Operation Block)三个部分。

每一个模块有一个开始标志(如:*DESCRIPTION)和结束标志(*END)。

描述模块定义了Dracula运行环境。

包括运行模式、基本单元名、输入/输出设备、文件名、格式、图形比例元素、网格大小、输出记录文件、警告消息显示等。

输入层模块把布局图的层名或层编号和Calibre的层名对应起来,并提供Calibre进行验证所需的其他关于层的信息。

主要是:要输出的层、层名、掩膜顺序、要输出的层、文本层。

操作层定义要进行的操作和应用程序并且标出错误。

它定义的操作类型有:逻辑、电气节点、缩放、参数、空间、ERC、DRC、LVS、LPE和PRE。

drc和lvs验证原理

drc和lvs验证原理DRC和LVS验证原理1. 什么是DRC和LVS验证DRC和LVS是集成电路设计中非常重要的验证流程,用于确保芯片设计的正确性和可靠性。

DRC全称为Design Rule Check(设计规则检查),LVS全称为Layout versus Schematic(布局与原理图相对比)。

DRC验证主要检查物理设计是否符合制造工艺规范,而LVS验证主要检查布局和原理图之间的一致性。

2. DRC验证原理•DRC验证主要通过规则检查器对物理设计进行分析和验证,通常包括以下几个方面:–尺寸规则检查:检查晶体管、连线等元件的尺寸是否符合制造工艺要求;–布局规则检查:检查器件间的间距、连线的宽度等是否符合要求;–链接规则检查:检查连接的连线长度、电容等是否符合要求;–电压规则检查:检查是否存在电压冲突、短路等问题。

•DRC验证的目标是确保物理设计满足制造工艺的要求,避免制造工艺的失败和电路性能的问题。

3. LVS验证原理•LVS验证主要通过比较布局和原理图之间的差异来检查设计的正确性,通常包括以下几个步骤:1.提取布局:将物理设计中的连线、晶体管等元件提取出来,生成布局;2.提取原理图:从设计工具中提取原理图;3.生成SPICE模型:将原理图转换为SPICE模型,用于电路模拟;4.进行电路模拟:使用SPICE模拟器对提取的布局和原理图进行电路模拟;5.比较结果:对模拟结果进行比较,检查是否存在差异。

•LVS验证的目标是确保布局和原理图的一致性,避免因布局错误导致的电路功能故障和性能问题。

4. DRC和LVS验证之间的关系DRC和LVS验证是互补的,虽然都是针对芯片设计的不同方面进行验证,但两者之间相互影响: - DRC验证主要考虑制造工艺的要求,而LVS验证主要考虑设计功能的正确性,因此,DRC验证的结果可以为LVS验证提供一定的参考; - 如果DRC验证不通过,表示物理设计存在问题,可能导致LVS验证失败; - 如果LVS验证不通过,表示布局和原理图不一致,可能需要对物理设计进行调整,以修复问题。

半导体lvs过程

半导体lvs过程

半导体LVS(Layout Versus Schematic)过程是一种验证电路设计的正确性和一致性的过程。

在LVS过程中,电路设计团队将使用工具将电路原理图转换为版图,然后与原始的电路原理图进行比较,以检查二者之间的一致性。

具体来说,LVS过程包括以下几个步骤:

1.电路原理图到版图的转换:这一步通常使用EDA(Electronic Design Automation)工具来完成,将电路原理图转换为版图。

版图是电路元件和连接关系的物理表示,可以用于后续的物理验证和制造。

2.版图和电路原理图的比较:在这一步中,LVS工具将版图和电路原理图进行比较,以检查二者之间的一致性。

比较的内容包括连接关系、元件类型、大小和位置等,以确保版图与电路原理图完全一致。

3.报告和错误检查:如果版图和电路原理图之间存在不一致,LVS工具会生成报告并指出错误的位置和类型。

设计团队需要根据报告进行修正,并重新进行LVS验证,直到版图与电路原理图完全一致。

半导体LVS过程是确保电路设计正确性和一致性的重要步骤,有助于减少制造过程中的错误和返工。

lvs验证的小技巧

lvs验证的小技巧(原创实用版3篇)篇1 目录1.LVS 验证的重要性2.LVS 验证的小技巧概述3.具体小技巧一:合理选择验证工具4.具体小技巧二:制定详细的验证计划5.具体小技巧三:注重团队协作与沟通6.具体小技巧四:及时总结与反馈7.总结篇1正文LVS 验证的重要性LVS(Load Vector Simulation)验证是软件测试中一个重要的环节,主要用于模拟用户使用场景,以评估系统的性能、稳定性和可靠性。

通过LVS 验证,可以发现系统在高并发、高负载情况下的问题,从而保证软件质量。

因此,在进行 LVS 验证时,掌握一些小技巧是非常必要的。

LVS 验证的小技巧概述本文将为大家介绍四个 LVS 验证的小技巧,分别是:合理选择验证工具、制定详细的验证计划、注重团队协作与沟通、及时总结与反馈。

下面将逐一进行详细介绍。

具体小技巧一:合理选择验证工具选择合适的验证工具是 LVS 验证成功的关键。

目前市场上有很多验证工具,如 JMeter、LoadRunner 等。

选择验证工具时,需要考虑以下几点:1.验证目标:根据验证目标选择合适的工具,例如,如果需要测试数据库性能,可以选择专门针对数据库的验证工具。

2.系统架构:选择与被测系统架构相匹配的验证工具,例如,如果被测系统是分布式系统,需要选择支持分布式测试的验证工具。

3.预算与技术水平:根据预算和技术水平选择合适的验证工具,避免选择过于复杂或昂贵的工具。

具体小技巧二:制定详细的验证计划在进行 LVS 验证前,需要制定详细的验证计划,包括以下几个方面:1.验证目标:明确验证的目标,例如,吞吐量、响应时间、错误率等。

2.验证场景:根据用户使用场景,设计合理的验证场景,包括用户数量、操作类型、操作频率等。

3.验证工具:选择合适的验证工具,并了解其使用方法和注意事项。

4.验证环境:搭建与生产环境相似的验证环境,以确保验证结果的准确性。

5.风险评估:评估验证过程中可能出现的风险,并制定相应的应对措施。

lvs验证步骤 -回复

lvs验证步骤-回复LVS(Linux Virtual Server)是一种开源的软件负载均衡技术,它能够提供高可用性、可伸缩性和灵活性,用于提供稳定和可靠的网络服务。

在本文中,我将介绍LVS的验证步骤,以帮助读者了解如何正确地验证LVS 的配置。

验证LVS的步骤如下:1. 准备环境在验证LVS之前,我们需要准备一些基本环境。

首先,我们需要至少两台服务器,其中一台将作为LVS的负载均衡器,其他服务器将作为后端服务器。

另外,我们还需要安装并配置LVS软件,同时确保服务器之间能够正常通信。

2. 配置负载均衡器第一步是配置负载均衡器。

在LVS中,使用IPVS(IP Virtual Server)作为负载均衡的核心组件。

我们需要在负载均衡器上配置IPVS以确保其正常工作。

首先,我们需要创建一个VIP(Virtual IP),该VIP是客户端将访问的虚拟IP地址。

我们可以使用以下命令创建VIP:ip addr add VIP dev eth0其中VIP是我们选择的虚拟IP地址,eth0是服务器上的网络接口。

接下来,我们需要配置IPVS规则,以确定应将流量分发到哪些后端服务器。

我们可以使用以下命令来配置IPVS规则:ipvsadm -A -t VIP:端口-s 程序调度算法其中VIP是我们选择的虚拟IP地址,端口是要负载均衡的端口,程序调度算法是负载均衡使用的算法,例如轮询(rr)或加权轮询(wrr)。

3. 配置后端服务器在配置负载均衡器之后,我们需要配置后端服务器以确保它们能够正常工作。

首先,我们需要在每个后端服务器上启动服务,并确保它们可以相互通信。

然后,我们需要将后端服务器添加到负载均衡器中,以便流量可以被正确地分发。

我们可以使用以下命令将后端服务器添加到负载均衡器中:ipvsadm -a -t VIP:端口-r 后端服务器IP:端口-g其中VIP是我们选择的虚拟IP地址,端口是要负载均衡的端口,后端服务器IP是我们选择的后端服务器的IP地址,端口是要负载均衡的端口,-g选项表示将流量通过IP地址和端口进行分组。

lvs验证步骤

lvs验证步骤LVS(Linux Virtual Server)是一种用于构建高性能、高可用的服务器集群的开源软件。

通过将多台服务器组织成一个逻辑上的集群,LVS可以实现负载均衡、故障转移等功能,并提高整个系统的可扩展性和可靠性。

在使用LVS构建服务器集群之前,我们需要进行一系列的验证步骤,以确保集群的正常运行和功能实现。

第一步:确定需求和目标在进行LVS验证之前,我们需要确定我们要构建的服务器集群的需求和目标。

例如,我们可能需要实现负载均衡、高可用、高性能等功能,或者需要满足一定的性能指标和用户需求等。

根据需求和目标,我们可以选择合适的LVS技术和配置方案,并根据实际情况进行调整和优化。

第二步:选择合适的LVS技术LVS提供了多种负载均衡技术,包括NAT、DR(Direct Routing)和TUN(IP Tunneling)等。

在选择LVS技术时,我们需要考虑网络环境、服务类型和性能要求等因素。

例如,如果网络环境较为简单且要求提供透明的负载均衡服务,可以选择NAT技术;如果要求提供更高的性能和可扩展性,可以选择DR或TUN技术。

第三步:准备服务器集群在进行LVS验证之前,我们需要准备多台服务器,用于构建服务器集群。

这些服务器可以是物理服务器或虚拟机,需要安装相应的操作系统和软件环境,并进行网络配置和通信设置。

如果使用虚拟化技术,还需要确保虚拟机之间可以互相通信,并且与外部网络连接正常。

第四步:安装和配置LVS软件在服务器集群准备好后,我们可以开始安装和配置LVS软件。

LVS提供了一套完整的软件套件,包括ipvsadm、keepalived等工具,用于管理和配置LVS集群。

我们可以通过包管理工具如apt或yum来安装这些软件,并按照官方文档或相关资料进行配置。

配置过程中,我们需要设置LVS的参数、规则和策略,以实现负载均衡、故障转移等功能。

第五步:测试LVS集群在完成LVS的安装和配置后,我们需要进行一系列的测试来验证集群的功能和性能。

DRC验证

版图物理验证一、实验目的1、了解DRC和LVS在版图设计中的作用2、熟悉DRC和LVS的验证流程二、实验内容1、以反相器为例对版图进行DRC验证2、以反相器为例对版图进行LVS验证三、实验步骤根据上一节中所讲的,最后做出的版图如下所示,我们将根据这个版图进行DRC验证和LVS验证。

1、DRC验证DRC(Design Rule Check):几何设计规则验证,对IC版图做几何空间检查,以确保线路能够被特定加工工艺实现。

(1)在当前工作目录下,建立一个子目录calibre_drc,将所需要的验证文件CM35P5_4M.23a.2拷贝到calibre_drc目录下。

命令如下:mkdir calibre_drccp –rf /home/edauser/kong/TSMC035/Calibre_DRC/CM35P5_4M.23a.2 ./calibre_drc (2)建立.gds文件:在主窗口中File—>Export—>Stream,然后点击Library Browser,选择相应的库下相应的文件。

选好文件,关掉对话框即可。

将pmos的layout转成pmos.gds,并将pmos.gds拷贝到之前建立的calibre_drc文件夹中,如下面两幅图所示:选择Stream后会出现下列的对话框:添加的文本是制作的反相器的layout视图,点击Library Browser即可。

之后点击OK。

生成的文件为inv.gds,在后面的LVS、PEX验证中要用到。

返回当前版图,选择Calibre—>Run DRC出现如下对话框:通常我们先关掉Load Runset File对话框,进入设置Rules界面,填写DRC Rules File (之前在新建文件夹calibre_drc中的CM35P5_4M.23a.2文件)。

可以选择在目录calibre_drc 下运行,生成的一些文件会在这个目录中,不至于太乱。

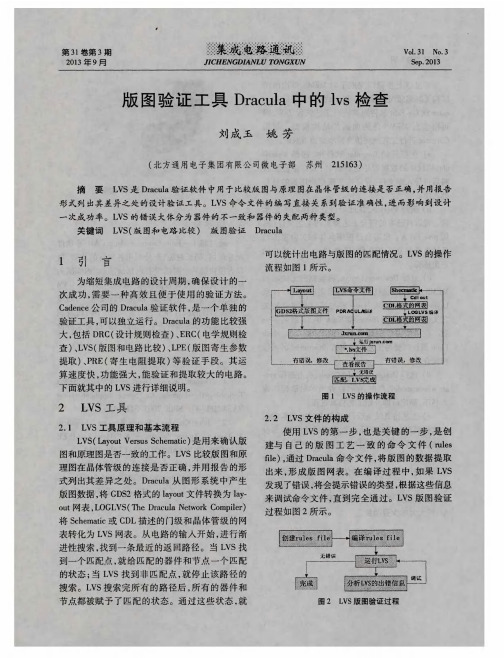

版图验证工具Dracula中的lvs检查

豢 纂戡

要

数 据库 的数值 。

3 9

L V S 命令文件结构包括以下三部分 :

1 ) 描述 块 : 包 括输 人输 出的文件 的路径 和名 称, 待检测 的顶 层 c e l 1 名, C A D版 图 图形 系统 名 ,

R E S O L U T I O N: 指定 检 查 版 图 时 的最 小 查 图 步进 量 。

此命 令 可产 生 日志文件 或列 表 文件 。 K E E P D A T A: 确定是 否保 存 中间数据 文件。

数 字是 版 图中 的 GFra bibliotekD S层 号 。

3 ) 操作运算块 : 命令文件的主体部分 。用来 进行版图的提取 , 要结合具体的工艺 、 版图的结构 识别出版图中的各种元器件和连接关系。利用层

识别 , 与具 体层 的名 称无 关 ) 。否则 , L V S不 可 能

0 I ND I S K =f i l e n a me . g d s; i n p u t i f l e n a me

OUTDI S K =c h e c k . o u t; o u t p ut il f e n a me

缺省 。

S UBS TRATE = b u l k 6 3 CONNEC T —LAYER =ps u b n we l l n s d p s d p o — l yl me al t l o p 2 di f

¥E ND ; t h e e n d o f he t b l o c k

( 1 )“¥ I N P U T—L AY E R” , “ E N D” 是 此

P R I M A R Y : 指定主单元名 , 此项不可缺省 。

LVS验证的实验指导

第五章物理验证(一)教学内容1.物理验证的概念;2.主流物理验证工具介绍;Calibre 是Mentor Graphics 的IC版图验证软件,此软件包括设计规则检查(DRC )、版图与原理图一致性检查(LVS)、电气规则检查(ERC)、及版图寄生参数萃取(LPE)等验证功能。

其操作界面主要分为图形模式(GUI)(graphical user interface) Calibre Interactive与指令模式(Command Line),其中图形模式可以单独启动,亦可与Virtuoso 等软件相连接,其操作界面皆相同。

本章我们主要研究图形模式。

3.主要术语⏹SVRF---Standard Verification Rule Format(标准的检查文件)⏹RVE---Results Viewing Environment(显示结果用的环境窗口)⏹SVDB---Standard Verification Database (LVS results)⏹DRC---Design Rule Check(设计规则检查)⏹ERC---Electrical Rule Checking(电气规则检查)⏹LVS---Layout Versus Schematic(版图原理图一致性检查)⏹LPE---Layout Parasitic Extraction(版图寄生参数萃取)第二节LVS版图与原理图的一致性4.Calibre LVS 简介Calibre LVS 是一个出色的版图与线路图对比检查工具,具有高效率、高准确度和大容量等优点。

Calibre LVS 不仅可以对所有的“元件”进行验证,而且还能在不影响性能的条件下,处理无效数据。

主要表现在以下几个方面:(1) 运行模式快捷方便:Calibre LVS 有两种运行模式,即命令行模式和界面模式(Calibre Interactive-LVS)。

采用命令行模式可以快速输入控制命令,快速运行,其结果精确稳定。

LVS检查

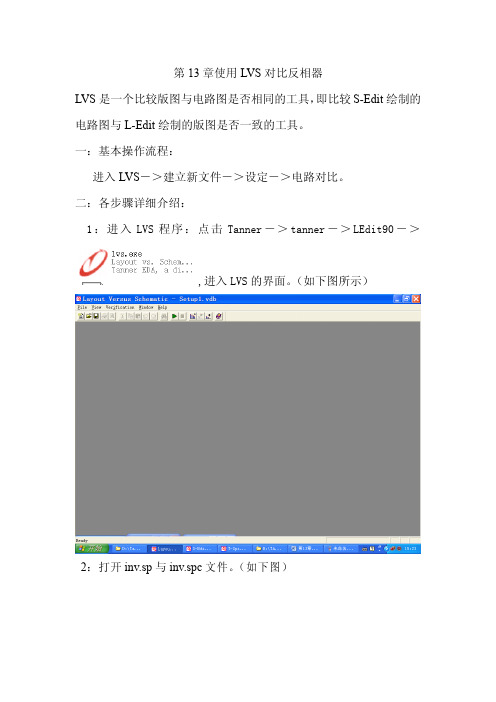

第13章使用LVS对比反相器LVS是一个比较版图与电路图是否相同的工具,即比较S-Edit绘制的电路图与L-Edit绘制的版图是否一致的工具。

一:基本操作流程:进入LVS->建立新文件->设定->电路对比。

二:各步骤详细介绍:1:进入LVS程序:点击Tanner->tanner->LEdit90->,进入LVS的界面。

(如下图所示)2:打开inv.sp与inv.spc文件。

(如下图)在两个文档中都要输入文件路径名:.include D:\Tanner\tanner\TSpice70\models\ml2_125.md。

3:各项参数的设定:选择File->New命令,出现如下对话框:单击确定,出现对话框Setup1。

(1):在Input标签下,各文本栏按如下所示填写:(2):在Output标签下,各文本栏按如下所示填写:(3):在Device Parameters标签下,各文本栏按如下所示填写:(4):Merge Devices,Parasitics,两个标签下的内容不要作任何的修改。

(5):在Options标签下,各文本栏按如下所示填写:(6):在Performance标签下,各文本栏按如下所示填写:4:按第3步将各项参数设定完成以后,进行保存。

选择File->Save As命令,在弹出的对话框中为文件取好名字后进行保存就可以了5:进行仿真:选择标签:,出现Verification对话框。

(如下图所示):从以上对比结果看,这两个文件不完全相同。

因为inv.sp文件中的MOS管的参数W为22u,e而inv.spc文件中的MOS管的参数W为5u。

6:将原理图中的MOS管的W都该为5u,然后在LVS的界面中重新生成一次新的inv.sp文件,再进行一次LVS比较可以得到两个文件的比较结果完全相同。

(如下图):。

版图验证

Cadence IC设计实验实验四、Diva Interactive Verification实验目的:掌握DRC和LVS验证方法版图绘制后要根据foundry厂的工艺要求进行DRC(Design Rule Checker)检查,编辑好的版图必须通过LVS(Layout Versus Schematic)验证,检查是否与schematic电原理图完全一致;版图中还可能存在一些悬空的器件和线网,通过电气规则检查ERC(Electrical Rule Check)可以发现这些错误。

进行LVS和ERC之前,需要用Diva验证工具中的Extract 程序对版图进行器件提取;Extract还可以进行寄生参数提取,电路仿真程序可以调用这个数据进行后仿真。

DIV A工具集包括以下部分:1.设计规则检查(DRC)2.提取Extractor:包括器件提取、版图寄生参数提取(LPE)、寄生电阻提取(PRE)3.电气规则检查(ERC)4.版图与线路图比较(LVS)预备工作:cp /eva01/cdsmgr/ training_IC_data/DivaInt_5_0.tar .tar-vxf DivaInt _5_0.tarcd diva实验内容与步骤:第一部分:DRC设计规则检查一、进入DRC菜单:[1]、 icfb &[2]、 在CIW 窗口(icfb-Log:/…),点击Tools->Library Manager;[3]、Library列表框中点击design;Cell列表框中点击peakDetect;View列表框中双击layout; (或用鼠标右键open)(注:这是峰值检测器电路版图,你可以查看相应的schematic 了解电路原理)[4]、在出现的Virtuoso Layout Editing窗口,点击Verify->DRC…菜单。

出现下图DRC窗口:二、查找某层(poly1层)DRC错误[5]、在DRC窗口,点击右边的Set Switches按钮,在弹出列表中选择poly1,点击OK,再点击DRC窗口OK。

版图验证之lvs课件

v 8)、输入则开始执行LVS检验。

v 9)、程序结束后,生成很多文件,可通过lvs.lvs来查看错误

版图验证之lvs

20

❖ 在当前目录~/home/yd8888/lvs下,运行查阅目录命令: lvs.lvs

版图验证之lvs

SELECT PBASE ENCLOSE NEMIT

NOT

NPLUS

NEMIT

NPNB(NPN管的基极) NCOLL

CHEESE

NEMIT

版图验证之lvs

8

pnp管的平面结构层次图

基极

集电极

ISO BLN N+

发射极

PBASE

CONT

版图验证之lvs

9

Device layers definition

框

运行目录

输出文件名

版图验证之lvs

17

5)建立电路网表。在icfb窗中,选命令File→Export→CDL...,出现“CDL Out Run Form ”对话框

版图验证之lvs

18

版图验证之lvs

19

v 6)、 以上操作全部完成后,在终端控制台中输入cd lvs 回车键入大 写LOGLVS,然后在回车后输入“cir 网表名”编译网表,“con 要转换的电路原理图的top cell名” 再回车后 输入“x”退出。

(8) 连接节点表

3. 查找和消除错误

LVS使用节点和器件的扩展名识别错误的电路图节点、器件或子电路, 也识别较高级别的门或部件的功能块。对于版图器件,LVS以自然单位 打印X和Y的位置,而且,LVS的错误类型能产生图示输出,在某些情况 下,它比列表(像表示阵列的重复错误)能更直接指出错误

LVS验证的实验指导

第五章物理验证(一)教学内容1.物理验证的概念;2.主流物理验证工具介绍;Calibre 是Mentor Graphics 的IC版图验证软件,此软件包括设计规则检查( DRC )、版图与原理图一致性检查(LVS)、电气规则检查(ERC)、及版图寄生参数萃取(LPE)等验证功能。

其操作界面主要分为图形模式(GUI)(graphical user interface) Calibre Interactive与指令模式(Command Line),其中图形模式可以单独启动,亦可与Virtuoso 等软件相连接,其操作界面皆相同。

本章我们主要研究图形模式。

3.主要术语⏹ SVRF---Standard Verification Rule Format(标准的检查文件)⏹ RVE---Results Viewing Environment(显示结果用的环境窗口)⏹ SVDB---Standard Verification Database (LVS results)⏹ DRC---Design Rule Check(设计规则检查)⏹ ERC---Electrical Rule Checking(电气规则检查)⏹ LVS---Layout Versus Schematic(版图原理图一致性检查)⏹ LPE---Layout Parasitic Extraction(版图寄生参数萃取)第二节 LVS版图与原理图的一致性4.Calibre LVS 简介Calibre LVS 是一个出色的版图与线路图对比检查工具,具有高效率、高准确度和大容量等优点。

Calibre LVS 不仅可以对所有的“元件”进行验证,而且还能在不影响性能的条件下,处理无效数据。

主要表现在以下几个方面:(1) 运行模式快捷方便:Calibre LVS 有两种运行模式,即命令行模式和界面模式(Calibre Interactive-LVS)。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

第四章验证多路复用器版图——Verifying the Multiplexer LayoutThis chapter introduces you to interactive verification. You will perform two different tests in the Virtuoso® layout editor while using Diva interactive verification. One test uses the Design Rule Checker (DRC) to compare your design against the design rule, and the other test uses Layout Versus Schematic (LVS) software to check your design’s connectivity. You will be 本章向您介绍交互式验证。

在使用Diva交互式验证时,您将在Virtuoso®版图编辑器中执行两个不同的测试。

一个测试使用设计规则检查器(DRC)将您的设计与设计规则进行比较,另一个测试使用Layout Versus Schematic(LVS)软件来检查您的设计的连通性。

你将会Creating a Test Case for Checking Errors 创建用于检查错误的测试用例⏹Performing a Design Rule Check 执行设计规则检查⏹Extracting Connectivity from the Layout 从版图中提取连接性⏹Comparing the Layout to the Schematic 将版图与原理图进行比较⏹Analyzing LVS Errors 分析LVS错误⏹Correcting the Error 更正错误⏹Rerunning Verification on page 重新验证When you finish this chapter, you will be able to 完成本章后,您将能够⏹Run a design rule check and view errors 运行设计规则检查并查看错误⏹View and correct DRC errors 查看并更正DRC错误⏹Run extraction on a layout 在版图上运行提取⏹View a schematic 查看原理图⏹Cross-probe between a layout and a schematic 版图和原理图间的交叉探测⏹Rerun verification after correcting an error 纠正错误后重新运行验证找出是否可以运行交互式验证——Finding Out if You Can Run Interactive Verification You might not have a license to run the interactive verification products.您可能没有运行交互式验证产品的许可。

➤Click the Verify menu to find out whether you can use interactive verification.➤单击“验证”菜单以确定是否可以使用交互式验证。

If the commands under Verify appear shaded, you do not have a license to run interactive verification. You can either read this chapter to get an idea about how interactive verification works, or you can go on to the next chapter.如果“验证”下的命令显示为阴影,则表示您没有运行交互式验证的许可证。

您可以阅读本章以了解交互式验证的工作原理,也可以继续阅读下一章。

如果您还没有完成以前的章节——If You Have Not Completed the Previous ChaptersThis chapter assumes you have followed the steps in the previous chapters. If you have, you can skip this section and go to the “Creating a Test Case for Checking Errors” on page 107. If you did not follow the steps in the previous chapters, you must copy a completed design from the master library so you can go through this chapter. The following steps show you how to copy the completed design from the master library.本章假设您已按照前面章节中的步骤进行操作。

如果有,可以跳过本节并转至第107页的“创建检查错误的测试用例”。

如果未按照前面章节中的步骤进行操作,则必须从master 库中复制已完成的设计,以便可以完成这一章。

以下步骤说明如何从master库复制完成的设计。

It is possible to run out of resources, such as memory, if you run multiple layout editors. Before you start the software, you need to check whether the software is already running.如果运行多个版图编辑器,则可能会耗尽资源(如内存)。

在启动软件之前,您需要检查软件是否已在运行。

1. Type the following in an xterm window to check whether the layout editor is already running:1.在xterm窗口中键入以下内容以检查版图编辑器是否已在运行:ps auxw | grep layout2. If the layout editor is running, choose File – Exit in the Command Interpreter Window (CIW)to exit the software.2. 如果版图编辑器正在运行,请在命令解释器窗口(CIW)中选择文件- 退出以退出软件。

3. Type the following in an xterm window to start the layout editor:3. 在xterm窗口中键入以下内容以启动布局编辑器:cd ~/cell_designlayoutPlus &4. Choose File – Open. 4. 选择文件- 打开。

The Open File form appears. 出现“打开文件”表单。

5. Type the library, cell, and view names as follows: 键入库,单元和视图名称,如下所示:Library Name masterCell Name mux2View Name layout6. Click OK.The mux2 cell from the master library opens. master库中的mux2单元打开。

7. In the cellview window, choose Design – Save As. 在cellview窗口中,选择Design–Save AsThe Save As form appears. 出现“另存为”表单。

8. In the Save As form, type the library and cell names as follows:8. 在“另存为”窗体中,键入库和单元名称,如下所示:Library Name tutorialCell Name mux29. Click OK.The mux2 cell is copied to the tutorial library. 将mux2单元格复制到教程库中。

10. In the mux2 cellview, choose Window – Close to close the cellview.10. 在mux2 cellview中,选择Window – Close以关闭cellview。

11. In the CIW, choose Open – File to open the mux2 layout you just saved.11. 在CIW中,选择Open – File以打开刚刚保存的mux2版图。

12. Type the library, cell, and view names as follows:键入库,单元和视图名称,如下所示:Library Name tutorialCell Name mux2View Name layout13. Click OK.The mux2 cell from the tutorial library opens. 将打开教程库中的mux2单元。

Note: Another way to open a cellview is with the Open command. Using Open replaces the current window with the new window. To use the Open command, choose Design – Open. The Open File form appears. Set the library, cell, and view names to the cellview you want to open, and click OK. The current cellview is replaced with the new cellview.注意:打开cellview的另一种方法是使用Open命令。

使用Open用新窗口替换当前窗口。