版图设计规则分析

版图设计规则

版图几何设计规则

版图几何设计规则可看作是对光刻掩 模版制备要求. 一般来讲,设计规则反映了性能和成 品率之间可能的最好的折衷.规则越保 守,能工作的电路就越多(即成品率越 高);然而,规则越富有进取性,则电路 性能改进的可能性也越大,这种改进可 能是以牺牲成品率为代价的.

版图几何设计规则

(1)微米规则 (2)λ规则

版图几何设计规则

大部分设计规则都可以归纳入以下描 述的四种规则之一. (1)最小宽度 (2)最小间距 (3)最小包围 (4)最小延伸

版图几何设计规则

设计规则(硅栅)举例:

0.6um 2p2m CMOS

0.6um 2p2m

版图几何设计规则-N阱

定义了P沟道器件的N阱尺寸,N型杂志注入该 区域形成N-well. N-well宽度 3.0 不同电势的N-well之间的距离-4.8 N-well中用于接触的N+与阱边沿的距离-0.4 N-well距阱外的N+的距离-4.0 N-well距阱外的P+的距离-0.4 N-well距阱内的P+的距离-1.8 距划线槽的距离8.0

版图几何设计规则-接触孔

0.6

0.6

0.4

0.6

0.7

0.4

0.6

0.4

版图几何设计规则

编号 1 2 描述 金属宽度 金属间距 尺寸 0.9 0.8 防止铝条接触 保证良好导电性

版图几何设计规则-金属1

metal1宽度:0.9 Metal1之间的距离:0.8 Metal1距接触孔的距离:0.3

版图几何设计规则-多晶硅

PMOS

NMOS

0.6

0.6

0.6

0.75

0.5

版图设计流程

版图设计流程版图设计是一项非常重要的工作,它直接关系到产品或者项目的整体形象和用户体验。

一个好的版图设计可以提升产品的吸引力和竞争力,因此,版图设计流程的规范性和有效性显得尤为重要。

在进行版图设计时,我们需要遵循一定的流程,以确保设计的高质量和高效率。

第一步,需求分析。

在进行版图设计之前,我们需要对产品或项目的需求进行充分的分析。

这包括对目标用户群体的需求分析,对产品功能和特性的分析,以及对市场和竞争对手的分析。

只有充分了解需求,我们才能进行有针对性的版图设计,满足用户的实际需求。

第二步,概念构思。

在完成需求分析后,我们需要进行概念构思。

这一阶段是版图设计的灵感迸发阶段,我们可以进行大胆的构思和创意的发挥。

在这个阶段,可以进行头脑风暴,绘制草图,或者进行一些简单的设计尝试,以寻找最合适的设计方向。

第三步,结构规划。

在完成概念构思后,我们需要进行版图设计的结构规划。

这包括对版图的整体结构进行规划,确定版面布局、内容分区、色彩搭配等。

在这一阶段,我们需要考虑版图的视觉引导和信息传达,确保用户在浏览版图时能够快速获取所需信息。

第四步,细节设计。

在完成结构规划后,我们需要进行版图设计的细节设计。

这包括对版面的各个细节进行精细化设计,包括文字排版、图标设计、配色搭配等。

在这一阶段,我们需要注重细节,确保版图的每一个元素都能够完美地融入整体设计中。

第五步,评审修改。

在完成版图设计后,我们需要进行评审和修改。

这一阶段需要邀请相关的人员对版图进行评审,包括设计师、产品经理、市场人员等。

根据评审意见,我们需要对版图进行适当的修改和调整,以确保设计符合实际需求和市场需求。

第六步,输出交付。

最后,我们需要将完成的版图设计进行输出和交付。

这包括将设计稿转化为可用的格式,如图片、PDF等,并交付给相关的部门或人员使用。

在交付时,我们需要确保设计的质量和准确性,以满足后续的使用需求。

总结。

版图设计流程是一个复杂而严谨的过程,需要设计师和相关人员的共同努力和配合。

电路版图设计与规则(参考模板)

第三章集成电路版图设计每一个电路都可以做的很完美,对应的版图也可以画的很艺术,需要的是耐心和细心,当然这需要知识,至少我这么认为。

3.1认识设计规则(design rule)什么是设计规则?根据实际工艺水平(包括光刻精度、刻蚀能力、对准容差等)和成品率要求,给出的一组同一工艺层及不同工艺层之间几何尺寸的限制,主要包括线宽、间距、覆盖、露头、凹口、面积等规则,分别给出它们的最小值,以防止掩膜图形的断裂、连接和一些不良物理效应的出现。

芯片上每个器件以及互连线都占有有限的面积。

它们的几何图形形状由电路设计者来确定。

(从图形如何精确地光刻到芯片上出发,可以确定一些对几何图形的最小尺寸限制规则,这些规则被称为设计规则)制定设计规则的目的:使芯片尺寸在尽可能小的前提下,避免线条宽度的偏差和不同层版套准偏差可能带来的问题,尽可能地提高电路制备的成品率。

设计规则中的主要内容:Design Rule通常包括相同层和不同层之间的下列规定:最小线宽 Minimum Width最小间距 Minimum Spacing最小延伸 Minimum Extension最小包围 Minimum Enclosure 最小覆盖 Minimum Overlay集成电路版图设计规则通常由集成电路生产线给出,版图设计者必须严格遵守!!!3.2模拟集成电路版图设计中遵从的法则3.2.1电容的匹配对于IC layout工程师来说正确地构造电容能够达到其它任何集成元件所不能达到的匹配程度。

下面是一些IC版图设计中电容匹配的重要规则。

1)遵循三个匹配原则:它们应该具有相同方向、相同的电容类型以及尽可能的靠近。

这些规则能够有效的减少工艺误差以确保模拟器件的功能。

2)使用单位电容来构造需要匹配的电容,所有需要匹配的电容都应该使用这些单位电容来组成,并且这些电容应该被并联,而不是串联。

3)使用正方块电容,并且四个角最好能够切成45度角。

周长变化是导致不匹配的最主要的随机因素,周长和面积的比值越小,就越容易达到高精度的匹配。

版图设计规则及验证汇总

N- Si 阱

P-S i Sub

光刻3:硅栅光刻

3#版为多晶光刻掩膜。用于制作多晶硅栅极以及 形成电路结构的多晶硅的连线和电阻。这一步是 在新生长的栅氧化层上先用CVD法沉淀多晶硅,用 该版以干法刻蚀出所需多晶硅图形。

光刻3:硅栅光刻

N- Si 阱

P-S i Sub

光刻4:P管源漏区芯片规划 根据已知的模块数量和线网连接表来估算芯片面 积,其中模块大约占用一半,另一半用来作为布 线通道。

二、版图设计过程

(三)布局 布局是指如何把各个模块合理地排布在芯片上, 怎样确定每个模块的最佳位置,以使占用芯片面 积为最小且布线结果又最好。

二、版图设计过程

二、版图设计过程

版图设计主要包括模块设计、芯片规划、布局、 布线等,是一个组合规划和巧拼图形的工作。在 一个规则形伏(一般为长方形)平面区域内不重 叠地布局多个模块(亦称部件),在各模块之间 按电路连接信息的要求逐行布线。版图设计是从 逻辑信息向几何信息的转换。

二、版图设计过程

(一)模块设计 芯片设计中最小的单位是元件,设计过程从元件, 门,基本单元,宏单元,芯片,从小到大进行。 基本单元和宏单元可视为模块。模块设计是最基 本的环节。

光刻5:N管源漏区注入光刻

N+注入

N- Si 阱

P-S i Sub

光刻6:接触孔光刻

6#版为接触孔掩膜。用来确定欧姆接触的大小和 位置。

光刻6:接触孔光刻

N- Si 阱

P-S i Sub

光刻7:金属引线光刻

7#版为金属图形(电极和连线)掩膜。用于确定集成 元器件电极引出和互连布线的位置和形状。在上 一版接触孔光刻之后,硅片表面用CVD法淀积上一 层金属膜,用该版留下所要的金属膜,实现金属层欧 姆引出和互连。

大型展版设计规则

大型展版设计规则

大型展版设计规则主要包括以下几个方面:

1. 版面布局:版面布局要合理,以逻辑性为先,让展板看起来舒适简洁。

展示顺序一定要有逻辑,根据主题的清晰度和简略度来安排。

重心位置要放在展板上的中心点上,能够吸引更多人的目光。

2. 标题设计:标题要简洁明了,字体要大,有吸引力,易于吸引人的注意力。

副标题要突出展板的主题,不要太长,字体大小与标题相匹配。

3. 文字设计:文字要简明扼要,字体大小不宜过小,同时也要注意排版的规范性,尽量使各个方面的信息量均衡。

4. 插图设计:插图一定要与主题相关,形象生动,不要太小,同时避免太多干扰人眼。

5. 色彩搭配:色彩搭配要和谐统一,不要过于花哨,也不要过于单调。

可以使用色彩心理学来选择适合主题的颜色。

6. 展版材质:选择合适的材质可以让展板更耐用,更易于维护。

比如可以选择塑料板、玻璃板、木板等不同材质。

7. 灯光设计:灯光设计要合理,能够突出展品的特色和优势。

可以使用不同的灯光效果来营造氛围。

8. 版面尺寸:展板尺寸一定要经过精心考虑,不要太小,避免人看不清,同时也不能太大,造成视觉上的冲撞。

9. 版面留白:展板四周留边距,不要过于拥挤。

适当的留白可以让版面更加整洁,易于观看。

10. 统一性:整个展版的风格、色彩、字体等都要统一,避免给观众带来视觉上的混乱。

以上是大型展版设计规则的一些基本要素和注意事项,希望对你有所帮助。

版图注意事项

版图注意事项版图(Layout)是指在设计活动场所(如办公室、商店、展览馆、室内设计等)时,根据功能需求合理布置、安排各个物件、设施和空间的一种方式。

一个合理的版图设计可以有效地提高工作效率,增加空间利用率,以及提升用户体验。

在设计版图时,有一些注意事项需要考虑,以确保最终设计符合需求并具有良好的可用性和可扩展性。

首先,版图设计需要考虑用户的需求。

不同的场所和活动有不同的功能需求,因此,在进行版图设计之前,需要了解用户的需求和习惯。

例如,在商店设计中,需要根据商品的种类和销售策略,确定不同区域的位置和大小,以便顾客能够方便地浏览和购买商品。

其次,版图设计需要合理安排空间和设施。

在设计版图时,需要考虑到整个空间的利用率和流线性。

例如,在办公室设计中,需要合理安排工位、会议室和公共休息区的位置,以方便员工之间的交流和协作。

此外,还需要合理安排设施,如电源插座、网络接口和储物空间等,以满足员工的需求。

同时,版图设计需要考虑环境因素。

在版图设计中,需要考虑到光源、空气流通和温度等环境因素。

例如,在室内设计中,需要考虑到窗户的位置和大小,以确保室内有足够的光线。

此外,还需要考虑到通风和空调系统的设计,以确保室内的空气流通和温度的适宜。

版图设计还需要考虑人们的行为习惯和心理因素。

在设计版图时,需要考虑到人们在活动场所中的行为习惯和心理需求。

例如,在商店设计中,需要合理安排通道和商品的摆放位置,以方便顾客的浏览和购买。

此外,还需要考虑到人们的隐私需求和舒适感,以确保设计的活动场所能够提供一个愉快和舒适的环境。

此外,版图设计还需要考虑到可扩展性和灵活性。

在设计版图时,需要考虑到未来可能的变化和扩展需求。

例如,在办公室设计中,需要留出一定的空间,以应对人员增加和功能扩展的需求。

此外,还需要考虑到布线和设施的灵活性,以便日后的维护和改造工作。

综上所述,版图设计是一项复杂而细致的工作。

在进行版图设计时,需要考虑用户的需求、空间布局、环境因素、行为习惯和心理需求、可扩展性和灵活性等因素。

版图设计重要知识点

版图设计重要知识点版图设计是指在平面传媒中利用文字、图片、色彩等元素进行排版,使之达到美观、易读和传达信息的目的。

良好的版图设计能够吸引读者的眼球,提升阅读体验,下面将介绍版图设计中的几个重要知识点。

一、页面布局页面布局是版图设计的基础,它决定了各个元素的位置、大小、顺序和比例。

常见的页面布局有对称布局、平衡布局和协同布局等。

对称布局指的是页面元素在水平或竖直方向上的对称排列,能够给人以稳定、整齐的感觉;平衡布局指的是页面元素在整个页面上的均衡分布,使得视觉上的重量平衡;协同布局则是指页面元素之间相互协调,形成整体效果。

二、字体选择在版图设计中,字体的选择很重要,它直接影响到文字的易读性和美观性。

在选择字体时,应考虑到字体的风格与内容的一致性,同时还要考虑到字体的大小和行间距,以确保文字清晰可读。

常见的字体有宋体、黑体、楷体等,它们在不同的设计场景中有不同的应用。

三、色彩运用色彩是版图设计中的重要元素之一,它能够给人以视觉冲击力和情感表达。

在运用色彩时,需要考虑到色彩的搭配和对比,避免过于花哨或造成视觉疲劳。

一般情况下,可采用类似的色系进行配色,同时保持页面整体的统一性和和谐感。

四、图片选择图片在版图设计中有很大的作用,能够直观地传达信息和吸引读者。

在选择图片时,应根据内容和风格的需要进行挑选,同时要保证图片的清晰度和分辨率。

此外,在版图设计中,还可以通过调整图片的大小、位置和透明度等方式,与文字和其他元素进行融合,形成更好的视觉效果。

五、白空间利用白空间是指页面中没有被文字、图片和其他元素填充的空白区域。

合理利用白空间可以提升版图设计的美感和阅读体验,使页面显得更加整洁和舒适。

白空间不仅能够使得内容更加突出,还能够提高文字的可读性。

总之,版图设计是一门独特的艺术,需要设计师兼顾美观性和功能性,灵活运用各种元素来达到理想的效果。

通过合理的页面布局、字体选择、色彩运用、图片选择和白空间利用等知识点的运用,可以制作出吸引人眼球、易读且传递信息的版图设计作品。

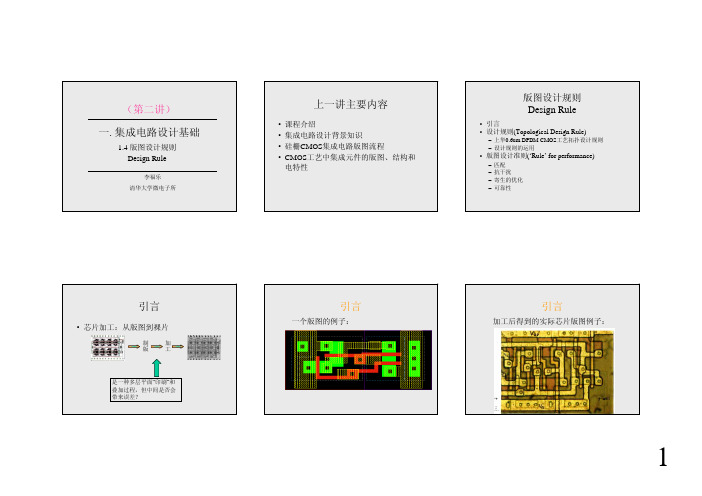

第二讲集成电路版图设计规则

- 1.5mA 最大电流密度

/um

-

- 禁止并行金属线90度拐角,用135

度拐角代替

a

c.2

b

c.1 c.2

设计规则 via

定义为两层金属之 间的连接孔

符号 尺寸

含义

12.a .7*.7 过孔最小面积

12.b 0.8 过孔间距

12.d~f - 接触孔、poly-poly电容和栅 上不能打过孔

12.g 0.4 金属1对过孔的最小覆盖

6.d 6.e 6.f 6.g

尺寸 1.2 1.0 0.5 3.2 1.5 0.8 -

含义 poly2做电容时的最小宽度 poly2做电容时的最小间距 Poly2与有源区的最小间距 做关键电容时的间距 电容底板对顶板的最小覆盖 电容Poly2对接触孔最小覆盖 Poly2不能在有源区上 Poly2不能跨过poly1边沿

– 上华0.6um DPDM CMOS工艺拓扑设计规则 – 设计规则的运用

• 版图设计准则(‘Rule’ for performance)

– 匹配 – 抗干扰 – 寄生的优化 – 可靠性

引言

• 芯片加工:从版图到裸片

制

加

版

工

是一种多层平面“印刷”和 叠加过程,但中间是否会 带来误差?

引言

一个版图的例子:

习)

VDD

15k

OUT IN 80/0.8

又试问NMOS晶体管的漏极面积和周长是多 少?

设计规则的运用

• TASK3:设计一个简单开关电容电路 (练习)

f1 IN

30/0.6 X

f2 OUT

60/0.6 2pF 6/0.6 12/0.6

又试问X点的寄生电容如何计算?

版图设计规范

Q/AT 中国电子科技集团公司第十三研究所企业标准Q/AT 43016.×××-2005第十六专业部薄膜电路版图设计规范拟制:审核:批准:2005-9-6版中国电子科技集团公司第十三研究所批准目录•1.版图一般要求•2.版图元件要求•3.基片和组装材料选择•4.薄膜电阻最大允许电流•5. 版图和组装图审核要求•附录1 元器件降额准则(摘要)•附录2 版图和组装图审核表•附录3 组装图模版(AUTOCAD格式)薄膜电路版图设计规范版本:2005-9-61版图一般要求:1.1基片和掩模版尺寸1.3非标准尺寸基片:50mm×60mm。

图形阵列最大尺寸不应大于46mm×56mm。

采用非标准基片要与工艺负责人商量。

1.4划线框尺寸:微晶玻璃基片200um,陶瓷基片 300um。

1.5基片厚度进口瓷片厚度 0.38mm 0.25mm。

国产瓷片厚度0.4mm 0.5mm, 0.8mm,1.0mm。

需要其它厚度陶瓷基片时,要提前预订。

1.6单元基片最大尺寸(包括划线槽)必须同时满足以下两个要求:(1)单元基片的每个边(角)到管座台面对应边(角)的最小距离0.5mm,(D-C>1)(2)单元基片边长比管壳对应管柱中心距应小1.5mm以上(A-B >1.5)。

表2 TO-8系列管壳对应最大正方形基片尺寸1.7常规生产应采用铬版。

1.8有薄膜电阻的版,要制作三层版。

第1层负版。

金块图形。

第2层正版。

金块图形加上电阻图形。

第3层正版。

仍为金块图形。

1.9没有薄膜电阻的版,制作2块版。

第1层负版。

金块图形第2层正版。

仍为金块图形。

1.10带金属化通孔的版,制作2层版。

,第1层正版。

金块图形,包括孔焊盘。

第2层正版。

金块图形加上电阻图形。

1.10.1小孔的位置在正式的版图中不应画出,也不用标记。

可以在不制版的图层中标出。

1.10.2版图上应设计一个十字对位标记,用于孔化基片光刻对位,如下图所示。

版图设计规则

精选课件

14

设计规则举例

Metal相关的设计规则列表

编号 描 述 尺 寸

5a 金属宽度 2.5

5b 金属间距 2.0

目的与作用

保证铝线的良好 电导

防止铝条联条

精选课件

15

设计规则举例

精选课件

16

tf文件(Technology File)和display.drf文件

这两个文件可由厂家提供,也可由设计人员根 据design rule自已编写。

• 版图的设计有特定的规则,规则是集成

电路制造厂家根据自已的工艺特点而制定

的。因此,不同的工艺就有不同的设计规

则。设计者只有得到了厂家提供的规则以

后,才能开始设计。

精选课件

7

设计规则(design rule)

两种规则: (a) 以λ(lamda)为单位的设计规则—相对单位 (b) 以μm(micron)为单位的设计规则—绝对单位 如果一种工艺的特征尺寸为S μm,则λ=S/2 μm, 选用λ为单位的设计规则主要与MOS工艺的成比例 缩小有关。

设计规则主要包括各层的最小宽度、层与层之 间的最小间距、最小交叠等。ห้องสมุดไป่ตู้

精选课件

8

设计规则(design rule)

1、最小宽度(minWidth) 最小宽度指封闭几何图形的内边之间的距离

在利用DRC(设计规则检查)对版图进行几何规则检查时,对于宽度低 于规则中指定的最小宽度的几何图形,计算机将给出错误提示。

原始层

poly

diff

精选课件

23

Layer Processing(层处理命令)

•Relational Commands (关系命令)

版图设计规则分析

设计规则(design rule)

2、最小间距(minSep) 间距指各几何图形外边界之间的距离。

TSMC_0.35μm CMOS工艺版图 各层图形之间的最小间距

设计规则

3、最小交叠(minOverlap) 交叠有两种形式: a)一几何图形内边界到另一图形的内边界长度(overlap), 如图 (a) b)一几何图形外边界到另一图形的内边界长度(extension), 如图 (b)

版图设计规则

版图概述

定义:版图(Layout)是集成电路设计者将设计 并模拟优化后的电路转化成的一系列几何图形, 包含了集成电路尺寸、各层拓扑定义等器件相 关的物理信息数据。 集成电路制造厂家根据这些数据来制造掩膜。 掩膜上的图形决定着芯片上器件或连接物理层 的尺寸。因此版图上的几何图形尺寸与芯片上 物理层的尺寸直接相关。

举例:

gate = geomAnd( GT TO ) connect = geomAndNot( GT TO ) drc( connect TO ( sep < 2.0) " Field Poly to Active spacing < 2.0") drc( gate TO (sep < 1.5) " Active Poly to Active spacing < 1.5")

drc(GT TO (enc<2) "Poly Overhang out of Active into Field<2.0")

DRC规则文件

geomAnd()把括号内层次“与”之后再 赋给前面的新层次。 geomAndNot()是把括号内层次“与非” 之后再赋给前面的新层次。

版图设计基础

• 交叠规则

• 两层之间交叠的最小尺寸。交叠规则定义 的两层为不同的层。

• 两层交叠,并且一层要伸出另一层的最小 尺寸

• 两层交叠,两层之间的最小尺寸

设计规则举例 • N阱层相关的设计规则及其示意图

• P+、N+有源区层相关的设计规则及其示意图

• Poly层相关的设计规则及其示意图

• Contact层相关的设计规则及其示意图

• Metal层相关的设计规则及其示意图

• Pad层相关的设计规则及其示意图

二、几何设计规则 -举例及问题讨论

当给定电路原理图设计其版图时,必须根据 所用的工艺设计规则,时刻注意版图同一层上 以及不同层间的图形大小及相对位置关系。然 而对于版图设计初学者来说,第一次设计就能 全面考虑各种设计规则是不可能的。为此,需 要借助版图设计工具的在线设计规则检查 (DRC)功能来及时发现存在的问题。

为了工艺上按比例缩小或版图编辑的需要, 合并接触采用图4.9(a)所示的分离式接触结 构,而不采用图4.9(b)的合并长孔结构。

版图的验证

• 版图设计完成后,还需要进行一系列的检 查和验证。

• 版图的验证包括:设计规则检查(DRC)、 电学规则检查(ERC)、版图参数提取以 及电路图与版图一致性检查(LVS)

• CIF格式 用文本命令来表示掩膜分层和版图图形,通过对 基本图形的描述、图形定义描述、附加图样调用 功能,可以实现对版图的层次性描述。采用字符 格式,可读性较强

EDIF格式 是电路的一种二进制描述,带有电路的单元符号 (symbol)信息,也是纯文本,主要用于电路数 据交换。EDIF文件可读性强

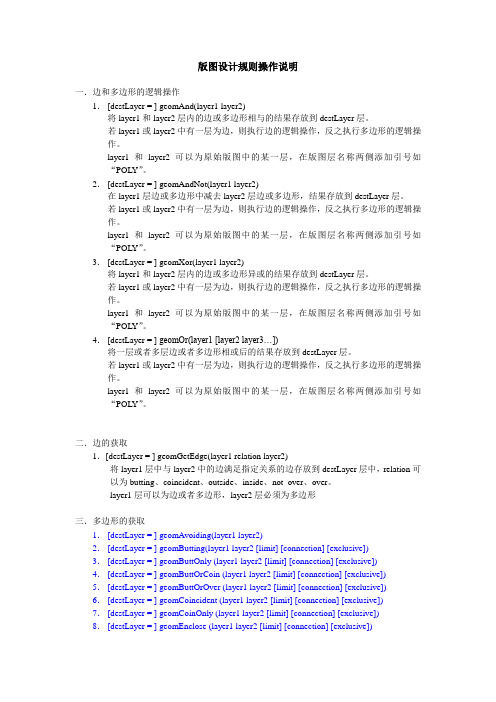

版图设计规则操作说明

版图设计规则操作说明一.边和多边形的逻辑操作1.[destLayer = ] geomAnd(layer1 layer2)将layer1和layer2层内的边或多边形相与的结果存放到destLayer层。

若layer1或layer2中有一层为边,则执行边的逻辑操作,反之执行多边形的逻辑操作。

layer1和layer2可以为原始版图中的某一层,在版图层名称两侧添加引号如“POL Y”。

2.[destLayer = ] geomAndNot(layer1 layer2)在layer1层边或多边形中减去layer2层边或多边形,结果存放到destLayer层。

若layer1或layer2中有一层为边,则执行边的逻辑操作,反之执行多边形的逻辑操作。

layer1和layer2可以为原始版图中的某一层,在版图层名称两侧添加引号如“POL Y”。

3.[destLayer = ] geomXor(layer1 layer2)将layer1和layer2层内的边或多边形异或的结果存放到destLayer层。

若layer1或layer2中有一层为边,则执行边的逻辑操作,反之执行多边形的逻辑操作。

layer1和layer2可以为原始版图中的某一层,在版图层名称两侧添加引号如“POL Y”。

4.[destLayer = ] geomOr(layer1 [layer2 layer3…])将一层或者多层边或者多边形相或后的结果存放到destLayer层。

若layer1或layer2中有一层为边,则执行边的逻辑操作,反之执行多边形的逻辑操作。

layer1和layer2可以为原始版图中的某一层,在版图层名称两侧添加引号如“POL Y”。

二.边的获取1.[destLayer = ] geomGetEdge(layer1 relation layer2)将layer1层中与layer2中的边满足指定关系的边存放到destLayer层中,relation可以为butting、coincident、outside、inside、not_over、over。

版图设计规则及验证

制定设计规则的目的:使芯片尺寸在尽可能小的 前提下,避免线条宽度的偏差和不同层版套准偏 差可能带来的问题,尽可能地提高电路制备的成 品率。

三、设计规则及工艺参数

版图设计规则的制定 考虑器件在正常工作的条件下,根据实际工艺水平(包 括光刻特性、刻蚀能力、对准容差等)和成品率要求, 给出的一组同一工艺层及不同工艺层之间几何尺寸的 限制,主要包括线宽、间距、覆盖、露头、凹口、面 积等规则,分别给出它们的最小值,以防止掩膜图形 的断裂、连接和一些不良物理效应的出现。

版图数据 命令文件 ZSE

LDC

CDL/Spice

DRC, ERC

NE LVS

Slognet

PDT

LDX

四、版图验证与检查

DRC(Design Rule Cheek):几何设计规则检查 ERC(Electrical Rule Check):电学规则检查 LVS(Layout versus Schematic):网表一致性检查

4#版为P+掺杂区图形掩膜。多晶硅栅本身作为漏, 源掺杂离子注入的掩膜(离子实际上被多晶硅栅阻 挡,不会进入栅下硅表面,称硅栅自对准工艺)。经 硼离子注入,扩散推进,完成P沟管和P型衬底欧姆 接触区的制作。

光刻4:P管源漏区注入光刻

P+注入

N- Si 阱

P-S i Sub

光刻5:N管源漏区注入光刻

N阱层相关的设计规则

编 号 1.1 1.2 1.3 描 述 尺 寸 3.0 6.0 2.5 目的与作用 保证光刻精度和器件尺寸 防止不同电位阱间干扰 保证N阱四周的场注N区环的 尺寸 减少闩锁效应

N阱最小宽度 N阱最小外间距 N阱内N阱覆盖P+

1.4

版图设计规则

ndiff

poly Original layer

Layer Processing(层处理命令)

•Logical Commands(逻辑命令)

原始层

poly

diff

Layer Processing(层处理命令)

•Relational Commands (关系命令)

利用这些原始层次的“与或非”关系可以生成 设计规则检查所需要的额外层次

drcExtractRules( bkgnd = geomBkgnd() NT = geomOr( "NT" ) TO = geomOr( "TO" ) GT = geomOr( "GT" ) W1 = geomOr( "W1" ) A1 = geomOr( "A1" )

•当technology file 创建后,用于divDaRDCR的C.r规ul则 在drcExtractRules 中定义

DRC (Design Rule Check)的命令

•DRC Function DRC函数

槽口

DRC (Design Rule Check)的命令

DRC规则文件

geomOr( )语句的目的是把括号里的层次合并起 来,也就是或的关系。

DRC规则文件

举例:

gate = geomAnd( GT TO ) connect = geomAndNot( GT TO ) drc( connect TO

( sep < 2.0) " Field Poly to Active spacing < 2.0") drc( gate TO

版图设计规则

SiO2

版图层次定义

有源区

光刻胶

光刻胶 Si3N4

Nwell

SiO2

P-type Si

SiO2

版图层次定义

有源区 封闭图形外形成LOCOS

场氧

场氧

Si3N4

PNwweellll

P-type Si

场氧 SiO2

SiO2

版图层次定义

有源区

场氧

场氧 PNwweellll

P-type Si

场氧 SiO2

实际上有源区掩膜板的意义在于作为制 造硅局部氧化(LOCOS)和薄氧(封闭图形 内形成薄氧,封闭图形外形成LOCOS)。

版图层次定义

Pwell Active Poly P+ implant N+ impant Omicontact Metal

active

有源区

Nwell

版图层次定义

有源区

生长薄氧氮化硅用于应力释放

Poly

场氧

场氧 PNwweellll

薄氧

P-type Si

场氧 SiO2

SiO2

版图层次定义

Poly

场氧

场氧

poly

PNwweellll

P-type Si

场氧 SiO2

SiO2

版图层次定义

Poly

Nwell Active Poly P+ implant N+ impant Omicontact Metal

P+/N+扩散区

场氧

光刻胶 场氧

poly

PNwweellll

场氧 SiO2

P-type Si

S/D

SiO2

版图设计知识点

版图设计知识点版图设计是指在平面设计中对于页面布局、元素排列以及配色等方面的设计。

在版图设计中,有许多重要的知识点需要注意和掌握。

本文将就版图设计的知识点进行详细论述。

一、页面尺寸与比例在版图设计中,页面尺寸与比例是首要考虑的因素之一。

根据设计需求和输出媒介的不同,选择适合的页面尺寸是非常重要的。

常见的页面尺寸包括A4、A5、网页尺寸等。

除了尺寸外,比例也需要考虑。

常见的比例有黄金比例、对称比例等,选择合适的比例可以使得版面更加平衡美观。

二、栏目设置与结构栏目设置是版图设计中的重要环节。

通过合理设置栏目,可以使得信息的展示更加清晰、有序。

在进行栏目设置时,需要考虑到内容的重要性、相似性以及层次关系。

常用的栏目设置有单栏、双栏、多栏等,根据设计需求选择合适的栏目布局。

三、文字排版文字排版是版图设计中不可忽略的一环。

合理的文字排版可以提升版面的可读性和美观度。

在进行文字排版时,需要注意字体的选择与搭配、字号的调整以及字距的设置等。

同时,还需要注意段落的分隔与缩进、文字的对齐方式等,确保文字排版整齐、清晰。

四、色彩运用色彩是版图设计中的重要元素之一,能够给人带来不同的情绪和感受。

在进行色彩运用时,需要考虑到色彩的搭配、主次关系以及色彩的饱和度和明度等因素。

同时,还需要注意色彩的运用要与设计主题相符合,避免色彩过于花哨或不协调而影响整体设计效果。

五、图片与图形元素图片与图形元素在版图设计中起到了画龙点睛的作用。

通过巧妙的图片与图形元素的运用,可以提升版面的视觉效果和吸引力。

在选择图片与图形元素时,需要注意其与设计主题的契合度,避免过多或不相关的图片与图形元素的使用。

同时,还需要注意图片的清晰度以及图形元素的简洁性和美观性。

六、空白与留白空白与留白是版图设计中的重要设计元素之一。

合理的运用空白与留白可以使版面更加清爽、简洁。

空白的选择需要考虑到信息的紧凑性与层次关系,留白的运用则需要考虑到版面的平衡性与美感。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

举例:工艺结构 ?TSMC 0.35umCMOS 工艺定义的全部工艺层

举例:工艺结构

?0.18um 工艺结构

MIM:metal-insulator-metal

HDP:high-density plasma

厚的顶层金属:信号线,减少了寄 生电容和电阻干扰

? Feature size L=0.18um

? 版图的设计有特定的规则,规则是集成 电路制造厂家根据自已的工艺特点而制定 的。因此,不同的工艺就有不同的设计规 则。设计者只有得到了厂家提供的规则以 后,才能开始设计。

设计规则(design rule)

? 两种规则: (a) 以λ (lamda) 为单位的设计规则— 相对单位 (b) 以μ m(micron) 为单位的设计规则— 绝对单位 如果一种工艺的特征尺寸为 S μ m,则λ =S/2 μ m, 选用λ 为单位的设计规则主要与 MOS工艺的成比例 缩小有关。

版图设计规则

版图概述

? 定义:版图 (Layout)是集成电路设计者将设计 并模拟优化后的电路转化成的一系列几何图形, 包含了集成电路尺寸、各层拓扑定义等器件相 关的物理信息数据。

? 集成电路制造厂家根据这些数据来制造掩膜。 ? 掩膜上的图形决定着芯片上器件或连接物理层

的尺寸。因此 版图上的几何图形尺寸与芯片上 物理层的尺寸直接相关 。

顶点 octagon

图形

Layer Processing(层处理命令)

?Selection Command(s 选择命令)

gate = geomAnd(poly diff) sd = geomAndNot(diff poly)

Layer Processing(层处理命令)

?Selection Command(s 选择命令)

? 设计规则主要包括各层的最小宽度、层与层之 间的最小间距、最小交叠等。

设计规则(design rule)

? 1、最小宽度 (minWidth) 最小宽度指封闭几何图形的 内边之间的距离

在利用DRC(设计规则检查)对版图进行几何规则检查时,对于宽度低 于规则中指定的最小宽度的几何图形,计算机将给出错误提示。

(NM?OMS/1P-MM防5O止(S7穿8 m通O注h入m/)sq) ThickVTN/VtPopN-m=eNta/l P(1C8hmaOnnheml /Tshq)reshold Voltage Adjust (NMO阈S值电压调 节注入)

设计规则(design rule)

? 版图几何设计规则可看作是对光刻掩模 版制备要求。光刻掩模版是用来制造集 成电路的。这些规则在生产阶段中为电 路设计师和工艺工程师提供了一种必要 的信息联系。

DRC(设计规则检查 Design Rule Check)

?层的概念

Original Layer 初始层 Derived Layer 衍(派)生层 Layer Processing 层处理 Geometry 几何图形

Layer Processing(层处理命令)

?层处理命令的类型

Layer Processing(层处理命令)

版图概述

? 设计者只能根据厂家提供的设计规则进行 版图设计。严格遵守设计规则可以极大地 避免由于短路、断路造成的电路失效和容 差以及寄生效应引起的性能劣化。

? 版图在设计的过程中要进行定期的检查, 避免错误的积累而导致难以修改。

举例:工艺ห้องสมุดไป่ตู้构

以TSMC(台积电)的0.35μm CMOS工艺为例

? TSMC的0.35μm沟道尺寸和对应的电源电压、 电路布局图中金属布线层及其性能参数

?Logical Command(s 逻辑命令)

ndiff

poly Original layer

Layer Processing(层处理命令)

?Logical Comman(ds逻辑命令)

原始层

poly

diff

Layer Processing(层处理命令)

?Relational Commands(关系命令)

设计规则(design rule)

?TSMC_0.35μm CMOS工艺中各版图层的线条最小宽度

设计规则(design rule)

? 2、最小间距 (minSep) 间距指各几何图形 外边界之间 的距离。

TSMC_0.35μm CMOS工艺版图 各层图形之间的最小间距

设计规则

? 3、最小交叠(minOverlap) 交叠有两种形式: a)一几何图形内边界到另一图形的内边界长度(overlap ),

Layer Processing(层处理命令)

?Relational Commands(关系命令)

外切

图片有错 颠倒一下

内切

Layer Processing(层处理命令)

?Sizing Command(s 尺寸命令)

把整个图形扩展

扩展边沿

线扩展

Layer Processing(层处理命令)

?Selection Command(s 选择命令)

? VDD 1.8V/2.5V

? Deep NWELL to reduce substrate noise

? MIM capacitor(1fF/um^2)

? 6 Metal 1 Poly

? Polycideresistor(7.5 Ohm/sq) NAP?T/HPiAgPhTN=/PNim/PplaCnhtarnensiesltoArn(-5t9i PunchOthhrmou/sgqh, 133 Ohm/sq)

如图 (a) b)一几何图形外边界到另一图形的内边界长度(extension) ,

如图 (b)

TSMC_0.35μm CMOS 工艺版图 各层图形之间最小交叠

设计规则举例

? Metal相关的设计规则列表

编号 描 述

尺

寸

5a 金属宽度 2.5

5b 金属间距 2.0

目的与作用

保证铝线的良好 电导

防止铝条联条

设计规则举例

tf文件(Technology File) 和display.drf文件

? 这两个文件可由厂家提供,也可由设计人员根 据design rule自已编写。

? tf文件规定了版图的层次、各层次的表示方式、 设计规则。

? display.drf 是一个显示文件,规定显示的颜色。

Tf & display