版图设计规则(最新版).ppt

第三讲+版图设计规则+

• 有源区最小间距10um Active to Active Spacing =10um

13

版图设计规则的应用

•多晶硅条最小宽度5 um Poly minum width =5 um

• 多晶硅条最小间距5 um poly to poly spacing=5 um

• 离子注入区对有源区最 小覆盖10 um

16

要了解采用的管壳和压焊工艺。封装形式 可分为金属圆筒塑(TO-5型)、扁平封装型和双 列直插型(DIP)等多种,管芯压点分布必须和管 壳外引脚排列相吻合。当采用热压焊时,压焊 点的面积只需70μm×70μm,超声压焊需 100μm×100μm ~125μm×25μm,金丝球焊 需125μm ×125μm,金丝球焊牢固程度高, 金丝在靠近硅片压点处是垂直的,可压到芯片 纵深处(但必须使用温度SiO2纯化层),使用起 来很灵活。

优点:版图设计独立于工艺和实际尺寸。

3

2. 微米设计规则

80年代中期,为适应VLSI MOS电路制造工 艺,发展了以微米为单位的绝对值表示的版图 规则。针对一些细节进行具体设计,灵活性大, 对电路性能的提高带来很大方便。

适用于有经验的设计师以及力求挖掘工艺潜 能的场合。目前一般的MOS IC研制和生产中, 基本上采用这类规则。其中每个被规定的尺寸 之间没有必然的比例关系。显然,在这种方法 所规定的规则中,对于一个设计级别,就要有 一整套数字,因而显得烦琐。但由于各尺寸可 相对独立地选择,所以可把尺寸定得合理。

28

基本逻辑门的版图设计

29

VDD

IN

OUT

VSS

30

31

32

M

VSS

M

VSS

M

VSS

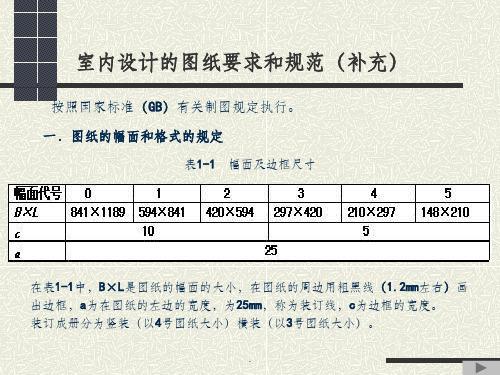

室内设计制图要求及规范ppt课件

.

.

.

.

图例线(填 充线) 标注线

线宽

0.3-0.4左右

外线0.09-0.13 内线(填充线) 0.05 0.05

0.05-0.09

名称 线宽

引出线 0.05-0.09

折断线 0.05

文本

同标注线或另设

图名下划 下细线为0.05-0.09 线

上粗线为0.4-0.6

十二.室内设计图纸内容及绘图步骤

3、根据不同的线型要求,选择相应图层绘图; 绘图顺序为:平面图、立面图、详图、效果图

➢ 设图层时先选颜色、后定线型、再设线宽 ➢ 常用线型宽值如下(见下表)

.

.

.

平面图

名称

墙线 后隔墙 图名下划 线

门、窗、 家具

电器、卫 生洁具

线宽

0.3-0.4左右 0.2左右 上粗线为0.4-0.6 下细线为0.05-0.09 外轮廓线0.09-0.13 内线(填充线) 0.05 外轮廓线0.09左右 轨迹线(填充线) 0.05

表中的b为所绘制的本张图纸上可见轮廓线设定的宽度,b=0.4-0.8mm。

.

四.剖面符号的规定

在绘制图样时,往往需要将形体进行剖切,应用相应的剖面符号 表示其断面,如图所示。

版图PPT课件

③ 蛇形,如图(c),包括29个方块,如图(d)。

多晶硅电阻的版图

2. 非矩形电阻的计算

版图设计中往往会遇到许多非矩形形状 的电阻, 如果是标准图形(平行四边形、 直角梯形、 等腰梯形), 也有相应的公 式可计算它的相对电阻。图中所示形状 的相对电阻可进行估算。

(1)矩形电阻:当L»W时,可以近似为

版图设计是制造IC的基本条件,版图设计是 否合理对成品率、电路性能、可靠性影响很大, 版图设计错了,就一个电路也做不出来。若设计 不合理,则电路性能和成品率将受到很大影响。 版图设计必须与线路设计、工艺设计、工艺水平 适应。版图设计者必须熟悉工艺条件、器件物理 、电路原理以及测试方法。

3

知识储备

作为一位版图设计者,首先要熟悉工艺条 件和器件物理,才能确定晶体管的具体尺寸。 铝连线的宽度、间距、各次掩膜套刻精度等。 其次要对电路的工作原理有一定的了解,这样 才能在版图设计中注意避免某些分布参量和寄 生效应对电路产生的影响。同时还要熟悉调试 方法,通过对样品性能的测试和显微镜观察, 可分析出工艺中的间题。也可通过工艺中的问 题发现电路设计和版图设计不合理之处,帮助 改版工作的进行。特别是测试中发现某一参数 的不合格,这往往与版图设计有关。

版图设计技术

1

1. 什么是版图?

根据逻辑与电路功能和性能要求以 及工艺水平要求来设计光刻用的掩 膜版图,实现IC设计的最终输出。

版图是一组相互套合的图形,各层 版图相应于不同的工艺步骤,每一 层版图用不同的图案来表示。 版 图与所采用的制备工艺紧密相关。

2

版图设计就是按照线路的要求和一定的工艺 参数,设计出元件的图形并进行排列互连,以设 计出一套供IC制造工艺中使用的光刻掩膜版的图 形,称为版图或工艺复合图。

版图设计规则

版图几何设计规则

版图几何设计规则可看作是对光刻掩 模版制备要求. 一般来讲,设计规则反映了性能和成 品率之间可能的最好的折衷.规则越保 守,能工作的电路就越多(即成品率越 高);然而,规则越富有进取性,则电路 性能改进的可能性也越大,这种改进可 能是以牺牲成品率为代价的.

版图几何设计规则

(1)微米规则 (2)λ规则

版图几何设计规则

大部分设计规则都可以归纳入以下描 述的四种规则之一. (1)最小宽度 (2)最小间距 (3)最小包围 (4)最小延伸

版图几何设计规则

设计规则(硅栅)举例:

0.6um 2p2m CMOS

0.6um 2p2m

版图几何设计规则-N阱

定义了P沟道器件的N阱尺寸,N型杂志注入该 区域形成N-well. N-well宽度 3.0 不同电势的N-well之间的距离-4.8 N-well中用于接触的N+与阱边沿的距离-0.4 N-well距阱外的N+的距离-4.0 N-well距阱外的P+的距离-0.4 N-well距阱内的P+的距离-1.8 距划线槽的距离8.0

版图几何设计规则-接触孔

0.6

0.6

0.4

0.6

0.7

0.4

0.6

0.4

版图几何设计规则

编号 1 2 描述 金属宽度 金属间距 尺寸 0.9 0.8 防止铝条接触 保证良好导电性

版图几何设计规则-金属1

metal1宽度:0.9 Metal1之间的距离:0.8 Metal1距接触孔的距离:0.3

版图几何设计规则-多晶硅

PMOS

NMOS

0.6

0.6

0.6

0.75

0.5

版图设计课件 PPT

一、双极集成电路工艺的基本流程

实现选择性掺杂的三道基本工序

(3)掺杂:在半导体基片的一定区域掺入一定浓度的杂质 元素,形成不同类型的半导体层,来制作各种器件。掺 杂工艺主要有两种:扩散和离子注入。

扩散:在热运动的作用下,物质的微粒都有一种从高浓 度的地方向低浓度的地方运动的趋势。在IC生产中,扩 散的同时进行氧化。

结论:对采用PN结隔离的双极IC基本工艺,与制作NPN 晶体管的基本工艺相比,只需增加外延工艺,当然工艺步 骤要增加不少。

一、双极集成电路工艺的基本流程

PN结隔离双极IC工艺基本流程

衬底材料(P型硅)- 埋层氧化-埋层光刻 -埋层掺杂(Sb)外延 (N型硅)隔离氧化-隔离光刻 -隔离掺杂(B)- 基区氧化-基区光刻 -基区掺杂(B)和发射区氧化-

一、双极集成电路工艺的基本流程

工艺类型简介

按照制造器件的结构不同可以分为: 双极型:由电子和空穴这两种极性的载流子作为在有源

区中运载电流的工具。 MOS型:PMOS工艺、NMOS工艺、CMOS工艺 BiCMOS集成电路:双极与MOS混合集成电路

按照MOS的栅电极的不同可以分为: 铝栅工艺、硅栅工艺(CMOS制造中的主流工艺)

(2) 光刻2:场氧光刻,又称为有源区光刻。将以后作为有源区区域的 氧(3化) 氧层化和氮层化生硅长层。保在留没,有其氮余化区硅域层的保氧护化的层区和氮化硅全部去除。 域(即场区)生长一层较厚的氧化层。图中 表面没有氧化层的区域即为有源区。

三、CMOS集成电路工艺流程

3. 生长栅氧化层和生成多晶硅栅电极 确定了有源区以后,就可以制作MOS晶体管。首先按下述步骤生长栅 氧化层和制作栅电极。 (1) 生长栅氧化层。去除掉有源区上的氮化硅层及薄氧化层以后,生长 一层作为栅氧化层的高质量薄氧化层。 (2) 在栅氧化层上再淀积一层作为栅电极材料的多晶硅。 (3) 光刻3:光刻多晶硅,只保留作栅电极以及起互连作用的多晶硅。 光刻后的剖面图如图所示。

版图设计规范

LCD外形及版图绘制规范文件编号:版号: 01 总页数: 15 页拟制:审核:会签:批准:生效日期:文件名称:LCD外形及版图绘制规范文件编号:版号:01 文件类型:检验标准总页数:15更改页状态更改日期更改内容申请人审批人页次 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17版次 A A A A A A B A A A A A A A A A A1.主题内容与适用范围本标准规定了液晶显示器外形图和版图绘制的基本要求,适用于句容骏科电子科技有限公司STN液晶显示器件外形图和版图设计。

2.引用标准GB4457〃1-5─1987机械制图—图纸幅面及格式、比例、字体、图线、剖面符号 GB4458〃4-1984尺寸标注法GB6250-1986 液晶显示器件名词术语3.绘制内容3.1外形绘制3.1.1基本原则3.1.1.1目的外形绘制的目的在满足本标准对关键尺寸、公差及走线逻辑有关要求的基础上,按照客户对外形尺寸、内部图形形状及尺寸等项目要求,绘制出外形图纸及逻辑表(或逻辑走线)。

3.1.1.2视图法:采用第三视图法,即主视图、右视图、仰视图。

3.1.1.3单位一般采用毫米(mm)为单位。

当客户原始资料以英制为单位时,采用公制毫米(mm)为单位绘制,器件外形图尺寸、视区尺寸在尺寸标注时可附注英制尺寸。

3.1.1.4比例:按1:1比例绘制,图纸以归一化(F/T)方式,即有效图界充满图纸方式输出。

3.1.2单片器件外形尺寸标准 : 各尺寸( 见附图)定义如下 :代码定义代码定义L1 宽片长度W1 宽片宽度L2 窄片长度W2 窄片宽度L3 偏光片长度W3 偏光片宽度L4 显示区长度W4 显示区宽度L5 图形区长度W5 图形区宽度L6 封口长度W6 封口宽度L7 可视区距玻璃边的长度W7 台阶宽度L8 点阵区距玻璃边的长度W8 可视区距玻璃边宽度L9 电极中心距玻璃边的长度W9 点阵区距玻璃边的宽度L10 偏光片距玻璃边的长度W10 偏光片距玻璃边的宽度H1 单片玻璃的厚度W11 封口定位H2 显示屏整体的厚度P1 单个电极宽度R 显示区圆角半径P2 电极的PITCH值P3 电极的整体PITCH值3.1.3外形图的层命名及颜色图层名图层代号颜色图形0 White标注 B GreenCOM走线 C YellowSEG走线S Red交点 D Magenta丝印0D Cyan3.1.4单片器件外形绘制要求如下:3.1.4.1图形精度要求如下:图案最细线宽为0.05mm,最细线隙为0.02mm,图案的对位余量为0.10mm;图形极小时,图案的对位余量可以采用最小为0.03mm的极限数值。

最新园林CAD制图规则PPT课件

——配电买材料、取电向电业局、计算电沟的工程量

1、灯的类型、规格、布置的位置标注;电缆电线的规格和联接方式;配电箱的数量和规格; 2、按照《电力设计规范》,照明用电和动力电分配用电,网格控制要严。

施工给排水绘制规则

线型、宽度及各种线型的运用

1. 粗实线:A2(0.4—0.5mm);A3(0.3—0.4mm);A4(0.25—0.3mm); 用于平、立、剖面图及详图中被剖切墙体的主要结构轮廓线;立面图的外轮廓线、剖切符号、详图符号、图面标志及标志等(地平线依次用0.6mm、0.4mm、0.3mm粗实线)。 2. 中实线:A2(0.35mm);A3(0.25mm);A4(0.25mm); 用于平、立、剖面图及详图中物体的主要结构轮廓。 3. 细实线:A2(0.20mm);A3(0.15mm);A4(0.15mm); 用于平、立、剖面图中可见的次要结构轮廓线,标注尺寸线、折断线(不需画全的断开界限)、引出线(用于对各种需要说明的部位详细说明)、图例线、索引图标、标高图标等。 4. 细虚线:A2(0.15mm);A3(0.1mm);A4(0.1mm); 结构图中不可见的部分等。 5. 点划线A2(0.15mm);A3(0.1mm);A4(0.1mm); 用于中心线、对称线、定位轴线; 6. 辅助实线A2(0.05mm);A3(0.03mm);A4(0.03mm); 用于地面填充等。

施工总平面图绘制规则

5、图例按《总图制图标准》中规定的图例进行绘制 6、图线绘制:线宽一般画:建筑、小品、水缘线、山缘线、置石等应用,正规的做法是在画图时不设定线宽,然后在出图要打印时设定。对于等高线、辅助线、填充、原有建筑和道路要采用细线。绘图过程中不能出现重复线(线宽及线形的设定)和未闭合的线条(填充); 7、总图中的坐标、标高和距离的单位以米为为宜,小数点后两位保留。详图中以毫米为单位,取小数点后三位;坡度以%表示且取到小数点后一位。 8、坐标分为测量坐标和施工坐标。测量坐标为绝对坐标(交叉十字线,用X和Y表示坐标值):施工坐标为相对坐标(相对零点或建筑物或道路的交叉点,用A或B表示),或用施工网格线(100、50、30、10、5)M。坐标标注要直接标注在图上,如果地方不够也可列表标注。

《设计图纸规范》PPT课件

横线用细实线绘制(见图八)。

• (八)剖切的表示方法: • 整体性剖切: • A沿图面上下方或左右方,进行整体性的剖切。

剖切线尽量不穿越图面上的

• 线条,当剖切线需要转折时,以一次为限; • B详图标志:在剖切图的图下方注明剖切图标及

• B封面上客户和设计师的名字必须用公司统一制定的模板打印。

• C 20页内的图纸(封面和封底除外)用拉杆夹装订,20页以上 的图

• 纸(封面和封底除外)用公司统一装订。

• D交审核的图纸须用公司统一制做的封面模板打印在A3白纸上做 封面。

•

备注:优秀级以上级别设计师,没按此规定扣5分。

精选ppt

5

的主要结构轮廓线;立面图的外轮廓线及地平线、 剖切符号、详图符号、图面标志、图名等;

• 中实线:平、立、剖面图及详图中物体的主要结构 轮廓线;

• 细实线:平、立、剖面图中可见的次要结构轮廓线, 电位图中开关与灯位的控制关系线,标注尺寸线、 折断线、引出线、图例线、索引图标、标高图标等;

• 细虚线:家具图中不可见的隔板,门窗的开启方式 及图例线等;

精选ppt

3

(一)图纸排列顺序

• 为了使设计师能够较好地向客户表达其设计意图,又使施工者有较完整的施工依 据,减少施工中变更、拆改项目,提高有效工作时间,因此要求设计师必须保证 图纸齐全,排列有序(按下列顺序排列)。

• (1)*图纸目录与工程概况 (公司统一制做的模板打印)

• (2)*装饰工程项目表

• 高度未注明的一律距地面300mm,有特殊 要求的要在插座旁注明

• 标高)。

精选ppt

11

数字电路版图设计规范及标准单元技术补充.pptx

网格式布线系统要求的库设计规则

❖ 八、天线规则 ❖ NAC二极管,是一个PN结,连接到金属,以

解决天线效应。 ❖ NAC:Net Area Check,网络节点区域控制

。

网格式布线系统要求的库设计规则

❖ 天线效应:在芯片生产过程中,暴露的金属线或者 多晶硅(polysilicon)等导体,就象是一根根天线,会 收集电荷(如等离子刻蚀产生的带电粒子)导致电 位升高。天线越长,收集的电荷也就越多,电压就 越高。若这片导体碰巧只接了MOS 的栅,那么高 电压就可能把薄栅氧化层击穿,使电路失效,这种 现象我们称之为“天线效应”。随着工艺技术的发展 ,栅的尺寸越来越小,金属的层数越来越多,发生 天线效应的可能性就越大。

内部的部件必须与单元边缘保持半个最小距 离。整个库就是根据这些约束条件建立起来 的。

网格式布线系统要求的库设计规则

网格式布线系统要求的库设计规则

❖ 七、布线通道 ❖ 隔行翻转

网格式布线系统要求的库设计规则

❖ 采用M2总线的供电回路:这种方法似的M1 层只能走电源线和最低层次的连线,如果金 属层较少,就会造成布线困难。

标准网络

❖ 沿网格布线限制了可能的布线方式,但却适 合于自动布线工具的布线。

❖ 思考:一个网格式布线器是否可以对不同的 金属层采用不同的网格尺寸?

标准网络

❖ 二、规则式布线器

❖ 在基于网格的布线系统中,由于每一层的线 宽和间距不同,而如果要保证在上下金属层 相接的时候,能够保持对准,就要以最宽那 一层的网格为基准,而显然这样会浪费布线 空间。

❖ 实现方法:让单元的边缘比内部导线的位置 多出半个网格的宽度,可以实现上述的两个 目的。

❖ 单元的上下左右四个方向都应该落在半网格 位置上。

第6章版图设计准则概论

‘Rule’ for performance

• 引言 • 设计规则(Topological Design Rule)

– 上华0.6um DPDM CMOS工艺拓扑设计规则 – 设计规则的运用

• 版图设计准则(‘Rule’ for performance)

– 匹配 – 抗干扰 – 寄生的优化 – 可靠性

除设计中的冗余逻辑,诊断设计中的 不可测逻辑结构)

版图综合 掩膜

将门级网表转化成版图 (完成布局、布线)

place & route

B. 布局、布线流程

网表输入 布图规划

布局 全局布线

详细布线 版图参数提取

LVS(Layout versus Schematic) 一致性检查

POST SIMULATION

匹配设计

• 失配:测量所得的元件值之比与设计的 元件值之比的偏差

• 归一化的失配定义:

– 设X1, X2为元件的设计值,x1, x2为其实测值, 则失配δ为:

x2

x1 X 2 X2 X1

X1

X1x2 X 2 x1

1

匹配设计

• 失配δ可视为高斯随机变量

• 若有N个测试样本δ1, δ2, …, δN,则δ的

电源线

掩蔽技术

• 掩蔽技术可以防护来自于或者去向衬底的电容耦 合。可以减小两条金属线之间的cross-talk

引言

所设计的版图:

引言

加工后得到的实际芯片版图例子:

引言

• 加工过程中的非理想因素

– 制版光刻的分辨率问题 – 多层版的套准问题 – 表面不平整问题 – 流水中的扩散和刻蚀问题 – 梯度效应

设计规则

• 设计规则的目的是 确定掩膜版的间距, 它是提高器件密度 和提高成品率的折 衷产物。

版图设计规则

精选课件

14

设计规则举例

Metal相关的设计规则列表

编号 描 述 尺 寸

5a 金属宽度 2.5

5b 金属间距 2.0

目的与作用

保证铝线的良好 电导

防止铝条联条

精选课件

15

设计规则举例

精选课件

16

tf文件(Technology File)和display.drf文件

这两个文件可由厂家提供,也可由设计人员根 据design rule自已编写。

• 版图的设计有特定的规则,规则是集成

电路制造厂家根据自已的工艺特点而制定

的。因此,不同的工艺就有不同的设计规

则。设计者只有得到了厂家提供的规则以

后,才能开始设计。

精选课件

7

设计规则(design rule)

两种规则: (a) 以λ(lamda)为单位的设计规则—相对单位 (b) 以μm(micron)为单位的设计规则—绝对单位 如果一种工艺的特征尺寸为S μm,则λ=S/2 μm, 选用λ为单位的设计规则主要与MOS工艺的成比例 缩小有关。

设计规则主要包括各层的最小宽度、层与层之 间的最小间距、最小交叠等。ห้องสมุดไป่ตู้

精选课件

8

设计规则(design rule)

1、最小宽度(minWidth) 最小宽度指封闭几何图形的内边之间的距离

在利用DRC(设计规则检查)对版图进行几何规则检查时,对于宽度低 于规则中指定的最小宽度的几何图形,计算机将给出错误提示。

原始层

poly

diff

精选课件

23

Layer Processing(层处理命令)

•Relational Commands (关系命令)

版图设计规则(最新版).ppt

设计规则(design rule)

•TSMC_0.35μm CMOS工艺中各版图层的线条最小宽 度

设计规则(design rule)

2、最小间距(minSep) 间距指各几何图形外边界之间的距离。

TSMC_0.35μm CMOS工艺版图 各层图形之间的最小间距

设计规则

3、最小交叠(minOverlap) 交叠有两种形式: a)一几何图形内边界到另一图形的内边界长度(overlap),

DRC规则文件

saveDerived 语句输出坏的接触孔图形到错 误层中。

举例: saveDerived( geomAndNot( W1 geomOr( TO GT ) ) "Contact not inside Active or Poly" ) saveDerived( geomAndNot( W1 A1 ) "Contacts not covered by Metal" ) drc( W1 width < 4.0 "Contact width < 4.0" ) drc( W1 sep < 2.0 "Contact to Contact spacing < 2.0" ) drc( TO W1 enc < 1.5 "Contact inside Active < 1.5" )

;接触孔

A1 = geomOr( "A1" )

;铝线

drc(GT TO (enc<2) "Poly Overhang out of Active into Field<2.0")

DRC规则文件

geomAnd()把括号内层次“与”之后再 赋给前面的新层次。

第二章-版图设计规则

华侨大学厦门专用集成电路系统重点实验室

华侨大学电子工程系

Copyright by Huang Weiwei

版图层次定义

N阱 P衬底

NWell

N阱和P衬底构成寄生二极管,在CMOS电路中衬 底通常接最低电平,确保二极管处于反偏。理想情况 下,从衬底流出的电流为0.

华侨大学厦门专用集成电路系统重点实验室

TO

TB PT BC

5. 低Vth NMOS沟道注入

6. 低VthPMOS沟道注入 7. 耗尽型NMOS沟道注入 8. 耗尽型PMOS沟道注入

ND

PD

华侨大学厦门专用集成电路系统重点实验室

华侨大学电子工程系

Copyright by Huang Weiwei

版图层次定义

Layout 9.纵向NPN 基区注入 10.多晶硅 11.N型源/漏 12.P型源/漏 13.ROM 14.Poly2阻挡层 15.Poly2 16.接触孔 P-base Poly1 N+ P+ ROM High Res Poly2 Contact

华侨大学厦门专用集成电路系统重点实验室

华侨大学电子工程系

有源区

有源区

有源区掩膜 栅氧 理想的LOCOS 栅氧 实际LOCOS FOX FOX

Copyright by Huang Weiwei

版图层次定义

Nwell 有源区 多晶硅1

•N阱

• 有源区(薄氧区) •多晶硅1(Poly1). • 多晶硅2(Poly2)

透光区

掩膜版 曝光区

Copyright by Huang Weiwei

版图层次定义

NWell

接着将硅片暴露在施主原子下,施主杂质会被光刻 胶阻挡住,同时也能通过光刻胶上的开孔扩散到开孔区 域的硅片中。

第6章版图设计准则ppt课件

符号 尺寸

含义

10.c 0.4 有源区,

(d, e)

Poly1, Poly2对最小孔最小覆盖

10.c.3 0.8 有源区对butting contact最小覆盖

10.f 0.6 漏源区接触孔与栅最小间距

10.g 0.6 Poly1,2上孔与有源区最小间距

dg

c

af

a

b

a.1 e

.

c.3

g

设计规则 metal1

8.c 0.6 注入区对有源区最小包围

8.d 0.6 注入区与有源区最小间距

H

c d N+

E

f

.

设计规则 implant

符号 尺寸

含义

8.E 0.75 N+(P+)注入区与P+(N+)栅 间距

8.f 0.75 N+(P+)注入区与N+(P+)栅 间距

8.H 0 注入区对有源区最小覆盖 (定义butting contact)

4.f 0.5 硅栅与有源区最小内间距

4.g 0.3 场区poly1与有源区最小内 间距

e

e

N+

f

b

g

c

P+

f

b

g

a

d

b

.

设计规则 High Resistor

在Poly2上定义高阻区

符号 尺寸

含义

5.a 2.0 高阻最小宽度

5.b 1.0 高阻最小间距

5.c 1.0 高阻对poly2的最小覆盖

5.d 1.0 高阻与poly2的间距

.

引言

• 解决办法 • 厂家提供的设计规则(topological design rule),

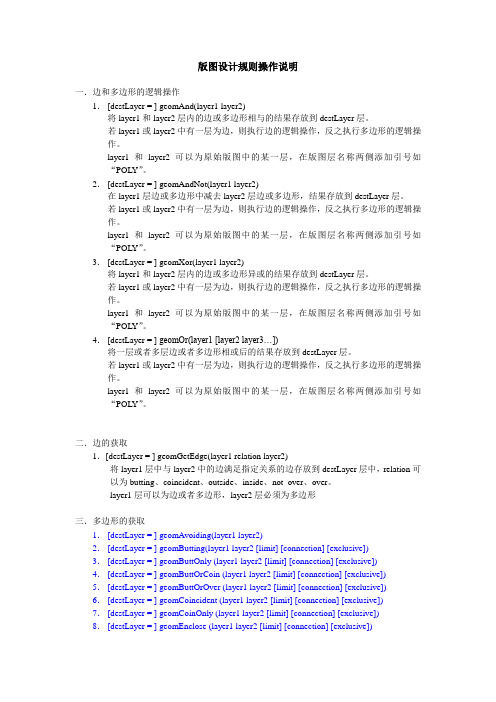

版图设计规则操作说明

版图设计规则操作说明一.边和多边形的逻辑操作1.[destLayer = ] geomAnd(layer1 layer2)将layer1和layer2层内的边或多边形相与的结果存放到destLayer层。

若layer1或layer2中有一层为边,则执行边的逻辑操作,反之执行多边形的逻辑操作。

layer1和layer2可以为原始版图中的某一层,在版图层名称两侧添加引号如“POL Y”。

2.[destLayer = ] geomAndNot(layer1 layer2)在layer1层边或多边形中减去layer2层边或多边形,结果存放到destLayer层。

若layer1或layer2中有一层为边,则执行边的逻辑操作,反之执行多边形的逻辑操作。

layer1和layer2可以为原始版图中的某一层,在版图层名称两侧添加引号如“POL Y”。

3.[destLayer = ] geomXor(layer1 layer2)将layer1和layer2层内的边或多边形异或的结果存放到destLayer层。

若layer1或layer2中有一层为边,则执行边的逻辑操作,反之执行多边形的逻辑操作。

layer1和layer2可以为原始版图中的某一层,在版图层名称两侧添加引号如“POL Y”。

4.[destLayer = ] geomOr(layer1 [layer2 layer3…])将一层或者多层边或者多边形相或后的结果存放到destLayer层。

若layer1或layer2中有一层为边,则执行边的逻辑操作,反之执行多边形的逻辑操作。

layer1和layer2可以为原始版图中的某一层,在版图层名称两侧添加引号如“POL Y”。

二.边的获取1.[destLayer = ] geomGetEdge(layer1 relation layer2)将layer1层中与layer2中的边满足指定关系的边存放到destLayer层中,relation可以为butting、coincident、outside、inside、not_over、over。

版图设计规则

ndiff

poly Original layer

Layer Processing(层处理命令)

•Logical Commands(逻辑命令)

原始层

poly

diff

Layer Processing(层处理命令)

•Relational Commands (关系命令)

利用这些原始层次的“与或非”关系可以生成 设计规则检查所需要的额外层次

drcExtractRules( bkgnd = geomBkgnd() NT = geomOr( "NT" ) TO = geomOr( "TO" ) GT = geomOr( "GT" ) W1 = geomOr( "W1" ) A1 = geomOr( "A1" )

•当technology file 创建后,用于divDaRDCR的C.r规ul则 在drcExtractRules 中定义

DRC (Design Rule Check)的命令

•DRC Function DRC函数

槽口

DRC (Design Rule Check)的命令

DRC规则文件

geomOr( )语句的目的是把括号里的层次合并起 来,也就是或的关系。

DRC规则文件

举例:

gate = geomAnd( GT TO ) connect = geomAndNot( GT TO ) drc( connect TO

( sep < 2.0) " Field Poly to Active spacing < 2.0") drc( gate TO

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

版图概述

设计者只能根据厂家提供的设计规则进行 版图设计。严格遵守设计规则可以极大地 避免由于短路、断路造成的电路失效和容 差以及寄生效应引起的性能劣化。

版图在设计的过程中要进行定期的检查, 避免错误的积累而导致难以修改。

举例:工艺结构

以TSMC(台积电)的0.35μm CMOS工艺为例

TSMC的0.35μm沟道尺寸和对应的电源电压、 电路布局图中金属布线层及其性能参数

顶点 octagon

图形

Layer Processing(层处理命令)

•Selection Commands(选择命令)

gate = geomAnd(poly diff) sd = geomAndNot(diff poly)

Layer Processing(层处理命令)

•Selection Commands(选择命令)

如图 (a) b)一几何图形外边界到另一图形的内边界长度(extension),

如图 (b)

TSMC_0.35μm CMOS工艺版图 各层图形之间最小交叠

设计规则举例

Metal相关的设计规则列表

编号 描 述 尺 寸

5a 金属宽度 2.5

5b 金属间距 2.0

目的与作用

保证铝线的良好 电导

防止铝条联条

设计规则(design rule)

•TSMC_0.35μm CMOS工艺中各版图层的线条最小宽 度

设计规则(design rule)

2、最小间距(minSep) 间距指各几何图形外边界之间的距离。

TSMC_0.35μm CMOS工艺版图 各层图形之间的最小间距

设计规则

3、最小交叠(minOverlap) 交叠有两种形式: a)一几何图形内边界到另一图形的内边界长度(overlap),

电阻

相邻的

邻近的

Layer Processing(层处理命令)

•Selection Commands(选择命令)

举例:工艺结构 •TSMC 0.35umCMOS工艺定义的全部工艺层

举例:工艺结构

•0.18um 工艺结构

Feature size L=0.18um VDD 1.8V/2.5V Deep NWELL to reduce

substrate noise MIM capacitor(1fF/um^2) 6 Metal 1 Poly Polycideresistor(7.5 Ohm/sq) NAPT/HPigAhPTN/=P Nim/pPlaCnhtarnesniesltor(59 Anti-OPhumnc/shqth, 1ro33ugOhhm/sq) (NM OMS/1P-MM5O(7S8防m止O穿h通m/注sq入) T)hickVTN/VtoPpN-m=eNta/l P(1C8hmaOnhnmel/sq) Threshold Voltage Adjust (NMOS阈值电压调节注入)

设计规则主要包括各层的最小宽度、层与层之 间的最小间距、最小交叠等。

设计规则(design rule)

1、最小宽度(minWidth) 最小宽度指封闭几何图形的内边之间的距离

在利用DRC(设计规则检查)对版图进行几何规则检查时,对于宽度低 于规则中指定的最小宽度的几何图形,计算机将给出错误提示。

DRC(设计规则检查 Design Rule Check)

•层的概念

Original Layer 初始层 Derived Layer 衍(派)生层 Layer Processing 层处理 Geometry 几何图形

Layer Processing(层处理命令)

•层处理命令的类型

Layer Processing(层处理命令)

版图设计规则

版图概述

定义:版图(Layout)是集成电路设计者将设计 并模拟优化后的电路转化成的一系列几何图形, 包含了集成电路尺寸、各层拓扑定义等器件相 关的物理信息数据。

集成电路制造厂家根据这些数据来制造掩膜。 掩膜上的图形决定着芯片上器件或连接物理层

的尺寸。因此版图上的几何图形尺寸与芯片上 物理层的尺寸直接相关。

Layer Processing(层处理命令)

•Relational Commands (关系命令)

外切

图片有错 颠倒一下

内切

Layer Processing(层处理命令)

•Sizing Commands(尺寸命令)

把整个图形扩展

扩展边沿

பைடு நூலகம்

线扩展

Layer Processing(层处理命令)

•Selection Commands(选择命令)

设计规则举例

tf文件(Technology File)和display.drf文件

这两个文件可由厂家提供,也可由设计人员根 据design rule自已编写。

tf文件规定了版图的层次、各层次的表示方式、 设计规则。

display.drf是一个显示文件,规定显示的颜色。

Tf & display

• 版图的设计有特定的规则,规则是集成 电路制造厂家根据自已的工艺特点而制定 的。因此,不同的工艺就有不同的设计规 则。设计者只有得到了厂家提供的规则以 后,才能开始设计。

设计规则(design rule)

两种规则: (a) 以λ(lamda)为单位的设计规则—相对单位 (b) 以μm(micron)为单位的设计规则—绝对单位 如果一种工艺的特征尺寸为S μm,则λ=S/2 μm, 选用λ为单位的设计规则主要与MOS工艺的成比例 缩小有关。

•Logical Commands(逻辑命令)

ndiff

poly Original layer

Layer Processing(层处理命令)

•Logical Commands(逻辑命令)

原始层

poly

diff

Layer Processing(层处理命令)

•Relational Commands (关系命令)

MIM:metal-insulator-metal

HDP:high-density plasma

厚的顶层金属:信号线,减少了寄 生电容和电阻干扰

设计规则(design rule)

版图几何设计规则可看作是对光刻掩模 版制备要求。光刻掩模版是用来制造集 成电路的。这些规则在生产阶段中为电 路设计师和工艺工程师提供了一种必要 的信息联系。