0-9999计数器程序

单片机原理应用实验指导书

《单片机原理与应用》课程实验指导书电子、机电及电气项目与自动化专业适用吴茂屈莉莉王飞编佛山科学技术学院二00 九年十月前言以往我校的单片机实验教案通常是使用启东DAIS 系列单片机微机仿真实验系统进行单片机实验教案的,DAIS 系统可以做二十多项实验,系统机构十分复杂,功能非常强大,但是在使用过程中也发现了一些不足的地方那个: 厂家为了技术保密,把核心电路都屏蔽了,我们不能了解实验系统的工作原理,另外系统庞大,不方便学生带回宿舍实验,不方便学生课外学习。

根据我校学生对单片机课程学习的需求, 我们在参考其他公司的产品的基础上,结合课程的实际情况,开发了适合学生入门学习的单片机学习板,FD-51 学习板,该学习板设置了包括LED数码管、LCD1602液晶、AD\DA转换器件等单元电路,可以做几十个单片机实验,而且本实验板我们是以配件的形式提供给学生,让学生自己焊接调试线路板。

学生不但可以学习软件编程技术,还可以学习硬件焊接及调试技术,可以更好地锻炼学生的动手操作能力。

目录系统介绍 (2)软件实验:实验一清零程序............. (4)实验二拆字程序.................... .. (5)实验三拼字程序.................... .. (5)实验四数据区传送子程序 (6)实验五查找相同数个数 (6)硬件实验:实验A 工业顺顺序控制 (7)实验B 简单IO口扩展实验 (8)实验一P1 口输出流水灯实验 (11)实验二P1 口输出交通灯实验 (11)实验三八段数码管显示实验 (12)实验四键盘实验.................. . (12)实验五遥控解码实验 ............. .. (12)实验六计数器实验..................... .. (13)实验七继电器控制实验 .................... (13)实验八定时器实验 (14)实验九单片机串行口通讯实验 (14)实验十电子时钟 (14)实验十一外部中断实验<急救车与交通灯) (15)实验十二AT24C02读写实验...... .......... . (15)实验十三93C46读写实验....... ........... (16)实验十四LCD1602字符型液晶控制显示实验 (16)实验十五LCD12864点阵型液晶控制显示实验 (17)实验十六A/D转换(数字电压表>实验 (17)实验十七D/A转换(波形发生器>实验 (18)实验十八计算机温度数据采集与处理 ............... . (19)系统介绍一、FD-51单片机学习板简介为了适应我校单片机课程教案的需要,我们在参考其他厂家学习板的基础上,再根据我校单片机课程教案大纲的要求,基于简单、使用的原则,开发了FD-51 单片机实验板。

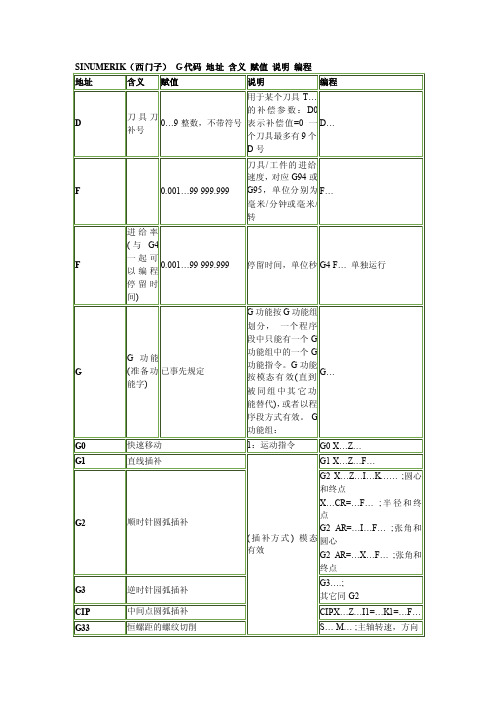

SINUMERIK西门子系统加工中心编程各代码

西门子系统,在机床没有回零点时,也可以循环起动的方法。

在启动状态下(诊断—机床设定)输入DB126 DBX4.0,B,1西门子系统,等分圆周孔,钻孔循环的另一种方法,MACLL CYCLE81(100,0,5,,20)HOLES 1 或2(0,0,126,90,360/7,7)MACLL1,是直线2,是圆周0,起始角度0,起始点Z值126,半径90,第一孔的起始角度360/7,在360度内钻7个孔7,一共要钻7个孔西门子系统按键说明:区域转换键菜单扩展键返回键加工显示键自动方式单段运行手动方式;门子系统操作面板,英—汉对照说明:JOG 手动方式窗口:PresetScratch 对刀Handwheel 手轮ICN ICN…………………Gfct+transf G功能Auxiliary func 功能表Spindles 主轴功能Axis federate 轴功能表Zoom act .val 坐标值放大Act.val MCS 机床坐标系/绝对坐标系;<<<<<<<<<<<<<<<<<<<<<<<<<<<AUTO自动方式窗口:Over-storeDRF offsetProgram control 程序控制Block searchHandwheel 手轮Correct programProgram overview…………………Gfct+transf G功能Auxiliary func 功能表Spindles 主轴功能Axis federate 轴功能表Zoom act .val 坐标值放大Act.val MCS 机床坐标系/绝对坐标系;<<<<<<<<<<<<<<<<<<<<<<<<<<<MDA 方式窗口Program control 程序控制Handwheel 手轮Editor function 编辑MDA file fct MDA程序管理…………………Gfct+transf G功能Auxiliary func 功能表Spindles 主轴功能Axis federate 轴功能表Zoom act .val 坐标值放大Act.val MCS 机床坐标系/绝对坐标系Delete MDA buffer 删除MDA缓冲区;<<<<<<<<<<<<<<<<<<<<<<<<<<<<<<<<<<<<< 按区域转换键后的窗口:Machine 机床Parameter 参数Program 程序Services 服务Diagnosis 诊断Startup 起动…………………AUTO 自动方式MDA MDA方式JOG 手动方式R.EPOSREF;<<<<<<<<<<<<<<<<<<<<<<<<<<<<<<<<<<<<< 按Parameter参数选择键后的窗口:Magazine list 刀具补偿R parameter R参数Setting data 设定数据(维修时用)Zero offset 零点偏置User data 用户数据Actire ZO+compens 坐标激活Tool manageme 刀具管理…………………Axes+ 轴+Axes- 轴-Rotation scale mirr Base ZOSet ZO;<<<<<<<<<<<<<<<<<<<<<<<<<<<<<<<<<<<<< 按Program程序选择键后的窗口:Work—pieces 工件Part programs 工件程序Sub—programs 子程序User cycles 用户循环Clip—board 剪粘板Log 记录…………………Interactiv programing 对话式编程New 新的Copy 复制Inserl 粘贴Delete 删除Rename 重命名AlterenableInteractiv programing 对话式编程New 新的Load 装载Unload 卸载Smulation 模拟Manage programs 程序管理Seleet 选择Save setup data 保存数据;<<<<<<<<<<<<<<<<<<<<<<<<<<<<<<<<<<<<< 按Services服务选择键后的窗口:Data in 数据输入Data out 数据输出Manage data 数据管理Data selection 数据选择Interface 接口…………………V24 RS232C接口PG 编程器Disk 磁盘Archive… 文档NC card NC卡;<<<<<<<<<<<<<<<<<<<<<<<<<<<<<<<<<<<<< 按Diagnosis诊断选择键后的窗口:Alarms 报警Messages 信息Alarm log 报警记录Serrice displays 服务显示Plc status LC状态…………………Display newStore logSort young—old;<<<<<<<<<<<<<<<<<<<<<<<<<<<<<<<<<<<<<按Program control程序控制,选择键后的窗口:• Skp:skip block跳过语句• Dry:dry run federate空运行• ROV:rap:trat o/ride 快速倍率• M01:program stop程序停止• DRF RF offset DRF偏差•RT: program test 程序测试SBL1: λ每一个机床切削后停止SBL2: 每一条语句后停止λSBL3: λ循环停止Display 显示Display all blocks 显示所有程序段λλ Display erav bloks anly 仅显示程序段移动;西门子系统打开两个程序窗口,可以相互复制程序段的操作步骤:新建一个文件或打开一个文件—→按“双页面键”—→打开第二个文件—→按“程序段选择键”,选中要复制的程序段—→按“复制程序段”键—→按NEXT/Window键,也就是把光标换到另一个文件下面—→按粘贴程序段键—→按“确定软键”。

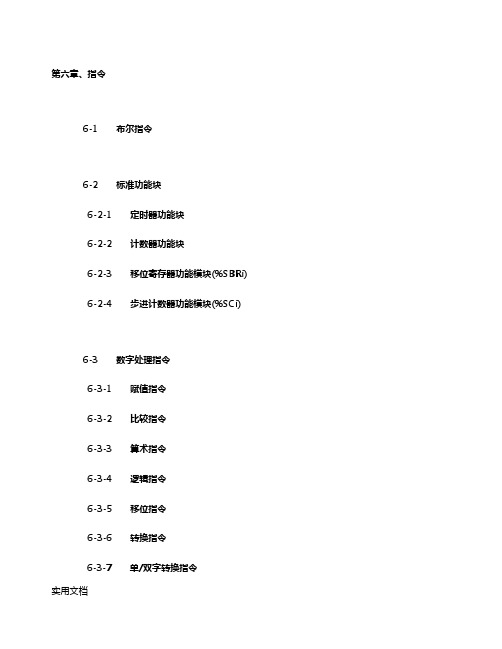

施耐德PLCTwidoPLC可编程控制器第六章、指令

第六章、指令6-1 布尔指令6-2 标准功能块6-2-1 定时器功能块6-2-2 计数器功能块6-2-3 移位寄存器功能模块(%SBRi)6-2-4 步进计数器功能模块(%SCi)6-3 数字处理指令6-3-1 赋值指令6-3-2 比较指令6-3-3 算术指令6-3-4 逻辑指令6-3-5 移位指令6-3-6 转换指令6-3-7 单/双字转换指令6-3-8 浮点算术指令6-3-9 三角指令6-3-10 转换指令6-3-11 整数转换指<-> 浮点6-3-12 表求和功能6-3-13 表比较指令6-3-14 表查找指令6-3-15 表最大值和最小值查找功能6-3-16 表中某个值的出现次数6-3-17 表循环移动功能6-3-18 表排序功能6-4 程序控制指令6-4-1 END指令6-4-2 跳转指令6-4-3 子程序指令6-5 专用功能块6-5-1 LIFO/FIFO寄存器功能模块(%Ri) 6-5-2 脉宽调制功能模块(%PWM)6-5-3 脉冲发生器输出功能模块(%PLS)6-5-4 磁鼓控制器功能模块(%DR)6-5-5 高速计数6-5-6 超高速计数器功能模块(%VFC)6-5-7 调度模块6-6 通讯指令6-6-1 信息发送/接收6-6-2 数据交换控制6-1 布尔指令掌握要点:布尔指令:用语所有位元件Load指令(装入):LD,LDN,LDR,LDF分别对应常开,常闭,上升沿,和下降沿其中: N 代表“非”R 代表“上升沿”F 代表“下降沿”程序例:逻辑AND 指令: AND, ANDN , ANDR , ANDF。

逻辑与指令执行操作数(或它的反转数,或上升沿,或下降沿)和前面指令的布尔运算结果间的逻辑与操作。

程序例:逻辑OR指令: OR , ORN , ORR , ORF,逻辑或指令执行操作数(或它的反转数,或上升沿,或下降沿)和前面指令的布尔运算结果间的逻辑或操作。

程序例:赋值指令ST, STN, S, 和R分别对应直接,反转,置位,和复位线圈,其中: N 表示输出的非S 表示强制置位R 表示强制复位程序例:异或指令(XOR, XORN, XORR, XORF)异或指令执行操作数(或它的反转数,或上升沿,或下降沿)和前面指令的布尔运算结果间的异或操作。

FANUC0I系统隐藏你的9000程序

FANUC0I....程序.........系统隐藏你的......90000I..系统..........程序.........9000~~9999........就可以隐藏你的..参数..NO3202#4..是.:.修改详细修改如下......:.口令..............)和参数......No.3210(PASSWD....No.3211(KEYWD)................功能..............可以通过参数..参数..No.3202#4(NE9)将程序锁住以保护程序.......到...........No.9000No.9999.......将不能被修改。

...........................No.9000.......在锁住状态下除非输入了正确的口令否则程序.......到.No.9999锁住状态意味着参数.....的设置值不同这些参数中的设置..................KEYWD..值与参数......的.设置.........PASSWD值不显示当.....的设置值相同时就可以解锁当参数....................参数.......KEYWD......的设置值与参数..PASSWDPASSWD...0.时.......显示为表明......没有设置......PASSWD锁住和解锁的步骤:.........锁住...方式....:. 1 .置为..MDI2 .设置参数开关为可写这时在...P/S100........报警...上显示............CNC3 .设置参数..............No.3210(PASSWD)...............这时就设定为锁住状态4 .将参数写入开关置为禁止写入.............5 .按下解除报警状态........解锁.....方式..MDI..:. 1 .置为2 .设置参数开关为可......报警...P/S100.....上显示........写这时在....CNC3 .在参数......No.3210(PASSWD)........................相同的值这时锁住状..............中设置与参数...No.3211(KEYWD)态解除...4 .将参数...0....NE9(No.3202#4)..............设置为5 .将参数写入开关置为禁止写入.............6 .按下解除报警状态........7 .程序..No.9000.......到.No.9999 .......现在就可以编辑了........详细说明....设置参数....PASSWD:.......当参数...PASSWD ......中设置非....0 .值时就设置了锁住状态然而参数.............. PASSWD ......仅在锁住状态尚未设置时当............PASSWD=0 ........或.PASSWD=KEYWD ............才可以设置如......果在其它情况下设置该参数就会出现一个不能写入的警告当设置了锁住状态后当...................................PASSWD0,........且.PASSWD KEYWD ...........参数..NE9 ...就会..自动..设置为...1 .如果在这时试图将........NE9...改.为.0 .就会出现一个不能写入的警告.............改变参数....PASSWD:.......当锁住状态解除后当.........PASSWD=0 ........或.PASSWD=KEYWD ............就可以更改.....设置状态在解锁步骤的第...........3 .步后可以在参数.......PASSWD ......中设置一个新的参数从这时起必须...............在.KEYWD .....中设置一个新值才能解除锁住状态...............锁住和解锁的步骤........在参数...PASSWD ......中设置...0:..当在参数....PASSWD ......中设置...0 .时显示数字.....0 .并且口令功能被设........为无效换句话说口令功能可以通过将................KEYWD .....中的值设为与......KEYWD .....中一样的值或者干........脆不设置....PASSWD ......来取消为了确保不进入锁住状态必须千万..................小心不要在参数.......PASSWD ......中设置非....0 .值.重新锁住....:.在锁住状态解除后可以通过在.............PASSWD ......参数中设置一个不同的值来重新设定或.................者通过关掉.....NC ..电源再打开后将.......KEYWD .....复位来设定.....警告..一旦设定了锁住状态参数...........NE9 ...就不能被设为......0 .并且参数....PASSWD<br>..........在锁住状态解除之........前或者执行清除所有内存的操作之前不能进行修改在设置.........................PASSWD ......时要千万小心......0.系统是...10.4....不相信你可以试试........。

单片机数码管动态显示1234-9999

一、实验目的1.掌握Keil软件的基本使用2.学习和掌握C语言编写程序的一般格式3.了解数码管与单片机的接口方法;4.了解数码管性能及动态显示编程方法;5.了解并掌握单片机系统中定时器中断控制的基本方法;二、实验内容用定时器中断实现四位数码管动态显示从1234-9999。

三、实验原理3.1基础知识介绍A.数码管是LED的升级,每位数码管里面继承了8个LED,点亮数码管就是点亮数码管里面的LED。

要在数码管上面显示相应的值,就是点亮不同位置的LED。

数码管有共阴和共阳两种,共阴数码管公共端是所有LED的负极连接在一起,相反共阳数码管公共端是所有LED的正极连接在一起。

一般公共端称作“位选”,控制每一个LED的称为“段选”。

数码管主要是利用视觉暂留的效果,通过快速循环点亮数码管方式,将数据呈现出来。

数码管如图1.2所示1.2数码管1.3数码管实物图/B.定时器定时器也可看作是对计算机机器周期的计数器。

因为每个机器周期包含12个振荡周期,故每一个机器周期定时器加1,可以把输入的时钟脉冲看成机器周期信号。

故其频率为晶振频率的1/12。

如果晶振频率为12MHz,则定时器每接收一个输入脉冲的时间刚好为1μs。

定时器有两种工作模式,分别为计数模式和定时模式。

对Px,y 的输入脉冲进行计数为计数模式。

定时模式,则是对MCU的主时钟经过12分频后计数。

因为主时钟是相对稳定的,所以可以通过计数值推算出计数所经过的时间。

计数器的计数值存放于特殊功能寄存器中。

T0(TL0-0x8A, TH0-0x8C), T1(TL1-0x8B, TH1-0x8D)定时器工作原理如下图由上图可见与定时器相关的寄存器主要有下面这几个:TMOD、TCON、TL0、TH0、TL1、TH1。

下面介绍一下这几个寄存器16位加法计数器:是定时计数器的核心,其中TL0、TH0、是定时计数器0的底八位和高八位;TL1、TH1是定时计数器1的底八位和高八位;并且高八位和底八位可单独使用。

欧姆龙plc指令

欧姆龙CPM1A系列PLC基本指令cpm1a系列PLC的基本逻辑指令与FX系列PLC相似,梯形图的表达方式也大致相同。

在此,列表显示了cpm1a系列PLC的基本逻辑指令(请参见表4-8)。

表4-8给出了cpm1a系列PLC的基本逻辑指令名称,指令符号功能操作号将LD读入逻辑线或电路块的第一个常开触点00000〜0191520000〜25507hr0000〜1915ar0000〜1515lr0000〜1515tim / cnt000〜127tr0〜7 * TR仅用于LD指令反向ld不读取逻辑线或电路块的第一个常闭触点常开触点与和串联常闭触点与非和非串联或与常开触点并联是否与常闭触点不平行电路块与LD串联连接,一个电路块不带LDLD或并联电路输出输出逻辑线的运算结果00000〜0191520000〜25507hr0000〜1915ar0000〜1515lr0000〜1515tim / cnt000〜127tr0〜7 * TR仅用于out指令输出取反不会反转输出逻辑线的运算结果将继电器状态设置为开重置RSET以将继电器重置为关闭Timing Tim打开延迟计时器(减法)的设置时间0〜999.9s Tim/ cnt000〜127的设置值0〜9999的计时单位为0.1s,计数单位为1次计数CNT减法计数器设置值0〜9999次欧姆龙CPM1A系列PLC功能指令功能指令也称为特殊指令。

cpm1a系列PLC提供的功能指令主要用于实现程序控制,数据处理和算术运算。

这种指令在简单的编程器上没有相应的命令键。

它仅为每条指令提供一个功能码,用两位数字表示。

输入此类指令时,请先按“ Fun”键,然后按相应的代码。

下面将介绍一些常用的功能指令。

1.无操作指令NOP(0 0 0)该指令不执行任何逻辑运算,因此称为空操作,它不使用继电器,也不需要操作号。

指令应用程序在调试程序时会在程序中保留一个地址,也可以用来微调扫描时间。

2. End指令end(01)该指令单独使用,不需要操作数。

c语言程序代码

c语言程序代码(总22页)--本页仅作为文档封面,使用时请直接删除即可----内页可以根据需求调整合适字体及大小--1.要求在屏幕上输出下一行信息。

This is a c program.程序:#include<>int main(){printf(“this is a c program.\n”);return 0;}2.求两个整数之和。

程序:#include<>int main(){int a,b,sum;a=122;b=234;sum=a+b;printf(“sum is %d\n”,sum);return 0;}3.求两个整数之间的较大者。

程序:#include<>int main(){int max(int x,int y);int a,b,c;scanf("%d,%d",&a,&b);c=max(a,b);printf("max=%d\n",c);return 0;}int max(int x,int y){int z;if(x>y)z=x;else z=y;return(z);}4.有人用温度计测量出华氏发表示的温度(如69°F),今要求把她转换成以摄氏法表示的温度(如20℃)。

公式:c=5(f-32)/9.其中f代表华氏温度,c代表摄氏温度。

程序:#include<>int main(){float f,c;f=;c=9)*(f-32);printf("f=%f\nc=%f\n",f,c);return 0;}5.计算存款利息。

有1000元,想存一年。

有一下三种方法可选:(1)活期:年利率为r1;(2)一年定期:年利率为r2;(3)存两次半年定期:年利率为r3。

分别计算一年后按三种方法所得到的本息和。

程序:#include<>int main(){float p0=1000,r1=,r2=,r3=,p1,p2,p3;p1=p0*(1+r1);p2=p0*(1+r2);p3=p0*(1+r3/2)*(1+r3/2);printf("p1=%f\np2=%f\np3=%f\n",p1,p2,p3);return 0;}6.给定一个大写字母,要求以小写字母输出。

VF设置一览表

通或断

23

9XXX PROGS EDIT LOCK

9XXX程序编辑锁定

通或断

74

9XXX PROGS TRALE

9XXX程序追踪

通或断

75

9XXX PROGS SINGLE BLK

9XXX程序单程序段

通或断

162

DEFAULT TO FLOAT

漂移预设

OFF/ON

GRPHICS(图形)

3

3D GRAPHICS

G51缺省比列尺

1至8380.000

72

DEFAULT G68 ROTATION

G68缺省旋转

0至360.0000

73

G68 INCREMENTAL ANGLE

G68增量角度

通或断

P

30

4TH AXIS ENABLE

可使用第四轴

OFF

34

4TH AXIS DIAMETER

第四轴直径

0至9.9999寸

MIRROR IMAGE B AXIS

B轴镜像

通或断

130

TAP RETRACT SPEED

攻丝退回速度

4

PROGRAM 3 (程序3 )

RS—232 PORTS(RS—232接口)

11

BAUD RATE SELECT

波特率选定

4800

12

PARTY SELECT

奇偶选择

NONE(无)ODD(奇)EVEN(偶)ZERO(零)

TOOL RELEASE LOCK OUT

刀具释放闭锁

通或断

16

DRY RUN LOCK OUT

空运转闭锁

通或断

凯恩帝数控 K1000 系列数控系统 PLC 说明书

K1000系列数控系统PLC用户手册012B-T00N-0201 KND LTD. 2008严禁以任何形式复制本书内容如有改动恕不另行通知。

本书尽可能做到通俗易懂,受篇幅限制,仍可能会有超出本书所描述的情况。

所有书中未描述到的情况均理解为不可使用或在北京凯恩帝公司指导下使用。

目录K1000系列数控系统 (I)第一篇 PLC编程 (I)1.概述 (1)2.系统组成 (1)3.技术指标 (2)3.1 K1000PLC的技术指标 (2)3.2 PLC定义地址 (3)4.顺序程序的制作 (3)4.1 PLC的选择(步骤1~3) (5)4.2 接口技术要求的形式(步骤4) (5)4.3 梯形图(步骤5) (5)4.4 指令编码(步骤6) (5)4.5 顺序程序的录入(步骤7~10) (5)4.6 顺序程序的调试(步骤11~15) (7)4.7 开发系统和维修资料(步骤16~19) (9)5.输入和输出信号 (12)5.1 输入信号 (12)5.2 输出信号 (13)6.系统输入输出接口 (15)7.K1000PLC的控制方法 (16)7.1 顺序工作 (16)7.2 连续工作 (16)7.3 高级顺序和低级顺序 (17)7.4 输入信号的同步处理 (19)7.5 互锁 (20)7.6 顺序程序处理时间 (20)7.7 顺序程序存储 (22)8.地址表 (23)8.1 与CNC连接信号的地址表 (24)8.2 机床信号地址 (24)8.3 控制继电器地址 (24)8.4定时器地址 (24)8.5 计数器、保护继电器和参数的地址表 (25)8.6 数据表的地址 (25)8.7 PLC内部特殊标志 (25)9.PLC指令 (26)9.1 基本指令 (28)9.2 功能指令 (41)10.固定存储器 (157)10.1 用法 (157)10.2 固定存储器的地址 (157)10.3 写入固定存储器 (158)10.4 固定存储器控制(MWRTF) (158)I11.1梯形图内容 (160)11.2 输入/输出信号、继电器等信号名称和代码 (160)11.3 其它 (162)第二篇 PLC开发环境 (163)1.概述 (165)1.1 KNDPLC总体说明 (165)1.2 信号名称定义 (166)2.菜单命令 (167)2.1 主界面简介 (167)2.2菜单栏 (168)3.工具栏 (190)3.1 视图管理工具条 (190)3.2 调试工具条 (190)3.3 连接CNC工具条 (191)3.4 通用工具条 (191)3.5 梯图编辑工具条 (192)3.6 状态栏 (192)4.界面操作 (193)4.1 梯图编辑快捷工具 (193)4.2 操作对象 (194)4.3 操作方法 (194)4.4 工程管理 (206)4.5 信号名称管理 (217)4.6 参数管理 (223)4.7 功能模块管理 (227)4.8 打印和打印预览 (236)4.9 多语言支持功能 (242)5.联机功能 (244)5.1 联机设置 (244)5.2 调试运行 (250)5.3 断点功能 (253)5.4 调试观察档 (255)5.5 运行实时信息 (256)6.辅助功能 (257)6.1 系统参数设置 (257)6.2 实用小技巧 (258)6.3 其它右键菜单 (259)6.4 对象信息提示功能 (261)6.5 快速定位梯级 (262)6.6 严格地址参数检查 (262)6.7 用户自定义快捷键 (263)6.8 版本兼容性 (264)6.9 快捷键汇总 (267)第三篇远程I/O模块 (269)II1.2 外形结构与安装尺寸 (271)2.设置说明 (272)2.1 模块ID号的设置 (272)2.2 系统参数设置 (272)2.3 数字DI/DO模块的参数位置 (273)3.外部连接 (274)3.1 外部连接框图 (274)3.2 电源接口的连接 (274)3.3 CAN接口的连接 (274)3.4 数字DI/DO接口的连接 (275)3.5 模拟输入/输出接口的连接 (277)3.6 RS422接口的连接 (278)5.CAN总线连接及CAN终端使用说明 (283)第四篇附录篇 (284)附录1:K1000T接口地址定义 (285)1.1 K1000T输入信号表(X区) (285)1.2 K1000T输出信号表(Y区) (289)1.3 K1000T系统PLC到NC的地址(G区) (291)1.4 K1000T系统NC到PLC的地址(F区) (297)附录2:K1000M接口地址定义 (310)2.1 K1000M输入信号表(X区) (310)附录3:K1000M4接口地址定义 (334)3.1 K1000M4输入信号表(X区) (334)3.2 K1000M4输出信号表(Y区) (336)3.3 K1000M4的PLC到NC的地址(G区) (337)附录4:K1000M5~8轴系统接口地址定义 (345)4.1 K1000M5~8输入信号表(X区) (345)附录5:PLC开发流程 (369)5.1 开发流程概述 (369)5.2 流程详细说明 (370)版权声明 (377)III第一篇PLC编程第I 篇 PLC 编程 1-概述11.概述在CNC 数控机床系统中,可编程控制器(PLC )介于机床和CNC 之间,用以控制主轴、刀架、刀具自动转换装置等等。

FANUC常用文字码及其含义

表4.3 常用文字码及其含义————【G2/G3 :圆弧插补指令】刀具从现处位置沿圆弧轨迹移动至圆弧终点。

移动的速度由进给速度F指令指定。

编程格式:XY平面圆弧:G2或G3 X — Y— R — F—X — Y—:为圆弧的终点位置坐标。

R—:圆弧的半径。

F—:为刀具移动的速度,即切削进给速度。

G2 —:顺时针圆弧插补。

G3 —:逆时针圆弧插补。

G2/G3 :圆弧插补指令应用将执行动作:刀具从现处位置C点沿CD之间的圆弧轨迹移移动至圆弧终点D。

CD段圆弧是一段顺时针圆弧轨迹,所以用G2指令。

加工程序:绝对坐标编程:N80 G90 G2 X63.0 Y20.0 R23.0相对坐标编程:N80 G91 G2 X23.0 Y-23.0 R23.0 F100平面的选择:数控系统一般可以加工XY、XZ、YZ平面的圆弧。

G17:该指令表示选择XY平面,在此平面中进行圆弧插补和刀具补偿。

此代码为系统初始代码。

电源一接通G17 就作为平面选择的起始代码而自动生效。

G18:该指令表示选择XZ平面,在此平面中进行圆弧插补和刀具补偿。

G19:该指令表示选择YZ平面,在此平面中进行圆弧插补和刀具补偿。

选择性单节删除:”/”在单节的最前端加一斜线"/"(选择性单节删除指令)时,该单节是否被执行,是由执行操作面板上的选择性单节删除开关来决定。

当此开关处于"ON"(灯亮),则该单节会被忽略而不被执行;当此开关处于"OFF" (灯熄),则该单节会被执行。

所以程序中有"/"指令之单节可由操作者视情况选择该单节是否被执行。

例子:N1;=>粗铣外形:/M00;N2;=>粗铣凹槽:/M00;N3;=>精铣外形:/M00;N4;=>精铣凹槽以上例子,当单节删除开关处于"ON"时,则所有的M00(程序停止指令)皆不被执行。

EDA实验报告-cnt9999

EDA实验报告CNT9999计数器的设计指导老师:***班级:电技1503学号:***********姓名:***交通工程学院2017.10.15实验一0~9999的计数器电路的设计1.实验目的(1)进一步熟悉和掌握Quartus II软件的使用。

(2)进一步熟悉和掌握GW48-CK或其他EDA实验开发系统的使用。

(3)学习和掌握VHDL进程语句和元件例化语句的使用。

2.实验内容设计并调试好一个计数范围为0~9999的4位十进制计数器电路CNT9999,并用GW48-CK或其他EDA实验开发系统进行硬件验证。

3实验条件(1)开发软件:Quartus II 13.0。

(2)实验设备:GW48-CK EDA 实验开发系统。

(3)拟用芯片:EP3C55F484C7。

4.实验设计1)系统原理框图为了简化设计并便于显示,本计数器电路CNT9999的设计分为两个层次,其中底层电路包括四个十进制计数器模块CNT10,再由这四个模块按照图1.1所示的原理图构成顶层电路CNT9999.图1.1 CNT9999电路原理图2)VHDL程序计数器CNT9999的底层和顶层电路均采用VHDL文本输入,有关VHDL程序如下。

CNT10的VHDL源程序:--CNT10.VHDLIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY CNT10 ISPORT(CLK:IN STD_LOGIC;CLR:IN STD_LOGIC;ENA: IN STD_LOGIC;CQ:OUT STD_LOGIC_VECTOR(3 DOWNTO 0);CO: OUT STD_LOGIC );END ENTITY CNT10;ARCHITECTURE ART OF CNT10 ISSIGNAL CQI:STD_LOGIC_VECTOR(3 DOWNTO 0);BEGINPROCESS(CLK,CLR,ENA) ISBEGINIF CLR='1' THEN CQI<="0000";ELSIF CLK'EVENT AND CLK='1' THENIF ENA='1' THENIF CQI="1001" THEN CQI<="0000";ELSE CQI<=CQI+'1';END IF;END IF;END IF;END PROCESS;PROCESS(CQI) ISBEGINIF CLK'EVENT AND CLK='1' THENIF CQI<"1001" THEN CO<='0';ELSE CO<='1';END IF;END IF;END PROCESS;CQ<=CQI;END ARCHITECTURE ART;CNT9999的VHDL源程序:LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;--使用IEEE.STD_LOGIC_1164程序包PORT(CLR: IN STD_LOGIC;CLK: IN STD_LOGIC;CLK2:IN STD_LOGIC;ENA: IN STD_LOGIC;COM: OUT STD_LOGIC_VECTOR(7 DOWNTO 0);SEG: OUT STD_LOGIC_VECTOR(7 DOWNTO 0));END ENTITY DCNT9999;ARCHITECTURE ART OF DCNT9999 ISCOMPONENT CNT10 IS --CNT10元件定义语句PORT(CLK, CLR, ENA: IN STD_LOGIC;CQ: OUT STD_LOGIC_VECTOR(3 DOWNTO 0);CO: OUT STD_LOGIC);END COMPONENT CNT10;COMPONENT CTRLS IS --元件定义语句PORT(CLK: IN STD_LOGIC;--端口说明语句(端口名:端口模式数据类型)SEL: OUT STD_LOGIC_VECTOR(2 DOWNTO 0));END COMPONENT CTRLS;COMPONENT DISPLAY IS --元件定义语句PORT(SEL: IN STD_LOGIC_VECTOR(2 DOWNTO 0);DATAIN: IN STD_LOGIC_VECTOR(15 DOWNTO 0);COM: OUT STD_LOGIC_VECTOR(7 DOWNTO 0);SEG: OUT STD_LOGIC_VECTOR(7 DOWNTO 0));END COMPONENT DISPLAY;SIGNAL S0,S1,S2: STD_LOGIC; --信号的定义,定义了3个标准位的单值信号SIGNAL SEL: STD_LOGIC_VECTOR(2 DOWNTO 0);--定义1个标准位矢量的位矢量信号SEL,含有3个元素SIGNAL DOUT:STD_LOGIC_VECTOR(15 DOWNTO 0);--定义1个标准位矢量的位矢量信号DOUT,有16个数组元素BEGINU0: CNT10 PORT MAP(CLK,CLR, ENA, DOUT(3 DOWNTO 0), S0); --元件例化语句,位置关联的方式U1: CNT10 PORT MAP(S0, CLR, ENA, DOUT(7 DOWNTO 4), S1);U2: CNT10 PORT MAP(S1, CLR, ENA, DOUT(11 DOWNTO 8), S2);U3: CNT10 PORT MAP(S2, CLR, ENA, DOUT(15 DOWNTO 12));U4: CTRLS PORT MAP(CLK2,SEL);U5: DISPLAY PORT MAP(SEL(2 DOWNTO 0),DOUT(15 DOWNTO 0),COM(7 DOWNTO 0),SEG(7 DOWNTO 0));--位置关联方式END ARCHITECTURE ART;3)仿真波形设置本设计包括两个层次,因此先进行底层的十进制计数器CNT10的仿真,再进行顶层CNT9999的仿真。

计数器说明书

正常工作

XXXX XXXX

按住 10秒后

进入功能编 号设定状态

XX-X

按 设定功能编号

设定动作停止 10秒后,设定 值保存并生效

0 8 - X 按 后

进入继电器动作方 式编号设定状态

08-X

按 设定继电 器动作方 式编号

08-2

按 设定继电 器动作方 式编号

0 8 - 5 按 和 设定复位时间5.0秒 0 8 - 5 按 后 0 8 - 5

动作方 编号

式编号

单延时(正)

0.01秒-99.99秒

01 1~6

单延时(正)

1秒-9999秒

05 1~6

单延时(正)

1秒-99分59秒

07 1~6

单延时(正)

1分-99时59分

09 1~6

单延时(正)

1分-9999分

03 1~6

单延时(倒)

0.01秒-99.99秒

02 1~6

单延时(倒)

1秒-9999秒

19

公 共 端 C O M M

20

D C 9 V出 V o u t

21

继电器 输 出

说 明:

端子图

(1) 继 电 器 触 点 引 出 端 子 : 为 常 闭 , 为 常 开 。

(2) 供 电 电 源 为 直 流 时 , 接 线 不 需 要 区 分 正 极 和 负 极 。

(3)R E S T端 为 复 位 端 , 与C O M M端 接 通 则 延 时 恢 复 初 始 状 态 , 断

开则延时重新开始。

(4) 在 正 常 工 作 时 , 直 接 按 键 , 上 边 四 位L E D数 码 闪 烁 显

示 继 电 器 释 放 时 间 动 作 值 , 下 边 四 位L E D数 码 闪 烁 显 示

MCGS高级教程

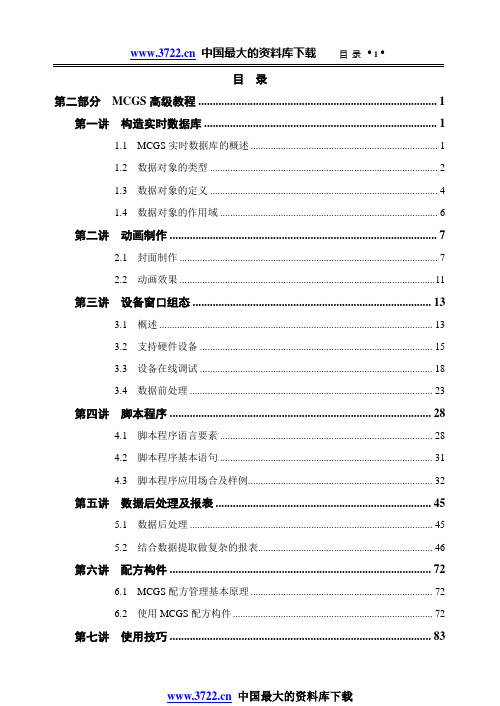

1.2

在MCGS组态软件中,数据对象有开关型、数值型、字符型、事件型、组对象等五种类型。不同类型的数据对象,属性不同,用途也不同。在初级培训教材中我们已经学会定义开关型、数值型、组对象三种类型。

第二部分

经过初级培训,您已经对MCGS组态软件的框架结构有了大致的了解,在初级培训教材的指引下,您一定能组态出一些简单的工程项目,但如果想应用自如还有一定困难。在高级培训教材帮助下,您一定会如虎添翼,组态出令人满意的工程。

培训目的经过培训,您可以熟练应用MCGS组态软件中的各项功能;

能根据工艺现场要求熟练制作动画流程;

1.4

实时数据库中定义的数据对象都是全局性的,MCGS各个部分都可以对数据对象进行操作,通过数据对象来交换信息和协调工作。数据对象的各种属性在整个运行过程中都保持有效。如在水位控制系统中的液位1、液位2,在实时曲线、实时报表、动画流程等都是用的同一变量。

第二讲 动画制作

2.1

封面窗口是工程运行后第一个显示的图形界面,演示工程的封面窗口样式如下图所示:

配方号

字符型

配方操作中用于配方查询的变量

配方查询号

字符型

配方操作中用于配方查询的变量

角度

数值型

用于封面窗口动画的变量

计数器1号

数值型

显示1号计数器的值

姓名

字符型

显示选择框的选择

计数器1号时间显示

字符型

用于时钟方式显示1号计数器的值

计数器1号工作状态

开关型

用于启动、停止1号计数器

机电控制与PLC应用-第四章答案

梯形图

LD

0.00

OR NOT 0.01

LD NOT 0.02

OR

0.03

AND LD

LD

0.04

OR

0.05

AND LD

OUT 100.00

分置法

LD

0.00

OR NOT 0.01

LD NOT 0.02

OR

0.03

LD

0.04

OR

0.05

AND LD

AND LD

OUT 100.00

后置法

梯形图

JMP和JME指令应用

LD 0.00 JMP &0 LD 0.01 OUT 100.00 AND 0.02 OUT 100.01 JME &0 LD 0.03 OUT 100.02

4.5、定时器和计数器应用指令 复

1、TIM 指令

位

格式: TIM N SV

定时器编号(0-4095)

定时器设定值 (#0-#9999),定时时间=SV*0.1s

LD

0.02

OR

0.03

AND

0.01

OUT

100.01

5.在不影响逻辑功能的情况下,应尽可能地将每一个阶梯简化 成串联支路或先并后串支路,尽量减少串并交叉的情况。有 时采用触点多次使用的办法,反而使程序结构更为简单。

6.尽量使用操作数少、执行时间短的指令编程,以缩短扫描周 期,提高I/O响应速度。

由于通过暂存继电器(TR0)来接收分支点,因此可进行程序化。

•输出分支电路较多时,在同一块(程序段)内,不能重复使用TR 的 继电器编号,但可以在其他块(程序段)中使用

TR指令和 IL/ILC指令的区别

C语言程序随机数的产生方法

随机数的产生方法瑞达路水瓶酒窝哥由于老师布置了产生随机数的作业,要求编一个程序能够产生0000到9999总共10000个不重复的随机数,可能大家在网上看了一些方法,都用了函数Rand与Brand的结合,可以产生10000个随机数,并且大家都是用公式(rand() % (b-a))+ a来约束产生随机数的范围和个数的,但是大家几乎忘了不能重复的要求,所以产生的随机数是有很多重复的,不能满足要求,鉴于这种情况,我把大众化随机数的产生方法以及自己的一点改进措施与大家共享如下:一、可重复随机数的产生方法:我们知道rand()函数可以用来产生随机数,但是这不是真正意义上的随机数,是一个伪随机数,是根据一个数(我们可以称它为种子)为基准以某个递推公式推算出来的一系列数,当这系列数很大的时候,就符合正态公布,从而相当于产生了随机数,但这不是真正的随机数,当计算机正常开机后,这个种子的值是定了的,除非你破坏了系统。

但是有一个函数srand()可以初始化这个种子函数。

1、函数rand()用法:说明:rand是包含在头文件stdlib.h中,跟stdio.h是一个道理,具体运用方法如下:代码:# include "stdio.h"# include "stdlib.h"int main(){int k;k=rand();printf("%d",k);return 0;}程序在编译软件中的运行截图过程如下:当运行这个程序时,我们会发现,产生的随机数永远都是一个值,例如我的电脑是41,这是因为计算机的随机数都是由伪随机数,即是由小M多项式序列生成的,其中产生每个小序列都有一个初始值,即随机种子。

(注意:小M多项式序列的周期是65535,即每次利用一个随机种子生成的随机数的周期是65535,当你取得65535个随机数后它们又重复出现了。

)rand()返回一随机数值的范围在0至RAND_MAX 间。

FANUC 0I系统保护8000-9000-9999号程序

FANUC 0I系统保护8000-9000-9999号程序参数NE8 NO3202#0:隐藏o8000~~o8999程序参数NE9 NO3202#4:隐藏o9000~~o9999程序说明:参数No.3202#4(NE9) 可以通过参数No.3210(PASSWD)和参数No.3211(KEYWD)将程序锁住以保护程序No.9000 到No.9999 在锁住状态下,除非输入了正确的口令否则程序No.9000到No.9999将不能被修改锁住状态意味着参数PASSWD 的设置值与参数KEYWD 的设置值不同这些参数中的设置值不显示当参数PASSWD 的设置值与参数KEYWD的设置值相同时就可以解锁当参数PASSWD 显示为0时表明PASSWD没有设置当No.3211(KEYWD)!=No.3210(PASSWD!=0) 锁定状态,程序保护,无法修改口令及NO3202锁住和解锁的步骤:锁住:1 置为MDI方式2 设置参数开关为可写这时在CNC 上显示P/S100报警3 设置参数No.3210(PASSWD) 这时就设定为锁住状态4 将参数写入开关置为禁止写入5 按下解除报警状态解锁:1 置为MDI方式2 设置参数开关为可写这时在CNC 上显示P/S100报警3 在参数No.3211(KEYWD)中设置与参数No.3210(PASSWD)相同的值这时锁住状态解除4 将参数NE9(No.3202#4)设置为05 将参数写入开关置为禁止写入6 按下解除报警状态7 程序No.9000到No.9999 现在就可以编辑了详细说明设置参数PASSWD:当参数PASSWD 中设置非0 值时就设置了锁住状态然而参数PASSWD 仅在锁住状态尚未设置时,当PASSWD=0 或PASSWD=KEYWD 才可以设置如果在其它情况下设置该参数就会出现一个不能写入的警告当设置了锁住状态改变参数PASSWD:当锁住状态解除后当PASSWD=0 或PASSWD=KEYWD 就可以更改设置状态在解锁步骤的第3 步后可以在参数PASSWD 中设置一个新的参数从这时起必须在KEYWD 中设置一个新值才能解除锁住状态重新锁住:在锁住状态解除后可以通过在PASSWD 参数中设置一个不同的值来重新设定或者通过关掉NC电源再打开后将KEYWD 复位来设定。

OMRON指令集

功能指令又称专用指令,CPM1A系列PLC提供的功能指令主要用来实现程序控制,数据处理和算术运算等。

这类指令在简易编程器上一般没有对应的指令键,只是为每个指令规定了一个功能代码,用两位数字表示。

在输入这类指令时先按下“FUN”键,再按下相应的代码。

下面将介绍部分常用的功能指令。

1.空操作指令NOP(0 0)本指令不作任何的逻辑操作,故称空操作,也不使用继电器,无须操作数。

该指令应用在程序中留出一个地址,以便调试程序时插入指令,还可用于微调扫描时间。

2.结束指令END(01)本指令单独使用,无须操作数,是程序的最后一条指令,表示程序到此结束。

PLC在执行用户程序时,当执行到END指令时就停止执行程序阶段,转入执行输出刷新阶段。

如果程序中遗漏END指令,编程器执行时则会显示出错信号:“NO END INSET”:当加上END指令后,PLC才能正常运行。

本指令也可用来分段调试程序。

3.互锁指令IL(02)和互锁清除指令ILC(0 3)这两条指令不带操作数,IL指令为互锁条件,形成分支电路,即新母线以便与LD指令连用,表示互锁程序段的开始;ILC指令表示互锁程序段结束。

互锁指令IL和互锁清除指令ILC用来在梯形图的分支处形成新的母线,使某一部分梯形图受到某些条件的控制。

IL和ILC指令应当成对配合使用,否则出错。

IL/ILC指令的功能是:如果控制IL的条件成立(即ON),则执行互锁指令。

若控制IL的条件不成立(即OFF),则IL与ILC之间的互锁程序段不执行,即位于IL/ILC之间的所有继电器均为OFF,此时所有定时器将复位,但所有的计数器,移位寄存器及保持继电器均保持当前值。

4.跳转开始指令JMP(0 4)和跳转结束指令JME(0 5)这两条指令不带操作数,JMP指令表示程序转移的开始,JME指令表示程序转移的结束。

JMP/JME指令组用于控制程序分支。

当JMP条件为OFF时,程序转去执行JME 后面的第一条指令;当JMP的条件为ON,则整个梯形图按顺序执行,如同JMP/JME 指令不存在一样。

EDA_FPGA_VHDL_数码管显示0000到9999

--深圳市21EDA电子--开发板型号:A-C8V4--学习4个数码管动态显示原理;--利用计数器自加,并且在数码管上显示--在4个数码管上面分别显示0000到9999的自加--递增方式在4位数码管上向上计数显示从0000-0001->0002……..9999….0000….0001…. --设计了一个4位十进制计数器,并用数码管显示当前计数值--视频教程适合我们21EDA电子的所有学习板library IEEE;use IEEE.STD_LOGIC_1164.ALL;use IEEE.STD_LOGIC_ARITH.ALL;use IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY LED_0000_9999 ISPORT (clk : IN std_logic; --系统时钟50Mrst : IN std_logic; --系统REST键,KEY1led_out : OUT std_logic_vector(7 DOWNTO 0); --各段数据输出led_bit : OUT std_logic_vector(3 DOWNTO 0)); --数码管的位选择口。

一共8位END LED_0000_9999 ;ARCHITECTURE arch OF LED_0000_9999 ISsignal div_cnt : std_logic_vector(24 downto 0 );signal data4 : std_logic_vector(3 downto 0);signal dataout_xhdl1 : std_logic_vector(7 downto 0);signal en_xhdl : std_logic_vector(3 downto 0);signal cntfirst :std_logic_vector(3 downto 0);signal cntsecond : std_logic_vector(3 downto 0);signal cntthird : std_logic_vector(3 downto 0);signal cntlast : std_logic_vector(3 downto 0);signal first_over: std_logic;signal second_over: std_logic;signal third_over : std_Logic;signal last_over : std_logic;beginled_out<=dataout_xhdl1;led_bit<=en_xhdl;process(clk,rst)beginif(rst='0')thendiv_cnt<="0000000000000000000000000";elsif(clk'event and clk='1')thendiv_cnt<=div_cnt+1;end if;end process;process(div_cnt(24),rst,last_over) ---first 10 counter beginif(rst='0')thencntfirst<="0000";first_over<='0';elsif(div_cnt(24)'event and div_cnt(24)='1')thenif(cntfirst="1001" or last_over='1')thencntfirst<="0000";first_over<='1';elsefirst_over<='0';cntfirst<=cntfirst+1;end if;end if;end process;process(first_over,rst) --second 10 counterbeginif(rst='0')thencntsecond<="0000";second_over<='0';elsif(first_over'event and first_over='1')thenif(cntsecond="1001")thencntsecond<="0000";second_over<='1';elsesecond_over<='0';cntsecond<=cntsecond+1;end if;end if;end process;process(second_over,rst) --second 10 counterbeginif(rst='0')thencntthird<="0000";third_over<='0';elsif(second_over'event and second_over='1')thenif( cntthird="1001")thencntthird<="0000";third_over<='1';elsethird_over<='0';cntthird<= cntthird+1;end if;end if;end process;process(third_over,rst) --second 10 counter beginif(rst='0')thencntlast<="0000";last_over<='0';elsif(third_over'event and third_over='1')thenif( cntlast="1001")thencntlast<="0000";last_over<='1';elselast_over<='0';cntlast<= cntlast+1;end if;end if;end process;---****************显示部分***************--process(rst,clk,div_cnt(19 downto 18))beginif(rst='0')thenen_xhdl<="1110";elsif(clk'event and clk='1')thencase div_cnt(19 downto 18) iswhen"00"=> en_xhdl<="1110";when"01"=> en_xhdl<="1101";when"10"=> en_xhdl<="1011";when"11"=> en_xhdl<="0111";end case;end if;end process;process(en_xhdl,cntfirst,cntsecond,cntthird,cntlast) begincase en_xhdl iswhen "1110"=> data4<=cntfirst;when "1101"=> data4<=cntsecond;when "1011"=> data4<=cntthird;when "0111"=> data4<=cntlast;when others => data4<="1010";end case;end process;process(data4)begincase data4 isWHEN "0000" =>dataout_xhdl1 <= "11000000"; WHEN "0001" =>dataout_xhdl1 <= "11111001"; WHEN "0010" =>dataout_xhdl1 <= "10100100"; WHEN "0011" =>dataout_xhdl1 <= "10110000"; WHEN "0100" =>dataout_xhdl1 <= "10011001"; WHEN "0101" =>dataout_xhdl1 <= "10010010"; WHEN "0110" =>dataout_xhdl1 <= "10000010"; WHEN "0111" =>dataout_xhdl1 <= "11111000"; WHEN "1000" =>dataout_xhdl1 <= "10000000"; WHEN "1001" =>dataout_xhdl1 <= "10010000"; WHEN "1010" =>dataout_xhdl1 <= "10000000"; WHEN "1011" =>dataout_xhdl1 <= "10010000"; WHEN "1100" =>dataout_xhdl1 <= "01100011"; WHEN "1101" =>dataout_xhdl1 <= "10000101"; WHEN "1110" =>dataout_xhdl1 <= "01100001"; WHEN "1111" =>dataout_xhdl1 <= "01110001"; WHEN OTHERS =>dataout_xhdl1 <= "00000011";END CASE;END PROCESS;end arch;。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

2、0-9999计数器的低层设计(VHDL语言代码)

分频器程序:

l ibrary ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

entity div is

generic(n: integer := 50000000);

port(

clk :in std_logic;

q :out std_logic

);

end div;

architecture bhv of div is

signal count :integer range n - 1 downto 0 := n - 1; begin

process(clk)

begin

if clk'event and clk='1' and clk'last_value = '0' then count <= count - 1;

if count >= n / 2 then

q <= '0';

else

q <= '1';

end if;

if count <= 0 then

count <= n - 1;

end if;

end if;

end process;

end;

计数器程序:

l ibrary ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

entity cnt_10 is

port(clk,en,reset :in std_logic;

cnt1,cnt2 :out std_logic_vector(3 downto 0)); end;

architecture bhv of cnt_10 is

signal temp1,temp2:std_logic_vector(3 downto 0);

signal c:std_logic;

begin

cnt1 <= temp1;cnt2<= temp2;

p1:process(clk,reset)

begin

if reset='1'then temp1 <="0000";

elsif clk'event and clk='1'then

if en='1'then

if temp1 <"1001"then temp1 <=temp1+1;c<='0';

else temp1 <="0000";c <='1';

end if;

end if;

end if;

end process p1;

p2:process(reset,c)

begin

if reset = '1' then temp2<="0000";

elsif c'event and c = '1' then

if en = '1' then

if temp2<"1001"then temp2<= temp2+1;

else temp2<="0000";

end if;

end if;

end if;

end process p2;

end;

数码管显示程序:

library ieee;

use ieee.std_logic_1164.all;

entity display is

port(clk_s :in std_logic;

data1, data2 :in std_logic_vector(3 downto 0);

dig :out std_logic_vector(1 downto 0);

seg :out std_logic_vector(7 downto 0) );

end;

architecture bhv of display is

signal cnt :std_logic;

signal d :std_logic_vector(3 downto 0);

begin

p0: process(clk_s)

begin

if clk_s'event and clk_s = '1' then cnt <= not cnt;

end if;

end process p0;

p1: process(cnt)

begin

case cnt is

when '0' => dig <= "10"; d <= data1;

when '1' => dig <= "01"; d <= data2;

end case;

end process p1;

p2: process(d)

begin

case d is

when "0000" => seg <= "11000000";

when "0001" => seg <= "11111001";

when "0010" => seg <= "10100100";

when "0011" => seg <= "10110000";

when "0100" => seg <= "10011001";

when "0101" => seg <= "10010010";

when "0110" => seg <= "10000010";

when "0111" => seg <= "11111000";

when "1000" => seg <= "10000000";

when "1001" => seg <= "10010000";

when others => seg <= "11111111";

end case;

end process p2;

end;。