数字电路逻辑设计第二版第-0-章引言精品PPT课件

数字电路与逻辑设计(第二版)章图文 (2)

第2章 组合逻辑电路

2.1 集成门电路 2.2 组合逻辑电路的分析和设计 2.3 组合逻辑电路中的竞争-冒险

第2章 组合逻辑电路

2.1 集成门电路

2.1.1 TTL门电路 TTL门电路由双极型三极管构成,它的特点是速度

快、抗静电能力强、集成度低、功耗大,目前广泛应用 于中、小规模集成电路中。TTL门电路有74(商用) 和54(军用)两大系列,每个系列中又有若干子系列,例 如,74系列包含如下基本子系列:

4)传输延时tP 传输延时tP指输入变化引起输出变化所需的时间,它 是衡量逻辑电路工作速度的重要指标。传输延时越短, 工作速度越快,工作频率越高。tPHL指输出由高电平变 为低电平时,输入脉冲的指定参考点(一般为中点)到 输出脉冲的相应指定参考点的时间。tPLH指输出由低电 平变为高电平时,输入脉冲的指定参考点到输出脉冲的 相应指定参考点的时间。标准TTL系列门电路典型的 传输延时为11ns;高速TTL系列门电路典型的传输延时 为3.3ns。HCT系列CMOS门电路的传输延时为7ns;AC 系列CMOS门电路的传输延时为5ns;ALVC系列CMOS 门电路的传输延时为3ns。

第2章 组合逻辑电路

图2―2和图2―3分别给出了TTL电路和CMOS电 路的输入/输出逻辑电平。

当输入电平在UIL(max)和UIH(min)之间时,逻辑电路可 能把它当作0,也可能把它当作1,而当逻辑电路因所接 负载过多等原因不能正常工作时,高电平输出可能低于 UOH(min),低电平输出可能高于UOL(max)。

第2章 组合逻辑电路

74AC和74ACT:先进CMOS(Advanced CMOS)。 74AHC和74AHCT:先进高速CMOS(Advanced High speed

数字电路与逻辑设计第二章

(7)扇出系数 C )扇出系数V 扇出系数表示与非门输出端最多能接同类与非门的个数,或称为负载能力。一般门电路的扇出系数为8 扇出系数表示与非门输出端最多能接同类与非门的个数,或称为负载能力。一般门电路的扇出系数为8,而驱动 或称功率门)的扇出系数可达15~ 。 门(或称功率门)的扇出系数可达 ~25。 (8)平均传输延迟时间 )

三态门总线结构 当EN1、EN2……ENn 轮流出现高电平时, 轮流出现高电平时,三 态门TS1、TS2……TSn 轮流将A1、B1,A2、 B2……An、Bn以与非 的形式送到总线BUS上 的形式送到总线 上

三态门双向传输 当EN = 0时,三态门TS1 时 工作, 禁止, 工作,TS2禁止,数据A 传送到B ;当EN =1时, 时 禁止, 三态门TS1禁止,TS2工 作,数据B传送到A

t pd

是一个反映门电路工作速度快慢的重要参数。信号经过任何门电路都会产生时间的延迟, 是一个反映门电路工作速度快慢的重要参数 。信号经过任何门电路都会产生时间的延迟 ,这是由 器件本身的物理特性所决定的。 器件本身的物理特性所决定的。

延时测量 电路 平均传输延迟时间

输入、 输入、输出 电压波形

t pd = (t phl + t plh ) / 2

按逻辑功能分类

第2章 组合逻辑电路 章

2.1 集成逻辑门

基本逻 辑运算 基本 逻辑 门 与、或、非 组成 复杂逻辑运算

与门、或门、 与门、或门、非门

构成

复合逻辑门、 复合逻辑门、复杂逻辑电路

双极型集成逻辑门( 双极型集成逻辑门(TTL、ECL、I2L、HTL ) 、 、 、 集成逻辑门 单极型集成逻辑门( 单极型集成逻辑门(NMOS、CMOS ) 、

电子技术精品课程-数字电路第2章 逻辑门电路 40页-41页PPT精品文档

逻辑0、1: 电路中用高、低电平来表示。

获得高、低电平的基本方法:利用半导体开关元件 的导通、截止(即开、关)两种工作状态。

二极管符号:

正极

+ uD -

负极

30.11.2019

回首页

2

iD ( mA)

IF

U BR

u D ( V)

2.4V

保证输出为低电平的最小输入高电平

(4)输入低电平值VIL VIL(max)=VOFF =0.8V

0.4V 0 VOFF VON

保证输出为高电平的最大输入低电平

0.3V v I

(5)噪声容限 VNH= VOH(min) – VON VNL= VOFF– VOL(max)

30.11.2019

回首页

30.11.2019

第2章 逻辑门电路

真值表

AB Y

00

1

01

1

10

1

11

0

逻辑表达式

YAB

回首页

15

VCC 3A 3B 3Y 4A 4B 4Y

14 13 12 11 10 9 8 74LS00

1234567

第2章 逻辑门电路

VCC 2A 2B NC 2C 2D 2Y

14 13 12 11 10 9 8 74LS20

放

Q

大

60μ A 40μ A 20μ A

区

Q1 iB=0

0 0.5 uBE(V)

0 UCES

VCC uCE(V)

工作原理电路

输入特性曲线

输出特性曲线截止区

截止状态

+

Rb b

数字电路逻辑设计(第二版) 王毓银╲t 电子科技大学

数字电路逻辑设计(第二版) 王毓银电子科技大学第1章绪论1.1 数字信号1.2 数制及其转换1.3 二一十进制代码(BCD代码)1.4 算术运算与逻辑运算1.5 数字电路1.6 VHDL1.7 本课程的任务与性质习题第2章逻辑函数及其简化2.1 逻辑代数2.1.1 基本逻辑2.1.2 基本逻辑运算2.1.3 真值表与逻辑函数2.1.4 逻辑函数相等2.1.5 三个规则2.1.6 常用公式2.1.7 逻辑函数的标准形式2.2 逻辑函数的简化2.2.1 公式法(代数法)2.2.2 图解法(卡诺图法)2.2.3 逻辑函数的系统简化法习题第3章集成逻辑门3.1 晶体管的开关特性3.1.1 晶体二极管开关特性3.1.2 晶体三极管开关特性3.2 TTL集成逻辑门3.2.1 晶体管一晶体管逻辑门电路(TTL)3.2.2 TTL与非门的主要外部特性3.2.3 TTL或非门、异或门、OC门、三态输出门等3.2.4 其他系列TTL门电路3.3 发射极耦合逻辑(ECL)门与集成注入逻辑(I2L)电路3.3.1 发射极耦合逻辑(ECL)门3.3.2 I2L逻辑门3.4 MOS逻辑门3.4.1 MOS晶体管3.4.2 MOS反相器和门电路3.5 CMOS电路3.5.1 CMOS反相器工作原理3.5.2 CMOS反相器的主要特性3.5.3 CMOS传输门3.5.4 CMOS逻辑门电路3.5.5 BiCMOS门电路3.5.6 CMOS电路的正确使用方法3.6 VHDL描述逻辑门电路3.6.1 VHDL描述电路的基本方法3.6.2 VHDL描述逻辑门电路习题第4章组合逻辑电路4.1 组合逻辑电路分析4.1.1 全加器4.1.2 编码器4.1.3 译码器4.1.4 数值比较器4.1.5 数据选择器4.1.6 奇偶产生/校验电路4.2 组合逻辑电路设计4.2.1 采用小规模集成器件的组合逻辑电路设计4.2.2 采用中规模集成器件实现组合逻辑函数4.3 组合逻辑电路的冒险现象4.3.1 静态逻辑冒险4.3.2 如何判断是否存在逻辑冒险4.3.3 如何避免逻辑冒险4.4 VHDL描述组合逻辑电路4.4.1 VHDL表达式、运算符和数据类型4.4.2 在结构体行为描述中常用语句4.4.3 结构描述语句4.4.4 VHDL语句描述组合逻辑电路习题第5章集成触发器5.1 基本触发器5.1.1 基本触发器电路组成和工作原理5.1.2 基本触发器功能的描述5.2 钟控触发器5.2.1 钟控R—S触发器5.2.2 钟控D触发器5.2.3 钟控J-K触发器5.2.4 钟控T触发器5.2.5 电位触发方式的工作特性5.3 主从触发器5.3.1 主从触发器基本原理5.3.2 主从J-K触发器主触发器的一次翻转现象5.3.3 主从J-K触发器集成单元5.3.4 集成主从J-K触发器的脉冲工作特性5.4 边沿触发器5.4.1 维持一阻塞触发器5.4.2 下降沿触发的边沿触发器5.4.3 CMOS传输门构成的边沿触发器5.5 VHDL描述触发器5.5.1 时钟信号和复位、置位信号的VHDL描述5.5.2 触发器的VHDL描述习题第6章时序逻辑电路6.1 时序逻辑电路概述6.2 时序逻辑电路分析6.2.1 时序逻辑电路的分析步骤6.2.2 寄存器、移位寄存器6.2.3 同步计数器6.2.4 异步计数器6.3 时序逻辑电路设计6.3.1 同步时序逻辑电路设计的一般步骤6.3.2 采用小规模集成器件设计同步计数器6.3.3 采用小规模集成器件设计异步计数器6.3.4 采用中规模集成器件实现任意模值计数(分频)器6.4 序列信号发生器6.4.1 设计给定序列信号的产生电路6.4.2 根据序列循环长度M的要求设计发生器电路6.5 时序逻辑电路的VHDL描述6.5.1 移位寄存器的VHDL描述6.5.2 计数器的VHDL描述习题第7章半导体存储器7.1 概述7.1.1 半导体存储器的特点与应用7.1.2 半导体存储器的分类7.1.3 半导体存储器的主要技术指标7.2 顺序存取存储器(SAM)7.2.1 动态CMOS反相器7.2.2 动态CMOS移存单元7.2.3 动态移存器和顺序存取存储器(SAM)7.3 随机存取存储器(RAM)7.3.1 RAM的结构7.3.2 RAM存储单元7.3.3 RAM集成片HM6264简介7.3.4 RAM存储容量的扩展7.4 只读存储器(ROM)7.4.1 固定ROM7.4.2 可编程ROM7.4.3 利用ROM实现组合逻辑函数7.4.4 EPROM集成片简介习题第8章可编程逻辑器件8.1 可编程逻辑器件基本结构8.1.1 “与一或”阵列结构8.1.2 查找表结构8.1.3 可编程逻辑器件编程技术8.2 简单可编程逻辑器件(SPLD)8.2.1 PAL器件的基本结构8.2.2 GAL器件的基本结构8.2.3 典型GAL器件8.3 复杂可编程逻辑器件(CPLD)8.3.1 概述8.3.2 可编程互连阵列结构CPLD8.3.3 全局互连结构CPLD8.4 现场可编程门阵列(FPGA)器件8.4.1 概述8.4.2 连续互连型FPGA器件8.4.3 分段互连型FPGA器件8.4.4 FPGA器件特点8.5 可编程逻辑器件的开发8.5.1 PLD设计流程8.5.2 PLD编程与配置习题第9章脉冲单元电路9.1 脉冲信号与电路9.1.1 脉冲信号9.1.2 脉冲电路9.2 集成门构成的脉冲单元电路9.2.1 施密特触发器9.2.2 单稳态触发器9.2.3 多谐振荡器9.3 555定时器及其应用9.3.1 555定时器的电路结构9.3.2 用555定时器构成施密特触发器9.3.3 用555定时器构成单稳态触发器9.3.4 用555定时器构成多谐振荡器习题第10章模数转换器和数模转换器10.1 概述10.1.1 数字控制系统1O.1.2 数据传输系统10.1.3 自动测试和测量设备10.1.4 多媒体计算机系统10.2 数模转换器(DAC)10.2.1 数模转换原理和一般组成10.2.2 权电阻网络DAC10.2.3 R-2R倒T形电阻网络DAC10.2.4 单值电流型网络DAC10.2.5 集成DAC及其应用举例10.2.6 DAC的转换精度与转换速度10.3 模数转换器(ADC)10.3.1 模数转换基本原理10.3.2 并联比较型ADC10.3.3 逐次逼近型ADC10.3.4 双积分型ADC10.4 集成ADC及其应用举例10.4.1 双积分型集成ADC10.4.2 逐次逼近型集成ADC10.4.3 ADC的转换精度和转换速度习题第11章数字系统设计基础11.1 数字系统设计的基本方法11.1.1 数字系统的组成11.1.2 数字系统设计方法11.2 系统控制器的描述11.2.1 ASM图描述方法11.2.2控制器设计——硬件实现11.2.3控制器设计——软件设计(VHDL描述)11.3 数字系统设计举例11.3.1 方案构思11.3.2 顶层的VHDL实现11.3.3 次级模块电路分析与设计11.3.4 控制器电路的设计习题附录一半导体集成电路型号命名方法附录二集成电路主要性能参数附录三二进制逻辑单元图形符号说明主要参考文献汉英名词术语对照。

数字电子电路第二版电子课件第二章组合逻辑电路

组合逻辑电路的设计步骤

首先,对实际问题进行分析,确定提出的问题中什么是输入变量、什么 是输出变量,并分析它们之间的逻辑关系,即把一个实际问题归纳为逻辑 问题。其次,合理地设置变量,列出真值表,然后由真值表写出逻辑表达 式,并根据所使用的逻辑门器件对表达式进行化简或变换。最后,根据化 简或变换后的逻辑表达式画出逻辑图。

77

§2—1 组合逻辑电路基础知识 §2—2 组合逻辑电路的分析和设计 §2—3 编码器 §2—4 译码器和显示器

§2—5 数据选择器和分配器 §2—6 加法器 §2—7 数值比较器

§2—1 组合逻辑电路基础知识

80

第二章 组合逻辑电路

学习目标

1. 了解组合逻辑电路的一般分析方法和设计方法。 2. 了解编码器、译码器典型集成电路的引脚功能和使用方法。 3. 了解数码选择器、数据分配器、加法器的基本工作原理和应用。 4. 掌握半导体七段显示数码管的使用方法。 5. 能根据电路图安装表决器、数码显示器等组合逻辑电路。

99

第二章 组合逻辑电路

三变量的最小项及其编号

100

第二章 组合逻辑电路

将n个变量的逻辑函数的2n个最小项用小方格代表并按相邻规则排列, 所形成的图形称为最小项卡诺图,简称卡诺图。所谓相邻规则就是指相邻2 个最小项只有1个变量不同,其他变量都相同。

卡诺图 a)二变量b)三变量c)四变量

101

第二章 组合逻辑电路

2. 用卡诺图表示逻辑函数 先将逻辑函数化为与或表达式,然后在卡诺图中把每一个乘积项所包含 的最小项都填上1,其余的填上0(或不填),便可得到该逻辑函数的卡诺 图。 3. 用卡诺图化简逻辑函数 在卡诺图中每两个相邻的小方格所代表的最小项只有一个变量不同,如 果这两个小方格均填的是1,则可利用这个特点消去一个变量。依次类推: 4个标有1的相邻项可合并为一项,消去2个变量;8个标有1的相邻项可合并 为一项,消去3个变量。

数字逻辑电路设计(第二版 鲍可进) ppt课件

作业点评

习题3

BEGIN WITH bcd_in SELECT

f<='1' WHEN "0101", '1' WHEN "0110", '1' WHEN "0111", '1' WHEN "1000", '1' WHEN "1001", '0' WHEN OTHERS;

图的输出表达式为:

电路图略

作业点评

习题3

3.21 设计一个1位二进制加/减法器,该电路在M的控制下

进行加、减运算。当M=0时,实现全加器功能;当M=1时, 实现全减器功能。

解:设被加/被减数为A、加数/减数为B、低位来的进位/借

位为C,和/差为F、向高位的进位/借位为F,据题意列真 值表如下表所示。

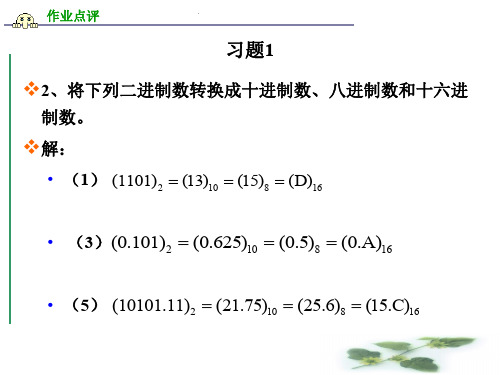

习题2

• 同样,根据二极管与门、或门电路,可知:

F3 ABC DEF F4 A B C D E F

作业点评

习题2

9、写出下图所示电路输出端的逻辑表达式。 解:本题中集电极开路的OC门实现线与功能和电平转换

的功能。

F AB CD

作业点评

2

• (1)

习题3

• (2)

作业点评

表达式:F=A+BC+BD

习题3

真值表如下表所列,由真值表可知该电路实现的功能是:判断输入的十

进制数是否对于或等于5,可以实现4舍5入功能。

数字电路逻辑设计课件 第二版 第 0 章 引言PPT共38页

谢谢!

61、奢侈是舒适的,否则就不是奢侈 。——CocoCha nel 62、少而好学,如日出之阳;壮而好学 ,如日 中之光 ;志而 好学, 如炳烛 之光。 ——刘 向 63、三军可夺帅也,匹夫不可夺志也。 ——孔 丘 64、人生就是学校。在那里,与其说好 的教师 是幸福 ,不如 说好的 教师是 不幸。 ——海 贝尔 65、接受挑战,就可以享受胜利的喜悦 。——杰纳勒 尔·乔治·S·巴顿

数字电路逻辑设计课件 第二版 第 0 章 引言

•

6、黄金时代是在我们的前面,而不在 我们的 后面。

•

7、心急吃不了热汤圆。

•

8、你可以很有个性,但某些时候请收 敛。

•

9、只为成功找方法,不为失败找借口 (蹩脚 的工人 总是说 工具不 好)。

•

Hale Waihona Puke 10、只要下定决心克服恐惧,便几乎 能克服 任何恐 惧。因 为,请 记住, 除了在 脑海中 ,恐惧 无处藏 身。-- 戴尔. 卡耐基 。

数字逻辑电路教程PPT第2章逻辑门电路

TTL与非门的电压传输特性及 抗干扰能力

CD段(过渡区):

1始也、.3导都TV5管<通处有v, 于I<一T导21、 小通.4V段T状3,、时态TT间,54管管同T开4 时导通,故有很大电流

流TT,电平52管、过T压vO4=T管很RvO054管急电 趋大.3V趋剧阻 于的。于下, 截基饱降止极T2和管到,电导提低输流通供电出,

TTL与非门的电压传输特性及 抗干扰能力

AB段(截止区): vI<0.6V,输出电压vO不

随输入电压vI变化,保持 在高电平VH。 VC1<0.7V,T2和T5管截 止,T3、T4管导通,输出 为高电平,VOH=3.6V。 由于这段T2和T5管截止, 故称截止区。

TTL与非门的电压传输特性及 抗干扰能力

⒉工作原理

当输入端A、B、C中有任一

个输入信号为低电平 (VIL=0.3V)时,相应的发射结 导通,T1工作在深度负饱和 状态,使T1管的基极电位VB1 被箝制在 VB1=VIL+VBE1=0.3+0.7=1V, 集电极电位 VC1=VCES1+VIL=0.1+0.3=0.4V 使T2管截止,IC2=0, VE2=VB5=0V,故T5管截止。

TTL与非门的电压传输特性及 抗干扰能力

CD段(过渡区): 由于vI的微小变化而

引起输出电压vO的急 剧下降,故此段称为 过渡区或转折区。

TTL与非门的电压传输特性及 抗干扰能力

CD段中点对应的输入电压 ,既是T5管截止和导通的分 界线,又是输出高、低电平 的分界线,故此电压称阈值 电压VT(门槛电压), VT=1.4V。

第二章 集成逻辑门电路

集成逻辑门电路,是把门电路的所 有元器件及连接导线制作在同一块 半导体基片上构成的。