可编程数字系统设计基础

《可编程序控制器应用技术》2-PLC基础知识

2.2 P LC控制系统与电器控制系统的比较 2.2.3 PLC等效电路

例:三相异步电动机单向运行电器控制系统 输入设备

输出设备

2.2 P LC控制系统与电器控制系统的比较 2.2.3 PLC等效电路

三相异步电动机单向运行PLC控制系统

2.2 P LC控制系统与电器控制系统的比较 2.2.4 PLC控制系统与电器控制系统的区别

日趋模糊的时候,PLC从传统的应用于离散的制造业向应用 到连续的流程工业扩展

2.1 概述 2.1.3 PLC的应用领域

2.1 概述 2.1.3 PLC的应用领域

2.1 概述 2.1.3 PLC的应用领域

2.1 概述 2.1.3 PLC的应用领域

2.1 概述 2.1.3 PLC的应用领域

2.1 概述 2.1.3 PLC的应用领域

目前国内市场还有韩国、台湾等PLC产品

2.1 概述 2.1.2 PLC的产生与发展 ■我国PLC发展情况

在70年代末和80年代初,我国随国外成套设备、专用设备 引进了不少国外的PLC。 我国不少科研单位和工厂在研制和生产PLC,如辽宁无线

电二厂、无锡华光电子公司、上海香岛电机制造公司、厦

门A-B公司等。 在传统设备改造和新设备设计中,PLC的应用逐年增多, 取得良好效果。PLC在我国的应用越来越广泛。

2.1 概述 2.1.3 PLC的应用领域

2.1 概述 2.1.3 PLC的应用领域

2.1 概述 2.1.3 PLC的应用领域

2.1 概述 2.1.3 PLC的应用领域

2.2 P LC控制系统与电器控制系统的比较 2.2.1 电器控制系统组成

2.2 P LC控制系统与电器控制系统的比较 2.2.2 PLC控制系统组成

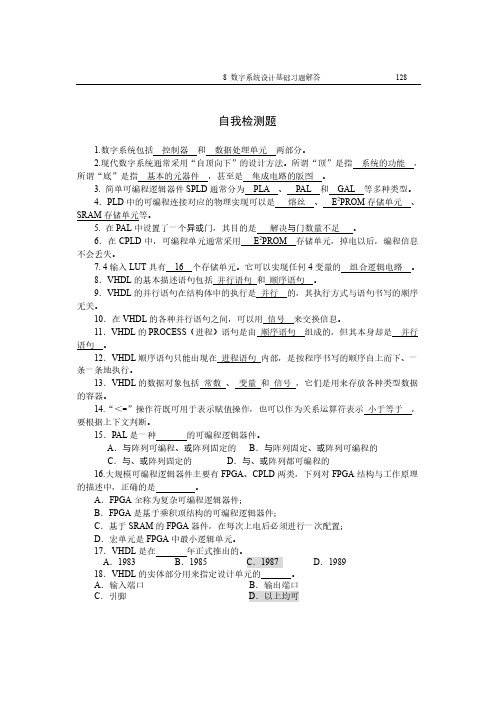

数字系统设计.pdf

PLD设计——CPLD与FPGA的区别

规模

CPLD规模一般比FPGA小,最多512个宏单元;FPGA则可以实现单片 1000万门。

速度

CPLD的速度可以比FPGA更高,其连线的延时固定,更适合做高速的应 用;FPGA的互连线为多段,延时不确定。

逻辑特点 CPLD适合做逻辑密集型的应用,FPGA适合做数据密集型的应用。 编程方式

ALTERA

XILINX

FPGA/CPLD生产商

ispLSI系列:1K、2K、3K、5K、8K ispLSI1016 、ispLSI2032、 ispLSI1032E、ispLSI3256A MACH系列 ispPAC系列:

LATTICE VANTIS (AMD)

CPLD

其他PLD公司: ACTEL公司: ACT1/2/3、40MX ATMEL公司:ATF1500AS系列、40MX CYPRESS公司 QUIKLOGIC公司

数字系统分类

数字系统本身实现的方法很多,一般来说,可以分为 以下几种方法: PLD(可编程逻辑器件) MCU(单片机) DSP(数字信号处理器) Embedded System(嵌入式系统) 以上几种设计方法的应用场合不同,设计方法也大 不相同,应该根据不同的应用场合、成本和设计的 难度来决定使用合适的设计方法。

SO MUCH IC!

FPGA CPLD

PLD设计——PLD设计的流程

设计输入

原理图 硬件设计语言

功能仿真

验证逻辑是否正确

综合

将原理图或者硬件描述语言翻译为网表。

时序仿真

加载器件延时文件后的仿真,验证在器 件上实现后的实际性能。

不同数字系统的应用场合(4)

Embedded System(嵌入式系统)

数字系统设计与Verilog HDL

数字系统设计与Verilog HDL(复习)EDA(Electronic Design Automation)就是以计算机为工作平台,以EDA软件工具为开发环境,以PLD器件或者ASIC专用集成电路为目标器件设计实现电路系统的一种技术。

1.电子CAD(Computer Aided Design)2.电子CAE(Computer Aided Engineering)3.EDA(Electronic Design Automation)EDA技术及其发展p2EDA技术的应用范畴1.3 数字系统设计的流程基于FPGA/CPLD的数字系统设计流程1. 原理图输入(Schematic diagrams )2、硬件描述语言 (HDL文本输入)设计输入硬件描述语言与软件编程语言有本质的区别综合(Synthesis)将较高层次的设计描述自动转化为较低层次描述的过程◆行为综合:从算法表示、行为描述转换到寄存器传输级(RTL)◆逻辑综合:RTL级描述转换到逻辑门级(包括触发器)◆版图综合或结构综合:从逻辑门表示转换到版图表示,或转换到PLD器件的配置网表表示综合器是能自动实现上述转换的软件工具,是能将原理图或HDL语言描述的电路功能转化为具体电路网表的工具适配适配器也称为结构综合器,它的功能是将由综合器产生的网表文件配置于指定的目标器件中,并产生最终的可下载文件对CPLD器件而言,产生熔丝图文件,即JEDEC文件;对FPGA器件则产生Bitstream 位流数据文件p8仿真(Simulation)功能仿真(Function Simulation)时序仿真(Timing Simulation)仿真是对所设计电路的功能的验证p9编程(Program)把适配后生成的编程文件装入到PLD器件中的过程,或称为下载。

通常将对基于EEPROM工艺的非易失结构PLD器件的下载称为编程(Program),将基于SRAM 工艺结构的PLD器件的下载称为配置(Configure)。

基于FPGA的数字信号处理系统设计与实现

基于FPGA的数字信号处理系统设计与实现数字信号处理(DSP)是对数字信号进行处理和分析的技术方法,广泛应用于通信、音频、图像等领域。

其中,利用可编程逻辑器件进行数字信号处理的算法加速已成为一种重要的技术趋势。

本文主要讨论基于FPGA(Field Programmable Gate Array)的数字信号处理系统的设计与实现。

一、FPGA的基础知识及特点FPGA是一种具有可编程逻辑和可编程连接的硬件器件,能够实现用户自定义的数字电路功能。

与固定功能的ASIC(Application-Specific Integrated Circuit)相比,FPGA具有灵活性强、开发周期短、成本低等优势。

在数字信号处理系统中,FPGA可以作为一种高性能的实现平台。

二、数字信号处理系统的基本框架数字信号处理系统通常包括信号的采集、预处理、算法处理和结果输出等步骤。

在FPGA上实现数字信号处理系统时,通常将这些步骤划分为不同的模块,并将其设计成可并行执行的结构,以提高系统的吞吐量和性能。

1. 信号采集与预处理信号采集模块通常用于将模拟信号转换成数字信号,并对其进行采样和量化处理。

预处理模块则用于滤波、降噪、增益控制等处理,以准备信号供后续的算法处理模块使用。

2. 算法处理算法处理模块是数字信号处理系统的核心,其中包括常用的信号处理算法,例如快速傅里叶变换(FFT)、数字滤波器、自适应滤波器等。

这些算法通常采用并行处理的方式,以提高系统性能。

3. 结果输出结果输出模块将经过处理的数字信号转换成模拟信号,并通过数字至模拟转换器(DAC)输出。

此外,还可以添加显示设备或通信接口,以直观地观察处理结果或将结果传输到其他设备。

三、基于FPGA的数字信号处理系统的设计流程基于FPGA的数字信号处理系统设计一般包括硬件设计和软件设计两个层面。

1. 硬件设计硬件设计主要包括系统的功能分析与规划、模块的设计与实现以及系统的验证与测试。

数字电路与系统设计实验

第二章 实验基本仪器

数字系统设计实验所需设备有: 直流稳压电源,示波器,基于CPLD的 数字电路实验系统,万用表,信号源, 计算机。

一、直流稳压电源

二、示波器

示波器是一种用来测量电信号波形的 电子仪器。用示波器能够观察电信号 波形,测量电信号的电压大小,周期 信号的频率和周期大小。双踪示波器 能够同时观察两路电信号波形。

能块相对集中地排列器件 3.布线顺序 VCC,GND,输入/输出,控制线 4. 仪器检测(电源,示波器,信号源) 5.实验 测试、调试与记录

6.撰写实验总结报告

(1)实验内容 (2)实验目的 (3)实验设备 (4)实验方法与手段 (5)实验原理图 (6)实验现象(结果)记录分析 (7)实验结论与体会

(((四三一)))、、、实实验实验目验的提内示容

•• 11..注测1意试.掌被T握T测LT器T器L件、件H7的CT4引和L脚HS7C器0和件4引的一脚传个输1特非4性门分。的别传接输地特和 十性5。V2。.掌握万用表的使用方法。

•• •

(2连为输23特二.接 被 入)..性将测测、123到 测 电。实试 试...被 非 压六六六验验HH反反反测 门 值所CC台相相相T器用非 的 。上器器器器件器门输4件777件7的入.444774输电LHH4KH入压SCCHΩC00T端。电C4400,旋位T片片44转R器0片T一电LR4的个T位一L输非的器个出门电改非端的压变门电传输非的压输出门传作特端的输性。

四、数字电路测试及故障查找、排除

1.数字电路测试

数字电路静态测试指的是给定数字电路若干组静态输 入值,测定数字电路的输出值是否正确。

数字逻辑基础与Verilog设计

在介绍逻辑电路时,作者指出:“逻辑电路是数字逻辑的基础,它是一种组 合电路,可以在任何两个节点之间建立连接。”这句话简单明了地表达了逻辑电 路的基本特点,即通过组合不同的门来连接两个节点。

在讲解组合逻辑时,作者强调了其重要的特性:“由于组合逻辑不具有存储 元件,因此它不具有记忆功能。”这句话准确地概括了组合逻辑与存储元件的区 别,让人清楚地理解了它们的差异。

第六部分是关于实验和设计案例的内容。这一部分介绍了一些实用的实验和 设计案例,旨在帮助读者将理论知识应用到实践中去。这些实验和案例涵盖了数 字逻辑和Verilog设计的各个方面,从简单的门级电路设计到复杂的系统级设计 都有涉及。通过这些实验和案例的学习,读者可以更好地掌握数字逻辑设计和 Verilog编程的技能。

精彩摘录

《数字逻辑基础与Verilog设计》是一本全面介绍数字逻辑基本概念与实际 应用的教科书。从逻辑电路到组合逻辑,从算术运算电路到存储元件,从同步时 序电路到异步时序电路,以及测试等方面,本书都进行了详尽的阐述。作为大多 数电气和计算机工程学科的基础课程,这本书不仅概念清晰,而且结合了逻辑设 计最新技术的发展。在这篇文章中,我们将分享这本书的一些精彩摘录。

在讲解同步时序电路和异步时序电路时,作者通过实例详细地解释了它们的 区别和实现方式。例如,对于同步时序电路,作者解释道:“同步时序电路的触 发器在同一时钟信号的控制下进行操作。”这句话清晰地表达了同步时序电路的 特点。

在介绍测试时,作者强调了测试的重要性:“测试是验证电路功能是否正确 的关键步骤。”这句话简洁明了地表达了测试的目的和重要性。

第四部分是关于数字逻辑电路的设计。这一部分详细介绍了组合逻辑电路和 时序逻辑电路的设计方法,并通过大量的实例让读者更好地理解数字逻辑电路的 设计过程。这部分还介绍了一些常用的数字逻辑电路,如译码器、编码器、比较 器等,为读者提供了丰富的设计资源。

数字系统设计的基础知识

05

数字系统的测试与验证

测试策略与技术

单元测试

对数字系统的各个模块进行独立测试,确保 每个模块的功能正常。

系统测试

对整个数字系统进行测试,确保系统满足设 计要求和功能需求。

集成测试

将各个模块组合在一起进行测试,确保模块 之间的接口正常工作。

验收测试

在数字系统交付之前,对系统进行全面测试, 确保系统能够满足用户需求。

案例分析:数字钟的设计需要高精度的计时和稳定的时钟源。石英晶体振荡器的选择对数字钟的准确性 和稳定性至关重要。此外,数字钟还需要考虑功耗和尺寸,以便于在各种应用场景中实现。

案例三:数字信号处理系统的设计

01

总结词:高效灵活

02

详细描述:数字信号处理系统是一种用于处理和分析信号 的数字系统。它通常由输入预处理电路、数字信号处理器 和输出后处理电路组成。数字信号处理器执行信号的滤波 、频谱分析、去噪等处理操作。

数字系统的发展历程

电子管时代

20世纪初,电子管作为数字系统的基 本元件,实现了计算机的初步发展。

02

晶体管时代

20世纪50年代,晶体管取代电子管成 为数字系统的基本元件,推动了计算 机小型化、便携化的发展。

01

互联网时代

21世纪初,互联网技术的普及和发展, 使得数字系统在信息传输和处理方面 发挥着越来越重要的作用。

03

的计数器用于控制指令的执行顺序。

存储器

存储器是数字系统中用于存储大量二进制数据的元件。

存储器由多个存储单元组成,每个存储单元可以存储一个二进制位。

存储器可以分为随机存取存储器(RAM)和只读存储器(ROM)等类型,在计算 机和其他数字系统中有着广泛的应用,如计算机的内存和硬盘等。

PLC编程及应用 全套课程

02 PLC编程语言与指令系统

CHAPTER

编程语言概述

编程语言种类

介绍PLC编程中常用的编程语言,如Structured Text、 Ladder Logic、Function Block Diagram等。

编程语言特点

分析各种编程语言的优缺点,以及适用场景和开发环 境。

编程语言规范

介绍国际电工委员会(IEC)和各国的PLC编程语言标 准执行顺序控制、逻辑运算、定时、计数和算术操作等指令,并通过数字或模拟输 入/输出控制各种类型的机械或生产过程。PLC具有可靠性高、抗干扰能力强、通用性良好、易学易用、可编程以 及良好的扩展性等特点。

PLC的历史与发展

总结词

PLC的历史可以追溯到20世纪60年代,最初用于取代继电器控制系统的逻辑控制。

CHAPTER

编程实践:基础控制系统的实现

总结词

掌握基础编程指令,实现简单逻辑控 制

指令学习

学习基础的PLC编程指令,如LD、 AND、OR等逻辑控制指令,以及计 时器和计数器等常用功能块。

实践应用

通过搭建简单的控制系统,如交通灯、 电机起停等,掌握PLC编程的基本流 程和实际操作。

调试与优化

对所实现的控制系统进行调试,优化 程序以提高系统的稳定性和可靠性。

数据处理中心

PLC收集并处理来自各种传感器的数据,为上层管 理系统提供决策支持。

集成接口

PLC作为不同设备和系统之间的集成接口,促进信 息流、物料流和资金流的协同运作。

谢谢

THANKS

05

03

调度算法

研究并应用先进的仓储设备调度算法, 如先入先出、后入先出等,以优化货 物存取效率。

04

系统集成

数字系统设计和PLD应用

算法设计的几种方法

跟踪法: 就是按照已确定的系统功能,由控制要求,逐步细化,逐步具体化。从而导 出系统算法; 归纳法: 归纳法 就是先把比较抽象的设计要求具体化,而后再进行一般规律的归纳,由此 导出系统算法; 分解法: 分解法 即把一个比较复杂的系统,分解(划分)成一系列简单的运算,来完成系 统的复杂运算; 解析法: 解析法 对一些难以划分(分解)的计算过程,则可以用数学分析的方法对其进行 数值近似,转换成多项式,或者某种迭代过程,从而导出算法; 综合法: 综合法 就是把上述四种方法组合起来运用,综合的考虑,逐步导出系统的算法。

输入电路 控制电路 ……… 输出电路

受控电路1

受控电路n

时基电路

脉冲与数字电路课程的回顾

布尔函数--数字系统数学基础(卡诺 图) 数字电路设计的基本方法

组合电路设计 问题 逻辑关系 真值表 化简 逻辑图 时序电路设计 列出原始状态转移图和表 状态优化 状态分 配 触发器选型 求解方程式 逻辑图

使用中、小规模器件设计电路(74、54 系列)

判别块: 符号为菱形,块内 给出判别变量和判别条 件。判别条件满足与否, 决定系统下一步将进行 不同的后续操作。

00

A1 A0

.

10

01

F D0

F

D1

F D2

Cp

CNT M=3

D0 D1 D2 D3

MUX

F

条件块:

条件块为一带横杠的矩 形块。条件块总是源于判别 块的一个分支,仅当该分支 条件满足时,条件块中标明 的操作才被执行,而且是立 即被执行。

算法就是对这种有规律、有序分解的一 种描述。 任何一个系统都可以用算法模型进行描 述。

算法模型的特征: 含有若干子运算。 这些子运算实现对数据或信息的传输、存 储或加工处理; 具有相应的控制序列。 控制子运算按一定规律有序地进行。 用算法流程图来描述上述运算过程。

可编程控制器的基本知识

可编程控制器(Programmable Logic Controller,简称PLC)是一种数字运算操作的电子系统,专为在工业环境下应用而设计。

以下是一些关于可编程控制器的基本知识:

结构:可编程控制器由微处理器、存储器、输入/输出接口、电源等部分组成。

其中,微处理器是控制器的核心部件,实现各种逻辑运算、算术运算,并对整个控制系统的各个部分的工作进行协调与控制。

存储器用于存放系统程序、用户程序、逻辑变量、输入/输出状态的映像等数据信息。

输入/输出接口是与被控对象设备或周边其他控制器相互联系、交换信息与指令的通道。

电源为整个控制器的电力供给中心,包括内部电源和外部电源,分别用于控制器内部元件的工作用电和传送设备上各传感器信号、驱动设备的各种执行元件。

工作原理:以可编程控制器为核心加入各种辅助器件(传感器、驱动器件等)构成控制系统,以顺序+反馈的方式实现设备的自动化运转。

主要特点:抗干扰能力强,可靠性高;程序简单易学,系统的设计调试周期短;安装简单,维修方便;采用模块化结构,体积小,重量轻;丰富的I/O接口模块,扩展能力强。

应用范围:可编程控制器在工业控制领域应用广泛,包括顺序控制、计数和定时控制、位置控制、模拟量控制、数据处理、通信联网等方面。

总之,可编程控制器是一种功能强大的工业自动化控制器,其基本知识包括结构、工作原理、主要特点和应用范围等方面。

了解和掌握这些基本知识有助于更好地应用可编程控制器进行工业控制系统的设计和应用。

plc控制系统设计的一般步骤

plc控制系统设计的一般步骤丰炜PLC说明资料1-PLC系统设计及选型方法在现代化的工业生产设备中,有大量的数字量及模拟量的控制装置,例如电机的起停,电磁阀的开闭,产品的计数,温度、压力、流量的设定与控制等,工业现场中的这些自动控制问题,若采用可编程控制器(PLC)可以轻松的解决,PLC已成为解决自动控制问题最有效的工具之一,越来越广泛的应用于工业控制领域中,本文简要叙述了PLC控制系统设计的步骤及PLC 的基本选型方法,供大家参考.一、可编程控制器应用系统设计与调试的主要步骤( 1 )深入了解和分析被控对象的工艺条件和控制要求这是整个系统设计的基础,以后的选型、编程、调试都是以此为目标的.a .被控对象就是所要控制的机械、电气设备、生产线或生产过程。

b .控制要求主要指控制的基本方式、应完成的动作、自动工作循环的组成、必要的保护和连锁等。

对较复杂的控制系统,还可将控制任务分成几个独立部分,这样可化繁为简,有利于编程和调试。

( 2 )确定 I/O 设备根据被控对象的功能要求,确定系统所需的输入、输出设备。

常用的输入设备有按钮、选择开关、行程开关、传感器、编码器等,常用的输出设备有继电器、接触器、指示灯、电磁阀、变频器、伺服、步进等.( 3 )选择合适的 PLC 类型根据已确定的用户 I/O 设备,统计所需的输入信号和输出信号的点数,选择合适的 PLC 类型,包括机型的选择、 I/O 模块的选择、特殊模块、电源模块的选择等。

( 4 )分配 I/O 点分配 PLC 的输入输出点,编制出输入 / 输出分配表或者画出输入 / 输出端子的接线图。

接着就可以进行 PLC 程序设计,同时可进行控制柜或操作台的设计和现场施工。

( 5 )编写梯形图程序根据工作功能图表或状态流程图等设计出梯形图即编程.这一步是整个应用系统设计的最核心工作,也是比较困难的一步,要设计好梯形图,首先要十分熟悉控制要求,同时还要有一定的电气设计的实践经验。

fpga现代数字系统设计教程——基于xilinx可编程逻辑

fpga现代数字系统设计教程——基于xilinx可编程逻辑在当今的数字系统设计领域中,基于现场可编程门阵列(Field-Programmable Gate Array,FPGA)技术的应用日益普遍。

Xilinx是其中一家领先的FPGA厂商,其可编程逻辑芯片被广泛应用于各个领域。

本教程旨在介绍FPGA现代数字系统设计的基本概念与技术,重点关注基于Xilinx可编程逻辑的实践应用。

一、引言FPGA是一种可重构的硬件平台,具有高度的灵活性与可定制性。

通过不同的配置,FPGA可以实现各种数字电路功能,比如逻辑运算、数字信号处理、嵌入式系统等等。

Xilinx提供了一套完整的开发工具与设计流程,使得FPGA的设计与实现更加高效与简便。

二、FPGA基础知识介绍1. FPGA的基本结构与工作原理在FPGA中,逻辑资源(如逻辑门、寄存器)通过可编程的内部连接资源相互连接,形成不同的数字电路。

FPGA采用按位编程的方式,通过配置存储器将逻辑连接进行设定,从而实现不同的功能实现。

2. Xilinx系列FPGA概述Xilinx公司生产的FPGA主要分为Artix、Kintex、Virtex等系列,每个系列有不同的性能与资源规模适用于不同的应用场景。

本节将介绍主要的Xilinx系列FPGA及其特点。

三、FPGA设计实践1. 集成开发环境(Integrated Development Environment,IDE)概述设计FPGA系统需要使用特定的软件工具,例如Xilinx提供的Vivado开发环境。

本节将介绍Vivado的基本功能与使用方法。

2. 基于Xilinx可编程逻辑的数字电路设计通过Vivado IDE,我们可以使用硬件描述语言(HDL)如VHDL或Verilog来描述数字电路。

本节将介绍如何使用HDL进行FPGA设计,包括逻辑门设计、时序控制、状态机设计等。

3. FPGA系统集成设计除了单个模块的设计,FPGA设计还需要进行系统级集成。

FPGA现代数字系统设计基于ilinx可编程逻辑器件与Vivado平台

目录分析

目录分析

《FPGA现代数字系统设计基于ilinx可编程逻辑器件与Vivado平台》是一本 深入浅出地介绍FPGA(现场可编程门阵列)设计和实现的书籍。作为一本专注于 Xilinx可编程逻辑器件和Vivado平台的书籍,其目录结构也反映了这一核心内容。 以下是该书的目录分析:

目录分析

这部分内容主要介绍了FPGA的基本概念、发展历程以及在数字系统设计中的 应用。还简要介绍了Xilinx公司及其产品,为后续深入学习打下基础。

精彩摘录

“在FPGA设计中,测试和验证是不可或缺的一环。通过充分的测试,我们可 以确保设计的正确性和可靠性。”

精彩摘录

“随着技术的不断发展,FPGA设计也在不断演进。未来,FPGA将在人工智能、 物联网、云计算等领域发挥更加重要的作用。因此,学习和掌握FPGA设计对于数 字系统设计师来说具有重要意义。”

目录分析

在这一部分,作者进一步探讨了高级的FPGA设计技术,包括高层次综合、者在实现复杂数 字系统的同时,优化设计性能和功耗。

目录分析

最后一部分内容以实际案例分析结束,包括几个具有代表性的FPGA设计项目。 通过这些案例的分析,读者可以更好地理解前面所学知识在实际项目中的应用。

目录分析

这一章详细介绍了Vivado设计套件,包括其功能、界面、以及在FPGA设计中 的重要性。通过这一章,读者可以了解如何使用Vivado进行FPGA设计的整个流程。

目录分析

在这一部分,作者深入探讨了数字系统设计的基础知识,包括逻辑门、触发 器、寄存器、以及基本的组合和时序逻辑电路。这些知识为后续的FPGA设计提供 了理论支持。

目录分析

这一章详细介绍了使用Vivado进行FPGA设计的整个流程,包括设计输入、综 合、实现以及生成比特流等步骤。还介绍了如何进行时序分析以及优化设计。

数字逻辑设计入门

直接说正题,帮助一下刚刚入门的朋友们,也算是学习IC设计的一个总结吧。

一、首先要知道自己在干什么?数字电路(fpga/asic)设计就是逻辑电路的实现,这样子说太窄了,因为asic还有不少是模拟的,呵呵。

我们这里只讨论数字电路设计。

实际上就是如何把我们从课堂上学到的逻辑电路使用原理图(很少有人用这个拉),或者硬件描述语言(Verilog/VHDL)来实现,或许你觉得这太简单了,其实再复杂的设计也就是用逻辑门电路搭起来的。

你学习逻辑电路的时候或许会为卡拉图,触发器状态推倒公式而感到迷惑,但是其实有一点可以放心的是,实际设计中只要求你懂得接口时序和功能就可以了,用不着那么复杂得推倒公式,只要你能够用语言把逻辑关系表述清楚就可以了,具体这个逻辑关系采用什么门电路搭的,可以不关心,综合工具(synthesis tool)可以帮你处理。

当然你要知道基本门电路的功能,比如D触发器,与门,非门,或门等的功能(不说多的,两输入的还是比较简单的)。

---一句话,采用verilog或者VHDL描述设计对象的逻辑功能,这就是数字电路设计的任务!说到这里入门必须要两个基本功:逻辑电路基础,硬件描述语言。

有了这两个基本功,就算你其他都不会也能找到工作,呵呵,或许你会说,现在面试要问fpga,要问时序分析,有那么简单么?其实这些东西在你有了这两个基本功之后,其他的都可以慢慢学习。

注意硬件描述语言和逻辑电路的学习可以同步学习,而且要牢记,学习硬件描述语言进步取决于你对电路的理解和你对仿真器的使用。

为什么这样子说呢?因为硬件描述语言RTL(寄存器传输级)主要是用来给综合工具综合成电路的,所以要满足特定的coding style,这些coding style 将对应这特定的逻辑,比如时序电路应该怎么写,组合电路怎么写,这是有一定约束的,为此若你对逻辑电路比较熟悉,你就知道自己写代码大体综合后会采用什么门电路来组成;另外,写代码就要仿真,这是不可以避免的---不仿真,你怎么知道自己写的代码符合设计的要求呢?能够熟练使用仿真器,你就有了调试代码的基本能力,否则,写再多的代码也没有用。

可编程逻辑设计基础

a)了解可编程数字系统设计的流程b)掌握Quartus 软件的使用方法c)掌握竞争和冒险的基本概念和电路时延分析方法二、实验原理1.实验内容观察并记录实验箱上的FPGA 型号,新建一个Project,器件选用实验箱上的FPGA;硬木课堂的FPGA型号是cyclone 4 EP4CE6F17C8N,由于quartus2 9.1web不能提供对于该芯片的仿真支持,故选用cyclone3 EP3C5E144C8作为仿真芯片建立project用“AND2”和“XOR”器件设计一个1 位半加器,并用功能仿真进行验证;输入输出信号:A、B分别表示输入的两位加数,S表示输出的和数,C表示输出的进位。

根据信号列出真值表:A B S C0 0 0 00 1 1 01 0 1 01 1 0 1根据真值表得出逻辑表达式:S = A xor BC = AB根据逻辑表达式作出原理图:功能仿真:首先通过然后为信号分配管脚进行全编译通过编写波形文件生成simulationnetlist开始功能仿真校验真值表与实际功能无误3、点击“File”“Create/Update”“Create Symbol File for Current File”菜单项,将1 位半加器封装成元件。

新建一个原理图文件,调用2 个半加器实现一个1 位全加器,并用功能仿真进行验证;输入输出信号:Ai Bi Ci-1分别表示两个加数与低位进位,Si表示和数Ci表示进位列出真值表:Ai Bi Ci-1 Si Ci 0 0 0 0 0 0 0 1 1 0 0 1 0 1 00 1 1 0 11 0 0 1 0 1 0 1 0 1 1 1 0 0 1 1 1 1 1 1 得出逻辑表达式:Si = Ai xor Bi xor Ci-1Ci = AB’Ci-1+A’BCi-1+AB = AB + Ci-1 * AxorB作出用两个半加器的原理图功能仿真:与真值表符合4、将 1 位全加器封装成元件,新建原理图文件,调用 4 个全加器实现一个 4 位行波加法器,用功能仿真进行验证,用“Tools”“Netlist Viewers”“RTL Viewer”查看电路综合结果;输入输出信号:Ai Bi Ci-1分别表示第i位两个加数与i-1位进位,Si表示第i位和数Ci表示第i位进位列出真值表:Ai Bi Ci-1 Si Ci0 0 0 0 00 0 1 1 00 1 0 1 00 1 1 0 11 0 0 1 01 0 1 0 11 1 0 0 11 1 1 1 1得出逻辑表达式:Si = Ai xor Bi xor Ci-1Ci = AB’Ci-1+A’BCi-1+AB = AB + Ci-1 * AxorB原理图:使用4个全加器易得第0位进位信号接地,然后依次串联即可得到行波4位加法器功能仿真:由于低位进位信号只与低位的加数与次低位信号有关,因此逐位验证功能,即固定低位进位信号测试功能,分四次测试第0位(最低位)第1位第2位第3位(最高位)与实际功能符合RTL Viewer显示的电路综合结果;5、适配编译,用“Tools”“Netlist Viewers”“Technology Map Viewer”查看电路Map 结果;用“Tools”“Chip Planner”查看器件适配结果;Technology Map Viewer显示的电路map结果Chip Planner显示的器件适配结果6、将4 位全加器下载到实验箱,连接逻辑电平开关进行功能验证7、对1 位半加器,进行时序仿真,并做时延分析,可参考预备知识相关内容编写好波形文件后(A 20NS B 40NS)进行时序仿真AB从10变为01时由于AS FR = 8.945ns AC FF = 7.371nsBS RF = 8.198NS BC RR= 6.903NS所以B信号的上升传到SC时A信号的下降还未传递过来,因此会S 会出现短暂的低电平C是高电平C的宽度S的宽度AB从“01”变为“11”时由于AC RR=7.142ns AS RF=8.817ns 因此C的上升要优先于S的下降出现SC的11态,后稳定于01,宽度为1.377nsAB由11变为00时,AC FF = 7.371 BC FF = 7.092实际显示经由7.108后C由1变为0AS FF=8.817 BS FR = 8.660因此产生一个宽度为148ps的高电平8、对1 位全加器,进行时序仿真,并做时延分析,要求:Progagation Delay显示的各输入对输出的时延a)测量 A 第1~4 个上升沿到对应的的S 输出之间的延迟时间;第一个第二个第三个第四个b)对输出S 的毛刺进行测量和分析;图中可见当AiBi从10变为01时由于B的RF = 4.659ns A的FR = 5.205ns 所以B的变化先影响Si,因此Si出现一个尖刺的低电平宽度为546psAiBiCi-1从110变为001时由于B FR =4.851 A 的FF = 5.157 所以Si会先变为短暂的高电平后恢复低电平直到Ci-1 的RR=7.494ns响应后才会变为稳定的高电平毛刺宽度高电平311ps低电平2.323nsc)对输出C 的毛刺进行测量和分析;AiBi从10变为01时由于Bi RR=5.149快于Ai的FF=5.535因此Ci会出现一个短暂的高电平毛刺宽度:386psd)对测得的时延结果进行分析BiCi-1=00 Ai 0-1与表中Ai对Si RR = 5.075非常接近AiCi-1=00 Bi 0-1与表中Bi对Si RR = 4.729相等AiBi=00 Ci-1 0-1与表中Ci-1对Si RR = 7.494相等BiCi-1=10 Ai 0-1与表中Ai 对Ci RR = 5.478相等AiCi-1=10 Bi 0-1与表中Bi对Ci RR = 5.149相等AiBi=10 Ci-1 0-1与表中Ci-1对Ci RR = 7.913相等9、对4 位全加器,进行时序仿真,并做时延分析,要求:Progagation Delay显示的各输入对输出的时延e)测量Cin=“0”,B=“0111”,A 从“0000”-“0001”所对应输出S3的时延;如图A0由0-1后,经由9.793ns S3由0-1与表对应f)测量Cin=“0”,B=“0110”,A 从“0000”-“0010”所对应输出S3的时延;如图A1由0-1后,经由9.501ns S3由0-1 与表对应g)测量Cin=“0”,B=“0100”,A 从“0000”-“0100”所对应输出S3的时延;如图A2由0-1后,9.125ns后S3由0-1 与表对应h)测量Cin=“0”,B=“0000”,A 从“0000”-“1000”所对应输出S3的时延;如图A3由0-1后,8.296ns后S3由0-1 与表对应i)测量Cin=”0”-“1”,B=“0000”,A 从“0000”-“0111”所对应输出S3的时延;如图Cin由0-1后,9.393ns后S3由0-1 与表对应j)测量Cin=“0”,B=“1111”,A 从“0000”-“0001”所对应输出Cout的时延;如图A0由0-1后,经由9.687ns Cout由0-1与表对应k)测量Cin=“0”,B=“1110”,A 从“0000”-“0010”所对应输出Cout的时延;如图A1由0-1后,经由9.395ns Cout由0-1与表对应l)测量Cin=“0”,B=“1100”,A 从“0000”-“0100”所对应输出Cout的时延;如图A2由0-1后,经由9.019ns Cout由0-1与表对应m)测量Cin=“0”,B=“1000”,A 从“0000”-“1000”所对应输出Cout的时延;如图A3由0-1后,经由8.191ns Cout由0-1与表对应n)测量Cin=”0”-“1”,B=“1000”,A 从“0000”-“0111”所对应输出Cout的时延;如图Cin由0-1后,经由9.287ns Cout由0-1与表对应o)对测得的时延结果进行分析见上述各条三、实验仪器Quartus 2 V9.1 sp2web四、实验记录下载后的程序未发生故障在时序仿真测量时延时偶有发生与delay表相差0.001ns的情况,未能解决五、实验小结初步学习了可编程逻辑器件及quartus的使用,掌握了一定的时延分析方法。

基于QuartusII的CPLD的数字系统设计与实现课程设计

基于QuartusII的CPLD的数字系统设计与实现课程设计1. 引言数字系统设计与实现是电子信息工程专业的一门重要课程,是学生掌握数字电路设计与实现的基础,具有一定的理论和实践意义。

本文将介绍基于QuartusII的CPLD的数字系统设计与实现课程设计的具体内容和实践步骤。

2. 设计背景与目的CPLD(Complex Programmable Logic Device)是一种可编程数字逻辑器件。

相比于普通的ASIC(Application-Specific Integrated Circuit)和FPGA(Field-Programmable Gate Array)器件,CPLD具有逻辑门数量多、功耗低等优点,适用于嵌入式系统、通信设备、工控设备等多个领域。

因此,CPLD的数字系统设计与实现课程设计旨在帮助学生掌握CPLD的基本原理、设计方法和实现技术,从而提高学生的数字电路设计和实现能力。

3. 设计内容3.1 设计思路本次课程设计的设计思路为:首先确定设计需求和目标,然后进行电路设计与仿真,最后实现电路并进行测试。

具体流程设计流程图设计流程图3.2 设计需求和目标本次课程设计的设计需求和目标如下:•设计一个功能较为简单的数字系统,包含输入、处理和输出三个部分。

•设计中需要使用基于QuartusII的CPLD开发板进行电路实现,并用Verilog硬件描述语言进行编程设计。

•设计需求和目标均需要满足实验要求,通过实验测试和评估。

3.3 电路设计与仿真基于上述需求和目标,我们进行了电路设计与仿真。

本课程设计的电路设计包括以下四个方面的内容:3.3.1 输入部分电路设计本文的输入部分选用拨码开关,可以通过拨动不同的拨码开关改变该输入端口的输入的状态。

3.3.2 处理部分电路设计本文的处理部分电路设计选用一个比较器。

该比较器可以将输入的二进制数与给定的比较值进行比较,然后输出比较结果,高电平表示输入数大于或等于比较值,低电平表示输入数小于比较值。

8数字系统设计习题解答

A.字母

B.数字

C.字母或数字

D.下划线

23. 在 VHDL 中,目标信号的赋值符号是

。

A. =:

B.=

C. :=

D.<=

习题

1.说明自顶向下的设计方法及步骤。 首先从系统设计入手,在顶层将整个系统划分成几个子系统,然后逐级向下,再将每 个子系统分为若干功能模块,每个功能模块还可以继续向下划分成子模块,直至分成许多 最基本模块实现。 2.说明 CPLD I/O 控制块的功能。 I/O 控制块允许每个 I/O 引脚单独地配置为输入、输出和双向工作方式。所有 I/O 引脚 有一个三态缓冲器,它控制的信号来自一个多路选择器,可以选择全局输出使能信号中的 一个或者直接连接到地(GND)或电源(Vcc)上。当三态缓冲器的控制端接地时,输出 为高阻态,此时 I/O 引脚可用作专用输入引脚。当三态缓冲器的控制端接高电平(Vcc)时, 输出被使能 3.以 Cyclone IV 系列 FPGA 为例,逻辑单元 LE 能否同时实现组合逻辑电路和时序逻 辑电路? 从图 8.2-18 可知,LUT 输入除了来自互连阵列,也来自触发器的输出,也就是说触发 器的输出反馈到 LUT 的输入端,便于构成计数器、状态机等时序电路。LUT 的输出可以 直接送到互连阵列,触发器的输入也可以不来自 LUT 的输出,而来自触发器链输入。LUT 和触发器可以独立工作,这意味着一个逻辑单元可以同时实现组合电路和时序电路。 4.CPLD 和 FPGA 有什么不同? FPGA 可以达到比 CPLD 更高的集成度,同时也具有更复杂的布线结构和逻辑实现。 FPGA 更适合于触发器丰富的结构,而 CPLD 更适合于触发器有限而积项丰富的结构。 在编程上 FPGA 比 CPLD 具有更大的灵活性;CPLD 功耗要比 FPGA 大;且集成度越高 越明显;CPLD 比 FPGA 有较高的速度和较大的时间可预测性,产品可以给出引脚到引脚 的最大延迟时间。CPLD 的编程工艺采用 E2 CPLD 的编程工艺,无需外部存储器芯片,使 用简单,保密性好。而基于 SRAM 编程的 FPGA,其编程信息需存放在外部存储器上,需

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

东南大学电工电子实验中心

实验报告

课程名称:数字逻辑电路实践

第六次实验

实验名称:可编程数字系统设计基础

院(系):专业:

姓名:学号:

实验室: 实验组别:

同组人员:实验时间:09年12 月28 日评定成绩:审阅教师:

1、申请题目:

健身自行车控制器

设计一个健身房使用的健身自行车控制器。

输入采用4*4键盘,显示采用4位数码管,其中最高位显示训练强度,低三位显示时间。

基本功能:

1.使用者骑上自行车时,控制器处于初始状态。

按“F”键启动控制器,此时四位数码管显示”0000“。

2用户输入从0~9中的任意数字,以改变训练强度,按”E”键确认。

选定的训练强度显示在数码管的最高位。

3训练强度选择完成之后,数码管低三位显示“0:00”。

通过数字键盘输入数字,以决定训练的时间,输入时数字顺序是从左到右。

如果输入正确,按下“E”键确认。

如果使用者输错了时间,可以按“C ”清除,显示恢复“0:00”的状态。

训练时间输入完成后,按下“F”键开始训练。

此时4位数码管的低三位显示时间从设定的时间倒计时到“0:00”。

在最后10s时,发光二极管亮1s暗1s.当计时到设定的时间,控制器恢复到初始状态,此时定时器显示“0:00”,训练强度为前面设定的值。

5、状态流程图:

(下面图片位置不能改了,顺序换下)

系统工作状态流程

从图中看共有9个状态,借助前第六章的自行车状态编码,仍将其四位编码,依次往下,前八个状态的最高为均为0,仅最后一个状态码的最高位为1,状态编码标于图中。

2、 状态机设计思路:

画出其操作流程图并注明操作之间条件:

非F 键 0~9键

F 键

非E 键

E 键

任意键

0000

0001 0010

⏹功能、指标、规模

启动控制器:在初始状态下,按下“F”键即能启动

清零复位:用户在输入时间时不慎输错,按C键可实现清零复位,由设定时间递减计数到0,数码管显示00,即清零状态;

改变训练强度和训练时间

输入数字:用户按下0~9中的数字来改变训练强度和训练时间,按“E”键确认,C键清零重新输入,F键启动。

开始训练有设定时间计时到0:设定好之后按F键即开始训练,计数器递减计数

最后10s发光二极管亮一秒暗一秒:在最后10s内有一个信号启动二极管工作

⏹面板(显示)、操作、规则

数码管第一位显示训练强度,后三位显示时间。

数字由4*4键盘输入,当输入合法时,在相应数码管显示对应输入值。

状态按“F”键四位数码管显示清零,非”F”键四位数码管状态保持;按下F键后按0~9中的任一数字,第一个数码管显示按下数字,按下非0~9键数码管清零状态保持;若按下0~9中的数字,再按下E键即确认,否则回到清零状态;按下“E”键后按0~9中任意数字,第二个数码管显示按下数字,按非0~9键,数码管显示状态不变;按下0~9键即第二个数码管显示正常,按下0~5中的数字,第三个数码管显示按下数字,按下C键三个时间数码管都清零,显示“0:00”,按下非0~5,非C键数码管显示状态不变;按下0~5键即第三个数码管显示正常,按下0~9中的数字,第四个数码管显示按下的数字,按下C键三个数码管都清零,显示“0:00”,按下非0~9,非C键数码管显示状态不变;按下0~9按“E”键确认后按F键开始训练即数码管显示时间递减,否则数码管状态保持。

⏹输入、输出接口

输入数字接口由4*4键盘和键盘电路实现;

各种状态转换由行列寄存器和ROM及译码电路实现;

数字输出由ROM和四个计数器实现。

3、实现方案:

⏹核心问题

1.键盘

2.实现模600递减计数

3.状态之间的转换

⏹解决方案

1.键盘电路

如下所示:

2.模600递减计数器

3.用rom实现(具体见后面rom编码)

4、系统结构:

系统框图

总的自行车电路由模600递减计数器,键盘电路,ROM ,译码电路,强度寄存器构成。

见下图:

模块功能描述

模600递减计数器:用来计时,由用户设定的时间递减计数到0;

行列式键盘:将输入数字由键盘实现;

寄存器(计数器):将送入数码管的数据进行寄存,使其输出稳定;

译码电路:实现八个状态之间的分别控制;

(组合逻辑(与非门):计时至最后10s时,由模600计数器输出一信号加至与非门输出控制二极管发光报警。

消抖同步化电路:行列式键盘中)

⏹模块接口标注(参数、协议)

6、各主要模块图与仿真波形

⏹各模块的仿真波形,详细注释输入输出功能端口,波形意义

键盘部分仿真:

RSM(r3~r0):行扫描信号

CJC(c3~c0):列检测信号

ROW(A7~A4):行信号寄存器,161输出,输入ROM的

COL(A3~A0):列信号寄存器,161输出,输入ROM的

CLK74:触发器时钟

CLK194:194时钟(扫描)

RcCR:行列寄存器的清零端,这里仿真时让其置于1

从RSM可知扫描信号正常,即信号在1110,0111,1011,1101 之间变化,CJC信号输出显示在没有键按下时,列始终为1。

令列中的C0为0,模拟检测到有键被按下,这时扫描应停止,行列信号值均被输出送入行列寄存器寄存,从图中可见,RSM的确停止,这时行信号值13,列信号值14被送入寄存器

寄存,可见键盘功能正常。

模600递减计数器仿真:

QHH:最高位时间

QH:中间时间

QL:低位时间

RCOMHH:高位161的进位信号

RCOMH:中间161的进位信号

RCOML:低位161的进位信号

从QL波形可知:低位计数器实现了模10的递减计数功能,并在递减到0时产生一个高电平借位信号RCOML; 中间的计数器也实现了模6的递减计数功能,并在递减到0时产生一个高电平借位信号RCOMH;高位计数器实现了模10 的递减计数功能,并且在递减到0时产生一个高电平借位信号。

三个计数器级联实现了模600的递减功能。

7、设计总结

⏹预期的目标与当前实现功能的差异

没有能够在实验箱上验证成功。

⏹调试过程中出现的问题分析及其解决措施

开始键盘电路仿真不成功,调整时钟周期后就行了。

⏹可以进一步发挥提高的部分

基本功能都没有完成。

⏹设计体会

看似简单的电路用软件做也很麻烦,一个人设计解决很辛苦。

键盘编码;

本题ROM编码:。