数字集成电路 后端设计 APR流程 之Astro

Astro完全流程

Astro完全流程Astro文档 V1.0数据准备(必需的文件)Foundry提供:·Technology File (.tf);·CLF Files (.clf);·GDSII Stream Files;·Reference Library;用户自己编写或编译:·Capacitance Model (.tlu):TLU or TLU+;·Pad Sequence Information (.tdf);·Timing Constraints (.sdc): 由DC产生的时钟约束文件;Astro 具体设计流程1. 建立设计库(Create Library)加入所需的工艺文件,建立一个新的工作库。

2. 生成TLU+模型(create TLU+ Model)将由Star-RCXT产生的.itf文件转化成.tlu文件,同时注意此步需要一个.map文件。

3. 同样可以产生TLU模型一般情况下,.tf文件含有相关信息,通过下面命令可实现:Tech File > Create Capacitance Model …4. 加参考库(addAndShowRefLib)在新建的设计库中加入Foundry提供的参考库,可以分别加入几个参考库。

之后,可以显示已经加入的参考库。

5. 读入网表(read Verilog)读入网表,Astro支持.v,.vhd,.edf等多种网表格式,我们组都采用Verilog语言编写程序,因此后缀名为.v。

6. 打碎网表(可选)若此网表为层次化的网表,需打碎网表,/doc/4012040478.html,L变为topcell.EXP,同时定义电源和地。

7. 生成cell及绑定网表(openLibAndBind)打开工作库,生成一个新的cell,绑定.EXP文件。

8. 层次化保护***Cell > Initialize Hierarchy InformationCell > Mark Module Instance Preserve9. 连接电源与地(connectPGnets)指定所有相关ports到电源或地。

数字集成电路设计方法、流程

数字集成电路设计方法、流程数字集成电路设计是指将数字电路功能进行逻辑设计、电路设计和物理布局设计,最终实现数字电路在集成电路芯片上的实现。

数字集成电路设计方法包括:1.设计需求分析:对于待设计的数字电路,首先需要了解设计需求。

明确电路所需的功能、性能指标、工作条件等,以确定电路设计的目标和约束条件。

2.逻辑设计:通过使用硬件描述语言(HDL)或者可视化设计工具,设计数字电路的功能逻辑。

在逻辑设计中,使用逻辑门、寄存器、计数器、状态机等基本逻辑单元,以及组合逻辑和时序逻辑的方法,实现所需功能。

3.电路设计:根据逻辑设计的结果,进行电路级设计。

包括选择和设计适当的电路模型、搭建电路拓扑、设计功耗、提高抗噪声性能等。

在电路设计中,需要考虑电源电压、电路延迟、功耗、抗干扰性能等因素。

4.物理布局设计:根据电路设计的结果,进行芯片级物理布局设计。

将电路中的逻辑单元和电路模块进行排布,设计电路的物理连接,并确定芯片的尺寸、引脚位置等。

物理布局设计需要考虑电路的功耗、面积、信号干扰等因素。

5.时序分析:对于复杂的数字电路,在设计过程中需要进行时序分析,以确保电路在各种工作条件下都能正常工作。

时序分析包括时钟分析、延迟分析、时序约束等。

6.仿真验证:在设计完成后,通过仿真验证电路的功能和性能。

使用仿真工具对电路进行功能仿真、逻辑仿真和时序仿真,验证设计的正确性。

7.物理设计:在完成电路设计和仿真验证后,进行物理设计,包括版图设计、布线、进行负载和信号完整性分析,以及完成设计规则检查。

8.集成电路硅掩模制作:根据物理设计结果,生成集成电路的掩模文件。

掩模文件是制造集成电路所需的制作工艺图。

9.集成电路制造:根据掩模文件进行集成电路的制造。

制造过程包括光刻、蚀刻、沉积、离子注入等工艺。

10.设计验证和测试:在集成电路制造完成后,进行设计验证和测试,确保电路的功能和性能符合设计要求。

数字集成电路设计的流程可以总结为需求分析、逻辑设计、电路设计、物理布局设计、时序分析、仿真验证、物理设计、硅掩模制作、集成电路制造、设计验证和测试等步骤。

IC设计流程课件

综合(Synthesis)

门级验证(Gate-level Verification)

后端设计(Back-end Design)

电路参数提取(Circuit Extraction)

版图后仿真(Post-layout Simulation)

物理

生产(Manufacture) 测试(Test)

数据形式与工具

目前DC可称作ASIC业界最流行的综合工具和 实际标准

09/11/08

6

西安邮电学院ASIC中心

静态时序分析工具

CMOS集成电路版图

静态时序分析技术是一种穷尽分析方法,可以 提取整个电路的所有时序路径,且不依赖于激 励,运行速度很快,占用内存很少,适合进行 超大规模的片上系统电路的验证,可以节省多 达20%的设计时间,但是静态时序分析存在的 问题在于不了解电路的动态行为。

09/11/08

11

西安邮电学院ASIC中心

版本管理工具

CMOS集成电路版图

在芯片开发流程中,文档、代码、网表 、工具配置脚本、工艺库甚至EDA工具本 身都在不断变更,版本控制的重要性日益 凸显。

常用的版本管理工具有CVS、Subvision 等,都包括windows和linux等版本。

09/11/08

IC设计流程课件

09/11/08

1

数字IC设计的流程

CMOS集成电路版图

逻辑

流程

需求分析(Requirement)

算法设计(Algorithm Optimization)

结构设计(Architecture Exploration)

RTL设计(RTL Design)

RTL验证(RTL Verification)

Astro过程1

Astro过程1、产生Milkyway的参考库1). Astro输入的数据文件:●技术文件(.tf)●参考库(参考库由以下的文件产生:1、技术文件(.tf);2、GDSII文件(包含了物理版图信息);3、综合库文件(.lib or .db 包含了cell的时序和功能))●设计库(Design_library),由以下文件产生:1、技术文件(.tf);2、GDSII文件(.gds 包含了物理版图信息);3、顶层设计文件(.tdf)包含了pin和port的信息。

4、约束文件(.sdc 包含了时序约束和时钟的定义,来自于综合过程);5、网表文件(.v or .vhd or .edf)包含V erilog、VHDL或者EDIF文件;6、设计库文件(.db)包含了网表,时序和设计规则约束。

2). Astro产生的数据文件●布局后产生的时序文件(design.sdf)●寄生信息(parasitic.spef or parasitic.spf)●优化过后的网表(.v(flattened)or .hv(hierarchical))●Layout文件(.gds)●(optional)cell 放置位置信息(.pdef)●(optional)网表和布局信息(.def)●(optional)版图、时序和技术信息3)Milyway 库目录Synopsys的Milyway 库目录是目录和文件的集合。

顶层目录是参考库或着是设计库。

参考库包含标准单元库、宏库和引脚库,这几个库构成一个设计。

1)数据库●CEL view:版图物理单元数据,包含输入的和astro产生的;●FRAM:版图数据提取出的布局布线数据;●SMASH:打平的CEL view;●HTV:版图的层次化时序数据,类似于和其它synopsys工具的一个接口;2)时序、功耗和逻辑文件夹●LM(Logic Model)view:时序,功耗和逻辑信息(新的格式提供了类似于TIM和PWR的数据信息)。

数字集成电路后端设计的一般流程

数字集成电路后端设计的一般流程下载温馨提示:该文档是我店铺精心编制而成,希望大家下载以后,能够帮助大家解决实际的问题。

文档下载后可定制随意修改,请根据实际需要进行相应的调整和使用,谢谢!并且,本店铺为大家提供各种各样类型的实用资料,如教育随笔、日记赏析、句子摘抄、古诗大全、经典美文、话题作文、工作总结、词语解析、文案摘录、其他资料等等,如想了解不同资料格式和写法,敬请关注!Download tips: This document is carefully compiled by theeditor. I hope that after you download them,they can help yousolve practical problems. The document can be customized andmodified after downloading,please adjust and use it according toactual needs, thank you!In addition, our shop provides you with various types ofpractical materials,such as educational essays, diaryappreciation,sentence excerpts,ancient poems,classic articles,topic composition,work summary,word parsing,copy excerpts,other materials and so on,want to know different data formats andwriting methods,please pay attention!数字集成电路后端设计是将前端设计的逻辑电路转化为实际的物理版图的过程,主要包括布局布线、时钟树综合、时序分析、功耗分析等步骤。

基于Astro的MIC总线控制器专用集成电路后端设计

P c n ot) 件 , l e dR u 软 a a e 提供 Cl—BsdD s n e l a e g e i F w实体设计部分 , l o 它可 以满足 五千万 门 , 时钟

动布局布线工具 , 例如 C dne aec 公司的 s E设计工

时产 生 。

片面积的增大将给时钟树 的设计 、 电源 网络设计 、

功耗控 制 等都带 来 困难 。而一 个好 的版 图布局 可 以节 约很 多 的芯 片 面积 , 因此 在 版 图设 计 中最 先 要考 虑 的就是芯 片 的布局 问题 。

要求 , 积 优 化 , 序 收 敛 , 耗 ,R Do , 面 时 功 I rp 串扰 ,

信号完整性 , 天线效应 ,S ……如何在规定 的时 ED

间里完成复杂的版图设计已经成为越来越多的设

计 人员 经常 要面 对 的问题 。 由此 出现 了很 多 的 自

3 简要介绍后端自 动布局布线 工具一 so At r

功的另一半呢?就是好 的方法, 也就是充分利用 工具。这也是我们在设计 中的一点体会。本文介 绍 的是使用 A t 自动布局布线工具 , 成 M C s o r 完 I 总线控制器远程模块专用集成电路的设计实例。

Co kS A t — a , so R i 提供 Pw r d vraot r l oe — r e l u i y

正 能力

・

tbt u n , r u dr t g使得大的电路设计可以更快的完成 i eo i

维普资讯

第5 第 期 2 3 卷

4 At s o的基 本 设 计 流 程 r

数字集成电路 后端设计 APR流程 之Astro

Astro布局布线流程随着深亚微米工艺的应用,逻辑门间的连线主导了电路的时序性能。

在实际设计时,设计者不再只是完成简单的逻辑门摆放和连线工作,更重要的是要降低实际的连线延迟,使最后的物理设计时序性能满足设计要求。

Astro是由Synopsys公司开发的物理设计软件,适用于现在的主流设计。

Astro提供了一套完整的物理设计流程,布局布线同时还具有时序优化功能,可以在一次流程中使设计电路达到预设指标。

但Astro步骤繁多、设定复杂,本章将针对Astro的设计流程借助一个简单的设计实例,对Astro一次流程中的主要步骤进行简单说明,使读者短时间内可以了解Astro。

一.数据准备本流程中需要的输入数据包括:网表文件(Netlist File)、时序约束SDC文件(Timing Constraint File)、参考库(Reference Library)、定义PAD TDF文件(Top Design File)、工艺tf文件(Technology File)。

其中工艺文件和部分参考库文件由Foundry提供。

1.网表:网表文件由前端工程师提供,格式一般采用verilog(.v)格式。

布局布线用网表文件一般由Design Compiler(DC)综合得到。

从DC中输出网表时,需要在脚本中如下命令,以满足Astro的要求。

2.时序约束文件:时序约束文件由前端工程师提供,格式一般采用SDC(.sdc)格式,SDC文件也由DC中输出。

时序约束文件中所加的约束只能针对顶层端口,文件中时钟定义可能需要加以修改。

因为从DC中输出的时钟定义一般不指定具体的单元及其端口,Astro通常很难根据这样的时钟定义找到真正的时钟源,因此需要先在网表中找到真正的时钟端口,并据此在SDC文件中加以修改。

例如,原来的SDC文件中时钟的定义片段为:原来的时序约束文件是给予综合的DC用,而不是用来布局布线的。

所以综合用的SDC文件中只给出了一个“产生时钟(create clock)”的命令,根据上面这段时序约束文件中的片段,Astro一般无法找到clk_div/clk,因此需要将“get_pin”的目标修改替换为在网表中的一个实际的时钟产生的单元:clk_div/CK01D1/Z.。

数字后端流程二【astro】[精华]

![数字后端流程二【astro】[精华]](https://img.taocdn.com/s3/m/cc2e23d9a0c7aa00b52acfc789eb172ded639939.png)

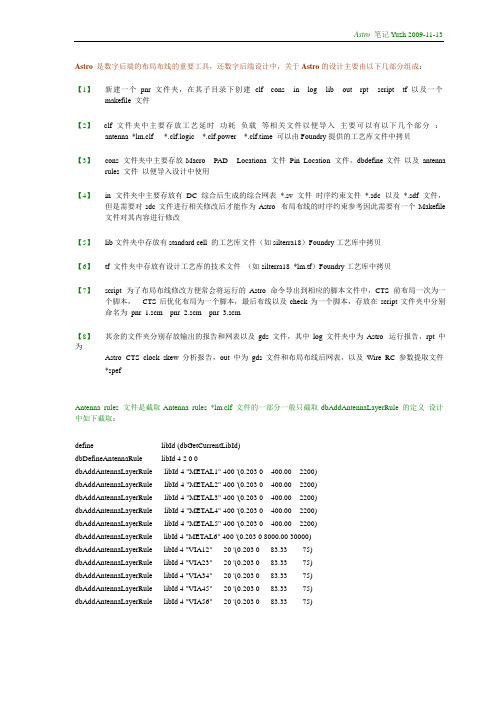

Astro 笔记Y uzh 2009-11-13Astro 是数字后端的布局布线的重要工具,还数字后端设计中,关于Astro 的设计主要由以下几部分组成:【1】新建一个pnr 文件夹,在其子目录下创建clf cons in log lib out rpt script tf 以及一个makefile 文件【2】clf 文件夹中主要存放工艺延时功耗负载等相关文件以便导入主要可以有以下几个部分:antenna_*lm.clf *.clf.logic *.clf.power *.clf.time 可以由Foundry 提供的工艺库文件中拷贝【3】cons 文件夹中主要存放Macro PAD Locationa 文件Pin Location 文件,dbdefine 文件以及antenna rules 文件以便导入设计中使用【4】in 文件夹中主要存放有DC 综合后生成的综合网表*.sv 文件时序约束文件*.sdc 以及*.sdf 文件,但是需要对sdc 文件进行相关修改后才能作为Astro 布局布线的时序约束参考因此需要有一个Makefile 文件对其内容进行修改【5】lib 文件夹中存放有standard cell 的工艺库文件(如silterra18)Foundry 工艺库中拷贝【6】tf 文件夹中存放有设计工艺库的技术文件(如silterra18_*lm.tf)Foundry 工艺库中拷贝【7】script 为了布局布线修改方便常会将运行的Astro 命令导出到相应的脚本文件中,CTS 前布局一次为一个脚本,CTS 后优化布局为一个脚本,最后布线以及check 为一个脚本,存放在script 文件夹中分别命名为pnr_1.scm pnr_2.scm pnr_3.scm【8】其余的文件夹分别存放输出的报告和网表以及gds 文件,其中log 文件夹中为Astro 运行报告,rpt 中为Astro CTS clock skew 分析报告,out 中为gds 文件和布局布线后网表,以及Wire RC 参数提取文件*spefAntenna_rules 文件是截取Antenna_rules_*lm.clf 文件的一部分一般只截取dbAddAntennaLayerRule 的定义设计中如下截取:define _libId (dbGetCurrentLibId)dbDefineAntennaRule _libId 4 2 0 0dbAddAntennaLayerRule _libId 4 "METAL1" 400 '(0.203 0 400.00 2200)dbAddAntennaLayerRule _libId 4 "METAL2" 400 '(0.203 0 400.00 2200)dbAddAntennaLayerRule _libId 4 "METAL3" 400 '(0.203 0 400.00 2200)dbAddAntennaLayerRule _libId 4 "METAL4" 400 '(0.203 0 400.00 2200)dbAddAntennaLayerRule _libId 4 "METAL5" 400 '(0.203 0 400.00 2200)dbAddAntennaLayerRule _libId 4 "METAL6" 400 '(0.203 0 8000.00 30000)dbAddAntennaLayerRule_libId 4 "VIA12"20 '(0.203 083.3375)dbAddAntennaLayerRule_libId 4 "VIA23"20 '(0.203 083.3375)dbAddAntennaLayerRule_libId 4 "VIA34"20 '(0.203 083.3375)dbAddAntennaLayerRule_libId 4 "VIA45"20 '(0.203 083.3375)dbAddAntennaLayerRule_libId 4 "VIA56"20 '(0.203 083.3375)dbDefine 文件是为了Astro 做时钟树综合优化时作准备的,在CTS 之前需调用该文件,Astro 做时钟树时只对它默认的DFF 的时钟管脚做相关处理一般是定义了clock 但我们设计需要对一些多扇出的复位信号scan 链信号做处理就需要专门声明下这也是时钟树需要处理的信号,就在dbDefine 做这样的声明,一般有同步复位、异步复位、scan_enable 以及宏单元的clk 信号,异步复位最常用需要做scan 链才定义SE,有Memory 时才定义clk,具体设置如下:(let* ((selectedlist (geGetSelectedSet (getEditWindow))))(for-each (lambda (x)(let* ((instName (dbFetchObjectField (geGetEditCell) x "name")))(dbDefineSyncPin (geGetEditCell) instName '( ("RN" "nonInvertRise" 0) ("RN" "invertRise" 0)) )(dbDefineSyncPin (geGetEditCell) instName '( ("SN" "nonInvertRise" 0) ("SN" "invertRise" 0)) );; (dbDefineSyncPin (geGetEditCell) instName '( ("SE" "nonInvertRise" 0) ("SE" "invertRise" 0)) );; (dbDefineSyncPin (geGetEditCell) instName '( ("CLK" "nonInvertRise" 0) ("CLK" "invertRise" 0)) )))selectedlist))tdf 文件定义相关的PAD 或者是PIN 的位置信息,坐标描述方法基本一致设计中根据实际的需要略有不同如下:tdfPurgePadConstrdefine step15define offset50define off0pin "clk"39 0 0"right"0(set! offset(+ step1 offset))pin "rstn"39 0 0"right"0(set! offset(+ step1 offset))pin "scan_mode"39 0 0"right"0(set! offset(+ step1 offset))pin "mic_fm_sel" 39 0 0 "right" 0 (set! offset(+ step1 offset))在Astro 布局布线时需要根据DC 综合时设置生成的时序约束文件对相关cel(l standard cell)进行布局优化,通常在Place 设置时考虑congestion 和time 因素,通常考虑关键性的时序路径,满足设计的时序约束条件,而对于非关键路径的cell 可以放置的远离些,增加延时,如果将非关键路径的cell 布局在关键时序路径布局区域就会对其产生影响,使其布线拥塞增加布线难度。

集成电路(IC)设计完整流程详解及各个阶段工具简介

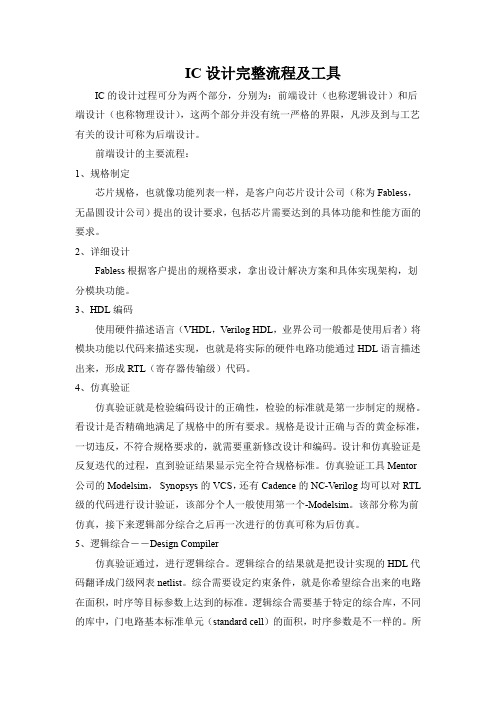

IC设计完整流程及工具IC的设计过程可分为两个部分,分别为:前端设计(也称逻辑设计)和后端设计(也称物理设计),这两个部分并没有统一严格的界限,凡涉及到与工艺有关的设计可称为后端设计。

前端设计的主要流程:1、规格制定芯片规格,也就像功能列表一样,是客户向芯片设计公司(称为Fabless,无晶圆设计公司)提出的设计要求,包括芯片需要达到的具体功能和性能方面的要求。

2、详细设计Fabless根据客户提出的规格要求,拿出设计解决方案和具体实现架构,划分模块功能。

3、HDL编码使用硬件描述语言(VHDL,Verilog HDL,业界公司一般都是使用后者)将模块功能以代码来描述实现,也就是将实际的硬件电路功能通过HDL语言描述出来,形成RTL(寄存器传输级)代码。

4、仿真验证仿真验证就是检验编码设计的正确性,检验的标准就是第一步制定的规格。

看设计是否精确地满足了规格中的所有要求。

规格是设计正确与否的黄金标准,一切违反,不符合规格要求的,就需要重新修改设计和编码。

设计和仿真验证是反复迭代的过程,直到验证结果显示完全符合规格标准。

仿真验证工具Mentor 公司的Modelsim,Synopsys的VCS,还有Cadence的NC-Verilog均可以对RTL 级的代码进行设计验证,该部分个人一般使用第一个-Modelsim。

该部分称为前仿真,接下来逻辑部分综合之后再一次进行的仿真可称为后仿真。

5、逻辑综合――Design Compiler仿真验证通过,进行逻辑综合。

逻辑综合的结果就是把设计实现的HDL代码翻译成门级网表netlist。

综合需要设定约束条件,就是你希望综合出来的电路在面积,时序等目标参数上达到的标准。

逻辑综合需要基于特定的综合库,不同的库中,门电路基本标准单元(standard cell)的面积,时序参数是不一样的。

所以,选用的综合库不一样,综合出来的电路在时序,面积上是有差异的。

一般来说,综合完成后需要再次做仿真验证(这个也称为后仿真,之前的称为前仿真)逻辑综合工具Synopsys的Design Compiler,仿真工具选择上面的三种仿真工具均可。

数字IC后端流程

11.Tape out。在所有检查和验证都正确无误的情况下把最后的版图GDSⅡ文件传递给Foundry厂进行掩膜制造。

2.布局规划。主要是标准单元、I/O Pad和宏单元的布局。I/O Pad预先给出了位置,而宏单元则根据时序要求进行摆放,标准单元则是给出了一定的区域由工具自动摆放。布局规划后,芯片的大小,Core的面积,Row的形式、电源及地线的Ring和Strip都确定下来了。如果必要 在自动放置标准单元和宏单元之后, 你可以先做一次PNA(power network analysis)--IR drop and EM .

6.ECO(Engineering Change Order)。针对静态时序分析和后仿真中出现的问题,对电路和单元布局进行小范围的改动.

7.Filler的插入(pad fliier, cell filler)。Filler指的是标准单元库和I/O Pad库中定义的与逻辑无关的填充物,用来填充标准单元和标准单元之间,I/O Pad和I/O Pad之间的间隙,它主要是把扩散层连接起来,满足DRC规则和设计需要。

8.布线(Routing)。Global route-- rack assign --Detail routing--Routing optimization 布线是指在满足工艺规则和布线层数限制、线宽、线间距限制和各线网可靠绝缘的电性能约束的条件下,根据电路的连接关系将各单元和I/O Pad用互连线连接起来,这些是在时序驱动(Timing driven ) 的条件下进行的,保证关键时序路径上的连线长度能够最小。--Timing report clear

那你可用write_milkway, read_milkway 传递数据。

4.时钟树生成(CTS Clock tree synthesis) 。芯片中的时钟网络要驱动电路中所有的时序单元,所以时钟源端门单元带载很多,其负载延时很大并且不平衡,需要插入缓冲器减小负载和平衡延时。时钟网络及其上的缓冲器构成了时钟树。一般要反复几次才可以做出一个比较理想的时钟树。---Clock skew.

百万门系统级芯片的后端设计

百万门系统级芯片的后端设计张玲;罗静【摘要】采用0.18 μm及以下工艺设计高性能的VLSI芯片面临着诸多挑战,如特征尺寸缩小带来的互联线效应、信号完整性对芯片时序带来的影响、时序收敛因为多个设计变量的相互信赖而变得相当复杂,使百万门级芯片版图设计师需深入物理设计,选用有效EDA工具,结合电路特点开发有针对性的后端设计流程.文章介绍了采用Synopsys公司Astro后端工具对一款百万门级、基于0.18 μm工艺SoC芯片后端设计的过程,分为后端设计前的数据准备、布局规划、电源设计、单元放置及优化、时钟树综合、布线等几个阶段进行了重点介绍.同时考虑到深亚微米工艺下的互联线效应,介绍了如何预防串扰问题以及在整个布局布线过程中如何保证芯片的时序能够满足设计要求.【期刊名称】《电子与封装》【年(卷),期】2010(010)005【总页数】5页(P25-29)【关键词】时钟树;串扰;时序分析;时序优化【作者】张玲;罗静【作者单位】中国电子科技集团公司第58研究所,江苏,无锡,214035;中国电子科技集团公司第58研究所,江苏,无锡,214035【正文语种】中文【中图分类】TN4021 引言集成电路后端设计过程是从RTL综合到GDSⅡ数据的实现过程,一个好的芯片版图设计为集成电路物理设计和实施奠定了好的基础。

随着集成电路工艺与设计技术的不断发展,系统级芯片SoC已成为当今IC的发展方向。

如何缩短SoC芯片的设计周期,同时解决芯片特征尺寸缩小、芯片规模达几百万甚至上千万、时钟频率提高以及电压降等因素使SoC芯片物理设计复杂度越来越高的问题,已成为版图设计师需面临的主要设计挑战。

用自动布局布线工具来完成芯片后端设计可以节省宝贵的设计时间,但后端设计绝不仅仅是自动化工具的掌握和应用,结合电路特点开发有针对性的后端设计流程对芯片的成功起着关键性作用。

本文介绍了采用Synopsys公司Astro后端工具对一款百万门级、基于0.18 μ m工艺SoC芯片后端设计的过程,其中包括了设计之前的数据准备、布局规划、电源设计、单元放置及优化、时钟树综合、布线过程,另外还介绍了如何预防串扰和如何保证芯片的时序能够满足设计要求。

集成电路设计完整流程详解

IC设计完整流程及工具IC的设计过程可分为两个部分,分别为:前端设计(也称逻辑设计)和后端设计(也称物理设计),这两个部分并没有统一严格的界限,凡涉及到与工艺有关的设计可称为后端设计。

前端设计的主要流程:1、规格制定芯片规格,也就像功能列表一样,是客户向芯片设计公司(称为Fabless,无晶圆设计公司)提出的设计要求,包括芯片需要达到的具体功能和性能方面的要求。

2、详细设计Fabless根据客户提出的规格要求,拿出设计解决方案和具体实现架构,划分模块功能。

3、HDL编码使用硬件描述语言(VHDL,Verilog HDL,业界公司一般都是使用后者)将模块功能以代码来描述实现,也就是将实际的硬件电路功能通过HDL语言描述出来,形成RTL(寄存器传输级)代码。

4、仿真验证仿真验证就是检验编码设计的正确性,检验的标准就是第一步制定的规格。

看设计是否精确地满足了规格中的所有要求。

规格是设计正确与否的黄金标准,一切违反,不符合规格要求的,就需要重新修改设计和编码。

设计和仿真验证是反复迭代的过程,直到验证结果显示完全符合规格标准。

仿真验证工具Mentor 公司的Modelsim,Synopsys的VCS,还有Cadence的NC-Verilog均可以对RTL 级的代码进行设计验证,该部分个人一般使用第一个-Modelsim。

该部分称为前仿真,接下来逻辑部分综合之后再一次进行的仿真可称为后仿真。

5、逻辑综合――Design Compiler仿真验证通过,进行逻辑综合。

逻辑综合的结果就是把设计实现的HDL代码翻译成门级网表netlist。

综合需要设定约束条件,就是你希望综合出来的电路在面积,时序等目标参数上达到的标准。

逻辑综合需要基于特定的综合库,不同的库中,门电路基本标准单元(standard cell)的面积,时序参数是不一样的。

所以,选用的综合库不一样,综合出来的电路在时序,面积上是有差异的。

一般来说,综合完成后需要再次做仿真验证(这个也称为后仿真,之前的称为前仿真)逻辑综合工具Synopsys的Design Compiler,仿真工具选择上面的三种仿真工具均可。

数字集成电路设计流程

数字集成电路设计是一个复杂而系统性强的工程,通常包括以下几个主要步骤:1. 确定需求在设计数字集成电路之前,首先需要明确设计的功能和性能要求,包括输入输出接口、逻辑功能、时序要求等方面的设计需求。

2. 概念设计通过对需求进行分析和理解,进行电路结构和功能的初步设计,确定电路的整体架构和模块划分,制定初步的电路设计方案。

3. 逻辑设计根据概念设计的结果,进行逻辑电路设计,包括逻辑门的选择、逻辑电路的设计与优化等,确保电路满足功能需求。

4. 电气特性设计在逻辑设计的基础上,进行电气特性设计,包括时序分析、电气参数分析等,保证电路在电气特性上符合要求。

5. 物理布局设计进行物理布局设计,确定芯片内各功能块的布局位置,考虑信号线路长度、时延等因素,使得布局紧凑且方便布线。

6. 时序分析与优化进行时序分析,保证电路中的时序要求得到满足,并对电路进行时序优化,减少时序迟滞,提高电路的性能。

7. 电路仿真与验证通过电路仿真软件对设计的电路进行仿真验证,包括功能仿真、时序仿真等,确保设计的准确性和可靠性。

8. 物理布线设计根据物理布局设计结果进行布线设计,连接各功能块之间的信号线路,考虑信号传输的稳定性和功耗等因素。

9. 版图设计生成版图设计,包括器件的排列、连线规划等,生成最终的版图文件,为后续的制造加工做准备。

10. 设计规则检查(DRC)和布局VS电气规则检查(LVS)进行设计规则检查和布局与电气规则检查,确保设计符合制造工艺要求和电气规范。

11. 前期验证进行前期验证,包括功能验证、时序验证等,确保设计符合需求,并进行必要的调整和优化。

12. 准备生产完成设计验证后,准备将设计文件交付给芯片制造厂商进行生产加工,最终完成数字集成电路设计流程。

以上是数字集成电路设计的主要流程,每个步骤都非常重要,需要经过严格的设计和验证。

在实际设计过程中,还会涉及到许多细节和技术要点,需要设计工程师具备扎实的专业知识和经验。

数字后端流程

数字后端流程1. 数据准备。

对于CDN 的Silicon Ensemble而言后端设计所需的数据主要有是Foundry厂提供的标准单元、宏单元和I/O Pad的库文件,它包括物理库、时序库及网表库,分别以.lef、.tlf和.v的形式给出。

前端的芯片设计经过综合后生成的门级网表,具有时序约束和时钟定义的脚本文件和由此产生的.gcf约束文件以及定义电源Pad的DEF(Desi gn Exchange Format)文件。

(对synopsys 的Astro 而言,经过综合后生成的门级网表,时序约束文件SDC 是一样的,Pad的定义文件--tdf ,.tf 文件--technology file,Foundry厂提供的标准单元、宏单元和I/O Pad的库文件就与FRAM, CELL view, LM view 形式给出(Milkway 参考库and DB, LIB file)2. 布局规划。

主要是标准单元、I/O Pad和宏单元的布局。

I/O Pad预先给出了位置,而宏单元则根据时序要求进行摆放,标准单元则是给出了一定的区域由工具自动摆放。

布局规划后,芯片的大小,Core的面积,Row的形式、电源及地线的Ring和Strip都确定下来了。

如果必要在自动放置标准单元和宏单元之后,你可以先做一次PNA(power netw ork analysis)--IR drop and EM .3. Placement -自动放置标准单元。

布局规划后,宏单元、I/O Pad的位置和放置标准单元的区域都已确定,这些信息SE(Silicon Ensemble)会通过DEF文件传递给PC(Ph ysical Compiler),PC根据由综合给出的.DB文件获得网表和时序约束信息进行自动放置标准单元,同时进行时序检查和单元放置优化。

如果你用的是PC +Astro那你可用write_milkway, read_milkway 传递数据。

数字后端流程二..

dbAddAntennaLayerRule_libId 4 "VIA12"20 '(0.203 083.3375) dbAddAntennaLayerRule_libId 4 "VIA23"20 '(0.203 083.3375) dbAddAntennaLayerRule_libId 4 "VIA34"20 '(0.203 083.3375) dbAddAntennaLayerRule_libId 4 "VIA45"20 '(0.203 083.3375) dbAddAntennaLayerRule_libId 4 "VIA56"20 '(0.203 083.3375)Astro 笔记Y uzh 2009-11-13Astro 是数字后端的布局布线的重要工具,还数字后端设计中,关于Astro 的设计主要由以下几部分组成:【1】新建一个pnr 文件夹,在其子目录下创建clf cons in log lib out rpt script tf 以及一个makefile 文件【2】clf 文件夹中主要存放工艺延时功耗负载等相关文件以便导入主要可以有以下几个部分:antenna_*lm.clf *.clf.logic *.clf.power *.clf.time 可以由Foundry 提供的工艺库文件中拷贝【3】cons 文件夹中主要存放Macro PAD Locationa 文件Pin Location 文件,dbdefine 文件以及antenna rules 文件以便导入设计中使用【4】in 文件夹中主要存放有DC 综合后生成的综合网表*.sv 文件时序约束文件*.sdc 以及*.sdf 文件,但是需要对sdc 文件进行相关修改后才能作为Astro 布局布线的时序约束参考因此需要有一个Makefile 文件对其内容进行修改【5】lib 文件夹中存放有standard cell 的工艺库文件(如silterra18)Foundry 工艺库中拷贝【6】tf 文件夹中存放有设计工艺库的技术文件(如silterra18_*lm.tf)Foundry 工艺库中拷贝【7】script 为了布局布线修改方便常会将运行的Astro 命令导出到相应的脚本文件中,CTS 前布局一次为一个脚本,CTS 后优化布局为一个脚本,最后布线以及check 为一个脚本,存放在script 文件夹中分别命名为pnr_1.scm pnr_2.scm pnr_3.scm【8】其余的文件夹分别存放输出的报告和网表以及gds 文件,其中log 文件夹中为Astro 运行报告,rpt 中为Astro CTS clock skew 分析报告,out 中为gds 文件和布局布线后网表,以及Wire RC 参数提取文件*spefAntenna_rules 文件是截取Antenna_rules_*lm.clf 文件的一部分一般只截取dbAddAntennaLayerRule 的定义设计中如下截取:define _libId (dbGetCurrentLibId)dbDefineAntennaRule _libId 4 2 0 0dbAddAntennaLayerRule _libId 4 "METAL1" 400 '(0.203 0 400.00 2200)dbAddAntennaLayerRule _libId 4 "METAL2" 400 '(0.203 0 400.00 2200)dbAddAntennaLayerRule _libId 4 "METAL3" 400 '(0.203 0 400.00 2200)dbAddAntennaLayerRule _libId 4 "METAL4" 400 '(0.203 0 400.00 2200)dbAddAntennaLayerRule _libId 4 "METAL5" 400 '(0.203 0 400.00 2200)dbAddAntennaLayerRule _libId 4 "METAL6" 400 '(0.203 0 8000.00 30000)Astro 笔记Y uzh 2009-11-13dbDefine 文件是为了Astro 做时钟树综合优化时作准备的,在CTS 之前需调用该文件,Astro 做时钟树时只对它默认的DFF 的时钟管脚做相关处理一般是定义了clock 但我们设计需要对一些多扇出的复位信号scan 链信号做处理就需要专门声明下这也是时钟树需要处理的信号,就在dbDefine 做这样的声明,一般有同步复位、异步复位、scan_enable 以及宏单元的clk 信号,异步复位最常用需要做scan 链才定义SE,有Memory 时才定义clk,具体设置如下:(let* ((selectedlist (geGetSelectedSet (getEditWindow))))(for-each (lambda (x)(let* ((instName (dbFetchObjectField (geGetEditCell) x "name")))(dbDefineSyncPin (geGetEditCell) instName '( ("RN" "nonInvertRise" 0) ("RN" "invertRise" 0)) )(dbDefineSyncPin (geGetEditCell) instName '( ("SN" "nonInvertRise" 0) ("SN" "invertRise" 0)) );; (dbDefineSyncPin (geGetEditCell) instName '( ("SE" "nonInvertRise" 0) ("SE" "invertRise" 0)) );; (dbDefineSyncPin (geGetEditCell) instName '( ("CLK" "nonInvertRise" 0) ("CLK" "invertRise" 0)) )))selectedlist))tdf 文件定义相关的PAD 或者是PIN 的位置信息,坐标描述方法基本一致设计中根据实际的需要略有不同如下:tdfPurgePadConstrdefine step15define offset50define off0pin "clk"39 0 0"right"0(set! offset(+ step1 offset))pin "rstn"39 0 0"right"0(set! offset(+ step1 offset))pin "scan_mode"39 0 0"right"0(set! offset(+ step1 offset))pin "mic_fm_sel" 39 0 0 "right" 0 (set! offset(+ step1 offset))在Astro 布局布线时需要根据DC 综合时设置生成的时序约束文件对相关cel(l standard cell)进行布局优化,通常在Place 设置时考虑congestion 和time 因素,通常考虑关键性的时序路径,满足设计的时序约束条件,而对于非关键路径的cell 可以放置的远离些,增加延时,如果将非关键路径的cell 布局在关键时序路径布局区域就会对其产生影响,使其布线拥塞增加布线难度。

eetop[1].cn_Astro使用操作流程

![eetop[1].cn_Astro使用操作流程](https://img.taocdn.com/s3/m/df121c669b6648d7c1c746c1.png)

Astro使用操作流程首先设置软件工作需要的环境,指令为:>source .cshrc将当前工作环境切换到根目录下,避免软件Astro与StarRC冲突。

图1接下来启动Astro软件,输入指令:Astro 。

打开该软件的界面(图1)。

然后首先要做好载入设计对象前的准备工作,所以先点击TOOLS选项下面的data prep选项使软件做好载入数据之前的准备。

图2然后选择netlist in 下的verilog in to cel 选项选择需要载入的对象库。

得到如下图3的选项卡,分别选择library name 、verilog file name、tech file name 以及对应高低电平1和0的电源和地的选项net name for 1’b1和net name for 1’b0。

其中verilog file name是后缀为.v的文件,tech file的文件后缀是tf(图4)。

图3 选择完以上路径后点击global net option给整个设计的VDD和GND定义,如图5所示。

然后选择选项reference lib 选择设计需要的参考工艺库CZ6H.3AL.tf(图6)。

这个库是除了工艺tech file以外仍然需要的库CZ6H_3AL_IO和CZ6H_ptf_5V_LIB,该库的后缀也为tf,位置位于找F/LIB/ps/_astro下面。

图4 图5图6完成以上操作后就可以选择设计所需要的设计库和单元了,在这里点击选择library和CELL选项下面的open就可以得到如图7 所示的简单版图布局了。

图7接下来可以对布局需要的版图位置进行设置了,在这里选择选项design setup下的set up floorplan进行版图位置的设置了,如图8所示。

Row core ratio选项一般选择1,决定了金属布线通道在芯片中占的布线通道的大小,当为1时表明金属布线通道不占用芯片周围的空间而是在芯片内部电路结构的上方走线。

XTY数值数据处理器的后端设计及验证

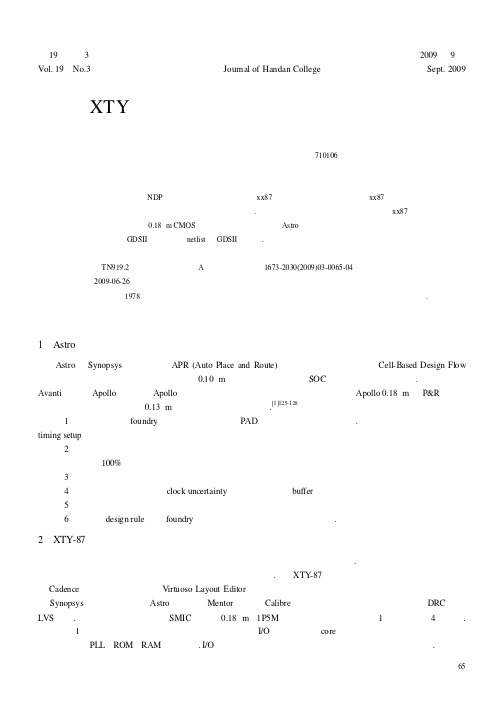

第19卷第3期邯郸学院学报2009年9月Vol.19No.3Journal of Handan College Sept.2009XTY数值数据处理器的后端设计及验证张俊峰,江涛(西安通信学院通信装备管理系,陕西西安710106)————————————————————————————————————————————摘要:数值数据处理器(NDP)芯片已问世多年,但对类xx87系列的研究仍在持续,由于xx87系列的技术难度以及国外技术封锁等原因,国内相应的对其研究成果极为鲜见.本文旨在开发具有我国自主知识产权与xx87完全兼容的专用芯片,采用的是先进的0.18m CMOS工艺,采用布局布线工具Astro按照版图规划、版图布局和版图布线的流程,生成最终的版图文件GDSII,实现了从netlist到GDSII的转换.关键词:数值数据处理器;逻辑综合;静态时序分析;时钟树;布局布线中图分类号:TN919.2文献标识码:A文章编号:1673-2030(2009)03-0065-04收稿日期:2009-06-26作者简介:张俊峰(1978—),男,河北邯郸人,西安通信学院通信装备管理系讲师,西安交通大学硕士研究生.————————————————————————————————————————————1Astro版图设计流程Astro是Synopsys公司开发的APR(Auto Place and Route)布局布线工具软件,提供Cell-Based Design Flow 实体设计部分,它可以满足五千万门,在0.10m及以下工艺线生产的SOC设计的工程和技术要求.它的前身是Avanti公司的Apollo,因此和Apollo具有相同的数据模型和用户环境,但它扩展了Apollo0.18m的P&R(布局布线)解决方案,能够实现0.13m及其以下工艺的物理设计.[1]125-128(1)读入网表,跟foundry提供的标准单元库和PAD库以及宏模块库进行映射.读入时序约束文件,设置好timing setup菜单,为后面进行时序驱动的布局布线做准备;(2)版图规划,规定了芯片的大致面积和管脚位置以及宏单元位置等粗略的信息,力求使后面布线能顺利满足布线布通率100%的要求和时序的要求;(3)根据时序和面积的要求摆放标准单元电路;(4)时钟树综合,为了降低clock uncertainty等而产生由许多buffer单元组成的“时钟树”;(5)自动布线,先对电源线和时钟信号布线,然后对信号线布线,目标是最大程度地满足时序和设计规则;(6)为满足design rule从而foundry能成功制造出该芯片而做的修补工作.2XTY-87芯片版图总体设计在数字集成电路设计的过程中,版图设计一般都是由自动布局布线工具进行的.通过工具将版图设计中的主要部分设计完成后,再根据实际要求对芯片版图进行适当修改.在XTY-87芯片的版图设计过程中,模拟部分采用Cadence公司的版图设计工具V irtuoso Layout Editor进行模拟版图设计,数字版图和数模混合版图的设计则采用Synopsys的版图设计工具Astro,最后用Mentor公司的Calibre对整个数模混合电路的版图进行了DRC以及LVS验证.设计时数字部分采用了SMIC公司的0.18m、1P5M数字工艺,布线时使用了1层多晶硅和4层金属.由图1可以看到,该芯片从版图平面结构上看主要由I/O、数字内核(core)以及一个或多个宏单元(其中包P A./.括模拟模块、LL、ROM、R M等)组成I O在整个芯片的外面部分,一般情况下其是连成一个环状的在版图设计时,要考虑到电源I/O 与输入输出I/O 之间的比例,使芯片中所有的I/O 都能得到足够的电压.数字集成电路的内核(core)为标准单元摆放的地方.在版图设计中,考虑到版图的紧凑性,一般采用double back ,相邻排(row)共用同一个电源或者地线,最大程度上减少了芯片的整体面积.在I/O 和内核之间有专门放置电源环的地方.电源环为整个芯片提供电源.按照芯片对功耗的要求,需要版图的电源线与地线都具有比较高的电流承载能力.[2]4宏单元的摆放需要针对不同的芯片设计要求,具体的情况具体分析.对于ROM 与RAM 而言,需要在其周围放置足够的电源带(Stripe),这样做的目的是为了使ROM 上的电源线能够以最短的距离连接到电源上.对于模拟版图模块,需要在其与相邻的数字版图之间添加隔离带加以隔离.3XTY-87芯片摆放标准单元主要包括预布局优化(Pre-Place )、布局优化(In-Place )与布局后优化(Post-Place ),Astro 通过这一步在给定的约束的基础上完成标准单元的布局.图2为完成了放置标准单元前后的本芯片的版图示意图:4XTY-87芯片实钟树综合在大规模集成电路中,大部分时序元件间的数据传输是由时钟信号同步控制的,时钟频率决定了数据处理和数据传输的速度,CTS (Clock Tree Synthesis )它是电路性能最主要的标志.当集成工艺进入深亚微米阶段,决定时钟频率的主要因素有两个,一是组合逻辑电路部分的最长路径的延时,一是同步元件内的时钟偏差(Clock Skew ),现代集成技术使得组合逻辑电路的开关速度提高,因此时钟偏差成为影响电路性能的制约因素.[3]12-15时钟树延迟模型很多,如自上而下的时钟树BB 算法,利用启发式方法划分电路,使各个电路总电容负载基本相同;自上而下的构造时钟树的KCR 算法等,迭代地连接相近的子对,解决时钟汇点不对称分布的问题.一般在ASIC 芯片设计中,运用正态随机分布的思想,来解决驱动元件的选择问题,即假定驱动元件都是按照正态分布原则,以某一基准驱动强度分布的,其相邻器件分布在最佳驱动值两边.以某一定值开始左右搜索,找出最佳的器件驱动范围.具体算法描述如下:2()2012()12t d x E x e d tπ=+∫为可能的最佳驱动时,抽象器件表征量进行两次搜索法:第一步,选择驱动能力居中的器件和其左右两图1芯片版图示意图图2放置标准单元前后的本芯片的版图d .部分相邻的器件{buf n/4,buf n/2,buf 3n/4}做时钟树综合、分析;第二步,选择驱动能力居中的器件,左右作进一步二次靠近,{buf n/8,buf n/2,buf 5n/8}将两次时钟树效果进行对比;也可以做远离算法,即每一步向外偏离.Astro 时钟树综合技术是建立在Astro 先进算法上的,它包括了参数提取,延时计算及时序分析等,在时钟树综合时,考虑了Blockage 及预布线.CTS (时钟树综合)[4]的目标,一是要减少多个触发器之间的时钟到达时间差,二是减少时钟树综合时,插入器件的延迟.CTS 是在驱动时钟的器件输出端到触发器之间插入多个buffer 或inverter 来实现的.命令格式为astCTS ,Astro 通过这一步在时钟树的路径上插入缓冲器或者反相器,完成时钟树综合的目标.CTS 完成后版图为图3所示:5XTY-87芯片版图布线设计全局布线为整个芯片中没有连接的线进行全局路径规划.此过程用一个两维的全局布线模型来模拟布线要求.布线工具使用标准单元的平均高度来设置全局布线模型的高度和宽度.在全局布线过程中并不将信号线布到实际的路径上,但是它会将连到每个全局布线模型上的线都记录下来,以便于进一步的布线.[5]95-1051)布线修复,在详细布线后,如果仍然存在很多违反设计规则的地方,就需要采用命令axgSearchRepair 对布线再进行修复.如果布线修复后仍然存在着DRC 错误,可以将Search Repair Loop 的数值加大,再进行一次修复.如果继续存在DRC 错误,就应该考虑对芯片重新进行版图规划,适当加大版图面积或者优化宏单元的摆放位置;[6]45-472)布线后时钟树的优化,由于布线会使时钟树综合后的clock skew 以及路径的延时发生微小的变化,因而需要对布线后的时钟树再次进行优化,命令格式为astPostRouteCTO ;3)布线优化,芯片的布线完成之后,时序问题会变差,所以在最后流片前需要进行优化.要对整个版图的布线进行优化,命令格式为:axgRoutOpt ;4)DFM (Design For Manufacture ),为满足design rule 从而foundry 能成功制造出该芯片而做的修补工作.这一步主要包括修补天线效应、单孔变成多孔、金属开槽、填充金属等.命令格式为:axgSearchRepair ,axgAddFillerCell ,axgSlotWire ,axgFillWireTrack.整个芯片的整体版图如图4所示:6结束语本论文的重点在于超大规模集成电路,尤其是深亚微米下协处理器设计流程的研究.XTY87-1的物理验证工作主要是基于公司的LD F K SR 3完成的之所以选择可编程器件作验证,是为了确保协处图3CTS完成后版图为图4芯片的整体版图Altera CP EP 10200C240-.理器XTY87-1与微处理器的接口通信时序兼容.同时也为了验证文中所述体系结构在实际应用中的有效性.最终验证表明基于CPLD的XTY87-1可完全替代xx87工作.最后,基于XTY87-1的实验结果表明(详细分析结果见附录):早先的xx87集成了近3万只晶体管,时钟频率为5MHZ,面积约5mm2,功耗为3w;我们XTY87-1芯片为86位浮点运算,面积1200m×1200m,最高工作频率达到70MHZ,数字部分功耗不到10mw,设计合理正确,具有较高的实用价值和一定的学术意义,综合性能优于同类芯片,达到了预先的设计要求.参考文献:[1]刘必慰,陈书明,汪东.先进微处理器体系结构及其发展趋势[J].计算机应用研究,2007,(3).[2]Kashfi F,Mehdi Fakhraie S.Implementation of a high-speed low-power32-bit adder in70nm t echnology[C].2006.[3]于海,樊晓桠,张盛兵.32位RISC微处理器FPGA验证平台设计与实现[J].计算机工程与应用,2007,(5).[4]R L Hummel.80x86处理器和80x87协处理器大全[M].北京:电子工业出版社,1994.[5]Ferretti M,Ozdag R O,Beerel PA.High performance asynchronous ASIC back-end design flow using s i ngle-track full-buffer standard cells[C].2004.[6]Rabaey J M C A,Ni kolic B.Digi tal Integrated Circuits-A Design Perspective[M].New Je rs ey:Pretice Hall,2003.Back-end Design and V erification of XTY NDPZHANG Jun-feng,JIANG Tao(Department of Communication and Administration,Xi’an Communication Institute PLA,Xi’an,710106,China)Abstr act:With the development of computer network,network security has also become an important issue.The necessary of network security was first developed and based on a framework for network security system design put forwarded,detailed analysis of the phase of network security design is made in this paper,and architecture model and policy management implemented mode land process of design are given,which hangs security architecture,security policy implement and the enforced mechanism of network security together.We built the final layout file after the design flows such as floorplan,placement and routing by using Astro which is the P&R tools of Synopsys.We translate the netlist to GDSII after layout design.K ey wor ds:numeric data processor;logic synthesis;static timing analysis;clock tree;P&R。

数字后端版图设计

数字后端设计流程-9 布线

第二步 布线通道分配

在global route 时已经将信号线分配到每个GRC,而track assignment旳 功能就是将这些信号线在分配到每个track上,决定每条线要走旳途径。 Track assignment是以整个芯片为处理单位来作规划,尽量绕出又长又 直且via数目至少旳绕线。

Formal Verification (ECO Netlist vs

CT Inserted Netlist)

Post-layout STA

Power check

Timing OK? Yes

Tape Out

DC MODELSIM MBISTARCHITECT FORMALITY

PT

Astro AstroRail FORMALITY

数字后端设计流程-5 布局

一般来说cell面积旳拥有率控制在70%左右, 布线旳时候不会引起拥塞。

数字后端设计流程-5 时钟树和复位树综合

时钟树综合旳目旳: 低skew 低clock latency

数字后端设计流程-5 时钟树和复位树综合

芯片中旳时钟网络要驱动电路中全部旳时序单元,所以 时钟源端门单元带载诸多,其负载延时很大而且不平衡, 需要插入缓冲器减小负载和平衡延时。时钟网络及其上 旳缓冲器构成了时钟树。一般要反复几次才能够做出一 种比较理想旳时钟树。

布线工具会自动进行布线拥塞消除、优化时序、减 小耦合效应、消除串扰、降低功耗、确保信号完整性等 问题。

Astro的布局与布线_经验总结

Astro中的布局布线流程和注意事项作者:CC,Zhan版本号日期备注基本流程和注意事项;0.5 2005-4-10主要是H053A流片的经验总结;Astro中的布局布线流程Asro是功能强大的布局布线工具,其基本流程如下:1、读入网表,跟foundry提供的标准单元库和Pad库以及宏模块库进行映射;2、整体布局,规定了芯片的大致面积和管脚位置以及宏单元位置等粗略的信息;3、读入时序约束文件,设置好timing setup菜单,为后面进行时序驱动的布局布线做准备;4、详细布局,力求使后面布线能顺利满足布线布通率100%的要求和时序的要求;5、时钟树综合,为了降低clock skew而产生由许多buffer单元组成的“时钟树”;6、布线,先对电源线和时钟信号布线,然后对信号线布线,目标是最大程度地满足时序;7、为满足design rule从而foundry能成功制造出该芯片而做的修补工作,如填充一些dummy等。

这七大步骤是基本的流程,其中每大步骤里面包含很多小的步骤,并根据各个不同的芯片特点而有很多的变化。

各大步骤的流程依次如下:该流程如下:1、创建库,库的名称最好就是前端输入的网表文件的名称,如H053A,需要提供技术文件,如smic18_6lm.tf,注意把大小写设置为敏感;命令是cmCreateLib2、添加参考库,主要包括foundry提供的(也可能是第三家公司帮忙foundry做的库,如Artisan的库)标准单元库和IO库,以及前端定制的宏单元库,如cache,RAM,ROM,PLL等;添加完毕之后显示参考库以确认;命令是cmRefLib和cmShowRefLib3、读入前端网表,注意拿到网表后往里面手动添加电源PAD和CORNER单元,读入的应该是经过这步添加的网表;命令是auVerilogIn4、展开网表,因为一般读入的是层次化的网表,需要flatten;命令是cmCmdExpand5、打开第一步创建的库并且新创建一个CELL,名字也最好是跟网表文件名称一致;命令是geOpenLib和geCreateCell6、绑定,就是把展开的网表绑定到刚创建的CELL中,这样,这个CELL就包含了网表中的所有元件;命令是axgBindNetlist7、保存网表的层次化信息到Astro的数据库中;这样布局布线结束后能输出层次化的网表进行后仿。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

Astro布局布线流程随着深亚微米工艺的应用,逻辑门间的连线主导了电路的时序性能。

在实际设计时,设计者不再只是完成简单的逻辑门摆放和连线工作,更重要的是要降低实际的连线延迟,使最后的物理设计时序性能满足设计要求。

Astro是由Synopsys公司开发的物理设计软件,适用于现在的主流设计。

Astro提供了一套完整的物理设计流程,布局布线同时还具有时序优化功能,可以在一次流程中使设计电路达到预设指标。

但Astro步骤繁多、设定复杂,本章将针对Astro的设计流程借助一个简单的设计实例,对Astro一次流程中的主要步骤进行简单说明,使读者短时间内可以了解Astro。

一.数据准备本流程中需要的输入数据包括:网表文件(Netlist File)、时序约束SDC文件(Timing Constraint File)、参考库(Reference Library)、定义PAD TDF文件(Top Design File)、工艺tf文件(Technology File)。

其中工艺文件和部分参考库文件由Foundry提供。

1.网表:网表文件由前端工程师提供,格式一般采用verilog(.v)格式。

布局布线用网表文件一般由Design Compiler(DC)综合得到。

从DC中输出网表时,需要在脚本中如下命令,以满足Astro的要求。

2.时序约束文件:时序约束文件由前端工程师提供,格式一般采用SDC(.sdc)格式,SDC文件也由DC中输出。

时序约束文件中所加的约束只能针对顶层端口,文件中时钟定义可能需要加以修改。

因为从DC中输出的时钟定义一般不指定具体的单元及其端口,Astro通常很难根据这样的时钟定义找到真正的时钟源,因此需要先在网表中找到真正的时钟端口,并据此在SDC文件中加以修改。

例如,原来的SDC文件中时钟的定义片段为:原来的时序约束文件是给予综合的DC用,而不是用来布局布线的。

所以综合用的SDC文件中只给出了一个“产生时钟(create clock)”的命令,根据上面这段时序约束文件中的片段,Astro一般无法找到clk_div/clk,因此需要将“get_pin”的目标修改替换为在网表中的一个实际的时钟产生的单元:clk_div/CK01D1/Z.。

修改SDC片段结果如下:3.参考库:参考库包括标准单元(STD)库、输入输出单元(I/O)库和IP库。

前两种都由Foundary提供,IP库可以由Foundary提供,也可以用户自己建立。

举一个简单的例子简要说明下IP库的建立。

在某些项目中,比较典型的用户自定义RAM IP模块。

使用Memory Compiler可以产生GDSII文件,需要自己建立Milkyway格式IP库以作为参考库代入Astro设计流程。

其具体步骤为:1.运行Memory Compiler,产生需要的Memory block,具体参考memory compiler的使用手册。

2.运行Astro,把GDSII文件导入,Smash,进行Blockage Pin Via Extraction后产生FRAM view。

3.在Astro中把memory compiler产生的lib文件转换成clf文件并读入,或者读入.db文件,生成TIM/LM view。

关于导入GDSII文件具体参考《milkyway database preparation》,需要注意两点:1.层号(Layer Number)问题,不同的工艺下的相同层的层号可能不同。

如若不同,需要写一个映射文件在读入GDSII文件转换。

2.特殊自定义模拟单元的IP库的,ib文件、clf文件等需要自己写,由Astro读入生成IP库的LM view,若仅由GDSII文件生成一个Fram view,IP库的Milkyway格式的库中没有TIM view,在时序驱动(Timing Driven)流程中处理到和这些模块相关的Net/Port的时候会有许多相关的Warning或Timing Error。

为了消除这些Warning和Timing Error,就需要把相应的.lib或者.db文件导入库中,以生成一个TIM/LM view。

这时可以简单地手工写一个lib文件,导入库中即可。

例如:4.TDF文件:这里用到的TDF文件定义了Pad的排列顺序。

需要注意的是:综合产生的网表中没有定义某些没有逻辑意义的Pad,如corner cell,split cell以及power cell的顺序,这些Pad和I/O Pad的摆放边和顺序都在该TDF文件中定义。

二.开始(Setup:Design Setup + Timing Setup)在Terminal中,引导到运行目录下内输入命令:启动软件后,很多布局布线步骤都可以写成脚本,直接载入运行即可。

这样既免去了一次次点鼠标提高工作效率,也减少手工操作可能会带来的失误。

该命令“Astro”也包括“-logd、Astro,随后章节中多采用基本的步骤是:1.建立库(cmCreateLib)Library→Create在弹出“Create Library”窗口中,填上“Library Name、Technology File Name”相应的表格。

“Library Name”是设计库的名字,库是设计单元的集合。

“Technology File Name”即为第一节数据准备中提及的工艺tf文件和文件引导路径。

一般前端综合DC输出网表是对大小写敏感的,因此建立库的时候要注意把“Set Case Sensitive”选项选上(默认)。

图2-1点击“OK”按钮,Library建立成功。

Astro启动目录下会产生一个以“Library Name”命名的文件夹,随后的单元的设计数据都将会保存在本目录下。

图2-22.读入Verilog(auVerilogToCell)1.在Astro的主窗口内输入命令这条命令集合了旧版Astro设计流程中的加上参考库(cmRefLib)、读入网表(auVerilogIn)和打平网表(cmCmdExpand)等几个个步骤。

图2-32.在弹出窗口中填入“Library Name、Cell Name、Verilog File Name”。

“Library Name”是刚刚建立的设计库名。

“Cell Name”单元名即随后具体的设计对象。

“Verilog File Name”是第一节数据准备中提及的网表文件和文件引导路径。

3.点击“Reference Library”按钮,顺序添加几个参考库后,点击“Hide”按钮隐藏窗口。

“Reference Library”是第一节数据准备中提及的参考库文件。

参考库可以是一个或者多个,如STD、IO、IP等。

图2-44.点击“Global Net Options”按钮,“Net Name、Port Pattern”分别都设置为“VDD、VSS”,并且“Apply”一下,点击“Hide5.点击“OK”按钮。

网表将被参照参考库或Astro默认的库读入,在设计库文件夹下产生一个以“Cell Name”命名的文件夹,其中包含几种设计观点cell view。

图2-53.打开库(geOpenLib)Library→Open在弹出窗口中填入“Library Name”,点击“OK”按钮。

图2-64.打开单元(geOpenCell)Cell→Open打开本节第2步中生成的单元,图2-7为弹出的窗口视图。

图2-7为使图片清晰,截图中,笔者将结构视图内容部分进行了反色处理。

可以发现,该部分由一些大小不一的方框“堆积”而成,这些方框就是STD、IO、IP单元的Fram view。

由于设计尚未进行布局规划(floorplan),它们都被“堆积”在视图的左下角(low-left)。

若网表是层次化的,还需要使用(astMarkHierAsPreserved)命令来标记保留层次化,至此设计启动部分(Design Setup)流程结束。

5.装载SDC文件(ataLoadSDC) Timing→Load SDC1.在Astro的主窗口内输入命令:推荐在装载SDC文件前移除设计中所有的时序相关的约束。

2.在弹出窗口中“SDC File Name”表格中填入,SDC文件名极其引导路径。

SDC文件是第一节数据准备中提及的时序约束文件。

图2-83.点击“OK”按钮载入SDC文件。

图2-96.时序设置(atTimingSetup)Timing→Timing Setup在弹出窗口中,根据需要选择相应的选项,设置相关环境参数、优化目标。

注意!这些设置选项在流程的后面可能会有改变。

另外本流程中部分选项设定使用系统默认,设定不作改变部分不在图2-10中作图示方式列出。

图2-10 7. 保存单元数据(geSaveAs )Cell →Save As填入自定义单元名称,阶段性保存设计数据。

图2-11补充说明:综合产生的网表一般不包含电源、地的Pad 、Corner 、Split 、Power 等单元,可以利用(geAddCell )Create →Cell 命令在设计单元中建立这些单元。

笔者个人偏好在DC 输出的Verilog 网表中手动修改网表,以引用Reference Library 中的单元的方式在网表中加入这些Cell 。

三.布局规划(Floorplan)Floorplan在整个流程中处于十分重要的地位,Floorplan不单指Astro中的axgPlanner命令,还包括macro的放置,电源布线设计(Power Plan)。

因为Floorplan一旦确定,则整个芯片的面积就已经确定了。

Floorplan的质量也与整个设计的timing和布通率有着密切的关系。

流程中的反复主要是发生在这一步中,如果这本步骤开始就规划得比较好,则随后的以便通过一步流程通过的几率就较高;反之,很可能出现完成了随后若干步骤后,发现设计无法通过修正继续布通的情况,那时只能返回到这一步,造成很大时间人力的浪费。

1.载入TDF文件(axgLoadTDF)Design Setup→Load TDF将设计单元名称和TDF文件以极其路径填入弹出表格中的“Cell Name、TDF File Name”,此处TDF文件即为是第一节数据准备中提及的TDF文件。

图3-12.全局的Floorplan(axgPlanner)Design Setup→Set Up Floorpan图3-2如图3-2中的参数来完成设置,并且点击“OK”完成初步的布局规划。

本设计流程中包含了一些的macro单元,不能简单地通过指定根据core的利用率(Aspect ratio)来让Astro决定设计的尺寸,而只能通过指定宽/长(width/hight)来确定。