课题十六 二进制计数器

二进制计数器

(a)Sample mode: The output follows the input (b)Hold mode: The output is held constant

until sample mode is resumed

(输出保持不变直到采样方式恢复)

2、The main application of S/H circuits is to hold the input signal to an ADC constant during conversion

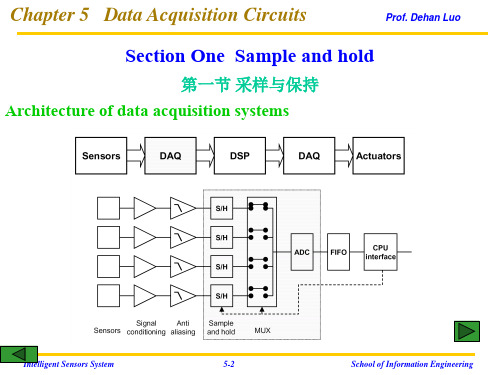

Chapter 5 Data Acquisition Circuits

Prof. Dehan Luo

Section One Sample and hold

第一节 采样与保持 Architecture of data acquisition systems

Intelligent Sensors System

Intelligent Sensors System

5-5

School of Information Engineering

Chapter 5 Data Acquisition Circuits

Prof. Dehan Luo

Sample & hold and Basic S/H circuit (Cont.)(续)

2、Operation(工作过程)

Counter is reset Analog input is sampled While VA > VB counter increments When VA=VB counter stops and binary code is available at the output (当VA=VB ,计数器停止计数, 输出端输出二进制数)

EDA论文用程序输入法设计16位二进制加法计算器

用程序输入法设计16位二进制加法计算器班级 xxxx 姓名 xxx 学号 xxxxx内容提要:计数器是数字系统中使用较多的一种时序逻辑器件。

计数器的基本功能是统计时钟脉冲的个数,即对脉冲实现计数操作。

计数器也可以作为分频、定时、脉冲节拍产生器和脉冲序列产生器使用。

计数器的种类很多,按构成计数器中的各触发器是否使用一个时钟脉冲源来分,可分为同步计数器和异步计数器;按进位体制的不同,可分为二进制计数器、十进制计数器和任意进制计数器;按计数过程中数字增减趋势的不同,可分为加法计数器、减法计数器和可逆计数器;还有可预制数和可编计数器等等。

本次课程设计将利用众多集成电路软件软件中的Quartus II软件,使用VHDL语言编程完成论文《用程序输入方法设计一个16位二进制加法计数器》,调试结果表明,所设计的计数器正确实现了计数功能。

关键词:二进制;加法计数器;VHDL语言1问题分析计数器是数字系统中使用较多的一种时序逻辑器件。

计数器的基本功能是统计时钟脉冲的个数,即对脉冲实现计数操作。

其工作原理可概述为:当输入时钟脉冲的一个上升沿(也可以是下降沿)来临时,二进制数据的低一位加1(或减1),并向高位进1(或借1)。

在没有外部约束条件时,计数器可进行与其二进制位数对应的数值的相应进制的自循环计数,如位数为3的计数器可进行8进制的自循环加法或减法计数。

可根据需要来设置计数器的位数,并通过外部约束条件来人为设定计数器的计数模数,来得到计数进制符合需要的N 进制计数器。

所谓N 进制计数器,是指一个计数器的计数过程,在经历时钟脉冲信号的个为N 之后,二进制数据又回到初始状态的计数器。

表1.1计数器的状态表图1.1计数器的状态图2 设计原理本论文所设计的16位二进制加法计数器,其中16位计数器输出Q[15..0]=0000000000000000,时钟CLK 的上升沿到来时,计数器处于预置工作状态,输出Q[15..0]= D[15..0],D[15..0]是16位并行数据输入端,COUT 是进位输入端,当UPDOWN=0(进行加法操作)且输出Q[15..0]=1111111111111111时,COUT=1表示进位输出。

数电课程设计题目

数电课程设计题目

数字电路课程设计题目有很多种,以下是一些常见的题目和拓展:

1. 设计一个数字时钟芯片,包括时钟输入、分频器、计时器、计秒器等功能。

拓展:了解时钟芯片的内部结构和原理,包括振荡器、分频器、计数器等,以及如何将它们组合成一个完整的数字时钟芯片。

2. 设计一个多位加法器电路,要求能够实现任意两位数字的加法运算。

拓展:了解不同类型的加法器,如二进制加法器、八路加法器、多位加法器等,以及如何将它们组合成一个完整的加法器电路。

3. 设计一个数字计数器电路,要求能够计数到任意整数。

拓展:了解不同类型的计数器,如二进制计数器、十进制计数器、十六进制计数器等,以及如何将它们组合成一个完整的计数器电路。

4. 设计一个数字滤波器电路,要求能够滤除指定频率范围内的频率分量。

拓展:了解不同类型的滤波器,如低通滤波器、高通滤波器、带通滤波器、带阻滤波器等,以及如何将它们组合成一个完整的滤波器电路。

5. 设计一个数字信号发生器电路,要求能够产生指定频率和振幅的数字信号。

拓展:了解数字信号发生器的基本原理和内部结构,以及如何将

它们组合成一个完整的数字信号发生器电路。

以上是一些常见的数字电路课程设计题目,希望能够提供一些灵感和帮助。

当然,具体的题目类型和难度会根据课程的要求和学生的技术水平而有所不同。

十六进制计数器

在数字电路中,将能够实现计数逻辑功能的器件称为计数器,计数器计数的脉冲信号是触发器输入的CP信号。

数字电路所接触到的计数器种类繁多,对计数器按进制来分有二进制,十进制和任意进制的计数器;按触发方式来分有同步和异步计数器;按计数的规则来分有加法和减法计数器等。

描述计数器的一个重要参数称为计数器的计数容量。

计数器计数器容量的定义是:计数器所能够记忆的输入脉冲个数。

因例4-1所分析的时序逻辑电路能够记忆的输入脉冲个数是5,所以,例4-1所示电路的计数容量为5,又称为5进制加法同步计数器。

因例4-2所示的电路能够记忆的输入脉冲个数是4,所以,例4-2所示电路的计数容量是4。

又因为该电路计数的规则是加法或减法可逆的,所以,例4-2所示的电路为同步4进制加/减计数器。

因例4-3所示的电路能够记忆的输入脉冲个数是10,所以,该电路的计数容量是10。

又因为该电路的触发信号是异步的,所以,例4-3所示的电路又称为十进制加法异步计数器。

计数器的容量又称为计数器的长度或模,简称计数容量。

由上面的分析可见,计数容量描述了计数器电路所能够输出的有效状态数。

若用n表示计数器输出的二进制数的位数,则该计数器的最大计数容量M为2n。

例4-1,例4-2和例4-3详细的介绍了时序逻辑电路的分析方法,研究时序逻辑电路的问题也是分析和设计,下面以计数器为例子来介绍时序逻辑电路的设计方法。

设计时序逻辑电路的方法与设计组合逻辑电路的方法相似,第一步都是进行逻辑问题的抽象。

在组合逻辑电路的设计中,将具体的逻辑问题抽象成真值表,而在时序逻辑电路的设计中,应将具体的逻辑问题抽象成状态转换图。

第二步都是画出卡诺图,并利用卡诺图进行逻辑函数式的化简。

在组合逻辑电路的设计中,化简所得到的结果为最简与或式,而在时序逻辑电路的设计中,化简所得到的结果为时序逻辑电路中触发器的状态方程。

第三步都是选择器件搭电路,在组合逻辑电路的设计中,通常用得.摩根定理处理最简与或式,将最简与或式转化成与非-与非式来搭电路;在时序逻辑电路的设计中,应先选定所用的触发器器件,然后根据化简得到的触发器状态方程列出相应的驱动方程,根据驱动方程来搭建电路。

二进制计数器

19

5.2.2 同步二进制计数器

同步计数器中,各触发器的翻转与时钟脉冲同步。 同步计数器的工作速度较快,工作频率也较高。

1.同步二进制加法计数器

(1)设计思想:

① 所有触发器的时钟控制端均由计数脉冲CP输

入,CP的每一个触发沿都会使所有的触发器状态更

新。

② 应控制触发器的输入端,可将触发器接成T

触发器。

2019/5/2

(a) 电路图 (b)时序图

12

2.异步二进制减法计数器

必须满足二进制数的减法运算规则:0-1不够减, 应向相邻高位借位,即10-1=1。

组成二进制减法计数器时,各触发器应当满足: ① 每输入一个计数脉冲,触发器应当翻转一次 (即用T′触发器); ② 当低位触发器由0变为1时,应输出一个借位信 号加到相邻高位触发器的计数输入端。

等效十进制数 0 1 2 3 4 5 6 7 0

2019/5/2

8

④ 时序图

图5-13 3位二进制加法计数器的时序图

2019/5/2

9

⑤ 状态转换图

圆圈内表 示Q2Q1Q0

的状态

用箭头表 示状态转 换的方向

图5-14 3位二进制加法计数器的状态转换图

2019/5/2

10

⑥ 结论

如果计数器从000状态开始计数,在第八个计 数脉冲输入后,计数器又重新回到000状态,完成 了一次计数循环。所以该计数器是八进制加法计 数器或称为模8加法计数器。

24

2.同步二进制减法计数器

(1)设计思想: ① 所有触发器的时钟控制端均由计数脉冲CP输入,

CP的每一个触发沿都会使所有的触发器状态更新。 ② 应控制触发器的输入端,可将触发器接成T触发

16进制同步加法计数器

目录1加法计数器 (2)1.1题目内容 (2)1.2状态图 (2)1.3选择触发器,求时钟方程,输出方程和状态方程 (2)1.4求驱动方程 (5)1.5画逻辑电路图 (6)2序列脉冲发生器 (7)2.1题目内容 (7)2.2状态图 (7)2.3选择触发器,求时钟方程,输出方程和状态方程 (8)2.4求驱动方程 (9)2.5画逻辑电路图 (10)3总结 (11)4参考文献 (11)1 加法计数器1.1题目内容设计一个十六进制同步加法计数器,具有清零和置位功能1.2状态图根据二进制递增计数的规律,可画出如图1所示的十六进制加法讣数器的状态图。

/ 0 / 0 / 0 / 0 / 0 / 0 /oOOOO«^OOO1^^OO1O«^OO11^^O1OO^^O1O1—^0110^^0111/o / 0111" 1110・ 110" 1100・ 1011・1010・ 100" 1000/ 0 / 0 / 0 / 0 / 0 / 0 / 0 /c排列:CF Q: Q: Qo图1十六进制同步加法计数器的状态图1.3 选择触发器,求时钟方程,输出方程和状态方程选择触发器山于JK触发器功能齐全,使用灵活,故选用4个时钟下降沿触发的边沿JK触发器。

求时钟方程III于要求构成的是同步计数器,显然各个触发器的时钟信号都应使用输入计数脉冲CP,即CPo=CPi=CP2=CP3=CP求输出方程山图1所示状态图可直接得到C二Q? Q: QiQo求状态方程根据图1所示状态图的规定,可画出如图2所示的计数器次态卡诺图。

\ Q-Qo Q3Q2 \ 00 01 11 100001001001000011010101101000011111011110000011111001101011001011图2十六进制同步加法计数器次态的卡诺图把图2所示卡诺图分解开,便可得到如图3所示各个触发器次态的卡诺图。

什么是计数器如何设计一个二进制计数器

什么是计数器如何设计一个二进制计数器计数器是一种电子设备,用于记录和显示特定事件或数据的次数。

它可以根据输入信号的变化来实现计数,常见的应用包括时钟、定时器、频率计等。

二进制计数器是一种特殊类型的计数器,它的计数方式采用二进制编码。

每当触发信号发生变化时,计数器的值会根据预设的计数规则进行自动递增或递减。

二进制计数器常用于电子数字电路中,以表示和控制各种复杂的数字逻辑。

设计一个二进制计数器需要考虑以下几个方面:1. 计数位数:确定计数器的位数决定了其能够表示的最大数字范围。

一般而言,n位二进制计数器可以表示0到2^n-1之间的数字。

2. 计数方向:确定计数器递增或递减的方向。

递增计数器按照二进制编码规则,顺序增加;递减计数器则按照相反的顺序递减。

3. 触发条件:确定计数器何时开始计数。

可以根据时钟信号、外部触发信号和逻辑运算等条件来触发计数器的计数。

4. 计数模式:确定计数器的工作模式,包括连续计数和循环计数。

连续计数模式下,计数器会一直递增或递减,直到达到最大或最小值;循环计数模式下,计数器会在达到最大或最小值后返回到初始值重新计数。

5. 输出接口:设计计数器的输出接口,以便将计数器的结果用于其他逻辑电路。

常见的接口形式包括二进制数码、BCD码、七段显示等。

根据上述要求,设计一个简单的4位二进制递增计数器,以实现从0到15的计数:首先,确定计数器的位数为4位,即可以表示0到15的数字。

其次,计数方向设置为递增模式,按照二进制编码规则从0000到1111。

然后,通过时钟信号触发计数器的计数。

可以将时钟信号作为计数器的输入,每当时钟信号发生一个上升沿或下降沿,计数器的值就会加1或减1。

最后,将计数器的结果输出到一个四位二进制数码管,以显示当前计数器的值。

通过以上设计,一个简单的4位二进制递增计数器便实现了。

它可以用于时钟、定时器、频率计等各种应用场景,并且可以根据需要进行扩展和优化,以满足更为复杂的计数需求。

二进制计数器

二进制计数器计数器是数字系统中用得较多的基本逻辑器件。

它不仅能记录输入时钟脉冲的个数,还可以实现分频、定时、产生节拍脉冲和脉冲序列等。

例如,计算机中的时序发生器、分频器、指令计数器等都要使用计数器。

计数器的种类很多。

按时钟脉冲输入方式的不同,可分为同步计数器和异步计数器;按进位体制的不同,可分为二进制计数器和非二进制计数器;按计数过程中数字增减趋势的不同,可分为加计数器、减计数器和可逆计数器。

8.4.1 二进制异步计数器1.二进制异步加计数器(1)电路结构以三位二进制异步加法计数器为例,如图8.4.1所示。

该电路由3个上升沿触发的D触发器组成,具有以下特点:每个D触发器输入端接该触发器Q 端信号,因而Q n+1=Q n,即各D触发器均处于计数状态;计数脉冲加到最低位触发器的C端,个触发器的Q 端信号接到相邻高位的C端。

图8.4.1 3位二进制异步加计数器(2)原理分析假设各触发器均处于0态,根据电路结构特点以及D触发器工作特性,不难得到其状态图和时序图,它们分别如图8.4.2和图8.4.3所示。

其中虚线是考虑触发器的传输延迟时间tpd后的波形。

图8.4.2 图8.4.1所示电路的状态图图8.4.3 图8.4.1所示电路的时序图由状态图可以清楚地看到,从初始状态000(由清零脉冲所置)开始,每输入一个计数脉冲,计数器的状态按二进制递增(加1),输入第8个计数脉冲后,计数器又回到000状态。

因此它是23进制加计数器,也称模八(M=8)加计数器。

从时序图可以清楚地看到Q0,Q1,Q2的周期分别是计数脉冲(CP)周期的2倍,4倍、8倍,也就是说Q0,Q1,Q2,分别对CP波形进行了二分频,四分频,八分频,因而计数器也可作为分频器。

需要说明的是,由图8.4.3中的虚线波形可知,在考虑各触发器的传输延迟时间tpd时,对于一个n位的二进制异步计数器来说,从一个计数脉冲(设为上升沿起作用)到来,到n个触发器都翻转稳定,需要经历的最长时间是ntpd ,为保证计数器的状态能正确反应计数脉冲的个数,下一个计数脉冲(上升沿)必须在ntpd后到来,因此计数脉冲的最小周期Tmin=ntpd。

16计数器 c语言实现原理 -回复

16计数器c语言实现原理-回复实现16计数器主要依靠C语言的逻辑和数学运算。

以下是一步一步详细回答关于16计数器C语言实现原理的文章。

首先,我们需要了解什么是16计数器。

16计数器是一种能够计数0到15的设备或程序,它可以循环地计数从0到15,并在达到最大值后重新回到0。

接下来,我们将一步一步实现一个简单的16计数器。

第一步,我们需要定义一个计数器变量。

在C语言中,我们可以使用整型变量来表示计数器。

根据16进制数的表示,我们可以选择使用unsigned char类型来存储计数器变量。

这样,计数器变量的范围就是从0到255。

cunsigned char counter;第二步,我们需要初始化计数器变量。

在计数器开始工作之前,我们需要将其值设置为0,从而确保计数器从最小值开始计数。

ccounter = 0;第三步,我们需要编写一个循环来实现计数器的循环计数功能。

在C语言中,我们可以使用while循环或for循环来实现这个功能。

这里,我们选择使用while循环,并设置一个无限循环。

在循环的每个迭代中,我们将计数器值打印出来,并根据需要执行其他操作。

cwhile(1) {printf("当前计数值: d\n", counter);其他操作}第四步,我们需要实现计数器的递增功能。

在每次循环迭代中,我们将计数器的值递增1。

当计数器达到最大值15时,我们需要将其值重新设置为0,以完成循环计数的要求。

cwhile(1) {printf("当前计数值: d\n", counter);counter++;if(counter > 15) {counter = 0;}其他操作}通过以上几个步骤,我们已经完成了一个简单的16计数器的实现。

这个计数器将从0开始递增,当计数值达到15时,重新回到0,并不断重复这个过程。

在实际应用中,我们可以根据需要对计数器的功能进行扩展。

例如,可以添加按键检测的逻辑,当按下某个特定的按键时,重置计数器的值为0,从而在需要时可以重新开始计数。

基于pspice的十六位二进制同步计数器

EDA课程考试报告题目:同步十六位二进制计数器专业:电子信息科学与技术班级:11 电科(专升本)姓名: 陈泓宇学号:11P110657000041时间:2012-6-8一.总体设计思路:此次设计首先是考虑到了利用JK触发器的分频特性来对脉冲计数。

起初是由三位二进制加法器的原理联想到扩展到更多的位数。

首先在我们谈到的很多计数器当中,如单片机的时钟脉冲等等,都会用到十六位以及三十二位。

所以考虑到仿真实验十六位的计数电路。

该电路首先是在同步二进制的计数原理上加以门电路来实现74LS161的芯片对四位二进制的计数功能,然后利用74LS161芯片级联来实现十六位二进制的计数功能。

二.系统总的框图结构:1.首先是同步三位加法计数器的原理框图:2利用同步计数器的原理,加以门电路来合成74LS161芯片:3.74LS161级联图:三.各模块的结构及功能分析:1.同步三位二进制加法计数器计数器:同步三位二进制的真值表:由于JK触发器都有不定状态的影响,所以这当中均使用的是带有预置使能端的JK触发器。

这个预置断同时也是清零端,使各触发器的初态为均为0.分析:1).由结构图可知:Q2[n]=Q1[n+1].Q0[n+1] ————[ .为逻辑与]2).由三个JK触发器的输出端时序波形来作为脉冲的计数显示端口,达到计数的功能。

3).仿真的时序波形图:该处的参数设置是:仿真时间0---1us。

由时序波形图:Q2Q1Q0对应cp脉冲的个数的二进制,所以用JK触发器的输出端来表示计数的个数的二进制。

该仿真的输出文本文件output profile 如下:** Creating circuit file "sanweierjinzhijishu-SCHEMA TIC1-CHY.sim.cir"** W ARNING: THIS AUTOMATICALLY GENERATED FILE MAY BE OVERWRITTEN BY SUBSEQUENT SIMULATIONS*Libraries:* Local Libraries :* From [PSPICE NETLIST] section of d:\Program Files\Orcad\PSpice\PSpice.ini file:.lib "nom.lib"*Analysis directives:.TRAN 0 1us 0.PROBE V(*) I(*) W(*) D(*) NOISE(*).INC ".\"**** INCLUDING sanweierjinzhijishu-SCHEMA ***** source SANWEIERJINZHIJISHUX_U1 $D_HI CLK $D_HI CLEAR Q0 M_UN0001 $G_DPWR $G_DGND JKFFRX_U2 Q0 CLK Q0 CLEAR Q1 M_UN0002 $G_DPWR $G_DGND JKFFRX_U3 N00838 CLK N00838 CLEAR Q2 M_UN0003 $G_DPWR $G_DGND JKFFRU_DSTM1 STIM(1,1) $G_DPWR $G_DGND CLEAR IO_STM IO_LEVEL=0+ 0 0+ +.03uS 1+REPEA T FOREVER+ +.98uS 0+ +.03uS 1+ ENDREPEATU_DSTM2 STIM(1,1) $G_DPWR $G_DGND CLK IO_STM IO_LEVEL=0+ 0 0+ +.02uS 1+REPEA T FOREVER 【时钟周期为0.04us,高低电平各为0.02us】+ +.02uS 0+ +.02uS 1+ ENDREPEATX_U4 Q1 Q0 N00838 $G_DPWR $G_DGND AND2**** RESUMING sanweierjinzhijishu-SCHEMATIC1-CHY.sim.cir ****.END**** 06/19/12 13:37:03 ********* PSpice 9.2 (Mar 2000) ******** ID# 1 ********** Profile: "SCHEMA TIC1-CHY" [ C:\sanweierjinzhijishu-SCHEMA TIC1-CHY.sim ]**** Digital Gate MODEL PARAMETERS2 关于74LS161芯片的各模块结构及功能:74LS161 芯片的外引脚74LS161芯片74ls161计数时的外部引脚连接图同步四位二进制74LS161的计数真值表:74LS161的计数功能真值表:此功能在74LS161级联构成十六位二进制的计数时,利用了ENT和ENP 两个端口的功能,在ENP=1的情况下利用ENT为0时保持,为1时启动计数有所体现。

进制计数器实验报告

进制计数器实验报告进制计数器实验报告一、引言计数器是数字电路中常用的一种元件,用于记录和控制信号的数量。

进制计数器是一种特殊的计数器,可以按照不同的进制进行计数。

本次实验旨在通过设计和实现一个进制计数器,深入理解计数器的工作原理和应用。

二、实验目的1. 理解计数器的基本原理和工作方式;2. 掌握进制计数器的设计方法和实现技巧;3. 分析进制计数器的应用场景和优缺点。

三、实验原理计数器是由触发器、逻辑门和时钟信号组成的电路。

触发器是计数器的核心部件,用于存储和传递计数值。

进制计数器是一种多位计数器,根据进制不同,可以分为二进制计数器、十进制计数器等。

本次实验以二进制计数器为例进行说明。

四、实验步骤1. 确定计数器的位数,本次实验设计一个4位二进制计数器;2. 根据位数确定触发器的数量,每一位对应一个触发器;3. 使用JK触发器实现计数器的设计,JK触发器具有可控制的置位和复位功能;4. 将各个触发器按照级联的方式连接起来,形成一个多位计数器;5. 设计时钟信号的输入方式,可以使用外部信号源或者计算机控制;6. 连接逻辑门,用于实现计数器的计数逻辑;7. 设计计数器的复位功能,使计数器可以从任意值开始计数。

五、实验结果经过设计和实现,成功搭建了一个4位二进制计数器。

通过输入时钟信号,计数器能够按照二进制规则进行计数,并在达到最大值时自动清零。

实验结果与预期相符,计数器的功能正常。

六、实验分析1. 进制计数器在数字电路中有着广泛的应用,可以用于时序控制、频率分频等场景;2. 进制计数器的位数决定了其能够表示的最大值,位数越多,能够表示的数值范围越大;3. 进制计数器的设计需要考虑触发器的选择、逻辑门的连接和时钟信号的输入方式等因素;4. 进制计数器的设计还需要考虑计数器的复位功能,以确保计数器能够从任意值开始计数。

七、实验总结通过本次实验,我深入了解了进制计数器的工作原理和设计方法。

实践中,我不仅学会了搭建一个进制计数器的步骤,还了解了进制计数器的应用场景和优缺点。

(完整word版)16进制计数器的电路设计及版图实现

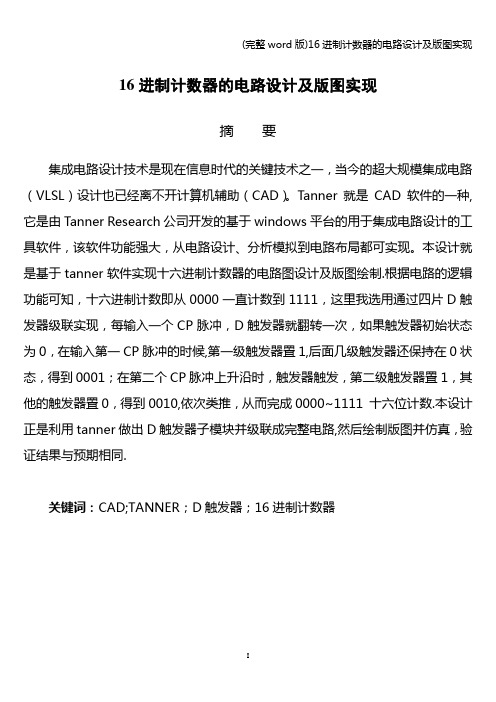

16进制计数器的电路设计及版图实现摘要集成电路设计技术是现在信息时代的关键技术之一,当今的超大规模集成电路(VLSL)设计也已经离不开计算机辅助(CAD)。

Tanner就是CAD软件的一种,它是由Tanner Research公司开发的基于windows平台的用于集成电路设计的工具软件,该软件功能强大,从电路设计、分析模拟到电路布局都可实现。

本设计就是基于tanner软件实现十六进制计数器的电路图设计及版图绘制.根据电路的逻辑功能可知,十六进制计数即从0000一直计数到1111,这里我选用通过四片D触发器级联实现,每输入一个CP脉冲,D触发器就翻转一次,如果触发器初始状态为0,在输入第一CP脉冲的时候,第一级触发器置1,后面几级触发器还保持在0状态,得到0001;在第二个CP脉冲上升沿时,触发器触发,第二级触发器置1,其他的触发器置0,得到0010,依次类推,从而完成0000~1111 十六位计数.本设计正是利用tanner做出D触发器子模块并级联成完整电路,然后绘制版图并仿真,验证结果与预期相同.关键词:CAD;TANNER;D触发器;16进制计数器Circuit Design and Layout Implementation ofHexadecimal CounterAbstractIC design technology is now one of the key technologies of the information age, today’s ultra-large scale integrated circuit (VLSL) has been inseparable from computer-aided design (CAD)。

Tanner is a CAD software, which is developed by the Tanner Research windows-based platform for integrated circuit design tool software, which is powerful,the circuit design, analysis,simulation of the circuit layout can be realized. This design is based on the software tanner to implement hexadecimal counter circuit design and layout drawing。

24进制计数器原理

24进制计数器原理一、概述24进制计数器是一种基于二进制计数器的扩展,可以用来计算更大的数字。

它采用了24个不同的数字,分别为0-9和A-Q,每个数字占据4个二进制位。

在实际应用中,24进制计数器常用于时间、频率等领域。

二、二进制计数器在介绍24进制计数器之前,我们先来了解一下二进制计数器。

二进制计数器是由若干个触发器组成的,每个触发器都能存储一个比特位(0或1),并且能够控制下一个触发器的状态。

当所有触发器的状态从000...0到111...1时,就完成了一次循环。

三、24进制表示法在24进制表示法中,每个数字占据4个二进制位。

这样做的好处是可以使用现有的逻辑门电路来实现24进制计数器。

四、实现原理1. 计数范围由于每个数字占据4个二进制位,因此一个4位的24进制数字可以表示$2^4=16$种不同的状态。

如果使用n个这样的数字组成一个n*4位的数字,则可以表示$24^{n}$种不同状态。

例如:使用3个4位的数字组成12位数字,则可以表示$24^{3}=13824$种不同状态。

2. 递增逻辑递增逻辑是指在当前状态下,如何将计数器的值加1。

对于24进制计数器,可以使用以下方法:(1) 将最低位数字加1。

如果最低位数字小于23,则直接加1;否则将最低位数字置为0,同时将第二低位数字加1。

(2) 如果第二低位数字也等于23,则继续向高位进位,直到某一位的数字小于23为止。

3. 递减逻辑递减逻辑是指在当前状态下,如何将计数器的值减1。

对于24进制计数器,可以使用以下方法:(1) 将最低位数字减1。

如果最低位数字大于0,则直接减1;否则将最低位数字置为23,同时将第二低位数字减1。

(2) 如果第二低位数字也等于0,则继续向高位借位,直到某一位的数字大于0为止。

五、应用场景24进制计数器常用于时间、频率等领域。

例如,在一个以秒为单位的定时器中,如果采用二进制计数器,则需要至少30个比特才能表示一个小时($2^{30}$秒)。

课题十六 二进制计数器解析

输2出进。制 8进制

16进制连接

CP入

2. 74161/74163(同步4位二进制计数器) V CC C 0 Q 0 Q 1 Q 2 Q 3 E T LD 16 15 14 13 12 11 10 9

74161功能表:P153

输入

C0 Q 0 Q1 Q 2 Q 3 S2

Cr

LD

CP D 0 D1 D 2 D3 S1

⑵速度快,主要用于构成任意进制计数器、地址 计数器、脉冲发生器等。

1. 加计数器的设计

<1>计数状态表

同步计数器CP0 = CP1 = CP2 = CP入

<2>分析: ①清零

② F0 —计翻, T触发器,T0=1 ③ F1 —计翻, T触发器,T1=Q0 ④ F2 —计翻, T触发器,T2=Q1Q0

T0 1 T1 Q0 T2 Q1 Q0

逻辑图

3. 可逆计数器 加控制端和选通门进行选择,电路设计课下自行练习。

2.3 集成二进制计数器

异步:4位:74LS197→Cr 异步清零,LD 异步置数。 74LS293→ 2-8-16进制计数器 cpA:2进制cp, cpB:8进制cp。

R01, R02 异步清零,R01R02 1清零。

0

00

<2>规律:

低位触发器: CP入→CP0,计翻;

其余触发器:只在相邻低位Q (由1→0),有CP,计翻。 D触发器:CP 有效,CPi= Qi-1 JK触发器:CP 有效,CPi = Qi-1

由D触发器构 成T’触发器。

由JK触发器构 成T’触发器。

<3>电路

低位触发器: CP入→CP0,计翻;

余触发器:只在相邻低位Q (由1→0),有CP,计翻。 JK触发器:CP 有效,CPi = Qi-1

二进制计数器

图5-17 4位二进制同步加法计数器74LS161的逻辑符号

如表5-6所示为74LS161的功能表。

清零 RD 0 1 1 1 1

预置 LD × 0 1 1 1

使能

EP ET ××

××

0× ×0

1

1

表5-6 74LS161的功能表

J1 J2

K1 K2

Q0 Q0Q1

J3 K3 Q0Q1Q2

由于该电路的驱动方程规律性较强,只需用“观察法”就 可画出时序波形图或状态转换表(参见表5-4)。

表5-4 4位二进制同步加法计数器的状态转换表

计数脉冲序号 0 1 2 3 4 5 6

电路状态 Q3Q2Q1Q0 0000 0001 0010 0011 0100 0101 0110

如图5-11所示为JK触发器组成的4位异步二进制加法计数器的 电路结构。

图5-11 4位异步二进制加法计数器的电路结构

图5-11中,将JK触发器连接成T触发器(即 J K 1 )的 形式,最低位触发器 FF0的时钟脉冲输入端接计数脉冲CP,其 他触发器的时钟脉冲输入端接相邻低位触发器的Q端。

由于该电路的连线简单且规律性强,因此无须用前面介绍的 分析步骤进行分析,只需进行简单的观察与分析就可画出时序波 形图和状态转换图,这种分析方法称为“观察法”。

2)二进制同步减法计数器

如表5-5所示为4位二进制同步减法计数器的状态转换表。

计数脉冲序号

电路状态 Q3Q2Q1Q0

等效十进制数

0

0000

0

1

1111

15

2

1110

14

3

1-16-5计数器—异步二进制加计数器

1

1CP 1Q0 3

1Q1 4

1Q2 5

2 1CR 1Q3 6

13

2CP 2Q0 11

2Q1 10

2Q2 9

12 2CR 2Q3 8

74HC/HCT393的逻辑符号

1

0 4tpd

Q3 0 0 0 0 0 0 0 0 1 1 1 1 1 1 1 1 0

➢异步计数脉冲的最小周期 Tmin=n tpd。(n为位数)

②典型集成电路 中规模集成电路74HC/HCT393中集成了两个4位异步 二进制计数器在 5V、25℃工作条件下,74HC/HCT393 中每级触发器的传输延迟时间典型值为6ns。

6.5.2 计 数 器

概述 1、计数器的逻辑功能 计数器的基本功能是对输入时钟脉冲进行计数。它也可 用于分频、定时、产生节拍脉冲和脉冲序列及进行数字 运算等等。 2、计数器的分类 •按脉冲输入方式,分为同步和异步计数器 •按进位体制,分为二进制、十进制和任意进制计数器 •按逻辑功能,分为加法、减法和可逆计数器

FF1 Q1

FF2 Q2

FF3 Q3

CP

1

>C Q0

R

>C R

Q1

>C R

Q2

>C R

Q3

CR 1

1

1

1

1

Q0

Q1

Q2

Q3

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 CP

Q0 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0

Q1 0 0 1 1 0 0 1 1 0 0 1 1 0 0 1 1 0

Q2 0 0 0 0 1 1 1 1 0 0 0 0 1 1 1 1 0

电工电子技术16.6 二进制计数器

班主任: 我觉得何旋今天取得这样的成绩, 我觉得,很重要的是,何旋是土生土长的北京 二中的学生,二中的教育理念是综合培养学生 的素质和能力。我觉得何旋,她取得今天这么 好的成绩,一个来源于她的扎实的学习上的基 础,还有一个非常重要的,我觉得特别想提的, 何旋是一个特别充满自信,充满阳光的这样一 个女孩子。在我印象当中,何旋是一个最爱笑 的,而且她的笑特别感染人的。所以我觉得她 很阳光,而且充满自信,这是她突出的这样一 个特点。所以我觉得,这是她今天取得好成绩 当中,心理素质非常好,是非常重要的。

青 春 风 采

高考总分:

692分(含20分加分) 语文131分 数学145分 英语141分 文综255分

毕业学校:北京二中 报考高校: 北京大学光华管理学 院 北京市文科状元 阳光女孩--何旋

来自北京二中,高考成绩672分,还有20 分加分。“何旋给人最深的印象就是她 的笑声,远远的就能听见她的笑声。” 班主任吴京梅说,何旋是个阳光女孩。 “她是学校的摄影记者,非常外向,如 果加上20分的加分,她的成绩应该是 692。”吴老师说,何旋考出好成绩的秘 诀是心态好。“她很自信,也很有爱心。 考试结束后,她还问我怎么给边远地区 的学校捐书”。

“用好课堂40分钟最重要。我的经验是,哪怕 是再简单的内容,仔细听和不上心,效果肯 定是不一样的。对于课堂上老师讲解的内容, 有的同学觉得很简单,听讲就不会很认真, 但老师讲解往往是由浅入深的,开始不认真, 后来就很难听懂了;即使能听懂,中间也可 能出现一些知识盲区。高考试题考的大多是 基础知识,正就是很多同学眼里很简单的内 容。”常方舟告诉记者,其实自己对竞赛试 题类偏难的题目并不擅长,高考出色的原因 正在于试题多为基础题,对上了自己的“口 味”。

孙老师说,杨蕙心学习效率很高,认真执行老师 的复习要求,往往一个小时能完成别人两三个小 时的作业量,而且计划性强,善于自我调节。此 外,学校还有一群与她实力相当的同学,他们经 常在一起切磋、交流,形成一种良性的竞争氛围。 谈起自己的高考心得,杨蕙心说出了“听话” 两个字。她认为在高三冲刺阶段一定要跟随老师 的脚步。“老师介绍的都是多年积累的学习方法, 肯定是最有益的。”高三紧张的学习中,她常做 的事情就是告诫自己要坚持,不能因为一次考试 成绩就否定自己。高三的几次模拟考试中,她的 成绩一直稳定在年级前5名左右。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

1.1 时序电路特点

1.2 时序电路结构

1.3 时序电路分类

1.4 时序电路状态表和状态图

二、寄存器

2.1 数码寄存器 2.2 移位寄存器及应用

参阅教材章节:6.3.2.1 二进制计数器

一、计数器基础 二、二进制计数器

2.1 异步二进制计数器设计

2.2 同步二进制计数器设计

2.3 集成二进制计数器及应用

(1)计数器电路是一种随时钟输入CP变 化,其输出按一定顺序变化的时序电路。 (2)二进制计数器设计 (3)中规模集成计数器74LS293、 74LS161、74LS163

用D实现: D T Q

n

0

0

0

T触发器,T=0:保持;T=1:翻转

用JK实现: J K T

多用JK 触发器。

<3>逻辑图:

用D实现: D T Q n 用JK实现: J K T

多用JK 触发器。 T0=1,T1=Q0, T2=Q1Q0 ,用JK实现:J=K=T

2. 减计数器的设计

1. 74293— 4级JK触发器(异步4位二进制计数器)

低位触发器: CP入→CP0,计翻; 余触发器:只在相邻低位Q (由1→0),有CP,计翻。 JK触发器:CP 有效,CPi = Qi-1 可组成2-8-16进制计数器

1

Q0

1

Q1

1

Q2

1

Q3

功能表

Q0 Q1 Q2 Q3

CP连接

CPA=CP入 ,二进制,Q0输出 CPB =CP入,八进制,Q3Q2Q1输出 CPA=CP入,且CPB =Q0 ,十六进制,Q3Q2Q1Q0输出。 2进制 8进制

同步置数,LD低有效。 2个使能端ET、EP均为1:计数。

进位输出:CO=ETQ3Q2Q1Q0

例:扩展应用 3片74161构成12位同步计数器。

级联原则:低位全1,高位进位(加1计数)。

Q0

Q3

Q4

Q7

Q8

Q11

①当Q3Q2Q1Q0=1111时,Co1=1→ET2=EP2=1,161(2)可计数. ②当Q3Q2Q1Q0=1111时,Co1=1→ET3=1, 且Q7Q6Q5Q4=1111时,Co2=1→EP3=1, 161(3)可计数.

D0 D1 D2 D3

0 1 1 1 1

× 0 1 1 1

× × 1 0 ×

× × 1 1 0

× (↑) ↑ ↑ × ×

××××

D0 D1 D2 D3

0

0

0

0

×××× ×××× ××××

D0 D1 D2 D3 计数 保持,C0=0 保持

Co=ETQ3Q2Q1Q0 清零,Cr低有效 特点:

74161异步清零。 74163同步清零。

Co=ETQ3Q2Q1Q0 同步置数

2. 74161/74163(同步4位二进制计数器)

74163功能表:

输入

清 零 置 数 使 能 时钟 Cr LD ET E P cp

数 据

输出

Q0 Q1 Q2 Q3

D0 D1 D2 D3

0 1 1 1 1

× 0 1 1 1

× × 1 0 ×

× × 1 1 0

↑ ↑ ↑ × ×

1. 加计数器的设计 <1>列计数状态表: 分析: ①清零 ② F0 →计数翻转, CP0→计数输入cp, 用T’触发器。 ③ F1 →计数翻转, CP1 →Q0(1→0), 用T’触发器。 ④ F2 →计数翻转, CP2 →Q1(1→0), 用T’触发器

0

0

0

<2>规律: 低位触发器: CP入→CP0,计翻;

同步:

同步清0/置数,在满足清0/置数条件后, 需等下一个cp到来后才执行清0/置数。

74161—异清(Cr)、同置(LD),使能ETEP,进位Co=ETQ3Q2Q1Q0

74163—同清(Cr)、同置(LD),使能ETEP,进位Co=ETQ3Q2Q1Q0 74LS191(16,可逆)—无清、异置(LD)、 控制端D/U (=1减、=0加) 74LS193(16,双时钟)— 异清(Cr)、异置(LD) 、 时钟CPU=↑, CPD =1:加 CPU=1 , CPD =↑:减 74LS169(16可逆)—无清、同置(LD) 、 控制端D/U (=1减、=0加) 使能 S1S0:S1+S0=0,计数

R01 , R02 异 步 清 零 , R01 R02 1清 零 。

74LS393→ 双16进制计数器

Cr 异 步 清 零 , Cr = 1清 零 。

7位:CC4024Fra bibliotekMr 异 步 清 零 , Mr= 1清 零 。 Mr 异 步 清 零 , Mr= 1清 零 。

12位:CC4040

14位:CC4060

数 据

1

Cr

2

CP

3

D0

4

D1

5

D2

6

D3

7

EP

8

GND

输出

Q0 Q1 Q2 Q3

D0 D1 D2 D3

0 1 1 1 1

× 0 1 1 1

× × 1 0 ×

× × 1 1 0

× ↑ ↑ × ×

××××

D0 D1 D2 D3

0

0

0

0

×××× ×××× ××××

D0 D1 D2 D3 计数 保持,C0=0 保持

对你的期望:

掌握二进制计数器的设计(同步、异步) 方法。 熟练掌握集成二进制计数器的应用。

一、计数器基础

计数:累计输入脉冲的个数。 构成:1个触发器有2个状态,可计2个二进制数(0,1); n个触发器有2n个状态,可计2n个数(n位二进制数)。 分类: CP引入方式 加计数

同步

异步

计数功能

减计数 可逆计数 JK

2.2 同步二进制计数器

⑴有统一的CP,状态更新与CP同步。共用CP信号源, CP负载较重。 ⑵速度快,主要用于构成任意进制计数器、地址 计数器、脉冲发生器等。 1. 加计数器的设计 <1>计数状态表

同步计数器CP0 = CP1 = CP2 = CP入

<2>分析: ①清零 ② F0 —计翻, T触发器,T0=1 ③ F1 —计翻, T触发器,T1=Q0 ④ F2 —计翻, T触发器,T2=Q1Q0 <3>逻辑图:

计数状态表:

同理可得:

T0 1 T 1 Q0 T2 Q1 Q0

逻辑图

3. 可逆计数器 加控制端和选通门进行选择,电路设计课下自行练习。

2.3 集成二进制计数器

异步: 4位:74LS197→ Cr 异 步 清 零 , LD 异 步 置 数 。 74LS293→ 2-8-16进制计数器 cpA:2进制cp, cpB:8进制cp。

CP入

符号

16进制连接

2. 74161/74163(同步4位二进制计数器)

V CC C0 C0 Cr CP

Q0

Q1

Q2

Q3

ET

LD

16 15 14 13 12 11 10

S2 LD D0 D1 D2 D3 S1

9

Q0

Q1

Q2

Q3

74161功能表:P153

输入

清 零 置 数 使 能 时钟 Cr LD ET E P cp

其余触发器:只在相邻低位Q (由1→0),有CP,计翻。

D触发器:CP JK触发器:CP 有效,CPi= Qi-1 有效,CPi = Qi-1

由D触发器构 成T’触发器。

由JK触发器构 成T’触发器。

<3>电路 低位触发器: CP入→CP0,计翻; 余触发器:只在相邻低位Q (由1→0),有CP,计翻。 D触发器:CP JK触发器:CP 有效,CPi= Qi-1 有效,CPi = Qi-1

××××

D0 D1 D2 D3

0

0

0

0

×××× ×××× ××××

D0 D1 D2 D3 计数 保持,C0=0 保持

Co=ETQ3Q2Q1Q0 同步清零 (与161的唯一区别)

2. 74161/74163(续)

输入

清零 置数 使 能 时钟 LD ET E P cp Cr

数 据

输出

Q0 Q1 Q2 Q3

<4>时序图

1

2

3

4

5

6

7

8

2分频 4分频 8分频

C Q0 Q1 Q2 异步二进制加法器工作波形 从时序图可以看出,若计数输入脉冲频率为 f0, 则Q0、Q1、Q2端输出脉冲的频率依次为f0/2、f0/4、 f0/8、,即为计数器的分频功能。

2. 用D触发器构成三位二进制异步减法器

3. 异步二进制可逆计数 设置控制端C,如设C=1时:加计数;(D:CPi= Qi-1 ) C=0时:减计数。(D:CPi= Qi-1 ) 加选通门即可实现。 电路:

二进制

计数体制

非二进制

构成方式

D

RS

二、二进制计数器

分析设计方法:

二进制计数器构成简单,规律 性强,用观察法。

(1)分析计数状态表,找各触发器状态翻转的规律; (2)根据所用触发器确定电路连线。

2.1 异步二进制计数器:

⑴无统一CP,输入时钟信号只作用于最低位触发器。 ⑵各触发器间串行连接,即状态更新逐级进行。速度 慢,可能会出现毛刺。 ⑶主要用于分频、定时,低速计数等。