西南交通大学《数字电子技术》模拟试题一(含答案)

《数字电子技术》模拟试题及答案6页word

《数字电子技术》模拟试题一、填空题(每题2分,共20分)1、十六进制数97,对应的十进制数为 151。

2、“至少有一个输入为0时,输出为 0 ”描述的是与运算的规则。

3、 4 变量逻辑函数有16个最小项。

4、基本逻辑运算有: 与 、 或 和 非 运算。

5、两二进制数相加时,不考虑低位的进位信号是 半 加器。

6、TTL 器件输入脚悬空相当于输入 高 电平。

7、RAM 的三组信号线包括: 数据 线、地址线和控制线。

8、采用四位比较器对两个四位数比较时,先比较 最高 位。

二、单项选择题(每个3分,共15分) 1、图1的国标逻辑符号中 B 是异或门。

图12、下列逻辑函数表达式中可能存在竞争冒险的是 C 。

A ))((C B B A F ++= B ))((C B B A F ++= C ))((C B B A F ++= D ))((C B B A F ++=3、下面逻辑式中,不正确的是_ A___。

A.C B A ABC ⋅⋅=B. A AB A +=C. ()A A B A +=D. AB BA =4、时序逻辑电路中必须有___B___。

A. 输入逻辑变量 B. 时钟信号C. 计数器D. 编码器5、有S1,S2两个状态,条件 B 可以确定S1和S2不等价。

A. 输出相同B. 输出不同C. 次态相同D. 次态不同三、简答题(共10分)1、证明:B A B A A +=+(4分)解:B A B A B A A A +=+⋅=+⋅+)()()左边=(1 2、某逻辑函数的真值表如表1所示,画出卡诺图。

(6分) 表1 某逻辑函数的真值表A B C F 0 0 0 0 0 0 1 1 0 1 0 1 0 1 1 X 1 0 0 X 1 0 1 0 1 1 0 1 111X四、分析题(20分)图2分析图2所示电路的逻辑功能。

1)列出其时钟方程:(2分) CP1=CP ↑;CP0=CP ↑。

2)列出其驱动方程:(4分)ZJ1=Q0;K1= 1 ;J0=1Q ;K0=11Q X Q X +⋅或。

数字电子技术试题及答案(题库)

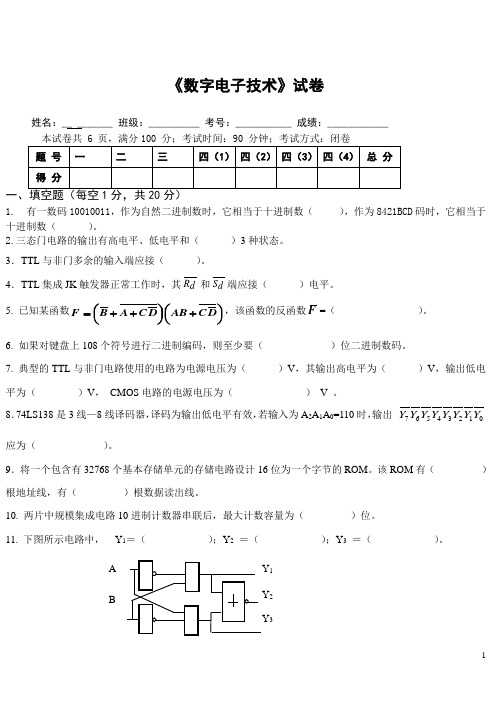

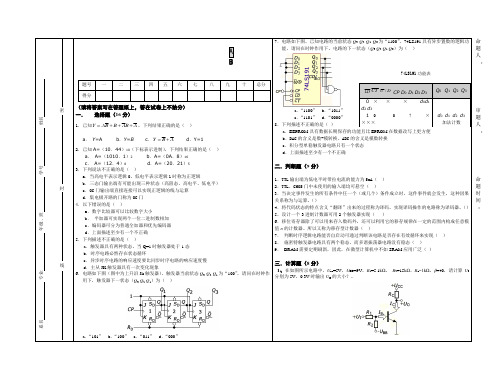

《数字电子技术》试卷姓名:__ _______ 班级:__________ 考号:___________ 成绩:____________1. 有一数码10010011,作为自然二进制数时,它相当于十进制数( ),作为8421BCD 码时,它相当于十进制数( )。

2.三态门电路的输出有高电平、低电平和( )3种状态。

3.TTL 与非门多余的输入端应接( )。

4.TTL 集成JK 触发器正常工作时,其d R 和d S 端应接( )电平。

5. 已知某函数⎪⎭⎫ ⎝⎛+⎪⎭⎫ ⎝⎛++=D C AB D C A B F ,该函数的反函数F =( )。

6. 如果对键盘上108个符号进行二进制编码,则至少要( )位二进制数码。

7. 典型的TTL 与非门电路使用的电路为电源电压为( )V ,其输出高电平为( )V ,输出低电平为( )V , CMOS 电路的电源电压为( ) V 。

8.74LS138是3线—8线译码器,译码为输出低电平有效,若输入为A 2A 1A 0=110时,输出 01234567Y Y Y Y Y Y Y Y 应为( )。

9.将一个包含有32768个基本存储单元的存储电路设计16位为一个字节的ROM 。

该ROM 有( )根地址线,有()根数据读出线。

10. 两片中规模集成电路10进制计数器串联后,最大计数容量为( )位。

11. );Y 3 =( )。

12. 某计数器的输出波形如图1所示,该计数器是( )进制计数器。

13.驱动共阳极七段数码管的译码器的输出电平为( )有效。

二、单项选择题(本大题共15小题,每小题2分,共30分)(在每小题列出的四个备选项中只有一个是最符合题目要求的,请将其代码填写在题后的括号内。

错选、多选或未选均无分。

)1. 函数F(A,B,C)=AB+BC+AC 的最小项表达式为( ) 。

A .F(A,B,C)=∑m (0,2,4) B. (A,B,C)=∑m (3,5,6,7) C .F(A,B,C)=∑m (0,2,3,4) D. F(A,B,C)=∑m (2,4,6,7)2.8线—3线优先编码器的输入为I 0—I 7 ,当优先级别最高的I 7有效时,其输出012Y Y Y ••的值是( )。

数字电子技术测试试卷与答案精选全文完整版

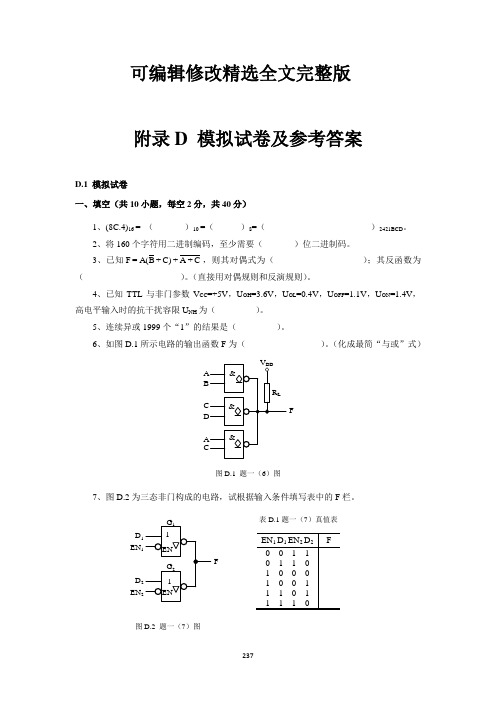

可编辑修改精选全文完整版附录D 模拟试卷及参考答案D.1 模拟试卷一、填空(共10小题,每空2分,共40分)1、(8C.4)16 = ( )10 =( )8=( )2421BCD 。

2、将160个字符用二进制编码,至少需要( )位二进制码。

3、已知F =A(B +C)+A +C ,则其对偶式为( );其反函数为( )。

(直接用对偶规则和反演规则)。

4、已知TTL 与非门参数V CC =+5V ,U OH =3.6V ,U OL =0.4V ,U OFF =1.1V ,U ON =1.4V ,高电平输入时的抗干扰容限U NH 为( )。

5、连续异或1999个“1”的结果是( )。

6、如图D.1所示电路的输出函数F 为( )。

(化成最简“与或”式)F图D.1 题一(6)图7、图D.2为三态非门构成的电路,试根据输入条件填写表中的F 栏。

图D.2 题一(7)图表D.1题一(7)真值表D 1EN 1D 2EN 2F8、设计模值为61的自然二进制码计数器、十进制计数器和余3 BCD码计数器分别需要()级、()级和()级触发器。

一个五位二进制加法计数器,由00000状态开始,问经过109个输入脉冲后,此计数器的状态为()。

9、用()片1024×4位的RAM可组成8K×8位的RAM,需要增加()条地址线、()条数据线。

10、在10位的倒T型电阻网络D/A转换器中,若U REF = ─10V,该D/A转换器能分辨的最小输出电压U LSB=()mV。

二、选择题(共10小题,每小题2分,共20分)1、有符号位二进制数的补码为(10011),则对应的十进制数为()。

A、-29B、+13C、-13D、-32、下列说法正确的是()。

A、n个变量所构成的全部最小项之和恒等于0B、n个变量所构成的全部最大项之和恒等于0C、n个变量所构成的全部最小项之积恒等于1D、n个变量所构成的全部最大项之积恒等于03、下列说法正确的是()。

西南交通大学《数字电子技术》模拟试题(含答案)

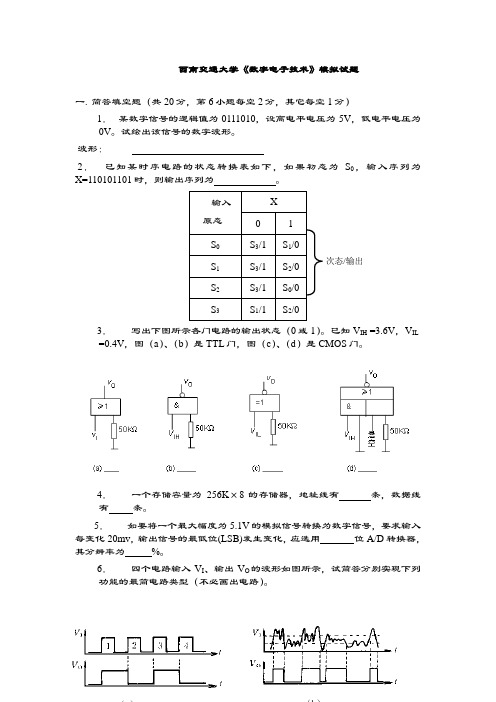

西南交通大学《数字电子技术》模拟试题一. 简答填空题(共20分,第6小题每空2分,其它每空1分)1. 某数字信号的逻辑值为0111010,设高电平电压为5V ,低电平电压为0V 。

试绘出该信号的数字波形。

波形:2. 已知某时序电路的状态转换表如下,如果初态为S 0,输入序列为X=110101101时,则输出序列为 。

3. 写出下图所示各门电路的输出状态(0或1)。

已知V IH =3.6V ,V IL =0.4V ,图(a )、(b )是TTL 门,图(c )、(d )是CMOS 门。

4. 一个存储容量为256K ×8的存储器,地址线有 条,数据线有 条。

5. 如要将一个最大幅度为5.1V 的模拟信号转换为数字信号,要求输入每变化20mv ,输出信号的最低位(LSB)发生变化,应选用 位A/D 转换器,其分辨率为 %。

6. 四个电路输入V I 、输出V O 的波形如图所示,试简答分别次态/输出实现下列功能的最简电路类型(不必画出电路)。

7. 写出下图所示PLD 的输出F 1、F 2逻辑表达式。

二. 逻辑代数和组合逻辑1. 公式法化简下列函数为最简与或式。

(4分)BD C D A B A C B A D C B A F ++++=),,,(2. 分析以下组合电路的功能,要求写出图示电路的逻辑表达式(3分),列出其真值表(2分),并说明电路的逻辑功能(2分)。

F 1=F 2=(a )三. 用或非门设计一个组合电路。

其输入为8421BCD 码,输出L 当输入数能被4整除时为1,其他情况为0。

(0可以被任何整数整除,要求有设计过程,给出电路图)(1)建立真值表 (3分) (2)写出函数的最小项表达式 (3分) (3)化简函数表达式 (4分) (4)用或非门实现。

(4分)四. 已知时序电路如图所示。

1. 请写出各触发器的驱动方程和次态方程。

(5分) 2. 画出电路的状态(Q 1Q 0)转换图。

西交20秋《数字电子技术》在线作业【标准答案】

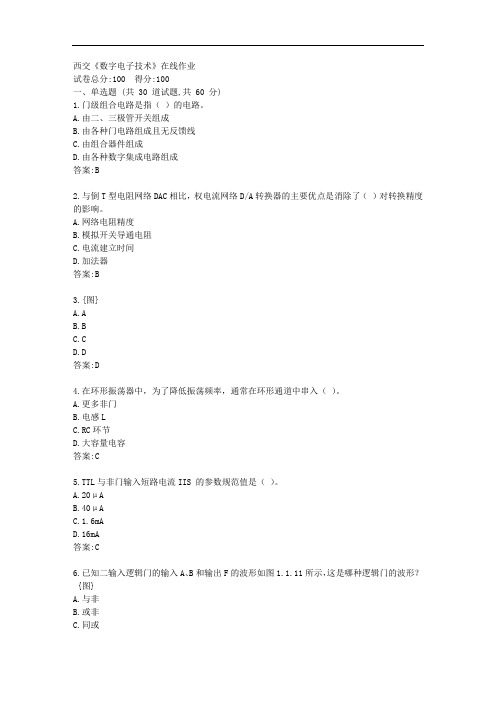

西交《数字电子技术》在线作业试卷总分:100 得分:100一、单选题 (共 30 道试题,共 60 分)1.门级组合电路是指()的电路。

A.由二、三极管开关组成B.由各种门电路组成且无反馈线C.由组合器件组成D.由各种数字集成电路组成答案:B2.与倒T型电阻网络DAC相比,权电流网络D/A转换器的主要优点是消除了()对转换精度的影响。

A.网络电阻精度B.模拟开关导通电阻C.电流建立时间D.加法器答案:B3.{图}A.AB.BC.CD.D答案:D4.在环形振荡器中,为了降低振荡频率,通常在环形通道中串入()。

A.更多非门B.电感LC.RC环节D.大容量电容答案:C5.TTL与非门输入短路电流IIS 的参数规范值是()。

A.20μAB.40μAC.1.6mAD.16mA答案:C6.已知二输入逻辑门的输入A、B和输出F的波形如图1.1.11所示,这是哪种逻辑门的波形? {图}A.与非B.或非C.同或D.与答案:C7.两个开关控制一盏灯,只有两个开关都闭合时灯才不亮,则该电路的逻辑关系是()。

A.与非B.或非C.同或D.异或答案:A8.{图}A.AB.BC.CD.D答案:B9.十进制数36转换为十六进制数,结果为( )A.26B.24C.22D.20答案:B10.数字信号是()。

A.时间和幅值上连续变化的信号B.时间和幅值上离散的信号C.时间上连续、幅值上离散变化的信号D.时间上离散、幅值上连续变化的信号答案:B11.门级组合电路是指的电路A.由二、三极管开关组成B.由各种门电路组成且无反馈线C.由组合器件组成D.由各种数字集成电路组成答案:B12.把模拟量转换成为相应数字量的转换器件称为()。

A.数-模转换器B.DACC.D/A转换器D.ADC答案:D13.已知F=(ABC+CD)',选出下列可以肯定使F=0的取值()。

A.ABC=011B.BC=11C.CD=10D.BCD=111答案:D14.{图}A.变为0B.保持1不变C.保持0不变D.无法确定答案:B15.数字系统中,降低尖峰电流影响,所采取的措施是()。

(完整版)数字电子技术基础模拟试题及答案完整

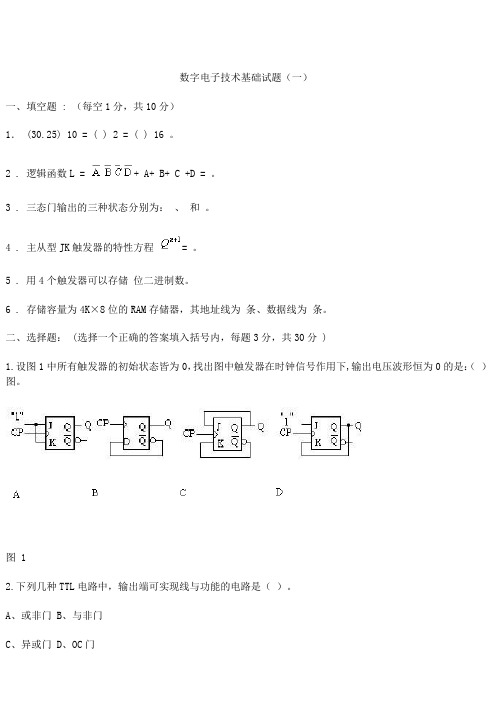

四.分析题(24 分)

五.应用题(43 分)

1.请用 74LS138 设计一个三变量的多数表决电路。具体要求如下: (1)输入变量 A、B、C 为高电平时表示赞同提案 (2)当有多数赞同票时提案通过,输出高电平 74LS138 的逻辑功能及引脚图如下:

三.计算题(8 分) 1、在如图所示电路中,Ucc=5V,UBB=9V,R1=5.1kΩ, R2=15kΩ,Rc=1kΩ,β=40,请计算 UI

分别为 5V,0.3V 时输出 UO 的大小?。

学号

年级、 班

专业

系名

a.“101” b.“100” c.“011” d.“000”

姓名

2.已知一个 8 位权电阻 DAC 系统的参考电源 UREF= -16V,转换比例系数 2RF 为 1。当输 R

姓名

学号

三(本大题 2 小题每小题 4 分共 8 分) 1 结果正确 1 分,步骤正确 3 分,参考结果如下:

UI=5V,UO≈0.3V UI=0.3V,UO≈5V

2 结果正确 1 分,步骤正确 3 分,参考结果如下:UO=3V 四(本大题 2 小题每小题 12 分共 24 分)

1.(1)Y Y2Y3Y4 AABC • B ABC • C ABC(4 分)

1”,LD =0 并保持,请画出在两个 CP↑作用下的状态转换关系? (2)请用清零法设计一个八进制记数器(可附加必要的门电

路)

学号

年级、 班

(1) 写出电路激励方程、状态方程、输出方程 (2) 画出电路的有效状态图

该电路具有什么逻辑功能并说明能否自启动

数字电子技术试题及答案题库

《数字电子技术》试卷姓名:__ _______ 班级:__________ 考号:___________ 成绩:____________ 本试卷共 6 页,满分100 分;考试时间:90 分钟;考试方式:闭卷 题 号 一 二 三 四(1) 四(2) 四(3) 四(4) 总 分 得 分一、填空题(每空1分,共20分)1.?有一数码10010011,作为自然二进制数时,它相当于十进制数( ),作为8421BCD 码时,它相当于十进制数( )。

2.三态门电路的输出有高电平、低电平和( )3种状态。

3.TTL 与非门多余的输入端应接( )。

4.TTL 集成JK 触发器正常工作时,其d R 和d S 端应接( )电平。

5. 已知某函数⎪⎭⎫ ⎝⎛+⎪⎭⎫ ⎝⎛++=D C AB D C A B F ,该函数的反函数F =( )。

6. 如果对键盘上108个符号进行二进制编码,则至少要( )位二进制数码。

7. 典型的TTL 与非门电路使用的电路为电源电压为( )V ,其输出高电平为( )V ,输出低电平为( )V , CMOS 电路的电源电压为( ) V 。

8.74LS138是3线—8线译码器,译码为输出低电平有效,若输入为A 2A 1A 0=110时,输出01234567Y Y Y Y Y Y Y Y 应为( )。

9.将一个包含有32768个基本存储单元的存储电路设计16位为一个字节的ROM 。

该ROM 有( )根地址线,有( )根数据读出线。

10. 两片中规模集成电路10进制计数器串联后,最大计数容量为( )位。

11. 下图所示电路中, Y 1=( );Y 2 =( );Y 3 =( )。

12. 某计数器的输出波形如图1所示,该计数器是( )进制计数器。

13.驱动共阳极七段数码管的译码器的输出电平为( )有效。

二、单项选择题(本大题共15小题,每小题2分,共30分) (在每小题列出的四个备选项中只有一个是最符合题目要求的,请将其代码填写在题后的括号内。

(完整word版)数字电子技术试题及答案(题库)

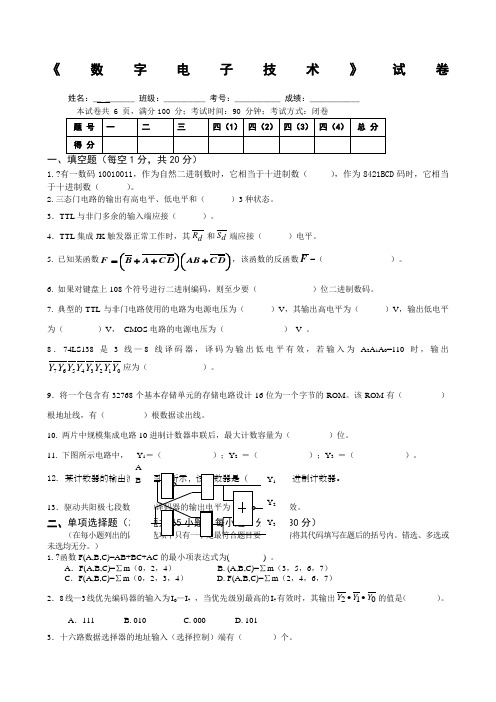

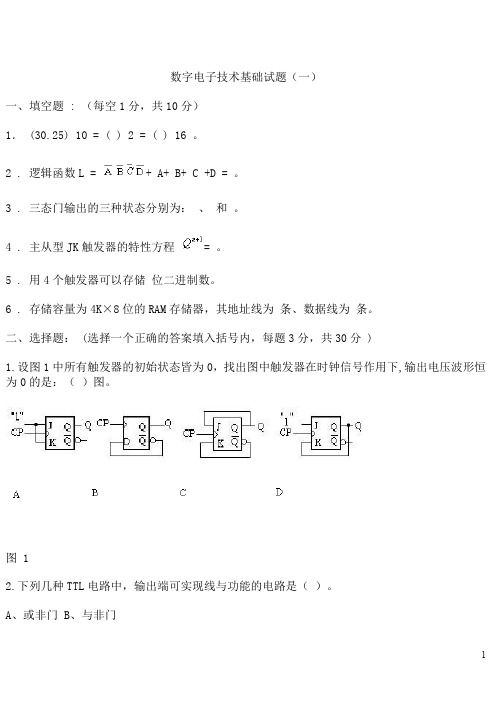

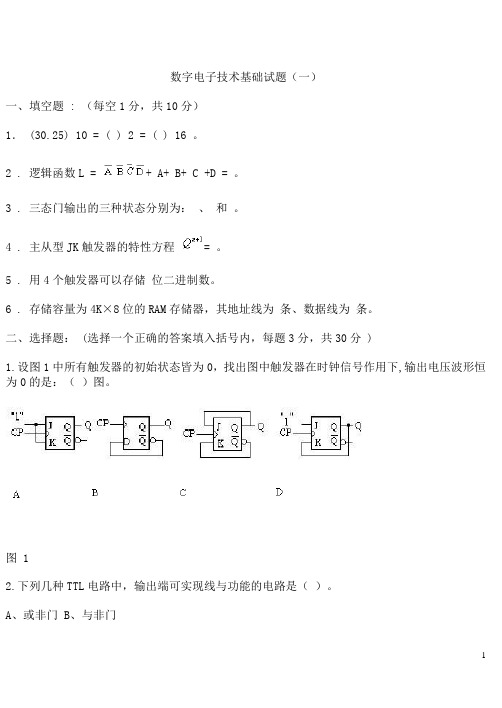

数字电子技术基础试题(一)一、填空题 : (每空1分,共10分)1. (30.25) 10 = ( ) 2 = ( ) 16 。

2 . 逻辑函数L = + A+ B+ C +D = 。

3 . 三态门输出的三种状态分别为:、和。

4 . 主从型JK触发器的特性方程= 。

5 . 用4个触发器可以存储位二进制数。

6 . 存储容量为4K×8位的RAM存储器,其地址线为条、数据线为条。

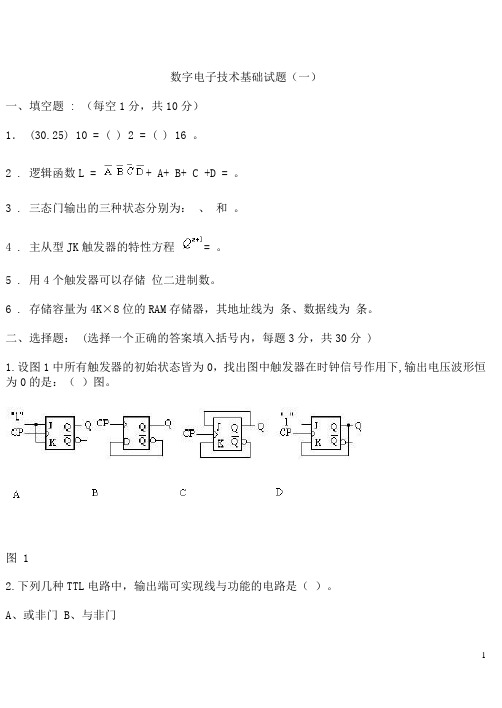

二、选择题: (选择一个正确的答案填入括号内,每题3分,共30分 )1.设图1中所有触发器的初始状态皆为0,找出图中触发器在时钟信号作用下,输出电压波形恒为0的是:()图。

图 12.下列几种TTL电路中,输出端可实现线与功能的电路是()。

A、或非门B、与非门C、异或门D、OC门3.对CMOS与非门电路,其多余输入端正确的处理方法是()。

A、通过大电阻接地(>1.5KΩ)B、悬空C、通过小电阻接地(<1KΩ)D、通过电阻接V CC4.图2所示电路为由555定时器构成的()。

A、施密特触发器B、多谐振荡器C、单稳态触发器D、T触发器5.请判断以下哪个电路不是时序逻辑电路()。

图2A、计数器B、寄存器C、译码器D、触发器6.下列几种A/D转换器中,转换速度最快的是()。

图2A、并行A/D转换器B、计数型A/D转换器C、逐次渐进型A/D转换器D、双积分A/D转换器7.某电路的输入波形 u I 和输出波形 u O 如图 3所示,则该电路为()。

图3A、施密特触发器B、反相器C、单稳态触发器D、JK触发器8.要将方波脉冲的周期扩展10倍,可采用()。

A、10级施密特触发器B、10位二进制计数器C、十进制计数器D、10位D/A转换器9、已知逻辑函数与其相等的函数为()。

A、B、C、D、10、一个数据选择器的地址输入端有3个时,最多可以有()个数据信号输出。

A、4B、6C、8D、16三、逻辑函数化简(每题5分,共10分)1、用代数法化简为最简与或式Y= A +2、用卡诺图法化简为最简或与式Y= + C +A D,约束条件:A C + A CD+AB=0四、分析下列电路。

数字电子技术试题及答案(题库)

数字电子技术基础试题(一)一、填空题 : (每空1分,共10分)1. (30.25) 10 = ( ) 2 = ( ) 16 。

2 . 逻辑函数L = + A+ B+ C +D = 。

3 . 三态门输出的三种状态分别为:、和。

4 . 主从型JK触发器的特性方程= 。

5 . 用4个触发器可以存储位二进制数。

6 . 存储容量为4K×8位的RAM存储器,其地址线为条、数据线为条。

二、选择题: (选择一个正确的答案填入括号内,每题3分,共30分 )1.设图1中所有触发器的初始状态皆为0,找出图中触发器在时钟信号作用下,输出电压波形恒为0的是:()图。

图 12.下列几种TTL电路中,输出端可实现线与功能的电路是()。

A、或非门B、与非门C、异或门D、OC门3.对CMOS与非门电路,其多余输入端正确的处理方法是()。

A、通过大电阻接地(>1.5KΩ)B、悬空C、通过小电阻接地(<1KΩ)D、通过电阻接V CC4.图2所示电路为由555定时器构成的()。

A、施密特触发器B、多谐振荡器C、单稳态触发器D、T触发器5.请判断以下哪个电路不是时序逻辑电路()。

图2A、计数器B、寄存器C、译码器D、触发器6.下列几种A/D转换器中,转换速度最快的是()。

图2A、并行A/D转换器B、计数型A/D转换器C、逐次渐进型A/D转换器D、双积分A/D转换器7.某电路的输入波形 u I 和输出波形 u O 如图 3所示,则该电路为()。

图3A、施密特触发器B、反相器C、单稳态触发器D、JK触发器8.要将方波脉冲的周期扩展10倍,可采用()。

A、10级施密特触发器B、10位二进制计数器C、十进制计数器D、10位D/A转换器9、已知逻辑函数与其相等的函数为()。

A、B、C、D、10、一个数据选择器的地址输入端有3个时,最多可以有()个数据信号输出。

A、4B、6C、8D、16三、逻辑函数化简(每题5分,共10分)1、用代数法化简为最简与或式Y= A +2、用卡诺图法化简为最简或与式Y= + C +A D,约束条件:A C + A CD+AB=0四、分析下列电路。

数字电子技术模拟试题1(含答案)

《数字电子技术》模拟试题 1 (试卷共8页,答题时间120分钟)一、填空题(每空1分,共30分,请将答案直接填在空内)1.()()()1610201.110111==;()()()102163D.B ==2. 逻辑与是当决定事物结果的条件 具备时,结果才发生。

逻辑或是当决定事物结果的条件 具备时,结果才发生。

3. 利用卡诺图法化简逻辑函数的方法称为 ,其依据是具有的最小项可以合并。

4. TTL 反相器电路由 , 和 三部分组成。

5. 编码器的逻辑功能是把输入的高低电平编成一个 ,目前经常使用的编码器有 和 两类。

6. 从一组输入数据中选出一个作为数据传输的逻辑电路叫做 。

7. 触发器按照逻辑功能的不同可以分为 ,, , 等几类。

8. 时序逻辑电路在任一时刻的输出不仅取决于 ,而且还取决于电路 。

9. 触发器在脉冲作用下同时翻转的计数器叫做 计数器, n 位二进制计数器的容量等于 。

10. 施密特触发器可以用于 , , 等。

11. 从数字信号到模拟信号的转换称为 ,通常用 和描述转换精度,用 来定量描述转换速度。

二、判断题(每题1分,共10分,正确的用T 表示,错误的用F 表示,请将答案填在下面的方格内)1. 数字信号在时间和数值上都是离散的,如人数统计;2. 同或运算关系,当两输入不相等时,其输出为1;3. 最小项,顾名思义就是指的乘积项中变量个数尽可能的少;4. 集电极开路的门电路输出可以实现线与;5. 译码器,顾名思义就是把高低电平信号翻译成二进制代码;6. 数值比较器在比较两个多位数的大小时,是按照从低位到高位的顺序逐位比较的;7. 基本RS 触发器只能由与非门电路组成,用或非门是不能实现的; 8. 触发器的结构形式和逻辑功能有一一对应的关系,也就是说同一种逻辑功能只能用唯一一种结构来实现;9. 移位寄存器不仅可以寄存代码,而且可以实现数据的串-并行转换和处理; 10. 占空比是指脉冲宽度与脉冲周期的比值;三、化简题(每题 6 分,共 12 分)1. 用代数法化简逻辑函数CD D AC ABC C A Y +++=解:2. 用卡诺图法化简逻辑函数C B AC B A Y ++=四、分析与设计题(第1题18分,第2题18分,第3题12分,共 48 分)1、电路如图所示,请写出Y的逻辑函数式,列出真值表,指出电路完成了什么功能?AC2、如图所示电路,CP为时钟脉冲,Y为输出,请写出电路的驱动方程、状态方程和输出方程,列出状态转换表,画出状态转换图,说明电路的功能。

(完整版)数电试题及标准答案(五套)。

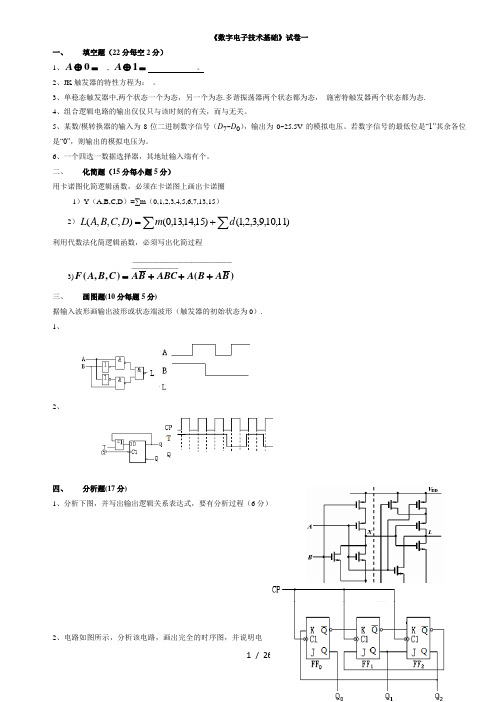

《数字电子技术基础》试卷一一、 填空题(22分每空2分)1、=⊕0A , =⊕1A 。

2、JK 触发器的特性方程为: 。

3、单稳态触发器中,两个状态一个为态,另一个为态.多谐振荡器两个状态都为态, 施密特触发器两个状态都为态.4、组合逻辑电路的输出仅仅只与该时刻的有关,而与无关。

5、某数/模转换器的输入为8位二进制数字信号(D 7~D 0),输出为0~25.5V 的模拟电压。

若数字信号的最低位是“1”其余各位是“0”,则输出的模拟电压为。

6、一个四选一数据选择器,其地址输入端有个。

二、化简题(15分每小题5分)用卡诺图化简逻辑函数,必须在卡诺图上画出卡诺圈1)Y (A,B,C,D )=∑m (0,1,2,3,4,5,6,7,13,15) 2)∑∑+=)11,10,9,3,2,1()15,14,13,0(),,,(d m D C B A L利用代数法化简逻辑函数,必须写出化简过程3)__________________________________________________)(),,(B A B A ABC B A C B A F +++=三、画图题(10分每题5分)据输入波形画输出波形或状态端波形(触发器的初始状态为0). 1、2、四、分析题(17分)1、分析下图,并写出输出逻辑关系表达式,要有分析过程(6分)2、电路如图所示,分析该电路,画出完全的时序图,并说明电路的逻辑功能,要有分析过程(11分)五、设计题(28分)1、用红、黄、绿三个指示灯表示三台设备的工作情况:绿灯亮表示全部正常;红灯亮表示有一台不正常;黄灯亮表示两台不正常;红、黄灯全亮表示三台都不正常。

列出控制电路真值表,要求用74LS138和适当的与非门实现此电路(20分)2、中规模同步四位二进制计数器74LS161的功能表见附表所示;请用反馈预置回零法设计一个六进制加法计数器。

(8分)六、分析画图题(8分)V作用下,输出电压的波形和电压传输特性画出下图所示电路在i74LS138功能表如下:74LS161功能表《数字电子技术基础》试卷一答案一、填空题(22分每空2分) 1、A ,A 2、n n n Q K Q J Q +=+13、稳态,暂稳态,暂稳态,稳态4、输入,电路原先状态5、0.1V6、两二、化简题(15分 每小题5分)1)Y (A,B,C,D )=∑m (0,1,2,3,4,5,6,7,13,15)=BD A +2)AC AD B A d m D C B A L++=+=∑∑)11,10,9,3,2,1()15,14,13,0(),,,(3))(),,(__________________________________________________________________________________=+++=++++=+++=A BC B A B A AB BC B A B A B A ABC B A C B A F三、画图题(10分 每题5分) 1、 2、四、分析题(17分) 1、(6分)B A L ⊕=2、(11分)五进制计数器五、设计题(28分) 1、(20分)1)根据题意,列出真值表由题意可知,令输入为A 、B 、C 表示三台设备的工作情况,“1”表示正常,“0”表示不正常,令输出为R ,Y ,G 表示红、黄、A B C R Y G 0 0 0 00 1 0 1 0 0 1 1 1 0 0 1 0 1 1 1 0 1 1 11 1 0 0 1 0 0 1 0 1 0 0 0 1 0 1 0 0 1 0 0 0 0 11 ×11 ×××××AB CD 00 0001 01 10 1011 11 1绿三个批示灯的 状态,“1”表示亮,“0”表示灭。

《数字电子技术》模拟试题西南交通大学

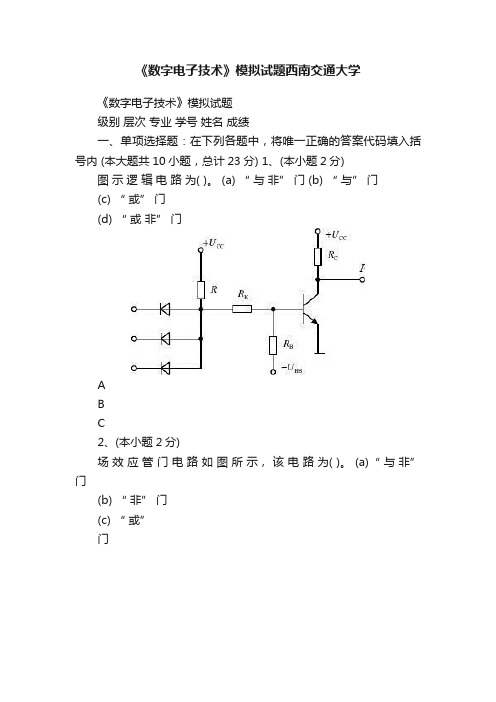

《数字电子技术》模拟试题西南交通大学《数字电子技术》模拟试题级别层次专业学号姓名成绩一、单项选择题:在下列各题中,将唯一正确的答案代码填入括号内 (本大题共10小题,总计23分) 1、(本小题2分)图示逻辑电路为( )。

(a) “ 与非” 门(b) “ 与” 门(c) “ 或” 门(d) “ 或非” 门ABC2、(本小题2分)场效应管门电路如图所示,该电路为( )。

(a)“ 与非” 门(b) “ 非” 门(c) “ 或”门+UDDF3、(本小题2分)逻辑图和输入 A ,B 的波形如图所示,分析在 t 1 时刻输出 F 为( )。

(a) “1”(b) “0”(c) 任意t 1=1AFBA B4、(本小题2分)半加器的逻辑图如下,指出它的逻辑式为( )。

(a) S =A ⊕B C =AB (b) S =A B+A B C =A B (c) S =A ⊕B C =ABABCS5、(本小题2分)逻辑电路如图所示,当A=“0”,B=“1” 时,C 脉冲来到后 D 触发器 ( )。

(a) 具有计数功能 (b) 保持原状态 (c) 置“0” (d) 置“1”B6、(本小题2分)某数/模转换器的输入为 8 位二进制数字信号(D 7 ~ D 0),输出为 0~25.5V 的模拟电压。

若数字信号的最低位是“1” 其余各位是“0”,则输出的模拟电压为( )。

(a) 0.1V (b) 0.01V (c) 0.001V7、(本小题2分)逻辑式F =A BC +ABC +A B C ,化简后为( )。

(a) F =A B +B C (b)F =A C +AB (c) F =A C +BC8、(本小题3分)二位二进制译码器的逻辑式为 Y 0=B A 、Y 1 =B A 、Y 2 =B A 、Y 3 =BA ,由逻辑式画出的逻辑电路为 ( )。

B A()b A()a9、(本小题3分)如图所示逻辑电路为()。

(a) 异步二进制计数器 (b) 异步四进制计数器 (c) 异步八进制计数器C10、(本小题3分)如图所示时序逻辑电路为()。

数字电子技术试题及答案解析1

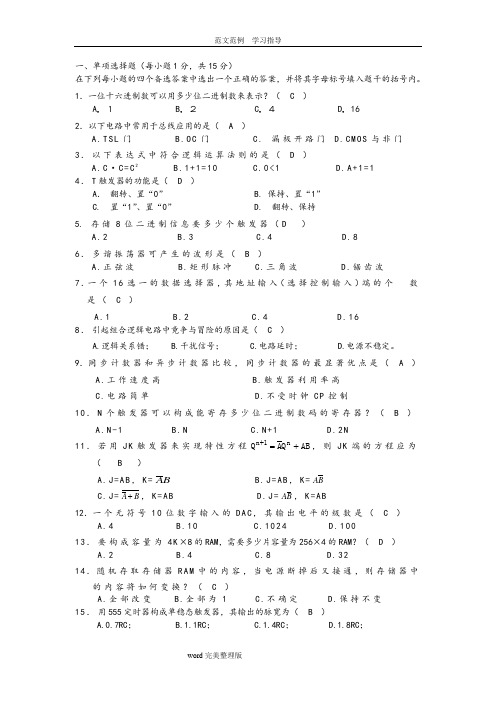

一、单项选择题(每小题1分,共15分)在下列每小题的四个备选答案中选出一个正确的答案,并将其字母标号填入题干的括号内。

1.一位十六进制数可以用多少位二进制数来表示?( C )A . 1B . 2C . 4D . 162.以下电路中常用于总线应用的是( A )A.T S L 门B.O C 门C. 漏极开路门D.C M O S 与非门 3.以下表达式中符合逻辑运算法则的是( D )A.C ·C =C 2B.1+1=10C.0<1D.A +1=1 4.T 触发器的功能是( D )A . 翻转、置“0” B. 保持、置“1” C. 置“1”、置“0” D. 翻转、保持 5. 存储8位二进制信息要多少个触发器(D )A.2B.3C.4D.8 6.多谐振荡器可产生的波形是( B )A.正弦波B.矩形脉冲C.三角波D.锯齿波 7.一个16选一的数据选择器,其地址输入(选择控制输入)端的个 数是( C )A.1B.2C.4D.16 8.引起组合逻辑电路中竟争与冒险的原因是( C )A.逻辑关系错;B.干扰信号;C.电路延时;D.电源不稳定。

9.同步计数器和异步计数器比较,同步计数器的最显著优点是( A ) A.工作速度高 B.触发器利用率高C.电路简单D.不受时钟C P 控制10.N 个触发器可以构成能寄存多少位二进制数码的寄存器?( B ) A.N -1 B.N C.N +1 D.2N11.若用J K 触发器来实现特性方程AB Q A Q n 1n +=+,则J K 端的方程应为( B )A.J =A B ,K =B AB.J =A B ,K =B AC.J =B A +,K =A BD.J =B A ,K =A B12.一个无符号10位数字输入的D A C ,其输出电平的级数是( C )A.4B.10C.1024D.100 13.要构成容量为4K ×8的RAM ,需要多少片容量为256×4的RAM ?( D )A.2B.4C.8D.32 14.随机存取存储器R A M 中的内容,当电源断掉后又接通,则存储器中的内容将如何变换?( C )A.全部改变B.全部为1C.不确定D.保持不变 15.用555定时器构成单稳态触发器,其输出的脉宽为( B )A.0.7RC ;B.1.1RC ;C.1.4RC ;D.1.8RC ;二、多项选择题(每小题1分,共5分)在下列每小题的四个备选答案中有二至四个正确答案,请将正确答案全部选出并将其字母标号填入题干的括号内;少选错选都不得分。

(完整版)数字电子技术试题及答案(题库)

数字电子技术基础试题(一)一、填空题 : (每空1分,共10分)1. (30.25) 10 = ( ) 2 = ( ) 16 。

2 . 逻辑函数L = + A+ B+ C +D = 。

3 . 三态门输出的三种状态分别为:、和。

4 . 主从型JK触发器的特性方程= 。

5 . 用4个触发器可以存储位二进制数。

6 . 存储容量为4K×8位的RAM存储器,其地址线为条、数据线为条。

二、选择题: (选择一个正确的答案填入括号内,每题3分,共30分 )1.设图1中所有触发器的初始状态皆为0,找出图中触发器在时钟信号作用下,输出电压波形恒为0的是:()图。

图 12.下列几种TTL电路中,输出端可实现线与功能的电路是()。

A、或非门B、与非门C、异或门D、OC门3.对CMOS与非门电路,其多余输入端正确的处理方法是()。

A、通过大电阻接地(>1.5KΩ)B、悬空C、通过小电阻接地(<1KΩ)D、通过电阻接V CC4.图2所示电路为由555定时器构成的()。

A、施密特触发器B、多谐振荡器C、单稳态触发器D、T触发器5.请判断以下哪个电路不是时序逻辑电路()。

图2A、计数器B、寄存器C、译码器D、触发器6.下列几种A/D转换器中,转换速度最快的是()。

图2A、并行A/D转换器B、计数型A/D转换器C、逐次渐进型A/D转换器D、双积分A/D转换器7.某电路的输入波形 u I 和输出波形 u O 如图 3所示,则该电路为()。

图3A、施密特触发器B、反相器C、单稳态触发器D、JK触发器8.要将方波脉冲的周期扩展10倍,可采用()。

A、10级施密特触发器B、10位二进制计数器C、十进制计数器D、10位D/A转换器9、已知逻辑函数与其相等的函数为()。

A、B、C、D、10、一个数据选择器的地址输入端有3个时,最多可以有()个数据信号输出。

A、4B、6C、8D、16三、逻辑函数化简(每题5分,共10分)1、用代数法化简为最简与或式Y= A +2、用卡诺图法化简为最简或与式Y= + C +A D,约束条件:A C + A CD+AB=0四、分析下列电路。

(完整版)数字电子技术试题及答案(题库)

数字电子技术基础试题(一)一、填空题 : (每空1分,共10分)1. (30.25) 10 = ( ) 2 = ( ) 16 。

2 . 逻辑函数L = + A+ B+ C +D = 。

3 . 三态门输出的三种状态分别为:、和。

4 . 主从型JK触发器的特性方程= 。

5 . 用4个触发器可以存储位二进制数。

6 . 存储容量为4K×8位的RAM存储器,其地址线为条、数据线为条。

二、选择题: (选择一个正确的答案填入括号内,每题3分,共30分 )1.设图1中所有触发器的初始状态皆为0,找出图中触发器在时钟信号作用下,输出电压波形恒为0的是:()图。

图 12.下列几种TTL电路中,输出端可实现线与功能的电路是()。

A、或非门B、与非门C、异或门D、OC门3.对CMOS与非门电路,其多余输入端正确的处理方法是()。

A、通过大电阻接地(>1.5KΩ)B、悬空C、通过小电阻接地(<1KΩ)D、通过电阻接V CC4.图2所示电路为由555定时器构成的()。

A、施密特触发器B、多谐振荡器C、单稳态触发器D、T触发器5.请判断以下哪个电路不是时序逻辑电路()。

图2A、计数器B、寄存器C、译码器D、触发器6.下列几种A/D转换器中,转换速度最快的是()。

图2A、并行A/D转换器B、计数型A/D转换器C、逐次渐进型A/D转换器D、双积分A/D转换器7.某电路的输入波形 u I 和输出波形 u O 如图 3所示,则该电路为()。

图3A、施密特触发器B、反相器C、单稳态触发器D、JK触发器8.要将方波脉冲的周期扩展10倍,可采用()。

A、10级施密特触发器B、10位二进制计数器C、十进制计数器D、10位D/A转换器9、已知逻辑函数与其相等的函数为()。

A、B、C、D、10、一个数据选择器的地址输入端有3个时,最多可以有()个数据信号输出。

A、4B、6C、8D、16三、逻辑函数化简(每题5分,共10分)1、用代数法化简为最简与或式Y= A +2、用卡诺图法化简为最简或与式Y= + C +A D,约束条件:A C + A CD+AB=0四、分析下列电路。

西南交1112考试批次《数字电子技术A》复习题及参考答案

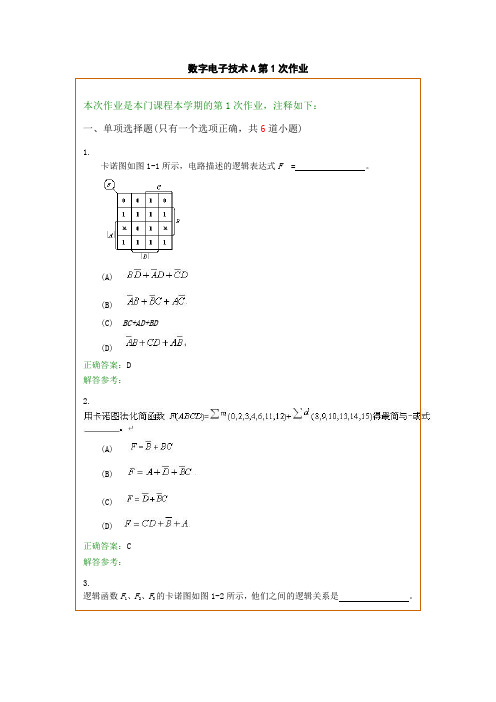

数字电子技术A第1次作业本次作业是本门课程本学期的第1次作业,注释如下:一、单项选择题(只有一个选项正确,共6道小题)1.卡诺图如图1-1所示,电路描述的逻辑表达式F = 。

(A)(B)(C) BC+AD+BD(D)正确答案:D解答参考:2.(A)(B)(C)(D)正确答案:C解答参考:3.逻辑函数F1、F2、F3的卡诺图如图1-2所示,他们之间的逻辑关系是。

(A) F3=F1•F2(B) F3=F1+F(C) F2=F1•F3(D) F2=F1+F3正确答案:B解答参考:4.八选一数据选择器74151组成的电路如图1-3所示,则输出函数为()(A)(B)(C)(D)正确答案:C解答参考:5. 十进制数3.625的二进制数和8421BCD码分别为()(A) 11.11 和11.001(B) 11.101 和0011.011000100101(C) 11.01 和11.011000100101(D) 11.101 和11.101正确答案:B解答参考:6. 下列几种说法中错误的是()(A) 任何逻辑函数都可以用卡诺图表示(B) 逻辑函数的卡诺图是唯一的。

(C) 同一个卡诺图化简结果可能不是唯一的(D) 卡诺图中1的个数和0的个数相同。

正确答案:D解答参考:四、主观题(共15道小题)7.如图3所示,为检测水箱的液位,在A、B、C、三个地方安置了三个水位检测元件,当水面低于检测元件时,检测元件输出低电平,水面高于检测元件时,检测元件输出高电平。

试用与非门设计一个水位状态显示电路,要求:当水面在A、B之间的正常状态时,仅绿灯G亮;水面在B、C 间或A以上的异常状态时,仅黄Y灯亮;水面在C以下的危险状态时,仅红灯R亮。

参考答案:8.电路如图7所示,图中74HC153为4选1数据选择器。

试问当MN为各种不同输入时,电路分别是那几种不同进制的计数器。

参考答案:MN=00 8进制计数器,MN=01 9进制计数器,MN=10 14进制计数器,MN=11 15进制计数器.9.发由全加器FA、2-4线译码器和门电路组成的逻辑电路如图3 a所示。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

西南交通大学数字电子技术学期考试试题一

一. 简答填空题(共20分,第6小题每空2分,其它每空1分)

1. 某数字信号的逻辑值为0111010,设高电平电压为5V ,低电平电压为0V 。

试绘出该信号的数字波形。

波形:

2. 已知某时序电路的状态转换表如下,如果初态为S 0,输入序列为X=110101101时,则输出序列为 。

3. 写出下图所示各门电路的输出状态(0或1)。

已知V IH =3.6V ,V IL =0.4V ,图(a )、(b )是TTL 门,图(c )、(d )是CMOS 门。

4. 一个存储容量为256K ×8的存储器,地址线有 条,数据线有 条。

5. 如要将一个最大幅度为5.1V 的模拟信号转换为数字信号,要求输入每变化20mv ,输出信号的最低位(LSB)发生变化,应选用 位A/D 转换器,其分辨率为 %。

次态/输出

6. 四个电路输入V I 、输出V O 的波形如图所示,试简答分别实现下列功能的最简电路类型(不必画出电路)。

7. 写出下图所示PLD 的输出F 1、F 2逻辑表达式。

二. 逻辑代数和组合逻辑

1. 公式法化简下列函数为最简与或式。

(4分)

BD C D A B A C B A D C B A F ++++=),,,(

2. 分析以下组合电路的功能,要求写出图示电路的逻辑表达式(3分),列出其

真值表(2分),并说明电路的逻辑功能(2分)。

(a )

F 1=

F 2=

三. 用或非门设计一个组合电路。

其输入为8421BCD 码,输出L 当输入数能被4整除时为1,其他情况为0。

(0可以被任何整数整除,要求有设计过程,给出电路图)

(1)建立真值表 (3分) (2)写出函数的最小项表达式 (3分) (3)化简函数表达式 (4分) (4)用或非门实现。

(4分)

四. 已知时序电路如图所示。

1. 请写出各触发器的驱动方程和次态方程。

(5分) 2. 画出电路的状态(Q 1Q 0)转换图。

(5分)

五. 下图为一个电路的状态转换图。

现准备用D 触发器实现该电路,请写出触发器的驱动方程和输出方程。

(S 0、

S 1、S 2的编码分别为00、01、11)(15分)

六. CP

0/0

0/0/

1. 74161接成了几进制的计数器?(3分) 2. 画出输出CP 、Q 0、Q 1、Q 2、L 的波形。

(7分)

(器件功能表见最后一页)

七.

(10分)

1. 的工作状态; 2. 8D 寄存器IC5

中的;

3. 写出按键P 时,b 7b 6b 5b 4b 3b 2b 1的编码值。

注:IC3的功能描述:

G 1G

2

:使能信号,低电平有效;

A 0A

1

A

2

A

3

:地址输入;

Y 0Y

1

······Y

15

:译码输出,低电平有效;

使能信号有效时,各译码输出的表达式见表:

八.用555定时器构成的一种触发定时电路如图所示。

(10分)试回答:

1.电路的稳态Q=?

2. v

i

为何种边沿触发?触发信号幅值应为多大?

3.画出v

c

及v o从触发翻转到定时结束的波形;

4.导出输出信号脉宽t

w

的计算公式。

(注:触发信号的脉冲宽度小于输出信号的脉冲宽度)

附:芯片功能表

同步4位二进制计数器74161的符号和功能表如下:

功能

表: 符号:

8选1选择器74151的符号和功能表如下:

功能表: 符号:

其中输出Q 3是最高位,输入D 3是最高位,C 是进位信号,74161只当 Q 3Q 2Q 1Q 0 =1111时,C=1。

8D寄存器内部电路:

西南交通大学数字电子技术模拟试题一答案

一. 简答填空题

1.波形:

2.输出序列为 001010010

3.

4.地址线有18条,数据线有8条

5.应选用8位A/D转换器,其分辨率为0.39 %

6.

7.

二. 逻辑代数和组合逻辑

1.答案:

2.答案:

表达式:

真值表:

电路功能:一位全加器,S是相加的和,CO是进位

三. 答案:

(1)设用A、B、C、D表示8421BCD码,根据题意列真值表如下:

(2)写出函数的最小项表达式:

(3)化简函数表达式:用卡诺图化简得

(4)用或非门实现:变化表达式

电路图:

四.答案:

1.电路方程:

2.电路的状态转化图:

五.答案:根据题意列出电路的激励表:

得出电路方程:

输出方程:

驱动方程:

六.答案:

1. 161接成6进制计数器

2.波形如下:

七. 答案:

1.计数器IC1、IC2均处于计数状态,IC3处于译码状态,根据IC1的计数值使相应的输出为低电平(0),多路选择器IC4处于选通状态,但所有输入数据均为高电平(1),所以输出Y=1,/Y=0,寄存器IC5无时钟信号有效沿到来,处于保持状态。

2.按下P时,当IC1计数到0010,译码器IC3输出Y

2

为底电平,IC2计数到0010时,使IC4的输出Y为低电平,将IC1、IC2计数值锁定并使其处于保持状态,IC4的输出/Y输出一个上升沿,IC5将IC1、IC2的当前值保存到寄存器中。

3.按键P时,b

7b

6

b

5

b

4

b

3

b

2

b

1

的编码值为0100010

八.答案:

1.电路的稳态Q=1

2.v i为正边沿触发,触发信号幅值应大于2/3V CC 3.v c及v o从触发翻转到定时结束的波形

4.输出信号脉宽t

w

的计算公式:

t

w =RCln3。